一种兼容处理pll和dll模式的isp接收器

技术领域

1.本发明属于集成电路技术领域,涉及显示信号处理,具体涉及一种兼容处理pll和dll模式的isp接收器。

背景技术:

2.isp(intergrated-stream protocol)是显示驱动芯片厂商定义的用于系统内的时钟内嵌高速串行接口协议,接收端需要把数据中的时钟数据恢复(cdr:clock data recovery)。isp协议定义了dll和pll两种工作模式,两种模式的训练模式不同,具体表现在使用的训练时钟信号不一致,如图3所示给出这两种模式的训练时钟,图3中,pll模式下[1]、[2]为一个信号全周期,dll模式下,[1]、[2]

…

[8]为一个信号全周期。

[0003]

现有的isp接收器设计成只能应用于pll模式或dll模式,测试时要求发送端配合调成对应模式才能正常工作, dll模式下的压控振荡器vco为低频多相位输出的; pll模式下的压控振荡器vco高频少相位输出的,使得pll模式架构和dll模式架构不兼容,不能同时处理两种模式。

技术实现要素:

[0004]

为克服现有技术存在的技术缺陷,本发明公开了一种兼容处理pll和dll模式的isp接收器。

[0005]

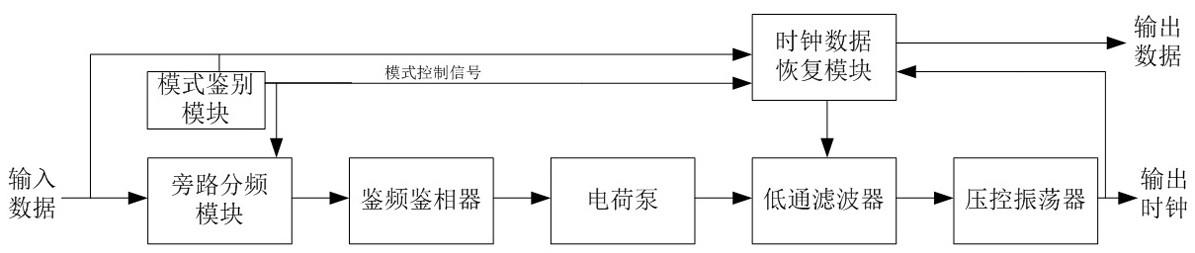

本发明所述兼容处理pll和dll模式的isp接收器,其特征在于,包括旁路分频模块及与其连接的锁相环路,所述锁相环路包括顺次连接的鉴频鉴相器、电荷泵、低通滤波器和压控振荡器;还包括与所述低通滤波器和压控振荡器连接的时钟数据恢复模块;其中旁路分频模块的功能为:当输入信号为dll模式时,将输入信号直接输出到锁相环路;当输入信号为pll模式时,将输入信号四分频后输出到锁相环路;所述时钟数据恢复模块可根据输入信号选择对应的工作模式。

[0006]

优选的:还包括一个模式鉴别模块,与所述旁路分频模块和时钟数据恢复模块信号连接。

[0007]

优选的:所述旁路分频模块包括两个d触发器串联而成的四分频器,两个d触发器的q端分别通过一个反相器连接d端,第一d触发器的d端连接第二d触发器的时钟输入端;模式选择端连接第一反相器输入端,第一反相器输出端连接第二反相器,第一反相器的输出端和复位端分别连接第一与门的两个输入端,与门的输出端连接两个d触发器的时钟端,旁路分频模块的时钟输入端连接第三反相器输入端,第三反相器输出端连接第一d触发器输入端;第一d触发器的q端和第二d触发器的d端分别连接第一与非门的两个输入端,第一与非门的输出端和第二反相器输出端分别连接或非门的输入端,或非门的输出端和时钟输入端分别连接第二与非门的两个输入端;第三反相器输出端和第二反相器输出端分别连接

第三与非门的两个输入端;第二与非门和第三与非门的输出端分别连接第二与门的两个输入端,第二与门的输出端作为旁路分频模块的时钟输出端。

[0008]

优选的:所述时钟数据恢复模块包括数据输入端、时钟校准输入端、恢复模式选择端、电流输出端、数据输出端及数据恢复子模块,dll模式时钟校准子模块和pll模式时钟校准子模块;所述数据输入端、电流输出端、时钟校准输入端和数据输出端接到数据恢复子模块,数据恢复子模块的数据输出到数据输出端,并输出到dll模式时钟校准子模块和pll模式时钟校准子模块,数据恢复子模块的电流输出端与低通滤波器连接;所述恢复模式选择端连接dll模式时钟校准子模块和pll模式时钟校准子模块;所述时钟数据恢复模块还包括锁定信号输出端,所述锁定信号输出端与dll模式时钟校准子模块和pll模式时钟校准子模块连接,所述锁定信号输出端还与锁相环路的鉴频鉴相器和电荷泵控制连接。

[0009]

本发明通过设置旁路分频模块的工作模式,配合时钟数据恢复模块的对应配置,可以实现对dll和pll两种模式的兼容处理,并可适时关闭锁相电路从而降低功耗。

附图说明

[0010]

图1是通过本发明所述isp接收器的一种具体实施方式示意图;图2是本发明所述旁路分频模块的一种具体实施方式示意图;图2中,inv1-第一反相器, inv2-第二反相器, inv3-第三反相器, inv4-第四反相器, inv5-第五反相器,nand1-第一与非门, nand2-第二与非门, nand3-第三与非门,and1-第一与门, and2-第二与门,nor-或非门,clk-时钟输入端,ckout-时钟输出端,reset-复位端,mode-模式选择端;图3为dll和pll两种工作模式的训练时钟信号,图中[0]、[1]、[2]

…

表示连续相等的时间间隔,0,1分别表示低电平和高电平;图4为本发明一个具体实施方式中旁路分频模块的信号波形示意图,图4中横坐标为时间,纵坐标为电压。

[0011]

图5为本发明所述时钟数据恢复模块的一个具体实施方式示意图,图5中,ck-时钟校准输入端,lock-锁定信号输出端,din-数据输入端,dout-数据输出端.rmode-恢复模式选择端,iout-电流输出端。

具体实施方式

[0012]

以下结合附图及附图标记对本发明的实施方式做更详细的说明。

[0013]

本发明所述兼容处理pll和dll模式的isp接收器,如图1所示,包括旁路分频模块及与其连接的锁相环路,所述锁相环路包括顺次连接的鉴频鉴相器、电荷泵、低通滤波器和压控振荡器,还包括与所述低通滤波器和压控振荡器连接的时钟数据恢复模块;其中旁路分频模块的功能为:当输入信号为dll模式时,将输入信号直接输出到锁相环路;当输入信号为pll模式时,将输入信号四分频后输出到锁相环路;所述时钟数据恢复模块可根据输入信号选择对应的工作模式。

[0014]

可以直接输入模式信号到时钟数据恢复模块和旁路分频模块,根据模式信号表示

当前信号为dll模式还是pll模式,选择旁路分频模块和时钟数据恢复模块的工作方式。

[0015]

图1所示的具体实施方式中,所述isp接收器还包括一个模式鉴别模块,鉴别输入信号工作模式,例如检测输入信号的频率,输出模式信号到旁路分频模块和时钟数据恢复模块进行工作方式选择。模式鉴别模块可以采用鉴频器直接检测输入信号频率实现。

[0016]

本发明用于兼容处理pll和dll模式信号,当输入信号为低频的dll模式信号时,旁路分频模块选择将输入信号不做处理直接输出到锁相环路,由锁相环路进行锁相处理后输出相位与输入信号相同的时钟信号到时钟数据恢复模块进行时钟提取和信号识别。

[0017]

当输入信号为高频的pll模式信号时,旁路分频模块将输入信号进行四分频降频后输出到锁相环路,由锁相环路进行锁相处理后输出相位与输入信号相同的时钟信号到时钟数据恢复模块进行时钟提取和信号识别。

[0018]

如图4所示给出旁路分频模块的一个具体波形示意图,图4中mode信号为低电平时,旁路分频模块工作在分频模式,对输入信号clk进行四分频后降频输出,当mode信号为高电平时,旁路分频模块工作在旁路模式,对输入信号clk不降频直接输出同频同相位信号。

[0019]

图2给出所述旁路分频模块的一个具体实施方式,本领域技术人员根据旁路分频模块的功能,可以根据数字电路原理得出可实现相同功能但结构不同的其他实现方式。

[0020]

如图2所示,所述旁路分频模块包括两个d触发器串联而成的四分频器,两个d触发器的q端分别通过一个反相器连接d端,第一d触发器的d端连接第二d触发器的时钟输入端;模式选择端mode连接第一反相器输入端,第一反相器输出端连接第二反相器,第一反相器的输出端和复位端reset分别连接第一与门的两个输入端,与门的输出端连接两个d触发器的时钟端,旁路分频模块的时钟输入端clk连接第三反相器输入端,第三反相器输出端连接第一d触发器输入端;第一d触发器的q端和第二d触发器的d端分别连接第一与非门的两个输入端,第一与非门的输出端和第二反相器输出端分别连接或非门的输入端,或非门的输出端和时钟输入端clk分别连接第二与非门的两个输入端;第三反相器输出端和第二反相器输出端分别连接第三与非门的两个输入端;第二与非门和第三与非门的输出端分别连接第二与门的两个输入端,第二与门的输出端作为旁路分频模块的时钟输出端ckout。

[0021]

当模式选择端mode为低电平时,表示为pll模式,旁路分频模块对从时钟输入端clk输入的时钟信号通过两个d触发器实现四分频后输出,当模式选择端mode为高电平时,表示为dll模式,此时d触发器不进行分频,旁路分频模块对输入的时钟信号通过第二与非门和第二与门直接输出。

[0022]

时钟数据恢复模块的具体作用是根据锁相环路输出的时钟信号,对输入数据进行数据识别处理,时钟数据恢复模块根据输入数据的不同格式选择不同的工作方式。

[0023]

为降低功耗,本发明对原有的数据恢复模块进行改进,如图5给出时钟数据恢复模块的一个具体实施方式,所述时钟数据恢复模块包括数据输入端、时钟校准输入端、恢复模式选择端、电流输出端、数据输出端及数据恢复子模块,dll模式时钟校准子模块和pll模式时钟校准子模块;所述数据输入端、电流输出端、时钟校准输入端和数据输出端接到数据恢复子模块,数据恢复子模块的数据输出到数据输出端,并输出到dll模式时钟校准子模块和

pll模式时钟校准子模块,数据恢复子模块的电流输出端与低通滤波器连接;所述恢复模式选择端连接dll模式时钟校准子模块和pll模式时钟校准子模块。

[0024]

数据从数据输入端din进入,由数据恢复子模块对数据进行恢复,数据恢复子模块是根据输入的数据和时钟信号对数据进行恢复的电路模块,数据恢复子模块内具有鉴频鉴相模块并从电流输出端输出电流到低通滤波器用于控制低通滤波器的频带位置,数据恢复子模块为本领域现有技术,在此不再赘述。

[0025]

数据恢复后从数据输出端dout输出,并输出到dll模式时钟校准子模块和pll模式时钟校准子模块,分别用于对数据进行两种模式下的时钟校准,并由模式控制端rmode输入信号控制两个时钟校准子模块的工作状态,例如rmode为高电平,表示为dll模式,则dll模式时钟校准子模块正常工作输出锁定成功信号而pll模式时钟校准子模块不工作且无输出;dll模式时钟校准子模块在dll模式下对输入的数据进行时钟校准,其中所述时钟校准输入端ck与所述压控振荡器的输出端连接。

[0026]

反之,如果rmode为低电平,表示为pll模式,则pll模式时钟校准子模块正常工作输出锁定成功信号而dll模式时钟校准子模块不工作且无输出。

[0027]

由dll模式时钟校准子模块或pll模式时钟校准子模块对数据完成时钟校准后,从锁定信号输出端lock输出锁定成功信号,所述锁定信号输出端与dll模式时钟校准子模块和pll模式时钟校准子模块连接,所述锁定信号输出端还与锁相环路的鉴频鉴相器和电荷泵控制连接。

[0028]

锁定信号输出端由dll模式时钟校准子模块和pll模式时钟校准子模块输出的信号相加决定,只要两个模式下任意一个时钟校准子模块实现了时钟校准,说明时钟数据恢复模块已经将时钟校准,锁定信号输出端即可输出锁定信号,由于数据恢复子模块内有鉴频鉴相模块可以实现对输入数据的鉴频鉴相功能,此时不再需要锁相环路中鉴频鉴相器和电荷泵工作,输出锁定信号关闭锁相环路中鉴频鉴相器和电荷泵,以降低功耗。

[0029]

以上内容是结合具体的优选实施方式对本发明作的进一步详细说明,不能认定本发明的具体实施方式只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明的技术方案下得出的其他实施方式,均应包含在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。