用于led或oled显示器的驱动器及驱动电路

技术领域

1.本发明涉及显示器领域,例如固态固定格式显示器(诸如离散发光led或oled显示器),以及制造或操作此类显示器的方法,以及可任选地用于执行此类方法的控制器和软件。具体而言,本发明涉及用于有源led或oled显示器的像素或子像素的控制或驱动电路和方法。

背景技术:

2.实现高动态范围显示器和发光器件的问题在本领域中是已知的。

3.us6987787b1描述了用于宽范围明度控制的led亮度控制系统。(用作液晶显示器的背光的)发光二极管的明度必须被控制在至少20000到1的范围上。us6987787b1描述了一种led控制系统,其中pwm信号的占空比与电流脉冲的振幅同时被调制。使用8位来对占空比进行编码且也使用8位对电流脉冲的振幅进行编码将给出总共65536明度范围。

4.pwm信号的占空比和电流脉冲的振幅这两者的调制将允许在较低明度级更小的明度步进和在较高明度级更大的明度步进。

5.us6987787b1没有提及如何在解决带宽约束(这将需要在小于16位上对明度进行编码)的同时,维持在至少20000到1的范围上控制明度的能力。与色点的稳定性相关联的问题(其随led中电流脉冲的振幅而变化)也仍然存在。

6.在us8339053中,描述了“led调光装置”,它利用两种调光机制来控制led发光器件的明度。

7.在第一“较低明度”机制中,流过led的电流是使用恒定电流脉冲振幅调制的脉宽。在第二“较高明度”机制中,流过led的电流按模拟方式来控制并且没有脉冲化。流过led的电流是连续的,并且其振幅由恒流电路来确定。

8.us8339053没有提供用于驱动led显示器的诸个体led的可行解决方案。us8339053没有讨论视觉伪影的问题,并且尤其是在以不同电流振幅驱动各led时必然存在的色彩伪影。

9.ep1846910b1“active matrix organic light emitting diode display(有源矩阵有机发光二极管显示器)”公开了如何使用所有像素共用的pwm信号对有源矩阵oled显示器进行调光,同时避免色彩伪影。

10.与ep1846910b1的图3相对应的图1示出了电路的一个示例,该电路可被用于在不影响色点的情况下使用pwm信号对发光二极管发出的光进行调光。晶体管(ep1846910的图3上的元件310)可以通过施加到其栅极的pwm信号来打开和闭合。当晶体管打开时,没有电流可以循环通过oled 308并且没有光被发出。当晶体管闭合时,电流i

oled

可以循环通过oled 308并且光被发出。电流的振幅由施加到晶体管304的栅极的模拟输出(a.o.)电压确定。由于相同的pwm信号被施加到显示器的每一像素,所以带宽没有问题。仍然需要模拟信号(将被加载到电容器306上)来“编程”对应于oled 308的(子)像素的亮度。

11.us2018/0197471a1“digital-drive pulse-width-modulated output system(数

字驱动脉宽调制输出系统)”公开了一种包括像素阵列的有源矩阵数字驱动显示系统。每一像素具有输出装置、响应于加载定时信号来用于在不间断加载时间段期间接收和存储多位数字像素值的串行数字存储器、以及驱动电路,该驱动电路响应于脉宽调制(pwm)定时信号和存储在串行数字存储器中的多位数字像素值,以在不间断的输出时间段期间驱动输出装置。

12.数字存储对于使用薄膜晶体管的传统平板显示器而言并不实际,因为数字像素值存储所需的薄膜电路太大而无法实现所需的显示分辨率。us2018/0197471a1通过具有晶体半导体基板的小型微转移印刷集成电路(小芯片)解决了这个问题,并在具有实用分辨率的数字显示器中提供小型、高性能串行数字存储器电路和时间控制的恒流led驱动电路。此类显示器可以具有出色的分辨率,因为小芯片非常小。如果小芯片不可用,则us2018/0197471a1中公开的解决方案不适用于高分辨率显示器。图2给出了根据us2018/0197471a1的电路的示例。

13.现有技术中的另一问题是如us2018/0197471a1中所公开的加载时间段。实际上,以具有160*135个led的显示器平铺片(tile)为例。如果帧速率为每秒60帧,则将例如12位到15位发送到与每一像素相关联的存储器必须在比最低有效位b0的pwm子周期更短的时间内完成(以避免视觉伪影)。理想地,这应该顺序地进行,以限制将信号传送到像素的信号轨道的数量。

14.如果pwm信号以15位或更多位进行编码,则最低有效位b0的pwm定时时段将必须小于0.5μs。在小于0.5μs的时间内将160*135个像素加载到每一串行存储器并不容易。

15.应用us2018/0197471a1的教导很有吸引力,但在不使用小芯片的情况下似乎是不可行的。

16.现有技术需要改进。

技术实现要素:

17.本发明的实施例提供用于分立光源(诸如固态光源)的电流控制或驱动电路以及驱动所述电路的方法,其中有源矩阵显示器的led或oled子像素或像素是其中的示例,其中存在存储器来存储用于驱动像素或子像素的控制信号的一个或多个位。光源由控制信号(诸如特定位深的脉宽调制信号)来驱动,由此用于存储pwm控制信号的一个或多个位的存储器存储比诸如pwm信号之类的控制信号的位深更少数目的位。

18.本发明的实施例的优点是可以使控制电路元件与薄膜工艺兼容,诸如以生产薄膜晶体管。

19.本发明的实施例的另一优点是用于控制诸如led或oled之类的光源的光输出的控制电路或驱动有利地没有对led或oled显示器的光源的分辨率(或像素节距)施加限制。这是因为该紧凑设计。本发明的实施例的又一优点是控制电路足够快以与给定的帧速率和用于编码pwm信号的位数相兼容。

20.因此,本发明的实施例提供用于包括有源矩阵显示器的led或oled像素的光源的电流控制或驱动电路。图14a、14c、15和17以及22至27中特别示出了电流控制或驱动电路的组件及其连接方式。在电流控制或驱动电路中:

21.提供第一存储元件(诸如电容器或电容器电路,其中具有电容器的采样保持装置

是一示例)以控制发光元件(诸如用于有源矩阵显示器中的子像素或像素的led或oled)中的电流。当电容器在一位存储器中存储诸如一个位所需的值时,它使该值对于其一个电极上的电路是可用的。代替电容器,具有相同功能的其他元件(诸如双稳态存储器元件)可被使用,诸如无时钟控制(unclocked)触发器。

22.此外,还提供存储控制信号(诸如pwm控制信号)的下一个或多个位的存储器元件。存储在存储器元件中的位数小于控制信号(诸如pwm控制信号)的位深。存储器元件优选地是一位、二位或多位时钟控制(clocked)双稳态元件,诸如一个或多个时钟控制触发器。

23.驱动电路或电流控制电路还可包括:

24.具有第一控制电极的控制元件,其被配置成控制通过发光元件(诸如用于有源显示器的像素或子像素的led或oled)的电流。

25.控制元件可以是诸如pmos晶体管之类的晶体管,并且优选地是薄膜晶体管。还可以使用nmos晶体管或pmos和nmos晶体管的组合,其中该晶体管或所有晶体管可以并且优选地是薄膜晶体管。控制电极可以是这样一个或多个晶体管的栅极。发光元件可以是像素的一部分、子像素或完整像素。通过发光元件的电流可以由一个或多个晶体管栅极上的电压来控制。

26.第二存储元件可以是被提供用于存储控制信号的第二值的存储器元件。第二存储元件可以是逻辑元件,诸如一位、两位或多位存储器,前提是位数小于控制信号(诸如pwm信号)的位深。例如,第二存储元件可以是与晶体管或时钟控制触发器相组合的电容器,或者具有与触发器相同的真值表的装置。因此,它通常可以是时钟控制双稳态元件。

27.电流控制或驱动电路可包括诸如开关之类的传输元件。传输元件或开关可以是晶体管,诸如pmos晶体管,优选地是薄膜晶体管,或者它可以是配置成开关的晶体管电路。可以使用nmos晶体管或nmos晶体管电路或者nmos和pmos晶体管的组合。

28.传输元件可具有用于将控制信号的第二值加载到第一存储元件的第二控制电极,其中由第一存储元件和/或第二存储元件存储的位数小于控制信号(诸如pwm控制信号)的分辨率的位深。

29.本发明的实施例的一优点是,电流控制或驱动电路的元件可以采用相同的技术来制造,例如存储元件(诸如任何存储器元件)采用相同的技术制造,作为实现成连接到发光元件(诸如led或oled)的晶体管的开关。具体而言,该相同技术是薄膜工艺(tft)技术。通过这些手段,可以实现紧凑设计。

30.本发明的实施例提供了一种用于分立光源(诸如固态光源,其中例如有源矩阵显示器的led或oled子像素或像素是其示例)的电流控制或驱动电路。电流控制或驱动电路可包括:存储器,用于存储用于驱动有源矩阵显示器的像素或子像素的控制信号(诸如pwm控制信号)的一个或多个位以及驱动所述电路的方法。光源可由特定位深的脉宽调制控制信号来驱动,其中用于存储pwm控制信号的一个或多个位的每一像素或子像素的存储器存储比pwm信号的位深更少数目的位。

31.电流控制或驱动电路可被适配成在当前位被用于控制诸如led或oled之类的光源中的电流(即电流控制因此控制光输出)时加载下一位。

32.存储器可以是仅存储下一位的一位存储器,或者可以是多位存储器,只要位数小于控制信号(诸如pwm控制信号)的位深。有源矩阵显示器可包括按行和列布置的像素或子

像素发光元件的阵列。存储器(例如时钟控制双稳态装置)可以是列宽移位寄存器的一部分。

33.使用控制位的时长给出了控制信号子周期(诸如与该位相关联的pwm子周期)的宽度。如下所述,对于位b-1和b-2,它意味着由于t0不能减小,因此可以通过使用复位信号来覆盖(override)该位的值。对于b-1,通过在时间t0/2直至时间t0之间覆盖b-1,使时间长度是t0/2;对于b-2,通过在时间t0/4和时间t0之间覆盖b-1,使时间长度是t0/4(复位信号(rst信号)在区间t0结束之前擦除位b-1或b-2)。

34.在本发明的一实施例中,提供了一种控制诸如led或oled之类的发光元件中的电流的电路,该电路包括:

35.具有第一控制电极以控制流过发光元件的电流的控制元件;

36.用于存储控制信号的第一值的第一存储元件,所述控制信号被施加到控制元件的第一控制电极;

37.用于存储控制信号的第二值的第二存储元件;

38.具有第二控制电极以向第一存储元件加载控制信号的第二值的传输元件。

39.在该电路中,可以使用相同的薄膜晶体管技术来实现控制元件、第一存储元件、第二存储元件和诸如晶体管之类的传输元件。

40.本发明的该实施例和其他实施例的优点是,当第一控制电压被施加到控制元件的控制电极以控制发光元件中的电流时,在第二存储元件上加载第二控制电压是可能的。因此,不存在因无数据可供用于控制而导致发光元件保持空闲的“停滞时间(dead time)”。

41.本发明实施例的优点是,即使第二存储元件一次只能存储有限数量的位,例如一位或两位,用任意大数量的顺序位来控制控制元件也是可能的。具体而言,第二存储元件可以存储比构成用于驱动像素的pwm信号的位深更少的位数。

42.更具体而言,第二存储元件存储一位或两位,或者可以是多位存储元件。

43.当发光元件中的电流由脉宽调制方案(pwm)控制时,这尤为重要,所需的脉宽调制被编码成位串,这些位可以被一次一个顺序地施加到控制元件的控制电极。

44.限制用于顺序地控制控制元件的诸位的存储的大小使得以经减小的像素或子像素节距(即,像素或子像素阵列的空间周期减小)实现电流控制电路的高密度阵列成为可能。

45.第一控制元件可以是将电流源与发光元件有条件地相连接的开关。第一控制元件控制来自电流源的电流能如何到达发光元件。第一控制元件可以与发光元件串联或并联。当并联时,它绕过发光元件,这防止发光元件被驱动,除非第一控制元件打开(即不导电)。

46.第一控制元件可以是晶体管(例如pmos晶体管),且第一控制电极可以是所述晶体管或所述pmos晶体管的栅极。这一晶体管(诸如pmos晶体管)可以是薄膜晶体管。可以使用nmos晶体管或者pmos或nmos晶体管电路。

47.第一存储元件可以是电容器,其第一电极连接到第一控制元件的第一控制电极且其第二电极连接到参考节点,尤其是供电节点。当电容器存储值(诸如它操作来在一位存储器中保持一位时),它使该值对于其一个电极上的电路是立即可用的。代替电容器,具有相同功能的其他元件(诸如双稳态存储器元件)可被使用,诸如无时钟控制触发器。

48.传输元件可以是晶体管,如pmos晶体管。晶体管可以是薄膜晶体管,诸如薄膜pmos

晶体管。可以使用nmos晶体管或者pmos或nmos晶体管电路。

49.第二存储元件可以是电容器和晶体管或另一可编程存储器,诸如单位或多位存储器,诸如一个或多个触发器。第二存储元件优选地是时钟控制的(clocked)。多位存储器可以存储比控制信号(诸如pwm控制信号)的位深更少的位数。

50.在替换实施例中,第一存储元件可以是可编程存储器,诸如单位或多位存储器,例如一个或多个触发器。此类触发器优选地是无时钟控制的(unclocked)。

51.在本发明的另一方面中,借助于第一存储元件施加到第一控制元件的控制电极的控制信号可以被覆盖。

52.覆盖存储在第一存储元件上的控制信号可以借助于开关来实现,该开关将控制电极有条件地连接到替换控制信号。

53.当第一存储元件是电容器时,开关可以是分流第一存储元件的复位开关。另选地,复位开关可以分流发光元件。开关可以是晶体管,且具体而言是pmos晶体管。这一晶体管或诸pmos晶体管可以是薄膜晶体管。

54.在本发明的另一实施例中,根据本发明的实施例的电流控制或驱动电路被用于驱动显示器。显示器可以是例如固态光源显示器,诸如led显示器或oled显示器。

55.根据本发明的实施例的电流控制或驱动电路及其所驱动的发光元件可以按行和列来布置,即按阵列来布置。阵列的l行中的每一行都具有m个电流控制或驱动电路及其相关联的发光元件。

56.同一列(或行)中的每一电路的第二存储元件可以连接到同一数据信号线,并且同一行(或列)中每一电路的第二存储元件可以连接到同一扫描线。施加到扫描线的信号使得能够存储数据信号线上存在的信号。扫描线可以例如控制开关,该开关使数据信号线和第二存储元件有条件地电接触。

57.或者,同一列(或行)中的每一电路的第二存储元件可以是列宽(或行宽)移位寄存器的一部分。移位寄存器可以用薄膜晶体管与电流控制电路的薄膜晶体管一起实现。本发明的这一方面的优点是它简化了数据和控制信号到电流控制电路的布线。

58.在本发明的另一方面中,提供了一种在第一存储元件的内容被用于控制发光元件中的电流的同时更新第二存储元件的内容的方法。旨在用于电流控制电路的阵列中同一列(或行)中的电流控制或驱动电路的第二存储元件的诸位中的每一位可以被顺序地施加到第二存储元件的输入端,诸如一位、二位或多位存储器元件(诸如电流控制电路的列(或行)中的第一触发器)。

59.为了更新列(或行)中的电流控制或驱动电路的第二存储元件,在列(或行)宽移位寄存器的输入端顺序地呈现n位,并通过使用一系列n个第一时钟信号对移位寄存器进行时钟计时来使该n位移位通过移位寄存器。

60.然后,第二存储元件的内容被传输到第一存储元件。

61.本发明的该方面的优点是,同时更新同一列(或行)中的电流控制或驱动电路的第一存储元件。或者,更新是针对整个阵列同时完成的。

62.在本发明的又一方面中,相邻阵列的移位寄存器被菊花式链接的。

63.本发明的一方面的优点是,它简化了发光阵列如在平铺式显示器中的平铺。具体而言,不需要修改或需要很少修改电路系统来控制这些阵列。

64.在本发明的另一方面中,一种驱动发光元件的控制电路的方法涉及以下步骤:

65.将控制信号从第二存储元件传输到第一存储元件

66.根据所述控制信号来控制发光元件中的电流,从而控制信号被存储在第一存储元件上

67.当发光元件中的电流由先前的控制信号控制时,向第二存储元件加载另一控制信号。

68.在本发明的另一方面中,提供了一种用于根据n1位 n2位来调制发光元件中的电流的方法,其中n2位具有比n1位更小的权重;该方法包括以下步骤:

69.对于n1位中的每一个位,发光元件中的电流由所述n1位控制,一次一个位且在持续时间至少为t

min

的时间区间内;

70.对于n2位中的每一个位,发光元件中的电流由所述n2位控制,一次一个位且在小于t

min

的第一时间区间内,并在小于t

min

的第二时间区间内覆盖所述n2位中的所述一个位,第一时间区间与第二时间区间的持续时间的总和等于t

min

。

71.本发明的该方面的优点是,可以在不必修改持续时间t

min

的情况下修改(且尤其是增加)位的总数n=n1 n2。n1 n2位可以对发光元件中的电流振幅进行编码。

72.例如,可以对电流进行脉宽调制,在这种情况下,n1 n2位可以对pwm信号的占空比进行编码,该占空比将确定pwm信号的周期t期间的电流平均值。

73.占空比可以用n=n1 n2位进行编码,其中n1≥1且n2≥0。为了限制位码(即,由位n1 n2表示的整数)和在发光元件(诸如发光二极管)中循环的平均电流之间的非线性度或误差,n2优选地小于n1,平均值是在pwm信号的周期t上计算得到的。

74.时间区间的持续时间t

min

可以是与n1位中权重最小的位的pwm子周期相对应的当前脉冲的持续时间(在pwm周期内)。整个位序列可以在等于(2

n1-1)*t

min

n2*t

min

的时间区间期间控制电流,之后发光元件中的电流可以由另一位序列来控制/确定。

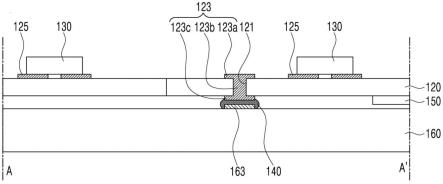

75.本发明的优点是,它可限制向发光元件阵列中的发光元件及其电流控制电路传送信号的电轨道的数量。

76.各个位可例如移位通过发光元件的c列和l行阵列中的列宽或行宽移位寄存器。将位从移位寄存器的输入端移位到其末端所需的时间可以确定时间区间t

min

。

附图说明

77.本发明的实施例的这些以及其他技术方面和优点现在将参考附图更详细地描述,其中:

78.图1示出了根据本领域的有源矩阵像素驱动电路的示意图,其中pwm信号被用于调光。

79.图2示出了根据本领域的有源矩阵像素驱动器的示意图,其中在连贯的pwm定时时段期间,pwm是逐位地施加的,对pwm信号进行编码的各个位被存储在串行存储器中。

80.图3示出了根据本领域的有源矩阵led阵列。

81.图4示出了可与脉宽调制一起使用的矩形脉冲波的示例。矩形脉冲波的脉宽被调制,从而造成波形的平均值的变化。

82.图5示出了一个周期t如何被拆分成跨一个周期分布的4个子脉冲sp1、sp2、sp3和

sp4。取决于应用,将一个周期分成多于4个区间可以是合需的。

83.图6示出了占空比设置成其最小值t

cl

/t时的脉宽调制信号。

84.图7示出了在占空比比相比于图6进一步增加(例如增加3t

cl

/t)的情况下,脉冲p可以如何被拆分成两个或更多个子脉冲,每一子脉冲发生在周期t被拆分的区间(或位块)之一中。

85.图8示出了用4位b0、b1、b2和b3(b0是lsb,而b3是msb)编码的pwm占空比的pwm子周期的示例。在该示例中,pwm信号的周期t已被拆分成四个子周期或四个pwm时间区间t0、t1、t2、t3,使得t=t0 t1 t2 t3。

86.图9和图10示出了pwm时间段可被如何拆分,而不是不间断的。

87.图9示出了在4位上编码的pwm信号的示例,其中b0=0、b1=0、b2=0且b3=1,并且b3的时间段是不间断的。b3的时间段是位b0的时间段t0的8倍。

88.图10示出了在4位上编码的pwm信号的示例,其中b0=0、b1=0、b2=0且b3=1,并且b3的时间段是跨pwm周期t尽可能均匀地拆分的。脉冲b3已被拆分成8个子脉冲b

31

、b

32

、b

33

、b

34

、b

35

、b

36

、b

37

和b

38

。每一子脉冲的持续时间t0等于位b0的持续时间,并且各子脉冲的持续时间之和等于持续时间t3=t0*23。

89.图11示出了在4位上编码的pwm信号的示例,其中b0=1、b1=0、b2=0且b3=1,并且b0和b3的时间段是跨pwm周期t尽可能均匀地拆分和分布的。

90.图12示出了编码在4位上的pwm信号,其中b0=1、b1=0、b2=0且b3=1,具有子脉冲b

31

、b

32

、b

33

、b

34

、b

35

、b

36

、b

37

和b

38

以及b0的不同分布。

91.占空比d对于图11和图12而言是相同的。

92.图13示出了在给定时刻驱动led的启用信号es(表1中的di)和在给定时刻被存储并在下一位块期间将驱动led的所存储信号ss(表1中的pi)。

93.图14a示出了根据本发明的实施例的电流控制电路的示例。

94.图14b示出了图14a的电路的节点处的信号随时间变化的状态。

95.图14c示出了根据本发明的实施例的电流控制电路的另一示例。

96.图15示出了根据本发明的一实施例的、相邻电流控制电路的第二存储元件如何被菊花式链接以形成移位寄存器。

97.图16示出了根据本发明的实施例的、在诸如oled或led之类的固态光源根据先前存储在每一像素或子像素的存储元件中的位中所编码的信息来发光时,如何发送和存储各个位。

98.图17示出了与电容器c

sh

17并联连接的复位开关,根据本发明的一实施例,该开关在时间区间t0结束之前闭合。

99.图18示出了根据本发明的一实施例的可如何使用rst信号来实现更高的位深。

100.图19示出了根据本发明的实施例的(其中n1=4且n2=2)复位信号rst如何随时间和pwm子周期(对于每一位bi)变化的示例。

101.图20示出了如何解决连接不同基板的问题的本发明实施例。

102.图21示出了如何将数据上传到有源显示器。

103.图22示出了根据本发明的实施例的控制元件1434(例如晶体管)的替换布置。

104.图23示出了根据本发明的实施例的复位元件rst(例如晶体管)的替换布置。

105.图24示出了根据本发明的另一实施例的基于图14a的电流控制电路的复制的多位(两位)电路。

106.图25示出了根据本发明的又一实施例的基于图14c的电流控制电路的复制的多位(两位)电路。

107.图26和27示出了根据本发明的又一实施例的基于图14c中的电流控制电路的复制的经修改形式的多位(两位)电流控制或驱动电路。

108.定义和首字母缩略词

109.有源矩阵。有源矩阵是一种用在平板显示器中的寻址方案。在对各个体元件(像素)进行开关的该方法中,每一像素附连到在其他像素被寻址时主动地维持像素状态的开关,诸如晶体管和电容器。图1给出了有源矩阵中的像素的示意性示例。

110.有源矩阵电路通常由形成在显示基板上的半导体层中的薄膜晶体管(tft)构成,并使用分开的tft电路来控制显示器中的每一发光像素。半导体层通常是非晶硅或多晶硅,并且分布在整个平板显示基板上。图3解说了有源矩阵的示意性表示。有源矩阵显示器也可以是例如lcd或电泳反射透射发射显示器或类似显示器。

111.显示子像素可以由一个控制元件控制,并且每一控制元件包括至少一个晶体管。例如,在简单的有源矩阵发光二极管显示器中,每一控制元件包括两个晶体管(选择晶体管和功率晶体管)和用于存储指定子像素亮度的电荷的一个电容器。每一led元件采用连接到功率晶体管和公共电极的独立控制电极。本领域已知的有源矩阵中的发光元件的控制通常通过数据信号线、选择信号线、电力或供电连接(称为例如vdd)和接地连接来提供。

112.临界闪烁频率。对比度最大时出现闪烁的最高可能频率是临界闪烁频率(或cff)。临界闪烁频率是若干因素的函数,例如亮度。对于人类而言,亮度越低,他们对闪烁越不敏感。

113.占空比。占空比是信号或系统激活的一个周期的分数。占空比通常表示为百分比或比率。因此,60%的占空比意味着信号在60%的时间处于打开状态,但在40%的时间处于关闭状态。在pwm电流控制电路中,占空比可以表示电流流入例如发光元件的时间的分数。

114.闪烁。闪烁是指在两个连贯帧或更一般的周期(例如,pwm信号的两个连贯周期)之间,亮度的可见衰减或降低。

115.可编程存储器,诸如触发器。

116.本发明的实施例利用存储元件,例如一位可编程存储器,诸如触发器或具有选择线的晶体管或电容器,例如采样保持装置或多位存储器。在一些实施例中,可编程存储器可以被时钟计时。

117.本发明的实施例可与用于驱动显示器(例如有源显示器)的像素和/或子像素的pwm方案一起使用。可使用一位可编程存储器元件,诸如触发器(例如时钟控制触发器)或者电容器或电容电路(诸如采样保持电容器)。多位可编程存储器可以由一位或多位存储器的倍数提供。

118.时钟控制可编程存储器的真值表的示例是:

119.[0120][0121]“x”表示不关心条件,从而意味着该信号是不相关的,或

[0122]

具有如下真值表的可编程存储器:

[0123][0124]

这些是具有nand和nor端口的存储器。触发器是可编程存储器元件。触发器可以是时钟控制或无时钟控制的,例如时钟控制或无时钟控制的可编程元件。对于无时钟控制可编程元件或无时钟触发器,输出直接与输入起反应。对于时钟控制可编程元件或有时钟触发器,输入仅在定时脉冲或脉冲的一部分之后才传输到输出。

[0125]

具体而言,d触发器如下所示。

[0126][0127]

d触发器符号

[0128]

d触发器被广泛使用。它也被称为“数据”或“延迟”触发器。

[0129]

d触发器在时钟周期的特定部分(诸如时钟的上升沿)处捕获d输入端的值。所捕获的值成为q输出。在其他时间,输出q不变。d触发器可以看作是存储器单元。具体而言,d触发器可以是可编程存储器元件。d触发器可以是时钟控制可编程存储器元件。

[0130]

d触发器或用作d触发器的任何可编程存储器元件的真值表如下所示:

[0131]

时钟dq

next

上升沿00上升沿11非上升xq

[0132]“x”表示不关心条件,从而意味着该信号是不相关的。

[0133]

大多数d型触发器(例如集成电路中的)都具有强制进入设置或复位状态(这忽略d和时钟输入)的能力,与sr触发器非常相似。在触发器被用作存储器元件的实施例中,可以使用时钟控制d-ff、jk-ff和sr-ff。本发明的实施例可以利用带触发器的时钟控制移位寄存器。

[0134]

通常,非法的s=r=1条件在d型触发器中解决。通过设置s=r=0,触发器可以如上所述使用。

[0135]

在此是其他s和r可能配置的真值表。

[0136][0137]

在本技术中,如果b被用作qb中的b,则b表示反相输出。

[0138]

fpga。现场可编程门阵列。一种电子器件,可被用于生成操作显示器(尤其是led矩阵显示器)所需的信号。例如,fpga可被用作控制器。关于fpga如何被用在led显示器中的示例可在例如us7450085b2“intelligent lighting module and method of operation of such an intelligent lighting module(智能照明模块和此类智能照明模块的操作方法)”中找到。

[0139]

fps或fps。每秒帧数。led显示器或led显示器平铺片上每秒显示的帧数。每秒帧数或fps是衡量显示设备性能的单位。它包括每秒发生的显示屏的完整扫描数。这是屏幕上的图像每秒刷新的次数,或成像设备产生称为帧的唯一性序列图像的速率。

[0140]

帧。帧是一个图片,例如制作一系列电影或动画电影或视频的一系列图片中的一个图片。它也可以表示要显示的完整图像(如在显示器上或平铺式显示器的平铺片上)。在某些上下文中,帧也可以表示显示帧的时间区间。这更好地被描述为“帧时间”,通常是1/60秒。

[0141]

薄膜技术是指薄膜的使用:在玻璃、陶瓷或半导体基板上沉积几个分子厚的薄膜,以形成电容器、电阻器、线圈、低温管或其他电路元件。沉积在固态基板(诸如玻璃或陶瓷)或作为支撑液体上的一个到几百分子厚的材料膜。

[0142]

薄膜集成电路:完全由以图案化关系沉积在基板上的薄膜组成的集成电路。基板不必是半导体,而更常用的是玻璃、石英、金刚石或聚酰亚胺。

[0143]

薄膜晶体管:完全由薄膜技术构造的场效应晶体管,用于薄膜电路。缩写是tft。

[0144]

[0145]

[0146][0147]

led。发光二极管。

[0148]

oled。有机发光二极管。

[0149]

led显示器。

[0150]

来自同一申请人的以下专利申请提供了led显示器和相关术语的定义。对于这些术语的定义,在此通过引用将其纳入于此。

[0151]

us7972032b2“led assembly(led组装件)”。

[0152]

us7176861b2“pixel structure with optimized subpixel sizes for emissive displays(用于发射性显示器的具有优化子像素大小的像素结构)”[0153]

us7450085“intelligent lighting module and method of operation of such an intelligent lighting module(智能发光模块和此类智能发光模块的操作的方法)”。

[0154]

us7071894“method of and device for displaying images on a display device(用于在显示设备上显示图像的方法和设备)”。

[0155]

lsb。最低有效位。如果一个数字用例如四位来编码,使得数字=b0 b1*2 b2*22 b3*23,则b0是lsb或最低有效位。

[0156]

亮度(l)。在给定方向上投影的每单位面积的发亮强度。si单元是每平方米坎德拉,有时还称为尼特。在文献中,亮度(luminance)和明度(brightness)通常互换地使用,即使亮度和明度不是同一个和同一事物。在此,每当使用“明度”时,发明人意指“亮度”。

[0157]

msb。最高有效位。如果一个数字用例如四位来编码,使得数字=b0 b1*2 b2*22 b3*23,则b3是msb或最高有效位。msb也可以被用于一个以上的位,例如四个位b0、b1、b2和b3可以拆分成两组。前两位b0和b1可以被称为四位组中的最低有效位。后两位b2和b3可以被称为四位组中的最高有效位。

[0158]

节距。像素(或子像素)阵列中两个相邻像素(或相同颜色的子像素)的中心之间的距离。也称为像素(或子像素)阵列的空间周期。

[0159]

像素。被用于渲染图片元素的一个或多个光源。像素可以是图像的单位=图片元素。它可以是显示器的物理结构,其取决于上下文而发光。像素可包括子像素。一个或多个

子像素可以发射一种颜色的光。子像素可被个体地寻址。

[0160]

pmos。有时称为pmosfet;p型金属氧化物半导体场效应晶体管。

[0161]

发光元件。发光元件可以是例如固态发光元件,诸如发光二极管,诸如led或oled(有机led)。

[0162]

pwm(脉宽调制)。

[0163]

脉宽调制(pwm)方案通过改变向发光元件(诸如发光二极管)提供恒定电流的时间来控制亮度。脉宽调制使用矩形脉冲波,其脉宽被调制,从而造成波形的平均值的变化。图4示出了此类矩形脉冲波的示例。

[0164]

pwm方案的控制信号具有位深。这在数字系统中是最常见的情况。从单个脉冲开始,并且脉宽要由数字系统来控制,脉宽将遵循二进制模式。位数越多,脉宽将越精确。在本发明的实施例中,单个脉冲可以在一个帧上按时间拆分。这一拆分可以按二进制方式完成。控制系统的位数越多,pwm脉冲越小,并且能越精确地显示值。

[0165]

方波具有周期t、下限i0(通常,i0=0)、上限i1和占空比d。脉冲p的持续时间(信号处于其上限i1的时间)是d/100*t(如果d以%表示)。例如,如果d=50%,则脉冲持续时间是1/2t。

[0166]

在一些情形中,脉冲p的形状如在图5所示地修改。如果周期t“长”或与重要物理过程的时间常数具有相同数量级,则将脉冲“拆分”成分布在波的一个周期中的多个子脉冲(sp)可以是有利的。在图5中,一个周期t已被分成跨一个周期分布的4个子脉冲sp1、sp2、sp3和sp4。取决于应用,将一个周期分成多于4个区间可以是合需的。

[0167]

在数字系统中,脉冲的持续时间是时钟周期t

cl

的倍数。对于给定t和t

cl

而言,可达到的最小占空比因而是t

cl

/t。如将进一步描述的,pwm周期可拆分成所谓的位块,每一位块具有相同的持续时间t0,其可等于或大于参考时钟周期t

cl

。

[0168]

如果占空比被设置在其最小值t

cl

/t,则脉宽调制信号将在图6上看到。如果占空比进一步增加例如3t

cl

/t,则脉冲p可被拆分出两个或更多个子脉冲,每一子脉冲占据周期t所被分成的区间(或位块)之一,如在图7上解说的。

[0169]

随着占空比进一步增加,区间中的每一者被填充,使得子脉冲的持续时间的总和等于d*t。

[0170]

i0=0时,由pwm信号驱动的发光元件(诸如发光二极管)中循环的平均电流《i》是:

[0171]

《i》=i1*d/100(其中d是以%来表示的)或

[0172]

《i》=i1*d(其中d是以t的分数来表示的,作为区间[0,1]中的实数)

[0173]

在led或其他类型的固定格式显示器中,诸帧以例如60hz的频率(对应于t=1/60s)来被显示。在led是用pwm信号驱动时,将脉冲拆分成诸子脉冲可降低可见闪烁(考虑到低于临界闪烁频率或cff的任何事物可被看到)。将脉冲拆分成多个子脉冲可被视为将频率增加多达n倍,其中n是周期被拆分成的区间数)。

[0174]

即使在这些情形中,电流的波形也可能不严格是通常所知的pwm信号的波形(例如,在图4上),但在讨论led电流驱动方案时将参考pwm。

[0175]

或者,代替将周期t拆分成相等持续时间的位块,pwm信号的每一周期t可被拆分成多个不同的pwm子周期,这些子周期在不同的时间顺序地提供。每一pwm子周期具有与多位数字像素值的不同位相对应的不同时长(提供经加权pwm信号)。图8示出了用4位b0、b1、b2

和b3(b0是lsb,而b3是msb)编码的pwm占空比的pwm子周期的示例。在该示例中,pwm信号的周期t已被拆分成四个子周期或四个pwm时间区间t0、t1、t2、t3,使得t=t0 t1 t2 t3。

[0176]

当多位数字像素值的对应位在逻辑上接通(on)时,可将诸如发光二极管之类的发光元件控制成开启(即,振幅为i

max

的电流流过发光元件)达给定的pwm时间段,并且当多位数字像素值的对应位在逻辑上关闭(off)时,可将led控制成关闭达给定的pwm时间段,使得输出量由诸接通pwm时间段的时间持续时间的总和与整个pwm定时信号的时间持续时间的比率d来指定。

[0177]

对于4位位深,占空比d是:

[0178]

d=(b

0 t0 b

1 t1 b

2 t2 b

3 t3)/t

[0179]

具体而言,pwm经加权区间可以使得ti=t

0 2i且d随后由下式给出:

[0180]

d=(b

0 t0 b

1 t0*2 b

2 t0*4 b

3 t0*8)/t

[0181]

例如,如果b0=0,b1=0,b2=0且b3=1;则d=(0*t0 0*t0*2 0*t0*22 1*t0*23)=8t0/t=8t0/(15t0)=8/15。

[0182]

整个pwm定时信号优选地能够以足够的速率切换,并且具有足够小的时间持续时间以避免可感知的闪烁。在某些情况下,pwm周期t和帧周期(帧的持续时间)可以相等。在其他情况下,帧的持续时间可以长于pwm周期t,并且具体而言,帧的持续时间可以是pwm周期t的倍数。在进一步开发的实施例的示例中,出于附图简明起见,可以将pwm周期和帧周期取为相等。

[0183]

pwm时间周期可被拆分,而不是不间断的。

[0184]

拆分整个pwm周期t的、持续时间是t0的诸连贯区间可以称为位块。取决于上下文,“位块”将指一个这样的时间区间,或指该时间区间内位的逻辑值(1或0、高或低、h或l)。

具体实施方式

[0185]

将就具体实施例并且参考某些附图来描述本发明,但是本发明不限于此而仅由权利要求书来限定。所描述的附图仅是示意性的而非限制性的。在附图中,出于说明性目的,要素中的一些要素的尺寸可被放大且未按比例绘制。在本说明书和权利要求书中使用术语“包括”时,该术语不排除其他元件或步骤。此外,说明书和权利要求书中的术语第一、第二、第三等被用于在类似元素之间进行区分,而不一定用于描述顺序或时间次序。应理解,如此使用的术语在适当的情况下是可互换的,并且本文中所描述的本发明的实施例能够以与本文中所描述或图示的不同的顺序来进行操作。

[0186]

脉宽调制

[0187]

本发明的实施例使用诸如脉宽调制(pwm)方案之类的控制方案来驱动像素或子像素。脉宽调制(pwm)通过改变向发光元件(诸如发光二极管,oled和led是其两个示例)提供恒定电流的时间来控制亮度。脉宽调制使用矩形脉冲波,其脉宽被调制,从而造成波形的平均值的变化。图4示出了此类矩形脉冲波的示例。

[0188]

方波具有周期t、下限i0(通常,i0=0)、上限i1和占空比d。脉冲p的持续时间(即,信号处于其上限i1的时间)是d/100*t(如果d以%表示)。例如,如果d=50%,则脉冲持续时间是1/2t。

[0189]

在一些情形中,脉冲p的形状如在图5所示地修改。如果周期t“长”或与重要物理过

程的时间常数具有相同数量级,则将脉冲“拆分”成分布在波的一个周期中的多个子脉冲(sp)可以是有利的。在图5中,一个周期t已被分成跨一个周期分布的4个子脉冲sp1、sp2、sp3和sp4。取决于应用,将一个周期分成多于或少于4个区间可以是合需的。

[0190]

在数字系统中,脉冲的历时是时钟周期t

cl

的倍数。对于给定t和t

cl

而言,可达到的最小占空比因而是t

cl

/t。如将进一步描述的,pwm周期可拆分成所谓的位块,每一位块具有相同的持续时间t0,其可等于或大于参考时钟周期t

cl

。

[0191]

如果占空比被设置在其最小值t

cl

/t,则脉宽调制信号将在图6上看到。如果占空比进一步增加例如3t

cl

/t,则脉冲p可被拆分出两个或更多个子脉冲,每一子脉冲占据周期t所被分成的区间(或位块)之一,如在图7上解说的。

[0192]

随着占空比进一步增加,区间中的每一者被填充,使得子脉冲的持续时间的总和等于d*t。

[0193]

i0=0时,由pwm信号驱动的发光元件(诸如发光二极管)中循环的平均电流《i》是:

[0194]

《i》=i1*d/100(其中d是以%来表示的)或

[0195]

《i》=i1*d(其中d是以t的分数来表示的,作为区间[0,1]中的实数)

[0196]

在例如可以与本发明实施例一起使用的类型的诸如led或oled显示器之类的固态显示器中,帧以例如60hz的频率显示,该频率对应于t=1/60s。当诸如oled或led之类的固态光源用pwm信号驱动时,将脉冲拆分成子脉冲可以减少可见闪烁。例如,认为可以看到低于临界闪烁频率或cff的任何事物。将脉冲拆分成多个子脉冲可被视为将频率增加多达n倍,其中n是周期被拆分成的区间数)。

[0197]

即使在这些情形中,电流的波形也可能不严格是通常所知的pwm信号的波形(例如,在图4上),但在本技术中,在讨论根据本发明的实施例的诸如led或oled之类的固态光源电流驱动方案中的任一者将参考pwm。

[0198]

或者,代替将周期t拆分成相等持续时间的位块,pwm信号的每一周期t可被拆分成多个不同的pwm子周期,这些子周期在不同的时间顺序地提供。每一pwm子周期具有与多位数字像素值的不同位相对应的不同时长(提供经加权pwm信号)。图8示出了用4位b0、b1、b2和b3(b0是lsb,而b3是msb)编码的pwm占空比的pwm子周期的示例。在该示例中,pwm信号的周期t已被拆分成四个子周期或四个pwm时间区间t0、t1、t2、t3,使得t=t0 t1 t2 t3。

[0199]

当多位数字像素值的对应位在逻辑上接通(on)时,将诸如发光二极管之类的发光元件控制成开启(即,振幅为i

max

的电流流过发光元件)达给定的pwm时间段,并且当多位数字像素值的对应位在逻辑上关闭(off)时,将led控制成关闭达给定的pwm时间段,使得输出量由诸接通pwm时间段的时间持续时间的总和与整个pwm定时信号的时间持续时间的比率d来指定。

[0200]

对于4位位深,占空比d是:

[0201]

d=(b

0 t0 b

1 t1 b

2 t2 b

3 t3)/t

[0202]

具体而言,pwm经加权区间可以使得ti=t

0 2i且d随后由下式给出:

[0203]

d=(b

0 t0 b

1 t0*2 b

2 t0*4 b

3 t0*8)/t

[0204]

在图9的示例中,对于b0=0,b1=0,b2=0且b3=1;则d=(0*t0 0*t0*2 0*t0*22 1*t0*23)=8t0/t=8t0/(15t0)=8/15。

[0205]

整个pwm定时信号优选地能够以足够的速率切换,并且具有足够小的时间持续时

间以避免可感知的闪烁。在某些情况下,pwm周期t和帧周期(帧的持续时间)可以相等。在其他情况下,帧的持续时间可以长于pwm周期t,并且具体而言,帧的持续时间可以是pwm周期t的倍数。在进一步开发的实施例的示例中,出于附图简明起见,可以将pwm周期和帧周期取为相等。

[0206]

如先前提及的,pwm时间周期可被拆分,而不是不间断的。这在图9和10中解说。

[0207]

图9示出了在4位上编码的pwm信号的示例,其中b0=0、b1=0、b2=0且b3=1,并且b3的时间段是不间断的。b3的时间段是位b0的时间段t0的8倍。

[0208]

图10示出了在4位上编码的pwm信号的示例,其中b0=0、b1=0、b2=0且b3=1,并且b3的时间段是跨pwm周期t尽可能平均地拆分的。脉冲b3已被拆分成8个子脉冲b

31

、b

32

、b

33

、b

34

、b

35

、b

36

、b

37

和b

38

。每一子脉冲的持续时间t0等于位b0的持续时间,并且各子脉冲的持续时间之和等于持续时间t3=t0*23。

[0209]

图11示出了在4位上编码的pwm信号的示例,其中b0=1、b1=0、b2=0且b3=1,并且b0和b3的时间段是跨pwm周期t尽可能均匀地拆分和分布的。

[0210]

图12示出了编码在4位上的pwm信号,其中b0=1、b1=0、b2=0且b3=1,具有子脉冲b

31

、b

32

、b

33

、b

34

、b

35

、b

36

、b

37

和b

38

以及b0的不同分布。

[0211]

占空比d对于图11和12而言是相同的。

[0212]

拆分整个pwm周期t的、持续时间是t0的诸连贯区间可以称为位块。取决于上下文,“位块”将指一个这样的时间区间,或指该时间区间内位的逻辑值(1或0、高或低、h或l)。

[0213]

根据本发明的实施例,可以逐位地(例如,在图9的示例中)或逐位块(例如,在图10、11和12的示例中)使用pwm信号来驱动固态光源,诸如led或oled。为了保持有源像素的大小足够小以便用薄膜晶体管实现,并且不显著降低分辨率,与每一像素或子像素相关联的存储器存储的位数少于经编码的pwm信号的位深。例如,如果位深是12,则与每一像素或子像素相关联的存储器可以一次存储例如2个位或单个位。与现有技术中公开的内容相反,在位块b

i,j

已经用于驱动像素或子像素时,优选地将在下一位块b

i,j 1

期间必须应用的位的值存储在存储器中,并且存储器以定期区间t0更新(t0是位块的持续时间)。另选地,存储器存储在下一pwm子周期期间必须应用的位bi的值,并且存储器以不同的时间区间更新,每一时间区间的持续时间是位bi的权重的函数(如图8的示例所示)。

[0214]

这在下表1且在图13中示出。

[0215]

表1示出了在给定时间区间或位块期间驱动led的信号di和存储在存储器元件中并将在下一时间区间或位块期间驱动led的信号pi 1。

[0216]

表1

[0217]

显示 d0d1d2d3d4d5...d59d60d61d62d63程序p0p1p2p3p4p5p6...p60p61p62p63 [0218]

图13示出了在给定时刻驱动led的启用信号es(表1中的di)和在给定时刻被存储并在下一位块期间将驱动led的所存储信号ss(表1中的pi)。

[0219]

其他实施例

[0220]

在以下对本发明实施例的描述中,每当b是被用在qb中时,这意味着逆变输出。

[0221]

根据本发明实施例的驱动电路或电流控制电路153可包括:

[0222]

具有第一控制电极的控制元件,用于控制流过发光元件的电流;

[0223]

用于存储控制信号的第一值的第一存储元件,所述控制信号被施加到控制元件的第一控制电极;

[0224]

用于存储控制信号的第二值的第二存储元件;

[0225]

传输元件,具有用于将控制信号的第二值加载到第一存储元件的第二控制电极。

[0226]

对于组件的定义,请参见上面的定义部分。

[0227]

控制元件、第一存储元件、第二存储元件和传输元件有利地利用相同的薄膜晶体管技术实现。

[0228]

利用根据本发明实施例的电路,在第一存储元件向控制元件的控制电极施加第一控制信号(电压)以控制发光元件中的电流的同时,在第二存储元件上加载第二控制信号(例如电压)是可能的。因此,不存在因无数据可供用于控制而导致发光元件保持空闲的“停滞时间”。

[0229]

在图14a所示电路的描述中:

[0230]

控制元件可以是晶体管143,且第一控制电极可以是晶体管143的栅极1433。晶体管可以是pmos晶体管,例如薄膜晶体管。控制元件连接到led或oled二极管发光元件146以提供对其的控制。晶体管可在操作上与诸如led或oled之类的光源连接,并且在操作上与电流源145连接。

[0231]

第一存储元件可以是电容器或电容电路,诸如采样保持装置,例如包括采样保持电容器144或其他立即呈现其值的存储元件,诸如无时钟控制触发器。第一存储元件(诸如举例而言采样保持电容器144的电容器)连接在栅极1433和供电电压vdd之间。它还可以连接在栅极1433和电流源145的输出端之间。

[0232]

第二存储元件可以是可编程存储器,诸如一位、二位或多位存储器,诸如可以由触发器141提供。第二存储元件可以是时钟控制的。可存储在第二存储元件上的位数应小于控制信号(诸如pwm信号)的位深;以及

[0233]

传输元件可以是晶体管142。晶体管142在一侧连接到第二存储元件141,并在另一侧连接到栅极1433。传输元件142的栅极被连接以接收enb信号。传输元件142将值(或电压)从第二存储传输到第一存储元件。

[0234]

图14a(控制信号)中的数据信号被菊花式链接的。因此,控制信号上的每一时钟周期都有一个位去往下一个一位存储器,诸如触发器。第一和第二存储仅捕获朝向发光元件146的控制信号的一位。

[0235]

图14a示出了根据本发明实施例的用于驱动固态光源146的像素或子像素的控制电路或驱动电路152的示例。

[0236]

pwm诸位可以一次一位地存储在第二存储元件中,诸如在一位存储器单元中,例如在d触发器141或具有两位存储器或多位存储器的可编程器件中,如可由多个触发器提供,前提是存储器的位数小于控制信号(诸如pwm信号)的位深。第二存储元件可以是时钟控制的。诸如触发器141之类的第二存储元件具有输入(d)和输出。第二存储元件(诸如触发器141)是一位存储器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深,像素阵列的同一列c或同一行r中的相邻像素可以被菊花式链接(如图15所示)。这一菊花链配置限制了控制阵列的每一像素或子像素本来所需的单独磁道的数量。

[0237]

当使用(来自第一存储元件)先前存储的值启用发光器件146时,一值可被捕获到

一位存储器中,例如触发器141(在本实施例中是第二存储元件)。一值可以在不干扰正在显示的值的情况下被存储。因此,在图14a中,可以在不中断图像显示的情况下更新诸如触发器141之类的一位存储器的输出。

[0238]

由时钟信号(clk)更新第二存储元件(诸如触发器141或两位存储器或多位存储器)的输出q,前提是存储器的位数小于控制信号(诸如pwm信号)的位深。作为传输元件的晶体管142被用作开关,其在闭合时将第二存储元件(诸如触发器141是一位存储器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出端连接到控制元件(诸如晶体管143)的栅极1433和第一存储元件(诸如电容器c

sh 144或电容电路(诸如具有电容器c

sh 144或无时钟控制触发器的采样保持电路))的电极。晶体管142和晶体管143可以是诸如pmos晶体管之类的薄膜晶体管。

[0239]

诸如晶体管142之类的传输元件由启用信号(en或enb)控制。在图14a的示例中,传输元件(诸如晶体管142)是pmos晶体管,当启用信号为低(例如,gnd)时,其将可编程存储器元件(诸如触发器141或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出qb(也可记为q或如图14a所示)连接至诸如晶体管143之类的控制元件的栅极1433。同时,第一存储元件(诸如电容器c

sh 144)或电容电路或无时钟控制触发器,其第一电极连接至晶体管143的栅极1433,第二电极连接至例如供电电压vdd)对可编程存储器元件(诸如触发器141或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出处的电压v

out

进行采样,并且即使在诸如开关或晶体管开关142之类的传输元件打开时,也将保持诸如晶体管143之类的控制元件的栅极1433处于相同的电压。

[0240]

诸如晶体管143之类的控制元件可被用作开关。当闭合时,用作开关143的晶体管将电流源145与发光元件(诸如发光二极管,例如led或oled 146)连接,该发光元件可以发光。当开关143打开时,没有电流流过诸如led或oled 146之类的发光元件,并且它不发光。

[0241]

如图14a的示例所示,如果诸如晶体管143之类的控制元件是pmos晶体管,则只要存储器的位数小于诸如pwm信号之类的控制信号的位深,则它可以连接到触发器141或两位存储器或多位存储器的反相输出qb,而不是连接到输出q。实际上,如果pmos晶体管被用于开关143,则“低”信号(例如,gnd电压)将闭合该开关,并允许电流源145的电流流过发光二极管146,诸如oled或led。这意味着当位bi,j为“高”时,即当位bi,j等于“1”时,发光元件146(诸如led或oled)在开关(如晶体管142)闭合时发光,并且当位bi,j为“低”时,即当位bi,j等于“0”(且输出qb处的bi,j为高)时,当诸如开关142之类的传输元件闭合并且bi,j的值由第一存储元件保持(例如由诸如电容器144之类的采样和保持装置采样和保持)时,诸如led或oled146之类的发光元件146不发光。

[0242]

一旦包括可编程存储器元件(诸如触发器141)的第二存储元件的输出已经施加到第一存储元件,例如已被采样并存储在采样保持装置(诸如电容器144)上,则可以打开诸如开关142之类的传输元件,并且可以将下一位存储在第二存储元件(例如触发器141或两位存储器或多位存储器之类的存储元件)中,前提是存储器的位数小于诸如pwm信号之类的控制信号的位深。

[0243]

本发明的该方面的优点是,则可以在不中断图像显示的情况下更新存储在第二存储器元件(诸如触发器141或两位存储器或多位存储器,前提是存储器的位数小于控制信号

(诸如pwm信号)的位深)中的位。

[0244]

图14b示出了图14a所示电路各个节点处的信号序列。高状态(h)对应于二进制值1。低状态(l)对应于二进制值0。“不关心”状态意味着二进制值可以是1或0。

[0245]

在时间t0,数据信号(例如位b0)呈现在触发器141(或者两位存储器或多位存储器,前提是存储器的位数小于诸如pwm信号之类的控制信号的位深)的输入端。在图14b的示例中,b0=1。在时钟信号clk的上升沿处,触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出q被更新以使得q=b0,同时触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出qb被更新以使得qb=b0(b0的逻辑逆)。

[0246]

在时间t1》t0,触发器141(或者两位存储器或多位存储器,前提是存储器的位数小于诸如pwm信号之类的控制信号的位深)的输出被连接到第一存储元件,诸如电容器或电容电路(诸如具有采样和保持电容器144的采样和保持装置或无时钟控制触发器是其示例)。这通过闭合诸如开关晶体管142之类的开关来完成,该开关将触发器141(或者两位存储器或多位存储器,前提是存储器的位数小于诸如pwm信号之类的控制信号的位深)的输出与第一存储元件相连接,诸如电容器或电容电路(诸如具有采样和保持电容器144(c

sh

)的采样和保持装置或无时钟控制触发器是其示例)。如果诸如开关晶体管142之类的开关是pmos晶体管,则通过将启用信号enb强制至低状态(例如接地)来将它闭合,如图14b所示。启用信号enb保持为低,直到时间t3》t2,其中δt=t

3-t2的长度足以保证第一存储元件144的正确充电或加载。

[0247]

在第一存储元件(诸如电容器或具有采样保持电容器144或无时钟控制触发器的采样保持装置)上存储的任何电压是根据存储在第二存储元件(诸如一位存储器触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深))上的信号(在这种情况下,是输出qb处的电压)来被“擦除”和更新的。在图14b的示例中,b0=1、qb=0且vg=0(其中vg是施加到控制元件143(例如晶体管)的控制电极1433(例如栅极)的电压)。当vg=0(例如gnd)时,控制元件143(例如晶体管)将电流源145与发光二极管(诸如led或oled146)相连接,并且在led或oled146中循环的电流是i

max

。

[0248]

经更新的信号被施加到控制元件143(诸如晶体管)的控制电极1433达时间t

hold

。t

hold

可以是位块的持续时间。t

hold

也可以是pwm子周期(t0、t1、t2、t3……

,如图9所示)的持续时间。

[0249]

在t

hold

结束之前;例如在时间t4》t3;新数据信号(例如b1)可以呈现在触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输入端,并且一位存储器触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出qb在时钟信号clk的上升沿被更新。在图14b的示例中,b1=1,其中b1在b0之后。

[0250]

与b0的情况一样,存储在第二存储元件141(诸如在触发器或两位存储器或多位存储器上,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)上的位可以通过闭合传输元件142(诸如晶体管)来盖写存储在第一存储元件144(诸如电容器或电容电路(诸如采样保持装置,例如具有采样保持电容器或无时钟控制触发器))上的数据。在图14b上,这发生在时间t5》t4,其中enb信号设置成低,这导致信号vg设置成高。诸如晶体管之类的控制元

件143被打开,从而从诸如led或oled 146之类的发光二极管断开电流源145。电流iled被设置成i

min

。

[0251]

对于每一数据信号(即,如果使用诸位块),t

hold

可具有相同的持续时间。另选地,t

hold

的持续时间可以根据数据信号(特别是根据存储在第一存储元件144上的位的权重)而变化,第一存储元件144诸如是电容器或电容电路,诸如采样保持装置或采样保持电容器或无时钟控制触发器。

[0252]

图14c示出了根据本发明的像素的替换实现。

[0253]

对于图14c所示的电路:

[0254]

控制元件例如是晶体管143,并且第一控制电极1433例如是晶体管143的栅极;晶体管可以是pmos晶体管,例如薄膜晶体管。控制元件连接到发光二极管,诸如oled或led 146,晶体管可在操作上与光源(诸如例如led或oled)相连接并在操作上与电流源145相连接;

[0255]

第一存储元件可以是电容器或电容电路,诸如具有采样保持电容器144或无时钟控制触发器的采样保持装置;第一存储元件(诸如电容器或采样保持电容器144或无时钟控制触发器)连接在栅极1433和供电电压vdd之间;

[0256]

第二存储元件147例如是电容器c2或电容电路,诸如采样保持装置或无时钟触发器;第二存储元件连接在电压源vdd和传输元件142的电极之间;

[0257]

传输元件例如是晶体管142;

[0258]

加载器可以是晶体管148;加载器148连接到数据线

[0259]

复位开关,诸如复位晶体管149;复位开关149连接在电压源vdd和栅极电极1433之间;

[0260]

发光元件,诸如oled或led像素或子像素146;发光元件连接在诸如晶体管143之类的控制元件和电压源之间;以及

[0261]

电流源145;电流源145连接在电压源vdd和诸如晶体管143之类的控制元件之间。

[0262]

代替使用触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)存储对pwm信号进行编码的位,第二电容器c2被用来代替元件141作为第二存储元件(图14c中的元件147)。诸如电容器c2之类的第二存储元件147可以借助于诸如由“扫描线#x”信号控制的加载晶体管148之类的加载元件来加载。第二存储元件147与晶体管148组合执行一位存储器的功能。如图14c所示,如果加载元件(诸如加载晶体管148)是pmos晶体管,则“扫描线#x”低将使“数据”线与第二存储元件147(诸如电容器c2)的电极相接触,并用数据线上存在的电压对其进行加载。

[0263]

诸如晶体管142之类的传输元件由信号enb闭合或打开,并且加载在诸如电容器c2之类的第二存储元件147上的信号被传输到第一存储元件,诸如电容器或电容电路,诸如采样保持装置,例如控制控制元件(诸如晶体管开关143)的控制电极1433的电容器c

sh

(图14c中编号144)或无时钟控制触发器。

[0264]

诸如复位晶体管149之类的复位元件由信号rstb控制,并且可以使第一存储元件(诸如电容器或电容电路,诸如采样保持装置(例如,具有电容器c

sh

或无时钟控制触发器)放电,并关断诸如晶体管开关143之类的第一控制元件。

[0265]

当激活时,复位元件(诸如复位晶体管149)将使电容器或电容电路(例如采样保持

装置(诸如电容器144或无时钟控制触发器))放电,并且没有电流在光源146(诸如led或oled)中循环。下面将更详细地讨论诸如复位晶体管149之类的复位元件的作用和有用性。

[0266]

图15示出了同一列中的相邻像素或子像素150a、150b、150c及其各自的可编程存储器元件(诸如触发器151a、151b、151c(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深))以菊花链式来连接(即,可编程存储器元件(诸如子像素(或像素)的触发器)的输出被连接到可编程存储器元件(诸如下一子像素(或像素)的触发器)的输入(或者对于两位存储器或多位存储器也是如此,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)。例如,诸如触发器151a之类的可编程存储器元件的输出qa连接到诸如触发器151b之类的可编程存储器元件的输入,并且诸如触发器151b之类的可编程存储器元件的输出qb连接到诸如触发器151c之类的可编程存储器元件的输入。在该配置中,诸如同一列中的子像素或像素的触发器之类的可编程存储器元件形成移位寄存器。

[0267]

通过这种配置,根据本发明,可以仅使用三个信号(en、clk和data(数据))来控制同一列中的所有子像素或像素。用于data信号的导电轨道易于从一个子像素或像素布线到相邻的像素或子像素(即,将可编程存储器元件(诸如触发器)的输出连接到下一可编程存储器元件(诸如触发器)的输入的轨道段)。

[0268]

图15中的每一像素或子像素被示为包括图14a的电流控制或驱动电路。在此明确公开了图14c、17、22-27中任何电路的替代物,以替换此附图中所示的电路。

[0269]

在由采样保持装置144(诸如每一活动子像素或像素150a、150b、150c

……

的采样保持电容器c

sh

)对pwm位或位块进行采样和保持之前,同一列中的可编程存储器元件(诸如触发器151a、151b、,151c

……

(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)必须使用其相应的pwm位或位块来被全部编程。

[0270]

为了说明这一点,以图15的像素为例,这些像素必须根据位深为4的pwm信号来显示数据。

[0271]

对于该示例,在给定帧中:

[0272]

确定(子)像素150a的灰度的pwm信号具有b0=1、b1=0、b2=0和b3=0

[0273]

确定(子)像素150b的灰度的pwm信号具有b0=0、b1=1、b2=0和b3=0,以及确定(子)像素150c的灰度的pwm信号具有b0=1、b1=0、b2=1和b3=0

[0274]

图16示出了当发光元件(诸如led或oled 146)根据先前存储在每一像素或子像素的第一存储元件(例如存储器元件)中的位来编码的信息发光时,如何发送和存储诸位。为了简明起见并且仅作为示例,讨论将限于三个连贯像素或子像素150a、150b和150c。如图15所示,第二存储元件是存储器元件,且优选地是可编程存储器元件,诸如d触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深,这些可编程存储器元件菊花式链接形成移位寄存器。数据通过触发器151a的输入d(图15中的输入data_in)(或通过两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)输入移位寄存器。

[0275]

例如,将描述在发光元件(诸如led或oled)根据第一存储元件中的第一位中所编码的信息保持发光时,第一位(例如b0)如何分别存储在第一存储元件中(例如,可编程存储器元件,诸如每一子像素或像素(150a、150b、150c)的触发器(b

0a

在151a中,b

0b

在151b中,b

0c

在151c中)),以及第二位(例如b1)如何最终存储在同一第二存储元件中,例如可编程存储

器元件,诸如触发器(b

1a

在151a中、b

1b

在151b中、b

1c

在151c中)。与图14a的情况一样,对传输元件和控制元件分别是pmos晶体管142、143的电路进行了描述:这些元件中的每一者都像一个开关一样操作,(a)当低(low)信号施加到其控制电极时闭合,(b)当高(high)信号施加到其控制电极时断开。

[0276]

举例而言,假设b

0a

=1、b

0b

=0、b

0c

=1且b

1a

=0、b

1b

=1、b

1c

=0。

[0277]

为了将位b

0a

、b

0b

和b

0c

移位通过移位寄存器,在施加时钟信号(clk)之前b

0c

首先呈现在第二存储元件(例如可编程存储器元件)的输入端,诸如输入端data_in(数据输入)。针对b

0b

和b

0a

重复该操作,如图16所示。三个时钟周期后,qa=1、qb=0且qc=1。启用信号(en)在时间t0被设置为高(这意味着施加到诸如图14a的pmos晶体管142之类的传输元件的栅极的enb(其是en信号的逻辑逆)被设置为低,并且诸如pmos晶体管142之类的传输元件充当已闭合的开关)。在en高的情况下,第二存储元件(例如,可编程存储器元件,诸如触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出被复制到每一像素或子像素的第一存储元件上,例如电容器或电容电路,诸如采样保持装置144,例如具有电容器c

sh

或无时钟控制触发器,从而根据存储为qa、qb或qc的位b0的状态来打开或闭合将发光元件(诸如每一像素或子像素的led或oled146)连接到电流源145的控制元件(诸如晶体管143)。在图14a、15和16的实施例中,当qa=qc=1且qb=0时,电流流过发光元件(诸如像素或子像素150a和150c的led或oled 146),而没有电流流过诸如像素或子像素150b的led或oled 146之类的发光元件。然后,en信号被设置回低,并且只要跨第一存储元件(诸如电容器或电容电路,例如采样保持装置144,诸如采样保持电容器c

sh

)上的电压未被更新,则在发光元件(诸如分别是像素150a、150b和150c的led或oled 146)中流动的电流ia、ib和ic将保持不变。

[0278]

发光元件(诸如led或oled 146a、146b和146c)现在根据位b

0a

=1、b

0b

=0和b

0c

=1发光。这将保持不变达时间区间t0(如果使用pwm子周期,则其可以是最低有效位的pwm子周期的持续时间,以及如果使用位块,则其可以是位块的持续时间)。在该时间区间t0期间,下一位b

1a

、b

1b

和b

1c

可以移位通过移位寄存器,就像对位b

0a

、b

0b

和b

0c

进行得一样。

[0279]

在时间区间t0结束处,en信号再次设置为高。在en高的情况下,第二存储元件(例如,可编程存储器元件,诸如触发器(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的输出被复制到每一像素或子像素的第一存储元件上,例如电容器或具有电容器c

sh

或无时钟控制触发器的电容电路采样保持装置144,从而根据存储为qa、qb或qc的位b1的状态来打开或闭合将发光元件(诸如每一像素或子像素146的led或oled)连接到电流源145的控制元件(诸如晶体管143)。在图14a、15和16的实施例中,当qa=qc=0且qb=1时,电流流过发光元件(诸如像素或子像素150b的led或oled 146),而没有电流流过诸如像素或子像素150a和150c的led或oled 146之类的发光元件。然后,en信号被设置回低,并且只要跨第一存储元件(例如具有采样保持电容器c

sh

或无时钟控制传感器的采样保持装置144)上的电压未被更新,则在发光元件(诸如分别是像素或子像素150a、150b和150c的led或oled 146)中流动的电流ia、ib和ic将保持不变。

[0280]

对于下一时间区间(使用位块时持续时间是t0,并且如果使用pwm子周期代替位块,则对于权重为n的位,持续时间tn=t0*2n),可以按相同的方式对控制发光元件(诸如像素或子像素的led或oled 146)发射的光的pwm信号进行编码的其他位进行编程。

[0281]

当然,这可以泛化到阵列的同一列(行)中的3个以上像素。

[0282]

在电流控制电路153的阵列中的同一列(或行)中,旨在用于电流控制电路153的第二存储元件的每个位顺序地施加到在电流控制电路153的该列(或行)中的第二存储元件的输入data_in;例如可编程存储器元件,诸如触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深),并被移位通过由该同一列(或行)中相邻电流控制电路153的第二存储元件(诸如可编程存储器元件或触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深))形成的移位寄存器。

[0283]

各个位顺序地呈现在列(或行)宽移位寄存器的输入端处,并通过使用一系列nb第一时钟信号(其中nb是移位寄存器的长度)对移位寄存器进行时钟计时来被移位通过移位寄存器。当nb位已经移位通过移位寄存器时,第二存储元件141(诸如触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)的内容随后通过向传输元件143(其可以是每一电流控制电路153的晶体管)的控制电极1433施加启用信号来被传输到第一存储元件144(诸如电容器或电容电路,诸如采样保持装置或采样保持电容器或无时钟控制触发器)。在该情形中,t0必须至少与向移位寄存器加载nb位所需的时间一样长。

[0284]

本发明的该方面的优点是,同一列(或行)中的电流控制电路153的第一存储元件144(诸如电容器或电容电路,诸如采样保持装置或采样保持电容器或无时钟控制触发器)被同时更新。另选地,对整个阵列而言,更新可以同时完成。

[0285]

在本发明的另一实施例中,对pwm信号进行编码的位深被增加,而不必改变t0的持续时间。

[0286]

如前所述,t0的最小持续时间等于将各个位(例如b

0a

、b

0b

、b

0c

……

)移位通过由第二存储元件(例如可编程存储器元件(151a、151b、151c),诸如触发器或两位存储器或多位存储器,前提是存储器的位数小于像素或子像素150的控制信号(诸如pwm信号)的位深)形成的移位寄存器所需的时间。

[0287]

pwm周期t不能增加到超过由所需帧速率所确定的最大值。

[0288]

因此,增加位深并不容易,并且在某些情况下,对于现有技术中描述的解决方案甚至是不可能的。

[0289]

举例而言,例如pwm信号将使用权重比位b0轻的2个附加的位来被编码。这些位将被称为b-1

和b-2

。

[0290]

在先前示例中,位深是4,且pwm信号是用位b0、b1、b2和b3编码的。为了说明可如何增加位深,假设pwm信号是用6位b-2

、b-1

、b0、b1、b2和b3编码的。

[0291]

如果使用pwm子周期,则表2中给出了针对每个位的pwm子周期的持续时间:

[0292]

表2

[0293]

位b-2

b-1

b0b1b2b3pwm周期的持续时间1/4t01/2t0t02t04t08t0[0294]

如前所述,最小pwm子周期不能减小到t0以下,否则,不能根据相同的方法继续使用相同的移位寄存器。例如,替换解决方案将需要增加信号轨道的数量,才能使数据与每一像素或像素群(子像素或子像素群)并行。

[0295]

然而,根据本发明的另一方面,为了继续对像素或子像素阵列和相关联的驱动电路使用相同的架构,使用复位信号rst。复位信号rst致动活动像素或子像素中的复位元件,例如开关171。如图17所示,对图14a的电路进行了修改。复位元件或开关171连接在控制元件(诸如晶体管143)的栅极1433和参考电压(例如vdd)之间,由此vdd的选择是因pmos晶体管143的情况而异的。当闭合时,复位元件或开关171将控制元件(诸如晶体管143)的栅极1433处的电压强制至vdd,从而将其打开,并且没有电流可以流过发光元件(诸如oled或led 146)。当复位元件或开关171打开时,晶体管143的栅极1433处的电压由第一存储元件(示例是电容器或电容电路,诸如采样保持装置144,例如采样保持电容器c

sh

或无时钟控制触发器)的第一电极的电压确定。在该示例中,当复位信号rst为高时,复位元件(诸如开关171)闭合,并且当复位信号rst为低时,复位元件或开关171打开。在rst高且诸如晶体管143之类的控制元件“打开”的情况下,发光元件或者led或oled 146被关断。在图17中,元件171可以盖写存储在第一存储元件中的值。

[0296]

图18解说了可如何使用rst信号来实现更高的位深。仍然使用类似于图15的电路,并且出于清晰的原因,描述仅限于像素阵列的行或列中的前三个像素。这一次,每一电流驱动电路153都配备复位元件,诸如图17电路上的复位开关171。与图16的情形一样,提供第二存储元件(例如可编程存储器元件,诸如d触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深),其在时钟信号的上升沿触发。

[0297]

如前所述,最小pwm子周期或位块的持续时间是t0。t0例如可以是加载像素或子像素的整行或整列中的第二存储元件(诸如可编程存储器元件,诸如触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)(即使得该行或列为下一信息位做好准备)所需的最小时间区间。

[0298]

对于前n1个msb(例如,n1=4,各个位例如是b0、b1、b2和b3),像素或子像素的发光元件146中的电流如前所述地受到控制,并由整个时间区间(子周期或位块)期间的前n1位的值来确定。

[0299]

对于后n2个lsb(例如,n2=2,各个位是b-1

和b-2

),像素或子像素的发光元件146中的电流由时间区间t0的第一部分(与b0相关联的子周期的持续时间或位块的持续时间)期间的后n2位的值和时间区间t0的第二部分期间的复位信号rst的值来确定。时间区间的第一部分的持续时间和时间区间的第二部分的持续时间之和等于时间区间t0的持续时间。

[0300]

在图18的示例中,假设如下:b-1a

=1、b-1b

=0、b-1c

=1且b-2a

=0、b-2b

=1、b-2c

=0。通过在时间区间t0结束之前针对所有像素或子像素(其第二存储元件(例如存储器可编程元件,诸如触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)被菊花式链接)激活rst信号,这些像素或子像素中的每一者的控制元件(诸如pmos晶体管143)的栅极1433处的电压被设置成供电电压vdd,从而闭合控制元件(诸如晶体管143)并中断通过发光元件(诸如led或oled 146)的电流i

ref

。如果复位信号rst在时间区间t0结束之前被激活,则实际上保证位b-1

和b-2

的权重小于位b0。在图18上,对于b-1

,rst信号在时间间隔t0的中间被设置为高。此时,通过发光元件(诸如led或oled 146)的电流将返回至零。对于b-2

,rst信号在持续时间t0的位块开始1/4t0后设置为高。

[0301]

复位信号rst可同时施加到同一列(或同一行)中的所有像素或子像素。另选地,复位信号rst可同时施加到像素阵列(具有n行和m列)中的所有像素或子像素。另选地,复位信

号rst被施加到同一列(或同一行)中的像素或子像素的子集,或者施加到像素阵列中的像素或子像素的子集n

×

m(其中n《n且m《m)。

[0302]

本发明的实施例提供了增加对(子)像素的明度/亮度进行编码所用的位深(即位数)问题的解决方案。

[0303]

如果(led或oled)固态显示器被设计成以最小pwm子周期t0或持续时间t0的位块来操作,则如本发明实施例中所述地施加复位信号允许将位深增加到超出本领域已知解决方案可能的程度。

[0304]

图19以示例(其中n1=4且n2=2)示出了复位信号rst如何随时间和pwm子周期(对于每一位bi)变化。对应于比特b1、b2和b3的子周期t1、t2和t3各自具有与该位的权重相匹配的持续时间,即t1=2*t0;t2=4*t0,且t3=8*t0。与附加位b-1

和b-2

相对应的子周期具有与对应于位b0的子周期相同的持续时间t0。该限制由例如加载例如在同一像素列中的第二存储元件(例如可编程存储器元件,诸如触发器141或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)所需的最小时间量来施加。由于在例如图14和15的电路中的第二存储元件(例如可编程存储器元件,诸如触发器141(或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深))是在前一位(例如b0)仍然确定发光元件(诸如led或oled 146)中的电流的同时来用一个位(例如b1)更新的,所以位b1必须在使用b0的子周期结束之前被加载。

[0305]

如果位b-1

的子周期是1/2t0(如根据表2的情形),则在需要驱动电流时,不一定在需要它时已经加载了后续位b-2

。无论位是被移位通过列宽或行宽移位寄存器以达到其目的地,还是使用扫描线,都是如此。

[0306]

现有技术通过使用多位存储器元件来解决此问题:首先将位b0、b1、b2、b3的序列加载到本地移位寄存器中,并随后通过以增加的时间区间对其进行时钟计时来相继地使用这些位来驱动电流。这会影响(a)加载时间(未被用于显示信息)和(b)存储器元件的大小。

[0307]

发明人认识到他们可以覆盖通常本来具有小于t0的子周期的位的驱动信号。

[0308]

位b-1

(和b-2

)的子周期与其他位的子周期一样开始:触发器存储的位b-1

被“复制”(或加载或传输)到第一存储元件上,诸如电容器或电容电路,诸如采样保持装置144,例如电容器c

sh

或无时钟控制触发器。一旦传输完成,下一位(b-2

)就被加载到第二存储元件(例如可编程存储器元件,诸如触发器141)上。如前所述,在大于时间1/2t0的时间t0之前,下一位可能不可用。除非缩短位b-1

控制发光元件(诸如led或oled 146)中的电流的时间,否则位b-1

将具有与位b0相同的权重。

[0309]

图17示出了根据本发明的像素的替换实现。

[0310]

在图17所示电路的描述中:

[0311]

控制元件例如是晶体管143,并且第一控制电极1433例如是晶体管143的栅极;晶体管可以是pmos晶体管,例如薄膜晶体管;晶体管可连接到led或oled二极管发光器件146以用于驱动它。晶体管在操作上与诸如led或oled之类的光源连接,并且在操作上与电流源145连接;

[0312]

第一存储元件可以是电容器或电容电路,诸如采样保持装置,举例而言诸如采样保持电容器144或无时钟控制触发器之类的采样保持装置;第一存储元件,诸如电容器,例如采样保持电容器144连接在栅极1433和供电电压vdd之间;

[0313]

第二存储元件可以是触发器141或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深;

[0314]

传输元件例如是晶体管142,诸如pmos晶体管,例如tft晶体管;

[0315]

复位元件,诸如复位开关171;

[0316]

发光元件,诸如oled或led像素或子像素146;

[0317]

电流源145。

[0318]

复位元件(诸如复位开关171)与第一存储元件(例如电容器或电容电路,诸如采样保持装置144)并联,采样保持装置144具有图17所示的采样保持电容器c

sh

或无时钟控制触发器。诸如复位开关171之类的复位元件在时间区间t0结束之前闭合:

[0319]

对于位b-1

,复位元件(诸如复位开关171)在持续时间t0的子周期开始1/2t0后闭合。因此,该时间区间的前半部分中的电流由b-1

确定(即,如果b-1

=0,则电流是0,并且如果b-1

=1,则电流是i

max

),而该时间区间的后半部分中的电流是零(由复位元件(诸如复位开关171)的状态确定,当闭合时复位开关171对电容器c

sh

(144)分流)。

[0320]

对于位b-2

,复位元件(诸如复位开关)在持续时间t0的子周期开始1/4t0后闭合。因此,该时间区间的前四分之一中的电流由b-2

确定(即,如果b-2

=0,则电流是0,并且如果b-2

=1,则电流是i

max

),而该时间区间的其余四分之三中的电流是零(由开关171的状态确定,当闭合时开关171对电容器c

sh

(144)分流)。

[0321]

对于位b-n

,在持续时间t0的子周期开始2-n

t0处,复位开关闭合。

[0322]

在一实施例中,对于前n1个msb(例如,n1=4,n4个msb例如是b0、b1、b2和b3),像素或子像素的发光元件146中的电流由整个时间区间(子周期或位块)期间的前n1位的值来确定。

[0323]

对于后n2个lsb(例如,n2=2,n2个lsb是b-1

和b-2

)中的每一者,像素或子像素的发光元件146中的电流由时间区间的第一部分(子周期或位块)期间的位的值和时间区间的第二部分期间的复位信号rst的值来确定。时间区间的第一部分的持续时间和时间区间的第二部分的持续时间之和等于该时间区间的持续时间。

[0324]

这允许修改用于编码控制发光元件146中的电流的信号的位深。在对电流进行控制之前必须加载一个以上位时,该技术规避了由定时(t0的最小值,t的最大值)和大小(例如第二存储元件的大小,例如可编程存储器元件(诸如触发器或两位存储器或多位存储器,前提是存储器的位数小于控制信号(诸如pwm信号)的位深)造成的限制。

[0325]

可以评估位b-1

和b-2

在占空比中的贡献。无论使用位块还是pwm子周期,占空比编码在六位b-1

、b-2

、b0、b1、b2和b3上的一个pwm周期的持续时间t是t=t0 t0 t0 2*t0 4*t0 8*t0=17*t0。

[0326]

由于在1/2t0和1/4t0之后,对应于b-1

和b-2

的脉冲被切断为0,因此可以实现的最大占空比小于100%:

[0327]

dc

max

=15.75t0/17t0≈0.93(或93%)。

[0328]

通常用于oled或led显示器的位深至少是12(而不是本示例中的4)。通过使用复位信号rst,发明人认识到他们可以将位深增加到例如16位(即,通过将较低有效位b-4

、b-3

、b-2

和b-1

添加到标准12位b0、b1、b2、b3、b4、b5、b6、b7、b8、b9、b

10

和b

11

)。

[0329]

在这种情况下,最大占空比是

[0330]

dc

max

=[(1/16 1/8 1/4 1/2) 2

12-1]/(4 2

12-1)≈0.99925

……

(或99.925%)。

[0331]

12位(不使用全局rst信号)的最小占空比增量将是:

[0332]

δ

min dc=1/4095≈0.00025(或0.025%)。

[0333]

12位 4个较低有效位b-4

、b-3

、b-2

和b-1

(并且使用rst信号)的最小占空比增量将是:

[0334]

δ

min dc=1/16/(4 2

12

–

1)≈0.000015(或0.0015%)。

[0335]

仅添加复位元件(诸如,复位开关171)和全局复位信号rst即可将灰度分辨率提高16倍,而不会对最大占空比产生重大影响,并且也不会对像素或子像素阵列的分辨率产生影响(例如,开关171可以是一个薄膜晶体管)。

[0336]

在实施例的另一示例中,根据本发明的一实施例,一个显示器平铺片的移位寄存器可以与相邻显示器平铺片的移位寄存器进行菊花链式链接,从而有助于组装平铺式显示器,其中每一平铺片由n

×

m个像素(即n列m个像素)组成。图15解说了可如何将同一列中的像素的移位寄存器菊花式链接起来以形成列宽移位寄存器。像素列的概念通常限于在同一基板中形成其薄膜晶体管的像素。在大型显示器中,可以将若干基板组装在一起。组装不同基板的主要困难之一是如何连接这些不同基板,同时保持两个相邻基板之间的距离最小。图20示出了如何解决连接不同基板的问题的本发明实施例。

[0337]

第一基板2001、第二基板2002和第三基板2003沿平行于第一、第二和第三基板上像素列的方向dir彼此相邻地定位。基板可以是半导体(较不优选),优选地是绝缘的,以用在薄膜工艺中。此类基板可以是绝缘基板,如聚酰亚胺、玻璃、石英、金刚石、蓝宝石等。基板是载体,用于在其顶部处理不同的导电和非导电材料层。

[0338]

每一基板上的第二存储元件(例如可编程存储器元件,例如触发器(例如第二基板2002上的2004和2005)被(按列)连接以分别在基板2001、2002和2003上形成例如2006、2007和2008之类的列宽移位寄存器。

[0339]

每一移位寄存器需要两个输入信号:数据信号(即针对同一列中的每一发光元件(诸如led或oled)对pwm信号进行编码的位)和时钟信号,如前所述。如果在最后第二存储元件(诸如基板2001上的列宽移位寄存器2006的最后触发器的q电极)和第一第二存储元件(例如基板2002上的列宽移位寄存器2007的第一触发器的d电极)之间进行连接,则数据信号可以移位到下一移位寄存器(例如2007)。为简明起见,省略了可被用于保护每一基板上的电路以及可能存在于移位寄存器2006中的最后触发器和移位寄存器2007中的第一触发器之间的任何缓冲器、电平移位器

……

。

[0340]

图21解说了有源矩阵显示器,其中选择(select)线选择一整行。数据线被用于提供每列的数据。线0被选中(通过选择0),所有其他选择线被禁用。这样,图14c中的开关148闭合。数据被置于行0的每个列数据线(data 0-》data 2)上。通过这样做,同一行中每一元件中的每一数据线上的值被存储在图14c中的元件147中,然后取消对选择线0的选中。随后,线1被选中。数据被置于行1的每个列数据线上

……

。重复此顺序,直到有源矩阵显示器的整个高度都被加载了数据。

[0341]

这种线的选择是将数据获取到有源显示器的每一单独元件中的优选技术。更简单的有源矩阵示例(2t1c)在图1和图3中示出并且可按与上述相同的方式来驱动。这些方法可以扩展到包括图14a、17、22-27或类似的电流控制或驱动电路。

[0342]

在如图22所示的本发明的另一实施例中,如图17所示使用复位信号rst,并修改了

控制元件(诸如晶体管1434)控制流过发光元件(例如像素或子像素146的oled或led)的电流的方式。图22中的附图标记表示图17中所示的相同电路元件,但旁路开关或晶体管1434除外。代替将诸如tft晶体管143之类的控制元件与诸如子像素或像素的led或oled 146之类的发光元件串联以对通过诸如led或oled 146之类的发光元件的电流进行开关,发光元件与诸如tft晶体管1434之类的控制元件直接短路。原理是相同的,即利用控制信号(诸如pwm驱动信号)接通和关断通过发光元件146的电流。该示意图的优点是,电流源145始终交付电流,无论是否流过发光元件146。这意味着功耗会是恒定的,并且不取决于光输出。本实施例在此明确公开,以包括应用于图14a、14c、22-27或类似电路的电流控制或驱动电路。

[0343]

图23示出了根据本发明的实施例的复位器件149(例如晶体管)的替换布置。具有相同附图标记的电路元件指的是图17中的相同元件,但用作控制元件并被连接以绕过发光元件146的复位器件149(例如,开关(诸如晶体管))除外。当复位元件或开关149闭合时,来自电流源145的电流绕过发光元件146,并且没有电流通过发光元件146。当复位元件或开关149打开时,来自电流源145的电流流过发光元件146。在该实施例中,当复位信号rst为高时,复位元件(诸如开关149)闭合,并且当复位信号rst为低时,复位元件或开关149打开。

[0344]

在该实施例中,一旦复位是活跃的,就没有电流可以流过发光元件146。

[0345]

这可如下完成:

[0346]

1)复位存储在第一存储元件(例如电容器144)中的位值,从而打开开关143,并且因此没有电流可以流过发光元件146。

[0347]

2)将发光元件146与复位器件149短路,诸如开关打开,则不会有电流流过发光元件146。当复位器件149活跃时,可以避免发光元件146的重影,因为诸如发光元件146的阳极之类的功率电极被完全放电。重影是当电流源145在发光元件146仍发光时从发光元件146断开连接时,诸如oled或led之类的发光元件中的现象。这可能有多个原因,其中之一是发光元件146的电容与led或oled的阳极上存在的电压相结合。另一重影原因可能是漏电流。通过绕过发光元件146,避免了这一点,这是一个优点。本实施例在此明确公开,以包括应用于图14a、14b、22-27或类似电路的电流控制或驱动电路。

[0348]

图24至27解说了可如何在选择电流控制或驱动电路中实现两位存储器。在这些附图中,-1和-2分别指与第一位和第二位相关的元件。

[0349]

图24示出了应用于图14a的电路的两位存储器。存储器中的位数应小于控制信号(诸如pwm信号)的位深。基本附图标记,即附图标记1431-1中的143,指的是与图14a中相同的元件。如图24所示,通过增加电流源145和存储器设备141以及其他组件的数量,可以将该两位电路扩展到任意数量的位。存储器中的位数应小于控制信号(诸如pwm信号)的位深。存储元件144-1和144-2(诸如电容器或电容器电路(诸如采样保持电路))分别设置控制元件(诸如晶体管143-1和143-2)的栅极上的电压。一个发光元件146被用于有源显示器的子像素或像素,而两个电流源145-1、145-2分别被用于一个位和第二位。

[0350]

图25示出了应用于图14c的电路的两位存储器。基本附图标记,即附图标记1431-1中的143,指的是与图14c中相同的元件。如图25所示,通过增加电流源145和存储器选择设备148-1、148-2以及其他组件的数量,可以将该两位电路扩展到任意数量的位。存储器中的位数应小于控制信号(诸如pwm信号)的位深。一个发光元件146被用于有源显示器的子像素或像素,而两个(或对于多位而言是更多个)电流源145-1、145-2分别被用于一个位和第二

位。

[0351]

图26和27示出了复制电路元件以提供两位存储器141和141-2的相同原理,而只有一个发光元件146被用于有源显示器的子像素或像素。这些电路基于图14c,但使用了两位存储器(诸如由触发器提供)。图26和图27之间的区别在于,图26中使用了单个数据线,而图27中使用了两个数据线。

[0352]

如果存在带有两个单位存储器的一个数据线,诸如触发器:

[0353]

a.将数据上传到两个单位存储器(诸如触发器)的时间(一个线上的两个单位存储器(诸如触发器))的两倍)是tblock时间

×

2。然而,由于同时发送两个位(2个电流),因此tblock(1位/tblock)的数量被除以2。

[0354]

b.因此,存在平衡或空(null)操作(相同的clk速度)。

[0355]

如果存在两个数据线:

[0356]

c.将数据上传到两个单位存储器(诸如触发器)的时间保持不变(触发器数/线不变);然而,由于两个位现在同时发送两个(2个电流),tblock的数量加倍。

[0357]

d.因此,有源矩阵显示器的刷新率是两倍高,或者在tblock数量相同的情况下,时钟速度可以除以2。

[0358]

在此专门公开了如上所述的两个数据线在使用如参考图24或25所描述的两位存储器的本发明的任何实施例中的使用。

[0359]

这些两位电路可通过增加电流源145和存储器设备141-1、141-2以及其他组件的数量(如在图26和/或27中所示)而被扩展到任意数量的位。存储器中的位数应小于控制信号(诸如pwm信号)的位深。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。