用于存储器的程序暂停和恢复的控制方法与控制器

1.本公开是申请日为2020年05月19日、申请号为202080001162.0、发明名称为“用于存储器的程序暂停和恢复的控制方法与控制器”的国际专利申请的分案申请。

技术领域

2.概括地说,本发明涉及控制方法和控制器,以及更具体地说,本发明涉及用于存储器的程序暂停和恢复的控制方法与控制器。

背景技术:

3.半导体存储器广泛地用于诸如蜂窝电话、数码照相机、个人数字助理、医疗电子设备、移动计算设备和非移动计算设备的各种电子设备。非易失性存储器允许信息被存储和保持。非易失性存储器的示例包括闪存(例如,nand型和nor型闪存)和电可擦除可编程只读存储器(电可擦除可编程只读存储器、eeprom)等。

4.在非易失性存储器中,每个存储元件被配置为存储电荷、电压或其它电参数,以表示在从浮栅晶体管形成的多个位单元(或存储元件)中的数据。程序操作通常在多个存储单元的组或页面中发生。读操作可以在存储单元的页面中或在较小的一组存储单元中发生。但是,在每个页面中单元的数量增加的情况下,可能需要一接收到读命令就立即暂停程序操作。

5.因此,有必要改进现有技术。

技术实现要素:

6.因此,本发明的主要目的是提供用于存储器的程序暂停和恢复的控制方法和控制器,以改善现有技术的缺点。

7.本发明的实施例公开了用于存储器阵列的控制方法,该控制方法包括:在编程阶段中对存储器阵列的位单元进行编程;以及在放电阶段中对存储器阵列的位单元进行放电;其中,编程阶段包括:利用多个编程电压脉冲对存储器阵列的位单元进行编程;其中,放电阶段包括:隔离存储器阵列的位单元的选择线;以及生成对存储器阵列的位单元的编程电压脉冲;其中,编程阶段可以是在放电阶段之后通过暂停命令被暂停到暂停阶段的;其中,暂停命令是在多个编程电压脉冲中的一个编程电压脉冲期间接收的。

8.本发明的实施例还公开了用于对存储器阵列进行编程的控制器,用于对存储器阵列进行编程的控制器包括:存储单元,其被配置为存储程序代码;以及处理单元,其被配置为执行以下步骤:在编程阶段中对存储器阵列的位单元进行编程;以及在放电阶段中对存储器阵列的位单元进行放电;其中,编程阶段包括:利用多个编程电压脉冲对存储器阵列的位单元进行编程;其中,放电阶段包括:隔离存储器阵列的位单元的选择线;以及生成对存储器阵列的位单元的编程电压脉冲;其中,编程阶段可以是在放电阶段之后通过暂停命令被暂停到暂停阶段的。

附图说明

9.在阅读了以下在各个附图和绘图中示出的优选实施例的详细说明之后,本发明的这些和其它目的对于本领域的普通技术人员无疑将变得显而易见。

10.图1是现有技术中用于存储器阵列的编程过程的波形的示意图。

11.图2是现有技术中用于存储器阵列的编程过程中的暂停的波形的示意图。

12.图3是现有技术中在编程过程中的编程电压脉冲的波形的示意图。

13.图4是根据本发明的实施例的用于存储器阵列的编程过程的波形的示意图。

14.图5a和图5b是根据本发明的实施例的用于存储器阵列的编程过程的波形的示意图。

15.图6是根据本发明的实施例的用于存储系统的编程过程60的示意图。

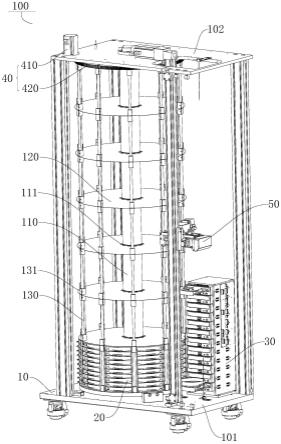

16.图7是根据本发明的实施例的存储系统70的示意图。

具体实施方式

17.遍及说明书和所附权利要求书使用某些术语来指代特定的组件。如本领域技术人员将认识到的,制造商可以通过不同的名称来指代组件。本文档不打算在名称不同但功能相同的组件之间进行区分。在以下描述和权利要求中,术语“包括”和“包含”是以开放方式来使用的,因此应当被解释为意指“包括但不限于”。此外,术语“耦合”旨在意指间接或直接的电连接。因此,如果一个设备电连接到另一个设备,则该连接可以是通过直接电连接,或者是通过经由其它设备和连接的间接电连接。“大致”意味着在可接受的误差预算内,本领域技术人员可以在一定的误差预算内解决技术问题,以及基本上实现技术效果。

18.虽然本文描述了许多实施例,但是所描述的实施例中的至少一些实施例促进针对电子存储设备的程序暂停/恢复操作。换句话说,可以临时地或永久地暂停在非易失性存储器(nvm)处正在处理的编程(或其它等效物)操作,以便允许在nvm处处理一个或多个其它存储器存取操作(例如,读取、擦除、部分程序等等)。如本文所使用的,术语“程序操作”包括在nvm上保持值(数字或模拟)或者保持表示值的状态的任何操作。其它程序(或等效物)操作的一些示例包括但不限于在nvm上刻录、存储、写入和设置持久值。本文中对程序操作的引用包括其它等效的或类似的操作。本文中对“暂停”的引用包括其它等效的或类似的术语,包括但不限于中止、中断、排队和延迟。

19.存储器包括存储器阵列,所述存储器阵列包括许多页面的存储元件。每个存储元件被配置为存储电荷、电压或其它电参数以表示数据。但是,在每个页中的单元的数量的增加的情况下,编程时间也增加。因此,在其中存储器在每个编程命令之间可以为读命令提供服务的处于空闲的间隔在减小,以及问题在于当存储器正在执行编程命令时需要暂停命令。

20.更具体而言,图1是针对现有技术中的存储器阵列的编程过程的波形的示意图。如可以看出的,编程过程包括处于多个编程阶段中的多个编程电压脉冲,其中多个编程电压脉冲的电压是通过值ispp来增加的。此外,要求验证阶段来验证编程是否成功。

21.换句话说,编程过程可以是使用递增的电压脉冲来执行的,该递增的电压脉冲将值的电压电平递增地增加到每个电压脉冲,这将在ispp的值中的电压电平增加以将逻辑0或1存储在存储器阵列的位单元(存储单元)中,直到通过验证为止。如果然后验证失败,则

施加另一个具有较高电压电平的编程电压脉冲(第二编程电压的脉冲,在验证失败之前施加的较低的电平电压为第一编程电压)以对存储器阵列的位单元进行编程。

22.此外,随着对存储器阵列的位单元的组进行编程,可以执行程序暂停操作以暂停在存储元件的给定页面上的程序(或者写入或其它等效的)操作,以便从存储元件中的一个存储元件中读取数据。在暂停程序操作之前,存储与当前程序操作相对应的编程电压脉冲计数,以便使存储器阵列空闲(器可以为被中断的命令服务,诸如读命令),然后继续进行到编程阶段,其中编程电压脉冲的电压电平是基于在暂停之前存储的编程电压脉冲计数。

23.图2是现有技术中在针对存储器阵列的编程过程中的暂停操作的波形的示意图。如可以看出的,当执行编程过程时接收到暂停命令,存储器阵列将为到其它页面的读取请求服务,然后恢复以继续地进行编程过程。

24.但是,当在一个编程电压脉冲期间暂停编程过程时,对编程过程的恢复可能导致编程沟道为负。换句话说,关于正常程序,位单元的这些门限电压vt在时间上左移。结果,孔(空穴)将在沟道中以及还在电荷捕获层(存储元件中包含了电荷俘获层)中累积。此外,暂停时间越长,将导致越多的累积,即使未很好地对位单元进行编程,这使位单元在恢复之后更易于通过首次验证。

25.另一方面,如果读命令是在队列中以及是在编程过程完成之后执行的,则读取时间将是悬而未决的,直到页面完成编程和验证为止。因此,读取延时将随着页面的位单元的数量增加而增加。

26.例如,图3是现有技术中在编程过程中的编程电压脉冲的波形的示意图。如图3中所示,由存储器阵列接收到暂停命令,在恢复之后的第一验证很容易通过,这是因为与不具有暂停的门限电压vt(以粗线示出)相比,对门限电压vt进行了偏移(以虚线示出)。这将使在程序之后的读取具有更多的失败位。

27.与现有技术不同,当存储器在编程阶段中接收暂停命令时,本发明的控制方法在编程阶段之后通过插入放电阶段来执行针对存储器阵列的编程过程。从而,改善在编程过程中的错误的出错率。

28.具体而言,请参考图4,图4是根据本发明的实施例,用于存储器阵列的编程过程的波形的示意图。如可以看出的,将跟随一个编程电压脉冲(第一编程电压的脉冲)的清理电压脉冲(放电电压的脉冲)冲激到存储器阵列,然后存储器阵列将编程阶段转移到暂停阶段,以为其它存储请求服务。

29.实际上,清理电压脉冲的电压以及其脉冲宽度可以是根据不同的利用场景来可调节的。在一实施例中,清理电压脉冲的电压及其脉冲宽度可以是通过预先确定、校准、通过映射表确定、或者相应地调整以适合实际场景的固定值,其中该实际场景对应于电压、电流、温度、使用年限或者它们的组合。本领域技术人员可以相应地进行对决策规则的修改和变更,以及不受限于此。

30.为了实现对产生清理电压脉冲的要求,图5a根据本发明的实施例示出了用于存储器阵列的编程过程的波形的示意图。如图5a中所示,底部选择栅极线是在放电阶段(第一编程电压之后)启用的,这可以释放孔以及防止对位单元进行错误编程。

31.如可以看出的,存储器阵列的位单元的接口包括顶部选择栅极线tsg、底部选择栅极线bsg、电荷捕获线、共源极线和p阱线。在编程阶段,输入编程波形以逻辑0或逻辑1的形

式存储数据。但是,存储器阵列的接口并不限于上文,以及本领域技术人员可以根据在整个系统中的存储器阵列进行修改和变更。

32.此外,图5b根据本发明的实施例示出用于存储器阵列的编程过程的波形的示意图。如图5b中所示,可以在编程阶段的结束之前(第一编程电压的脉冲下降完成之前)提早启用底部选择栅极线(这里的启用底部选择栅极线代表向底部选择栅极线施加底部栅极线电压)。也就是说,放电阶段可以与编程阶段短暂地重叠,以节省从编程阶段到暂停阶段的过渡时间。

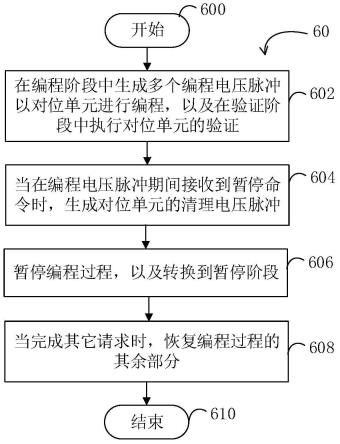

33.编程过程的操作可以概括为编程过程60,如图6所示。编程过程60包括以下步骤:

34.步骤600:开始。

35.步骤602:在编程阶段中生成多个编程电压脉冲以对位单元进行编程,以及在验证阶段中执行对位单元的验证。

36.步骤604:当在编程电压脉冲期间接收到暂停命令时,生成对位单元的清理电压脉冲。

37.步骤606:暂停编程过程,以及转换到暂停阶段。

38.步骤608:当完成其它请求时,恢复编程过程的其余部分。

39.步骤610:结束。

40.在步骤602中,可以将编程过程60修改为具有验证阶段,以依次跟随多个编程阶段。例如,在一实施例中,编程过程60可以包括第一编程阶段、第二编程阶段,然后是验证阶段。

41.在步骤604中,在完成对编程电压脉冲的一次验证之后,暂停命令可以被修改为要排队;也就是说,暂停阶段可以是从编程阶段或验证阶段转换的。但是,在步骤608中,应当继续地执行编程过程的其余部分。例如,如果存储器阵列在编程阶段中被暂停,则在步骤608中,以验证阶段来开始编程过程的其余部分;如果存储器阵列在验证阶段被暂停,则步骤608中以编程阶段来开始编程过程的其余部分。

42.此外,在步骤604中,可以通过虚设的编程电压脉冲、虚设的编程命令、或者可以将孔放电到针对存储系统暂停的编程过程中的位单元的其它方式,来生成清理电压脉冲。

43.编程过程60的详细操作可以参考前述的描述,为简洁起见,在此不再叙述。

44.图7是根据本发明的实施例的存储系统70的示意图。存储系统70包括:存储器阵列72,其被配置为存储以逻辑0或逻辑1的形式的数据;以及控制器74,其被配置为接收外部命令以及切换波形以控制存储器阵列72。底部选择栅极线是由用于切换波形或接收外部命令的控制器74启用的。在一实施例中,控制器74可以包括处理器和存储单元。存储单元可以存储程序代码,以指示处理器执行切换本发明的波形的功能。此外,处理器可以是处理单元、应用处理器(ap)或数字信号处理器(dsp),其中处理单元可以是中央处理单元(cpu),图形处理单元(gpu)或张量处理单元(tpu),以及不限于此。存储单元可以是存储器,该存储器可以是非易失性存储器,诸如电可擦除可编程只读存储器(eeprom)或闪存,以及不限于此。

45.在一实施例中,存储系统70可以通过生成虚设的编程命令,在放电阶段生成编程波形。在一实施例中,编程电压脉冲中的每个编程电压脉冲可以跟随有虚设的编程命令。值得注意的是,本发明并不限于生成对存储器的位单元的虚设的编程电压脉冲,以及本领域技术人员可以例如通过使能底部选择栅极线来适当地对位单元进行放电,或者组合上文所

提及的方法的优点。控制的方法是对于本领域技术人员已知的,为简洁起见,在此不再叙述。

46.此外,当存储器被暂停的使用并不仅限于读取。实际上,本领域技术人员可以根据不同的利用场景,利用其它存储器存取请求以及分别与其它存储器存取请求相对应的操作来代替读命令和读操作。

47.值得注意的是,上文所述的实施例被利用用于说明本发明的概念。本领域技术人员可以相应地进行修改和变更,以及不限于此。因此,只要在编程阶段之后插入放电阶段,以避免在编程过程中被累积到存储器阵列的位单元的孔被暂停用于存储系统,则满足本技术的要求。

48.综上所述,通过避免在编程过程中累积到位单元的孔被暂停用于存储系统,用于本技术的存储器的程序暂停和恢复的控制方法和控制器具有减少在编程过程中的失败位计数的优点,这可以增加存储器的稳健性。

49.本领域技术人员将容易地观察到的是,在保持本发明的教导的同时,可以对设备和方法进行多种修改和变更。因此,以上公开内容应当被解释为仅由所附权利要求书的边界和界限来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。