1.本发明涉及一种支持程序固化的仿真器的方案设计,主要应用于芯片仿真调试领域,特别涉及一种支持程序固化的仿真器及方法。

背景技术:

2.对于由fpga实现的芯片仿真器,通常采用ram仿真芯片的nvm存储器(包括flash、eeprom、rom等非易失性存储器),但是采用ram存放程序数据,在仿真器每次上电后都需要重新下载程序。对于芯片cos测试人员,希望使用已下载好程序的仿真器,可以向真实芯片一样方便移动测试,同时也不需考虑如何对下载的程序数据进行安全保护。

3.芯片仿真器实现程序固化的常用有方法两种:

4.方法一,采用fpga内部的block ram进行程序数据固化,fpga上电后程序即存在并可以运行,此方法主要问题是待测试的程序往往是频繁更新,每次都需要fpga重新综合实现,工作量大且易引入fpga时序问题,对于用户开发的程序涉及代码安全保护,此方法并不适用。

5.方法二,采用非易失性存储器替代ram来实现芯片的nvm存储器,此方法不仅增加仿真器硬件成本,主要问题是非易失性存储器读写速度慢,接口总线的位宽固定,无法满足fpga时序设计要求及对多块不同总线位宽存储器的需求。

6.为解决采用ram仿真芯片nvm存储器的仿真器程序如何固化的问题,本发明提出一种支持程序固化的仿真器及方法。

技术实现要素:

7.本发明所解决的技术问题是,如何设计一种支持程序固化的仿真器,在仿真器上电后程序自动加载运行,并能实现对程序数据的安全保护,又利于平台化,方便在多个芯片产品中开发和应用。

8.本发明提出一种支持程序固化的仿真器设计,采用非易失性的备份存储器存储芯片nvm模块中的程序数据,由芯片功能调试模块向备份存储器下载程序,芯片功能调试模块在仿真器上电后从备份存储器加载程序数据到芯片nvm模块,芯片功能调试模块控制芯片功能模块完成复位后,芯片功能模块开始执行nvm中的程序。

9.芯片功能调试模块和芯片nvm模块中都具有程序地址映射及配置功能,从而支持芯片nvm存储器容量及地址的调整,利于仿真器在芯片产品中进行平台化设计。在芯片nvm模块和备份存储器中采用存储密文的程序数据的方式实现对程序的保护功能;芯片nvm模块中的程序为密文数据,在备份存储器中支持存放明文或密文的程序数据。在无安全调试需求时备份存储器中存放明文,在有安全调试需求时备份存储器中存放密文。

10.仿真器包括:仿真器调试模块、备份存储器、芯片功能调试模块、芯片功能仿真模块,各组件功能说明如下:

11.仿真器调试模块,与芯片功能调试模块相连,控制芯片功能调试模块对芯片功能

仿真模块进行调试,仿真器调试模块用于产生明文和密文的程序数据,并实现程序数据的下载功能;

12.备份存储器,与芯片功能调试模块相连,用于存储程序数据,实现仿真器下电后程序数据保持功能;

13.芯片功能调试模块,具有以下功能:接收和响应仿真器调试模块发送的调试命令和数据,写入或读出备份存储器中程序数据,并实现对芯片功能仿真模块的调试功能,对芯片功能仿真模块中的程序数据进行读写访问;

14.芯片功能仿真模块,与芯片功能调试模块相连,通过芯片调试接口和数据访问接口与芯片功能调试模块进行数据交互,并实现对芯片功能的仿真。

15.本发明的仿真器中的芯片功能仿真模块由芯片功能模块和芯片nvm模块组成:

16.芯片功能模块,通过芯片调试接口、复位信号、权限控制信号与芯片功能调试模块中的访问控制模块相连,用于仿真芯片功能;芯片功能模块具有访问芯片nvm模块中程序数据的权限管理功能,并实现对芯片nvm模块中的程序存入加密、读出解密的功能,实现芯片nvm模块中存放加密的程序数据;

17.芯片nvm模块,用于仿真芯片nvm存储器,并实现访问存储器数据的数据访问接口。

18.本发明的仿真器中的芯片功能调试模块,由访问控制模块和地址配置模块组成:

19.访问控制模块,与芯片功能模块相连,实现对芯片功能模块的调试控制;访问控制模块与仿真器调试模块、地址配置模块相连,将仿真器调试模块产生的程序数据经过地址配置模块写入备份存储器,实现程序下载功能;访问控制模块输出复位信号至芯片功能模块,复位信号为低电平有效时芯片功能模块被复位,复位信号为高电平无效时芯片功能模块正常运行;访问控制模块输出权限控制信号至芯片功能模块,实现对芯片nvm模块访问的权限控制;访问控制模块输出访问控制信号至访问选择模块,访问控制信号为高电平有效时地址映射模块经过访问选择模块与ram存储器模块连通,访问控制模块通过数据访问接口读写ram存储器模块中的数据;访问控制信号为低电平无效时,nvm接口模块经过访问选择模块与ram存储器连通,访问控制模块通过芯片调试接口读写ram存储器模块中的数据。

20.地址配置模块,与访问控制模块、备份存储器相连,将程序的明文逻辑地址转换成程序在备份存储器存储的物理地址;地址配置模块中存放多组映射表,每组映射表定义一段程序数据的明文逻辑地址和备份存储器物理地址的对应关系,支持仿真器调试模块通过访问控制模块对映射表进行配置,从而支持具有不同ram结构及容量的ram存储器模块的仿真器的实现程序固化功能。

21.芯片功能模块中的芯片nvm模块,由nvm接口模块、ram存储器模块、地址映射模块、访问选择模块共4部分组成,

22.nvm接口模块,将芯片功能模块的nvm接口转换为ram存储器模块的ram接口;

23.ram存储器模块由ram_1~ram_n多块ram组成,和nvm接口模块共同仿真芯片的nvm存储器功能;芯片nvm模块中的程序数据存储在ram_1~ram_n中,ram存储器模块中的程序数据不仅包含可执行的程序代码,也包含执行程序需要固化的各种数据。

24.地址映射模块,实现多组地址映射寄存器,将程序数据的明文逻辑地址转换成ram存储器模块中ram_1~ram_n对应存储空间的物理地址,支持仿真器调试模块通过访问控制模块对地址映射寄存器进行配置,从而方便实现ram存储器模块的存储容量及地址调整后

的仿真器设计;地址映射模块通过数据访问接口与访问控制模块相连,支持访问控制模块通过地址映射模块、访问选择模块访问ram存储器模块中加密的程序数据,且不需要芯片功能模块参与。

25.访问选择模块,与nvm接口模块、地址映射模块、ram存储器模块、访问控制模块相连,访问控制模块输出的访问控制信号决定nvm接口模块还是地址映射模块访问ram存储器模块,访问控制模块和地址映射模块共同实现访问控制模块通过数据访问接口直接读写ram存储器模块中加密的程序数据的功能。

26.上述的地址配置模块和地址映射模块,将程序的明文逻辑地址与备份存储器和ram存储器模块的物理地址进行对应逐一映射,只需配置地址的映射关系,未对程序数据进行加解密。

27.访问控制模块读写ram存储器模块中的程序数据有两条通路,芯片调试接口和数据访问接口。通过芯片调试接口读写的程序数据为明文,通过数据访问接口读写的程序数据为密文;仿真器调试模块产生的明文程序数据和访问控制模块从芯片调试接口读写的程序数据相同;仿真器调试模块产生的密文程序数据和访问控制模块从数据访问接口读写的程序数据相同;仿真器调试模块产生的明文和密文的程序数据相比,程序数据的地址相同,密文数据是由明文数据加密生成,加密方式与芯片功能模块的加密方式一致,因此本发明的仿真器当需要在备份存储器中存放密文时,通过从数据访问接口读出密文的程序数据直接写入备份存储器,就不需要在仿真器调试模块中设计实现产生密文的功能,此方法使设计更简单可靠。

28.本发明的一种支持程序固化的方法,应用于支持程序固化的仿真器,芯片功能调试模块向备份存储器下载程序,在仿真器上电后芯片功能调试模块从备份存储器加载程序数据到ram存储器模块,芯片功能模块在芯片功能调试模块控制下完成复位并开始执行ram存储器模块中的程序,包括:程序固化流程、程序加载运行流程。

29.1、程序固化流程,是指将明文或密文的程序数据写入备份存储器,有直接下载和间接下载两种方法。

30.1)直接下载方法,是指仿真器调试模块将产生的明文或密文的程序数据,经过访问控制模块和地址配置模块写入备份存储器,步骤如下:

31.步骤1,仿真器调试模块对地址配置模块进行配置,使地址配置模块中各地址空间与芯片nvm模块中的ram_1~ram_n相对应;

32.步骤2,仿真器调试模块解析程序的地址及数据,按地址配置模块的配置向备份存储器下载数据。

33.2)间接下载方法,是指仿真器调试模块将明文或密文的程序数据先下载到ram存储器模块,再通过访问控制模块从ram存储器模块中读出程序数据下载到备份存储器,步骤如下:

34.步骤1,访问控制模块在仿真器调试模块控制下,将复位信号配置为有效,芯片功能模块被复位;

35.步骤2,访问控制模块在仿真器调试模块控制下,将权限控制信号配置为有效,将访问控制信号配置为无效,支持芯片功能模块访问ram存储器模块中所有的程序数据空间;

36.步骤3,访问控制模块在仿真器调试模块控制下,将复位信号配置为无效,芯片功

能模块开始运行;

37.步骤4,仿真器调试模块将程序的明文数据,经过访问控制模块、芯片功能模块、nvm接口模块、访问选择模块写入ram存储器模块;

38.步骤5,将ram存储器模块中的程序数据固化到备份存储器,有两种方法:

39.备份存储器存放明文程序数据的固化方法:访问控制模块在仿真器调试模块控制下,通过芯片调试接口从ram存储器模块读出程序数据并写入备份存储器;

40.备份存储器存放密文程序数据的固化方法:访问控制模块在仿真器调试模块控制下,将访问控制信号配置为有效,通过数据访问接口从ram存储器模块读出程序数据并写入备份存储器。

41.2、程序加载运行流程,是指仿真器上电后,访问控制模块将备份存储器中的明文或密文程序数据加载到ram存储器模块,芯片功能模块在访问控制模块控制下完成复位后开始执行ram存储器模块中的程序,分为两种流程:

42.1)备份存储器存放的程序数据为明文,步骤如下:

43.步骤1,访问控制模块将复位信号配置为无效,将权限控制信号配置为有效,将访问控制信号配置为无效,访问控制模块通过芯片调试接口从备份存储器读出程序数据并写入ram存储器模块;

44.步骤2,访问控制模块将权限控制信号配置为无效,芯片功能模块对ram存储器模块访问权限与芯片设计一致;

45.步骤3,访问控制模块将复位信号先配置为有效,再配置为无效,使芯片功能模块产生一次复位后从ram存储器模块读出程序开始运行。

46.2)备份存储器存放的程序数据为密文,步骤如下:

47.步骤1,访问控制模块先将复位信号和访问控制信号都配置为有效,再从备份存储器读出程序数据并通过数据访问接口写入ram存储器模块;

48.步骤2,访问控制模块将复位信号配置为无效,芯片功能模块完成复位后从ram存储器模块读出程序开始运行。

附图说明

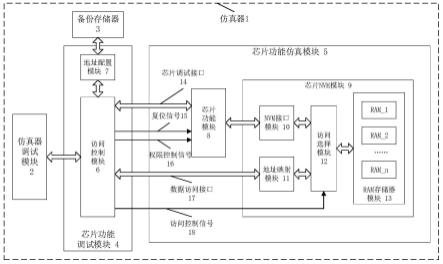

49.图1是一种支持程序固化的仿真器的结构图。

具体实施方式

50.下面结合附图对本发明仿真器进行详细说明。

51.如图1所示,给出仿真器结构图。仿真器1包括仿真器调试模块2、备份存储器3、芯片功能调试模块4、芯片功能仿真模块5。其中芯片功能调试模块4由访问控制模块6和地址配置模块7组成;芯片功能仿真模块5由芯片功能模块8和芯片nvm模块9组成。芯片nvm模块9由nvm接口模块10、地址映射模块11、访问选择模块12、ram存储器模块13组成,芯片nvm模块9用于仿真芯片的非易失性存储器,包括flash、eeprom、rom、nvram等各种下载后数据不丢失的存储器。

52.上述的仿真器调试模块2采用pc机软件工具实现,备份存储器3采用非易失性的flash存储器芯片实现,芯片功能调试模块4采用mcu芯片实现,也可以采用fpga芯片用逻辑

电路实现,芯片功能仿真模块5采用fpga芯片实现。备份存储器3、芯片功能调试模块4、芯片功能仿真模块5的硬件电路做在一块电路板上。访问控制模块6在仿真器调试模块2的操作控制下,完成对备份存储器3和ram存储器模块13的程序数据下载;访问控制模块6在仿真器上电后,将备份存储器3中的程序数据自动加载到ram存储器模块13,并控制芯片功能模块8执行ram存储器模块13中的程序。

53.按程序固化流程向备份存储器3下载程序数据,分为直接下载和间接下载两种方法:直接下载方法是指仿真器调试模块2实现形式为下载工具软件,根据安全需求生成明文或密文的数据下载到备份存储器3;间接下载方法是仿真器调试模块2实现形式为ide调试软件,只能生成明文程序数据,先将数据下载到ram存储器模块13,通过芯片调试接口14读出明文数据,或是通过数据访问接口17读出密文数据再写入备份存储器3。对于备份存储器3存储密文程序的设计,采用间接下载方法,不用关注程序数据如何加解密,使设计更加简单。

54.访问控制模块6通过芯片调试接口14访问ram存储器模块13:经过芯片调试接口14读写的程序数据为明文,此时复位信号15为高电平无效,权限控制信号16为高电平有效,访问控制信号18为低电平无效状态,访问控制模块6经过芯片功能模块8、nvm接口模块10、访问选择模块12连接到ram存储器模块13中的ram_1~ram_n。

55.访问控制模块6通过数据访问接口17访问ram存储器模块13:经过数据访问接口17读写的程序数据为密文,此时复位信号15配置为低电平有效,权限控制信号16电平状态对此操作无影响,访问控制信号18为高电平有效状态,访问控制模块6经过地址映射模块11、访问选择模块12连接到ram存储器模块13中的ram_1~ram_n。

56.以上实施例仅用以说明而非限制本发明的技术方案,尽管参照上述实施例对本发明进行了详细说明,本领域的普通技术人员应当理解:依然可以对本发明进行修改或等同替代,而不脱离本发明的精神和范围的任何修改或局部替代,其均应涵盖在本发明的权利要求范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。