1.本发明的示例总体上涉及可编程设备,尤其涉及用于可编程设备的配置存储器系统。

背景技术:

2.可编程设备(诸如现场可编程门阵列(fpga)和具有fpga可编程构造的片上系统(soc))在人工智能(ai)、数据中心和汽车应用中正获得发展势头。在这些应用中,一种有用的技术是可编程设备的部分重配置。部分重配置是通过下载部分配置位文件动态地修改可编程设备的逻辑块、同时剩余的逻辑继续操作而不中断的能力。传统上,部分重配置性能受到可编程设备中的分布式存储器系统的限制,其中数据线贯穿整个设备宽度,并且存储控制器必须等待前一次写入/读取完成才能启动下一次写入/读取。因此,希望在可编程设备中改进配置存储器系统的性能。

技术实现要素:

3.描述了用于在可编程设备中提供配置存储器系统的技术。在一个示例中,一种用于可编程设备的配置系统包括:配置存储器读取/写入单元,被配置为接收用于存储在可编程设备的配置存储器中的配置数据,配置存储器包括多个帧;多个配置存储器读取/写入控制器,耦合到配置存储器读取/写入单元;多个构造子区域(fsr),分别耦合到多个配置存储器读取/写入控制器,每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

4.在另一示例中,一种可编程设备包括:可编程构造;配置存储器,用于存储配置可编程构造的数据,配置存储器包括多个帧;配置存储器读取/写入单元,被配置为接收用于存储在配置存储器中的配置数据;多个配置存储器读取/写入控制器,耦合到配置存储器读取/写入单元;多个构造子区域(fsr),分别耦合到多个配置存储器读取/写入控制器,每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

5.在另一示例中,一种配置可编程设备的方法包括:通过配置存储器读取/写入单元接收用于存储在可编程设备的配置存储器中的配置数据,配置存储器包括多个帧;向耦合到配置存储器读取/写入单元的多个配置存储器读取/写入控制器提供配置数据;以及将来自多个配置存储器读取/写入控制器的配置数据提供给多个构造子区域(fsr),多个fsr分别耦合到多个配置存储器读取/写入控制器,每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

6.下文提供了所公开技术的其他非限制性示例。

7.示例1.一种用于可编程设备的配置系统,包括:

8.配置存储器读取/写入单元,被配置为接收用于存储在可编程设备的配置存储器中的配置数据,配置存储器包括多个帧;多个配置存储器读取/写入控制器,耦合到配置存储器读取/写入单元;以及多个构造子区域(fsr),分别耦合到多个配置存储器读取/写入控制器,每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

9.示例2.根据示例1的配置系统,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:触发器;多路复用器,具有耦合到触发器的输入的输出、耦合到多个配置存储器读取/写入控制器中的相应一个配置存储器读取/写入控制器的第一输入以及耦合到相应fsr中的缓冲器中的一个缓冲器的第二输入;以及第一缓冲器,耦合到触发器的输出,第一缓冲器的输出耦合到多个配置存储器读取/写入控制器中的该相应一个配置存储器读取/写入控制器。

10.示例3.根据示例2的配置系统,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:第一反相器,具有的输出耦合到多路复用器的第二输入;第二反相器,具有的输入耦合到第一反相器的输入并且具有的输出耦合到缓冲器中的所述一个缓冲器;以及第三反相器,具有的输出耦合到第一反相器的输入并且具有的输入耦合到缓冲器中的所述一个缓冲器。

11.示例4.根据示例3的配置系统,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线包括:第二缓冲器,具有的输入耦合到触发器的输出并且具有的输入以及耦合到缓冲器中的所述一个缓冲器。

12.示例5.根据示例4的配置系统,其中第一和第二缓冲器中的每个缓冲器均包括三态缓冲器,并且其中第三反相器包括三态反相器。

13.示例6.根据示例1的配置系统,其中多个fsr中的每个fsr中的流水线包括数据线管线、帧地址寄存器(far)管线和控制管线,其中数据线管线传播配置数据,far管线传播地址信息,以及控制管线传播用于锁存数据线管线和far管线的控制信号。

14.示例7.根据示例1的配置系统,其中多个fsr中的每个fsr中的流水线包括被配置为在数据线管线上锁存读取数据的标签管线。

15.示例8.一种可编程设备,包括:可编程构造;配置存储器,用于存储配置可编程构造的数据,配置存储器包括多个帧;配置存储器读取/写入单元,被配置为接收用于存储在可编程设备的配置存储器中的配置数据,配置存储器包括多个帧;多个配置存储器读取/写入控制器,耦合到配置存储器读取/写入单元;多个构造子区域(fsr),分别耦合到多个配置存储器读取/写入控制器,每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

16.示例9.根据示例8的可编程设备,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:触发器;多路复用器,具有耦合到触发器的输入的输出、耦合到多个配置存储器读取/写入控制器中的相应一个配置存储器读取/写入控制器的第一输入以及耦合到相应fsr中的缓冲器中的一个缓冲器的第二输入;以及第一缓冲器,耦合到触发器的输出,第一缓冲器的输出耦合到多个配置存储器读取/写入控制器中的该相应一个配置存储器读取/写入控制器。

17.示例10.根据示例9的可编程设备,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:第一反相器,具有的输出耦合到多路复用器的第二输入;第二反相器,具有的输入耦合到第一反相器的输入并且具有的输出耦合到缓冲器中的所述一个缓冲器;以及第三反相器,具有的输出耦合到第一反相器的输入并且具有的输入耦合到缓冲器中的所述一个缓冲器。

18.示例11.根据示例10的可编程设备,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:第二缓冲器,具有的输入耦合到触发器的输出并且具有的输入耦合到缓冲器中的所述一个缓冲器。

19.示例12.根据示例11的可编程设备,其中第一和第二缓冲器中的每个缓冲器均包括三态缓冲器,并且其中第三反相器包括三态反相器。

20.示例13.根据示例8的可编程设备,其中多个fsr中的每个fsr中的流水线包括数据线流水线、帧地址寄存器(far)管线和控制管线,其中数据线管线传播配置数据,far管线传播地址信息,以及控制管线传播用于锁存数据线管线和far管线的控制信号。

21.示例14.根据示例8的可编程设备,其中多个fsr中的每个fsr中的流水线包括被配置为在数据线流水线上锁存读取数据的标签流水线。

22.示例15.一种配置可编程设备的方法,包括:在配置存储器读取/写入单元处接收用于存储在可编程设备的配置存储器中的配置数据,配置存储器包括多个帧;向耦合到配置存储器读取/写入单元的多个配置存储器读取/写入控制器提供配置数据;以及将来自多个配置存储器读取/写入控制器的配置数据提供给分别耦合到多个配置存储器读取/写入控制器的多个构造子区域(fsr),每个fsr均包括设置在缓冲器之间的配置存储器的存储器单元的流水线以及耦合在该流水线与多个fsr中的下一个fsr之间的配置存储器读取/写入流水线单元。

23.示例16.根据示例15的方法,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:触发器;多路复用器,具有耦合到触发器的输入的输出、耦合到多个配置存储器读取/写入控制器中的相应一个配置存储器读取/写入控制器的第一输入以及耦合到相应fsr中的缓冲器中的一个缓冲器的第二输入;以及第一缓冲器,耦合到触发器的输出,第一缓冲器的输出耦合到多个配置存储器读取/写入控制器中的该相应一个配置存储器读取/写入控制器。

24.示例17.根据示例16的方法,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:第一反相器,具有的输出耦合到多路复用器的第二输入;第二反相器,具有的输入耦合到第一反相器的输入并且具有的输出耦合到缓冲器中的所述一个缓冲器;以及第三反相器,具有的输出耦合到第一反相器的输入并且具有的输入耦合到缓冲器中的所述一个缓冲器。

25.示例18.根据示例17的方法,其中多个fsr中的每个fsr中的配置存储器读取/写入流水线单元包括:第二缓冲器,具有的输入耦合到触发器的输出并且具有的输入耦合到缓冲器中的所述一个缓冲器。

26.示例19.根据示例18的方法,其中第一和第二缓冲器中的每个缓冲器均包括三态缓冲器,并且第三反相器包括三态反相器。

27.示例20.根据示例15的方法,其中多个fsr中的每个fsr中的流水线包括数据线管

线、帧地址寄存器(far)管线和控制管线,其中数据线管线传播配置数据,far管线传播地址信息,以及控制管线传播用于锁存数据线管线和far管线的控制信号。

28.可以参考以下详细描述来理解这些和其他方面。

附图说明

29.为了能够详细理解上述特征的方式,可通过参考示例实施来进行上文简要总结的更具体的描述,其中一些示例实施在附图中示出。然而,应注意,附图仅示出了典型的示例实施,因此不应被视为限制其范围。

30.图1a是示出根据一个示例的可编程设备的框图。

31.图1b是示出根据一个示例的可编程ic的框图。

32.图1c是示出根据一个示例的可编程ic的soc实施的框图。

33.图1d示出了根据一个示例的包括pl的可编程ic的现场可编程门阵列(fpga)实施。

34.图2是示出根据一个示例的配置子系统的框图。

35.图3是示出根据一个示例的配置流水线的框图。

36.图4是示出根据一个示例的配置存储器读取/写入流水线单元的框图。

37.图5是示出根据一个示例的写入操作的示意图。

38.图6是示出根据一个示例的读取操作的示意图。

39.图7是示出根据一个示例的配置可编程设备的方法的流程图。

40.为了便于理解,在可能的情况下使用相同的参考标号来表示附图共同的相同元素。可以设想,一个示例的元素可有益地并入其他示例。

具体实施方式

41.下文参考附图描述各种特征。应当注意,附图可以按比例绘制,也可以不按比例绘制,并且贯穿附图由类似的参考标号来表示类似结构或功能的元素。应该注意,附图仅用于方便描述特征。它们不是对所要求保护发明的详尽描述,也不是对所要求保护发明的范围的限制。此外,所示示例不需要示出所示的方面或优点。结合特定示例描述的方面或优点不一定限于该示例,并且即使未如此说明或未如此明确描述,也可以在任何其他示例中实践。

42.描述了用于在可编程设备中提供配置存储器系统的技术。在示例中,配置存储器系统使用独特的结构,以将双向数据线与源时钟连接(pipeline),从而实现比以前的配置存储器系统更好的性能,同时最小化面积和成本。本文所述的配置存储器系统可有益于利用部分重配置的各种应用(包括人工智能(ai)、数据中心、汽车应用)以及需要通过配置存储器系统进行快速设备状态读回的应用(诸如仿真应用)。这些和其他方面将在下文结合附图进行描述。

43.图1a是示出根据一个示例的可编程设备54的框图。可编程设备54包括多个可编程集成电路(ic)1,例如可编程ic 1a、1b、1c和1d。在一个示例中,每个可编程ic 1是设置在中介片(interposer)90上的ic管芯。每个可编程ic 1都包括可编程设备54的超级逻辑区(slr)53,例如,slr 53a、53b、53c和53d。可编程ic 1通过中介片90上的导体(称为超长线路(sll)52)互连。

44.图1b是示出根据一个示例的可编程ic 1的框图。可编程ic 1可用于在可编程设备

54中实施可编程设备128或可编程ic 1a-1d之一。可编程ic 1包括可编程逻辑3(也称为可编程构造)、配置逻辑25和配置存储器26。可编程ic 1可耦合到外部电路,诸如非易失性存储器27、dram 28和其他电路29。可编程逻辑3包括逻辑单元30、支持电路31和可编程互连32。逻辑单元30包括可被配置为实施多个输入的一般逻辑功能的电路。支持电路31包括专用电路,诸如收发器、输入/输出块、数字信号处理器、存储器等。逻辑单元和支持电路31可使用可编程互连32而互连。通过配置逻辑25,将用于编程逻辑单元30、用于设置支持电路31以及用于编程可编程互连32的信息存储在配置存储器26中。配置存储器26被组织成多个帧95。配置逻辑25可从非易失性存储器27或任何其他源(例如,dram 28或其他电路29)获取配置数据。在一些示例中,可编程ic 1包括处理系统2。处理系统2可包括微处理器、存储器、支持电路、io电路等。在一些示例中,可编程ic 1包括片上网络(noc)55和数据处理引擎(dpe)阵列56。noc 55被配置为提供可编程ic 1的子系统之间的通信,诸如ps 2、pl 3和dpe阵列56之间的通信。dpe阵列56可包括被配置为执行数据处理的dpe阵列,诸如向量处理器阵列。

45.图1c是示出根据一个示例的可编程ic 1的soc实施的框图。在该示例中,可编程ic 1包括处理系统2和可编程逻辑3。处理系统2包括各种处理单元,诸如实时处理单元(rpu)4、应用处理单元(apu)5、图形处理单元(gpu)6、配置和安全单元(csu)12、平台管理单元(pmu)11等。处理系统2还包括各种支持电路,诸如片上存储器(ocm)14、收发器7、外围设备8、互连16、dma电路9、存储器控制器10、外围设备15和多路复用io(mio)电路13。处理单元和支持电路通过互连16而互连。pl 3还耦合到互连16。收发器7被耦合到外部引脚24。pl 3被耦合到外部引脚23。存储器控制器10被耦合到外部引脚22。mio 13被耦合到外部引脚20。ps 2通常被耦合到外部引脚21。apu 5可包括cpu 17、存储器18和支持电路19。

46.参照ps 2,每个处理单元都包括一个或多个中央处理单元(cpu)和相关电路,诸如存储器、中断控制器、直接存储访问(dma)控制器、存储器管理单元(mmu)、浮点单元(fpu)等。互连16包括各种开关、总线、通信链路等,其被配置为互连处理单元以及将ps 2中的其他部件互连到处理单元。

47.ocm 14包括一个或多个ram模块,它们可分布在整个ps 2中。例如,ocm 14可包括电池备份ram(bbram)、紧耦合存储器(tcm)等。存储器控制器10可包括用于访问外部dram的dram接口。外围设备8、15可包括一个或多个向ps 2提供接口的部件。例如,外围设备15可包括图形处理单元(gpu)、显示接口(例如,显示端口、高清多媒体接口(hdmi)端口等)、通用串行总线(usb)端口、以太网端口、通用异步收发器(uart)端口、串行外围接口(spi)端口、通用io(gpio)端口、串行高级技术附件(sata)端口、pcie端口等。外围设备15可被耦合到mio 13。外围设备8可被耦合到收发器7。收发器7可包括串行器/反串行器(serdes)电路、数千兆位收发器(mgt)等。

48.图1d示出了包括pl 3的可编程ic 1的现场可编程门阵列(fpga)实施。图1d所示的pl 3可用于本文所述的可编程设备的任何示例中。pl 3包括大量不同的可编程块(tile),包括收发器37、可配置逻辑块(“clb”)33、随机存取存储器块(“bram”)34、输入/输出块(“iob”)36、配置和时钟逻辑(“config/clocks”)42、数字信号处理块(“dsp”)35、专用输入/输出块(“i/o”)41(例如,配置端口和时钟端口)和其他可编程逻辑39,诸如数字时钟管理器、模数转换器、系统监控逻辑等。pl 3还可以包括pcie接口40、模数转换器(adc)38等。

49.在一些pl中,每个可编程块(tile)可包括至少一个可编程互连元件(“int”)43,其

连接到同一块中的可编程逻辑元件的输入和输出端子48,如图1d顶部包括的示例所示。每个可编程互连元件43还可以包括到同一块或其他块中的相邻可编程互连元件的互连段49的连接。每个可编程互连元件43还可以包括到逻辑块(未示出)之间的一般路由资源的互连段50的连接。一般路由资源可包括逻辑块(未示出)之间的路由通道,包括互连段(例如,互连段50)的轨道和用于连接互连段的开关块(未示出)。一般路由资源的互连段(例如,互连段50)可跨越一个或多个逻辑块。可编程互连元件43与一般路由资源一起实施用于所示pl的可编程互连结构(“可编程互连”)。

50.在示例实施中,clb 33可包括可被编程以实施用户逻辑的可配置逻辑元件(“cle”)44加上单个可编程互连元件(“int”)43。除一个或多个可编程互连元件之外,bram 34还可以包括bram逻辑元件(“brl”)45。通常地,块中包括的互连元件的数目取决于块的高度。在所示示例中,bram块的高度与五个clb相同,但也可以使用其他数目(例如,四个)。除适当数目的可编程互连元件之外,dsp块35还可以包括dsp逻辑元件(“dspl”)46。例如,除可编程互连元件43的一个实例之外,iob 36还可以包括输入/输出逻辑元件(“iol”)47的两个实例。本领域技术人员应理解,例如连接到i/o逻辑元件47的实际i/o焊盘通常不限于输入/输出逻辑元件47的区域。

51.在所示示例中,靠近管芯中心的水平区域(如图1d所示)用于配置、时钟和其他控制逻辑。从该水平区域或列延伸的垂直列51用于在pl的宽度上分布时钟和配置信号。

52.利用图1d所示架构的一些pl包括破坏构成pl的大部分的规则柱状结构的附加逻辑块。附加逻辑块可以是可编程块和/或专用逻辑。注意,图1d旨在仅说明示例性pl架构。例如,一行中逻辑块的数目、行的相对宽度、行的数目和顺序、包括在行中的逻辑块的类型、逻辑块的相对大小以及包括在图1d顶部的互连/逻辑实施纯粹是示例性的。例如,在实际pl中,通常在clb出现的地方包括多个相邻的clb行,以促进用户逻辑的有效实施,但是相邻clb行的数目随着pl的总体大小而变化。

53.图2是示出根据一个示例的配置子系统200的框图。例如,配置子系统200设置在可编程ic 1中,以在其中配置可编程逻辑。配置子系统200包括配置存储器读取/写入单元(本文称为cframe单元(cfu)202)、多个配置存储器读取/写入控制器(本文称为cframe引擎204)、多个配置存储器读取/写入流水线单元(本文称为cpipe 206)以及构造子区域(fsr)208中的配置存储单元。cfu 202可设置在可编程ic 1的平台管理控制器或类似部件(例如,pmu 11)中。cfu 202被配置为接收可编程ic的输入配置数据。cfu 202用作用于配置子系统200的主配置控制器。

54.cfu 202被耦合到每个cframe引擎204。每个cframe引擎204都包括配置帧写入/读取控制器。“帧”是将被存储到配置存储器单元的集合或者从中读取的配置数据的单位。一帧所具有的“高度”基于其包含数据的配置存储器单元的数目。每个cframe引擎204通过包括cpipe 206和fsr 208的流水线向一个或多个fsr 208提供数据。下文将进一步描述cpipe 206。每个fsr 208都是具有帧高度的可编程逻辑和相关配置存储器的区域。

55.图3是示出根据一个示例的配置流水线300的框图。配置流水线300包括cframe引擎204和一个或多个fsr 208(例如,所示为两个)。每个fsr 208都包括缓冲器(cbrk 302)、配置存储器单元(mem单元304)和cpipe 206。每个cbrk 302都包括双向缓冲器。mem单元304被设置在cbrk 302之间。通常,每个fsr 208都包括一个或多个cbrk 302,其中mem单元304

设置在它们之间。在操作中,通过cbrk302将配置数据从cframe引擎204提供给mem单元304。在一个示例中,每个fsr 208都包括cpipe 206(例如,设置在cbrk存储单元链的末端)。在没有cpipe 206的情况下,数据线在fsr 208的整个宽度上运行,这限制了配置存储器的写入/读取带宽。通过根据fsr208添加cpipe 206,在连续的cpipe 206之间分割数据线。数据线段小于fsr 208的宽度,这提高了配置存储器的写入/读取带宽。

56.图4是示出根据一个示例的cpipe 206的框图。cpipe 206包括缓冲器402、触发器404、多路复用器406、反相器408、反相器410、反相器412和缓冲器414。多路复用器406的输入(“1”)被耦合到cframe引擎204(例如,直接或通过其他部件)。多路复用器406的另一输入(“0”)被耦合到反相器408的输出。多路复用器406的控制输入被耦合到控制信号c2。多路复用器406的输出被耦合到触发器404的输入。触发器404的输出被耦合到缓冲器402的输入。缓冲器402的输出被耦合到cframe引擎204(例如,直接或通过其他部件)。在一个示例中,缓冲器402是三态缓冲器,并且包括耦合到控制信号c1的控制输入。

57.触发器404的输出被耦合到缓冲器414的输入。缓冲器414的输出被耦合到cbrk 302。在一个示例中,缓冲器414是三态缓冲器,并且包括耦合到控制信号c3的控制输入。反相器412的输入被耦合到cbrk 302。反相器412的输出被耦合到反相器408的输入。反相器410的输入被耦合到反相器412的输出。反相器410的输出被耦合到cbrk302。在一个示例中,反相器410是三态反相器,并且包括耦合到信号c4的控制输入。在图4中,示出了一条数据线的电路。对穿过cpipe206的每条数据线重复该电路。

58.在操作中,在写入期间,配置数据耦合到多路复用器406的“1”输入。控制信号c2被设置为选择多路复用器406的“1”输入。配置数据存储在触发器404中,然后通过缓冲器414被cbrk 302接收。控制信号c3被设置为使能缓冲器414。控制信号c4被设置为禁用反相器410。以这种方式,配置数据从cframe引擎204经由cpipe 206传递到cbrk 302,用于写入配置存储器。

59.在读取期间,回读数据被耦合到多路复用器406的“0”输入。具体地,反相器412和反相器410形成用于锁存来自cbrk 302的回读数据的锁存器。被锁存的回读数据通过反相器408被耦合到多路复用器406的“0”输入。控制信号c4被设置为使能反相器410,因此使能锁存器。控制信号c2被设置为选择多路复用器406的“0”输入。回读数据被存储在触发器404中,并且通过缓冲器402被cframe引擎204读取。控制信号c1被设置为使能缓冲器402。控制信号c3被设置为禁用缓冲器414。以这种方式,回读数据从cbrk 302传递到cframe引擎204,用于从配置存储器进行读取。

60.图5是示出根据一个示例的写入操作的示意图。图中心的圆圈(标记为ctrl管线)是符号流水线级,用于匹配数据线传播延迟。在一个示例中,有三种类型的管线:数据线管线502(标记为data管线)、帧地址寄存器(far)管线504(标记为far管线)和ctrl管线506。data管线502传播配置数据,far管线504传播要被配置的配置存储器的地址信息,以及ctrl管线506传播用于锁存数据管线和far管线504的控制信号。

61.在写入操作期间,cframe引擎204生成写入波形,其包括帧数据和必要的控制信号/序列。现在,整个波形必须在锁步中通过cpipe 206传播。控制信号路径包括额外的流水线级,以匹配数据线传播时间。数据线流水线502是多周期路径,因此标签/令牌用于在其稳定之后在cpipe 206处锁存数据线值。每个fsr 208本地地解码帧地址,以确定波形是否用

于它。波形从cframe引擎204流向设备边缘,而与目标帧位置无关。

62.图6是示出根据一个示例的读取操作的示意图。cframe引擎生成的读取波形(无数据)、far 504、控制506和rdata_tag 602传播到设备的边缘。数据线502传播回cframe引擎204。每个帧对读取的far进行解码,并且将从帧读取中只获得活动帧。读取的数据被rdata_tag捕获到cpipe中,然后传播回cframe引擎204。在图6中,far和控制没有在图中心示出额外的圆圈,因为在读操作期间不需要像在写入操作期间那样匹配数据线传播。在示例中,可以为far和控制添加额外的流水线级,就像写入操作为了定时或降噪目的所添加的一样。多路复用器(mux)被设置为每个fsr多路复用rdata_tag和读取波形。

63.由于rdata_tag针对时钟运行(从cframe引擎204到设备边缘),所以标签必须至少为两个时钟宽,以确保不被下一个cframe的同步器错过。在同步之后,rdata_tag被伸缩回至少两个时钟宽。rdata_tag用于在数据线上锁存缓慢传播的读取数据。存在rdata_tag的附加圆圈以匹配传播延迟。

64.本文描述的配置系统使用源时钟。由于其分布式特性,配置系统不使用时钟树。一旦事务离开cframe引擎204,很难停止流水线。因此,cframe引擎204必须解析它接收到的传入事务,并监督流水线的流量,以确保流水线不会溢出。分布式流水线也会产生读取风险情况。如果新的读取比先前的读取更接近cframe引擎204,则读取的数据可发生冲突。因此,cframe引擎204可检测到这种风险,并根据需要延迟新事务。

65.对于帧寻址,在以前的系统中,帧地址基于列/主地址。即,每一块都有其唯一的列/主地址,并且在每一列中具有n个帧。一旦达到n帧,列/主地址将基于反馈信号递增。本文描述的配置系统使用线性地址方案,这消除了与上述先前方案相关联的任何性能限制。

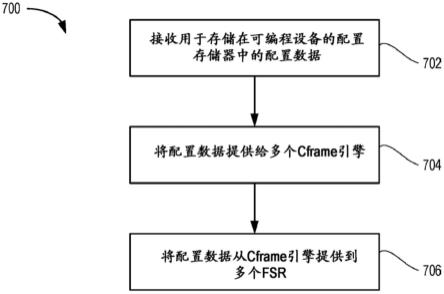

66.图7是示出根据一个示例的配置可编程设备的方法700的流程图。方法700从步骤702开始,其中cfu 202接收用于存储在可编程设备1的配置存储器26中的配置数据。配置存储器26包括多个帧95。在步骤704中,cfu 202向耦合到cfu 202的多个cframe引擎204提供配置数据。在步骤706中,cframe引擎204向多个fsr 208提供配置数据。每个fsr 208都包括设置在缓冲器(cbrk 302)之间的配置存储器的存储器单元304的流水线以及耦合在该流水线和下一个fsr 208之间的cpipe电路206。

67.虽然前述内容针对具体示例,但在不脱离其基本范围的情况下,可设想其他和进一步的示例,并且其范围由以下权利要求确定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。