1.本发明是关于脑电采集,特别是关于一种脑电采集模块及其应用系统。

背景技术:

2.市面上现有的八导联脑电模块所用芯片基本依赖于进口,国外进口芯片在国内市场上基本处于垄断地位,价格高昂,供货周期长且存在随时断货的风险,若没有可替代的国产方案,国内该领域将一直处于被动地位。

3.公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

4.本发明的目的在于提供一种脑电采集模块及其应用系统,其供货周期短、不存在断货风险且打破了国外芯片的垄断地位。

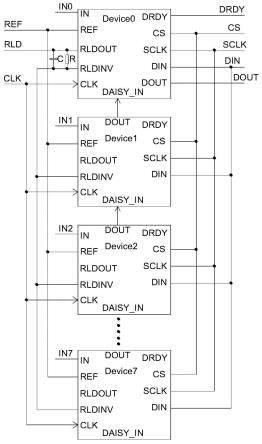

5.为实现上述目的,本发明的实施例提供了一种脑电采集模块,包括多个心电采集芯片,所述心电采集芯片采用菊花链模式相互连接,从而形成多路脑电数据采集通道。

6.在本发明的一个或多个实施方式中,所述心电采集芯片包括主心电采集芯片和从心电采集芯片,所述心电采集芯片均由一个片选信号控制。

7.在本发明的一个或多个实施方式中,所述主心电采集芯片的daisy_in引脚与所述从心电采集芯片的dout引脚相连,各所述从心电采集芯片之间均通过daisy_in引脚和dout引脚相连的方式形成串联,所述主心电采集芯片的dout引脚用于输出数据信号。

8.在本发明的一个或多个实施方式中,所述心电采集芯片的rldinv引脚相连,所述主心电采集芯片的rldout引脚用于接收右腿驱动信号。

9.在本发明的一个或多个实施方式中,所述主心电采集芯片和从心电采集芯片的cs引脚相连。

10.在本发明的一个或多个实施方式中,所述心电采集芯片具有对应的in采集引脚,所述in采集引脚对应连接所述心电采集芯片内部的pga放大器的正输入端,所述心电采集芯片的ref引脚相连,所述ref引脚对应连接所述心电采集芯片内部的pga放大器的负输入端。

11.在本发明的一个或多个实施方式中,所述心电采集芯片的clk引脚相连,所述心电采集芯片的sclk引脚相连,所述心电采集芯片的din引脚相连。

12.在本发明的一个或多个实施方式中,所述心电采集芯片为lh1291心电采集芯片。

13.在本发明的另一个或多个实施方式中,一种脑电采集模块的应用系统,包括所述脑电采集模块,所述脑电采集模块与晶振以及单片机mcu连接,所述脑电采集模块用于采集脑电数据信号并在时钟信号的控制下将脑电数据信号输入至所述单片机mcu。

14.在本发明的一个或多个实施方式中,所述脑电采集模块的各in采集引脚、ref引脚和rld引脚均分别与滤波电路连接。

15.与现有技术相比,根据本发明实施方式的脑电采集模块,采用菊花链模式将多个心电采集芯片进行连接,具有功耗低、性价比高的特点。同时,能够降低总成本,总成本不到现有方案的1/3;能够降低供货周期,不存在断货风险;所采用的元器件均是国产,打破了国外芯片的垄断地位。

附图说明

16.图1是根据本发明一实施方式的脑电采集模块的原理框图;

17.图2是根据本发明一实施方式的spi数据读取时序图;

18.图3是根据本发明一实施方式的脑电采集模块的应用系统框图。

具体实施方式

19.下面结合附图,对本发明的具体实施方式进行详细描述,但应当理解本发明的保护范围并不受具体实施方式的限制。

20.除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

21.如图1所示,根据本发明优选实施方式的一种脑电采集模块,包括多个心电采集芯片,心电采集芯片采用菊花链模式相互连接,从而形成多路脑电数据采集通道。一实施方式中,心电采集芯片采用八个,分别对应device0、device1、device2~

···

device7。八个心电采集芯片均具有in采集引脚,分别对应in0、in1、in2~

···

in7,从而形成八路脑电数据采集通道。

22.一实施方式中,心电采集芯片为lh1291心电采集芯片。该型号的心电采集芯片应用于心电领域,是超低功耗、高精度心电测量afe,集成了24位σ-δadc及可编程增益放大器,还包含右腿驱动等功能,150hz带内噪声3uvpp。经实际使用测试,可以最大程度的还原出微伏级信号源,且通过该芯片采集到的脑电数据信号经算法处理,可解析出专注度,冥想度,睁、闭眼状态等信息,由此验证该芯片性能满足脑电数据信号采集需求。lh1291心电采集芯片通过spi接口进行数据收发,通过菊花链模式将多个lh1291心电采集芯片连接在一起。

23.在八个心电采集芯片device0、device1、device2~

···

device7中选择一个心电采集芯片为主心电采集芯片,其余心电采集芯片均为从心电采集芯片,所有心电采集芯片均由一个片选信号控制。一实施方式中,心电采集芯片device0作为主心电采集芯片。心电采集芯片device1、device2~

···

device7作为从心电采集芯片。

24.如图1所示,主心电采集芯片的daisy_in引脚与从心电采集芯片的dout引脚相连,各从心电采集芯片之间均通过daisy_in引脚和dout引脚相连的方式形成串联,主心电采集芯片的dout引脚用于输出数据信号。一实施方式中,七个从心电采集芯片之间的连接方式为:心电采集芯片device7的daisy_in引脚与心电采集芯片device6的dout引脚相连。心电采集芯片device6的daisy_in引脚与心电采集芯片device5的dout引脚相连。采用此种方式依次连接,最终,心电采集芯片device2的daisy_in引脚与心电采集芯片device1的dout引脚相连。从心电采集芯片与主心电采集芯片的连接方式为:心电采集芯片device1的dout引

脚与心电采集芯片device0的daisy_in引脚连接。心电采集芯片device0的dout引脚用于输出脑电数据信号。

25.心电采集芯片device0、device1、device2~

···

device7对应的in采集引脚in0、in1、in2~

···

in7与该心电采集芯片内部的pga放大器的正输入端连接。心电采集芯片device0、device1、device2~

···

device7对应的ref引脚与该心电采集芯片内部的pga放大器的负输入端连接。同时,心电采集芯片device0、device1、device2~

···

device7对应的ref引脚均相连,从而形成共同控制。

26.心电采集芯片device0、device1、device2~

···

device7的rldinv引脚相连。主心电采集芯片的rldout引脚与rldinv引脚之间连接有电容c以及电阻r。主心电采集芯片的rldout引脚用于接收右腿驱动信号rld,通过右腿驱动信号rld能够消除由人体引入的共模噪声。

27.主心电采集芯片的cs引脚和从心电采集芯片的cs引脚均相连。心电采集芯片的sclk引脚相连。心电采集芯片的din引脚相连。心电采集芯片的clk引脚相连。

28.如图1和图2所示,心电采集芯片device0、device1、device2~

···

device7通过din引脚相连以及sclk引脚相连而共享din和sclk信号。使用菊花链模式,需要设置spi_ctrl寄存器中的daisy_en位来启用菊花链模式。将主心电采集芯片的daisy_in引脚连接到下一个从心电采集芯片的dout引脚,从而创建一个链。在sclk时钟信号为上升沿时,数据会在dout引脚上往所在的lh1291心电采集芯片外部移出。在sclk时钟信号为下降沿时,会将数据锁存到链中对应的心电采集芯片的daisy_in引脚上。在使用菊花链模式时,多读回功能不可用,寄存器读回(rreg)仅对菊花链模式中的主心电采集芯片有效。

29.如图3所示,一种脑电采集模块的应用系统,包括脑电采集模块,该脑电采集模块为将八个心电采集芯片device0、device1、device2~

···

device7封装后形成的模块。封装后的脑电采集模块的尺寸为20*20mm,封装后的脑电采集模块上可以焊接屏蔽罩,保证脑电采集模块不受外界噪声干扰。

30.脑电采集模块与晶振x以及单片机mcu连接,脑电采集模块用于采集脑电数据信号并接收右腿驱动信号,脑电采集模块在时钟信号的控制下将脑电数据信号输入至单片机mcu。

31.一实施方式中,脑电采集模块上形成有in0~in7测量引脚、ref引脚、rld引脚、clk引脚、drdy引脚、cs引脚、sclk引脚、din引脚和dout引脚。脑电采集模块的in0~in7测量引脚对应于所有心电采集芯片的in采集引脚。脑电采集模块的ref引脚对应于所有心电采集芯片的ref引脚。脑电采集模块的rld引脚对应于主心电采集芯片的rldout引脚。脑电采集模块的clk引脚对应于所有心电采集芯片的clk引脚。脑电采集模块的drdy引脚对应于主心电采集芯片的drdy引脚。脑电采集模块的cs引脚对应于所有心电采集芯片的cs引脚。脑电采集模块的sclk引脚对应于所有心电采集芯片的sclk引脚。脑电采集模块的din引脚对应于所有心电采集芯片的din引脚。脑电采集模块的dout引脚对应于主心电采集芯片的dout引脚。

32.各in采集引脚in0~in7、ref引脚和rld引脚均分别与滤波电路的输出端连接。脑电采集模块的drdy引脚、cs引脚、sclk引脚、din引脚、dout引脚与单片机mcu连接。脑电采集模块的clk引脚与晶振x连接。为保证sclk时钟信号的精度和稳定性,采用高精度、低飘移的

晶振x。

33.如图3和图2所示,八个通道的脑电数据经过对应的滤波电路进入脑电采集模块。脑电数据经对应的心电采集芯片内部的pga放大器的放大以及模数转化模块的转换后,心电采集芯片device0的drdy引脚产生低电平中断信号,此时单片机mcu通过spi管脚读取八个通道的原始脑电数据,进行后续的数据处理和应用。

34.在sclk时钟信号为上升沿时,数据从dout引脚输出。在sclk时钟信号为下降沿时,数据锁存到daisy_in引脚。单片机mcu读取数据时,首先读取心电采集芯片device0中转换出的原始数据,数据高位在前,低位在后。而后是心电采集芯片device1中的原始数据,直到最后一个心电采集芯片的数据读取完成,即得到八个通道的原始脑电数据。

35.本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机程序产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

36.本发明是参照根据本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

37.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

38.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

39.前述对本发明的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本发明限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本发明的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本发明的各种不同的示例性实施方案以及各种不同的选择和改变。本发明的范围意在由权利要求书及其等同形式所限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。