1.本发明属于半导体技术领域,尤其涉及一种氧化镓垂直场效应晶体管制备方法及场效应晶体管。

背景技术:

2.超宽禁带氧化镓作为一种新的半导体材料,在击穿场强、巴利加(baliga)优值和成本等方面优势突出。β-ga2o3材料巴利加优值是gan(氮化镓)材料的4倍,是sic(碳化硅)材料的10倍,是si材料的3444倍。β-ga2o3功率器件与gan和sic器件相同耐压情况下,导通电阻更低,功耗更小,能够极大地降低器件工作时的电能损耗。

3.现有技术中,ga2o3场效应晶体管(fet)多为横向器件,而商用市场更偏向于采用纵向mosfet功率器件。然而,由于ga2o3难以实现有效的p型掺杂,ga2o3纵向mosfet制备十分困难。

技术实现要素:

4.有鉴于此,本发明实施例提供了一种氧化镓垂直场效应晶体管制备方法及场效应晶体管,以解决现有技术中,纵向ga2o3场效应晶体管器件制备困难的问题。

5.本发明实施例的第一方面提供了一种氧化镓垂直场效应晶体管制备方法,包括:

6.在氧化镓衬底的上表面生长氧化镓沟道层;

7.对氧化镓沟道层进行离子注入掺杂,形成源区;其中,离子注入的深度小于氧化镓沟道层的厚度;

8.在氧化镓沟道层上依次生长源电极层及掩膜层;

9.对源电极层上及氧化镓沟道层上未被掩膜层覆盖的区域进行刻蚀,形成沟槽;其中,氧化镓沟道层的刻蚀深度小于氧化镓沟道层的厚度,且大于离子注入的深度;

10.在沟槽及掩膜层上生长p型介质层;

11.在p型介质层上生长栅电极层;

12.去除掩膜层;

13.在氧化镓衬底的下表面制备漏电极。

14.可选的,在在沟槽及掩膜层上生长p型介质层之后,方法还包括:

15.在p型介质层上生长栅介质层;

16.在p型介质层上生长栅电极层,包括:

17.在栅介质层上生长栅电极层。

18.可选的,去除掩膜层,包括:

19.在沟槽内形成光刻胶层;

20.采用湿法腐蚀去除掩膜层;

21.去除光刻胶层。

22.可选的,在p型介质层上生长栅介质层包括:

23.采用ald或pecvd法在p型介质层上生长栅介质层。

24.可选的,氧化镓衬底的掺杂浓度大于1.0

×

10

18

cm-3

,氧化镓沟道层的掺杂浓度小于1.0

×

10

18

cm-3

。

25.可选的,源电极层自下而上依次包括:第一金属层和第二金属层;

26.第一金属层与氧化镓沟道层之间欧姆接触;

27.第二金属层与掩膜层接触。

28.可选的,第一金属层的形成材料为ti,第二金属层的形成材料为au。

29.可选的,沟槽为矩形或梯形。

30.可选的,p型介质层的形成材料为nio

x

、sno2、cuo

x

、mno

x

、feo

x

、cumo2及znm2o4中的任意一种。

31.本发明实施例的第二方面提供了一种场效应晶体管,包括:

32.氧化镓衬底;

33.氧化镓沟道层,形成于氧化镓衬底的上表面,氧化镓沟道层远离氧化镓衬底的一侧设有多个沟槽;

34.p型介质层,形成于氧化镓沟道层上,且位于多个沟槽中;

35.栅电极层,形成于p型介质层上;

36.源电极层,形成于多个沟槽之间的凸台上;

37.漏电极层,形成于氧化镓衬底的下表面。

38.本发明实施例提供了一种氧化镓垂直场效应晶体管制备方法及场效应晶体管,上述方法包括:在氧化镓衬底的上生长氧化镓沟道层;对氧化镓沟道层进行离子注入掺杂,形成源区;其中,离子注入的深度小于氧化镓沟道层的厚度;在氧化镓沟道层上依次生长源电极层及掩膜层;对源电极层上及氧化镓沟道层上未被掩膜层覆盖的区域进行刻蚀,形成沟槽;其中,氧化镓沟道层的刻蚀深度小于氧化镓沟道层的厚度,且大于离子注入的深度;在沟槽及掩膜层上生长p型介质层;在p型介质层上生长栅电极层;去除掩膜层;在氧化镓衬底的下表面制备漏电极。本发明实施例采用自对准剥离技术,通过p型介质层形成pn结,制备过程简单,降低了垂直场效应晶体管的制备难度。

附图说明

39.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

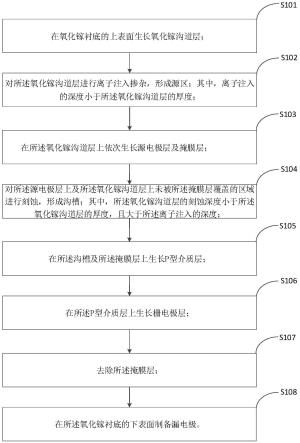

40.图1是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的实现流程示意图;

41.图2是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

42.图3是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

43.图4是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面

图;

44.图5是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

45.图6是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

46.图7是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

47.图8是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

48.图9是本发明实施例提供的一种氧化镓垂直场效应晶体管制备方法的工序截面图;

49.图10是本发明实施例提供的又一种氧化镓垂直场效应晶体管制备方法的工序截面图;

50.图11是本发明实施例提供的又一种氧化镓垂直场效应晶体管制备方法的工序截面图;

51.图12是本发明实施例提供的又一种氧化镓垂直场效应晶体管制备方法的工序截面图;

52.图13是本发明实施例提供的又一种氧化镓垂直场效应晶体管制备方法的工序截面图;

53.图14是本发明实施例提供的又一种氧化镓垂直场效应晶体管制备方法的工序截面图;

54.图15是本发明实施例提供的氧化镓垂直场效应晶体管的互联电极pad的示意图。

具体实施方式

55.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

56.为了说明本发明的技术方案,下面通过具体实施例来进行说明。

57.参考图1,本发明实施例提供了一种氧化镓垂直场效应晶体管制备方法,包括:

58.s101:在氧化镓衬底201的上表面生长氧化镓沟道层202;

59.s102:对氧化镓沟道层202进行离子注入掺杂,形成源区2021;其中,离子注入的深度小于氧化镓沟道层202的厚度;

60.s103:在氧化镓沟道层202上依次生长源电极层203及掩膜层204;

61.s104:对源电极层203上及氧化镓沟道层202上未被掩膜层204覆盖的区域进行刻蚀,形成沟槽300;其中,氧化镓沟道层202的刻蚀深度小于氧化镓沟道层202的厚度,且大于离子注入的深度;

62.s105:在沟槽300及掩膜层204上生长p型介质层205;

63.s106:在p型介质层205上生长栅电极层206;

64.s107:去除掩膜层204;

65.s108:在氧化镓衬底201的下表面制备漏电极207。

66.氧化镓(β-ga2o3)是一种新型直接带隙宽禁带半导体材料,具有禁带宽度大(4.9ev),击穿场强高(8mv/cm),在功率电子器件领域具有巨大的应用前景。本发明实施例提供了一种氧化镓垂直场效应晶体管制备方法,无需进行p型掺杂,p型介质层205与氧化镓形成pn结,同时采用自对准剥离技术实现器件制备,大幅降低了垂直场效应晶体管的制备难度。

67.同时,由于传统的栅电极下方具有一个尖峰电场,器件的击穿往往发生在这个区域,因此氧化镓场效应晶体管的击穿往往发生在栅电极下方。本发明实施例中,氧化镓场效应集体管的p型介质层与ga2o3形成异质pn结,对沟道载流子起到耗尽作用,从而调节器件阈值电压,并降低器件峰值场强,有效提高了场效应晶体管的耐压值。

68.具体的,氧化镓垂直场效应晶体管制备方法如下:

69.1,参考图2,在氧化镓衬底201的上表面生长氧化镓沟道层202。

70.一些实施例中,氧化镓衬底201和氧化镓沟道层202掺杂si或sn。

71.本发明实施例中,氧化镓衬底201为高掺杂的n型β-ga2o3层,氧化镓沟道层202为低掺杂的n型β-ga2o3层,氧化镓衬底201的掺杂浓度大于氧化镓沟道层202的掺杂浓度。氧化镓衬底201和氧化镓沟道层202作为导电层,提供载流子。

72.一些实施例中,氧化镓衬底201的掺杂浓度可以大于1.0

×

10

18

cm-3

;氧化镓沟道层202的掺杂浓度可以小于1.0

×

10

18

cm-3

。

73.一些实施例中,氧化镓衬底201和氧化镓沟道层202的掺杂浓度的取值范围可以为1.0

×

10

15

cm-3

~1.0

×

10

20

cm-3

。进一步的,二者的掺杂也可以为梯度变化。

74.一些实施例中,氧化镓衬底201和氧化镓沟道层202的厚度可以为10nm~1000μm。

75.2、参考图3,在对氧化镓沟道层202进行离子注入掺杂,并激活,形成源区2021;其中,离子注入的深度小于氧化镓沟道层202的厚度,保留氧化镓沟道层202的部分,同时部分离子注入,作为源区。

76.3、参考图4,在氧化镓沟道层202上依次生长源电极层203及掩膜层204。

77.其中,源电极层203和掩膜层204由金属形成,可采用电子束蒸法制备源电极层203及掩膜层204。

78.一些实施例中,源电极层203自下而上可以依次包括:第一金属层和第二金属层;

79.第一金属层与氧化镓沟道层202之间欧姆接触;

80.第二金属层与掩膜层204接触。

81.一些实施例中,第一金属层的形成材料可以为ti,第二金属层的形成材料可以为au。

82.本发明实施例中,源电极层203采用两层金属层形成,第一金属层采用ti,便于与氧化镓沟道层202形成欧姆接触。第二金属层采用au,便于与掩膜层204形成接触。

83.一些实施例中,掩膜层204的形成材料为ni。

84.ni作为金属掩膜,便于刻蚀。

85.4、参考图5,对源电极层203上及氧化镓沟道层202上未被掩膜层204覆盖的区域进行刻蚀,形成沟槽300。其中,刻蚀深度大于离子注入的深度,小于氧化镓沟道层202的深度,

使得离子注入的部分暴露出来,且保留部分氧化镓沟道层202,从而可以在沟槽300中布置栅电极,且栅电极与源电极不接触。

86.其中,采用干法刻蚀形成沟槽300。

87.一些实施例中,沟槽300可以为矩形或梯形。

88.5、参考图6及图7,在沟槽300及掩膜层204上生长p型介质层205和栅电极层206。刻蚀完成后不去除掩膜层204,直接在沟槽300及掩膜层204上制备p型介质层205和栅电极层206。

89.一些实施例中,p型介质层205的形成材料可以为nio

x

、sno2、cuo

x

、mno

x

、feo

x

、cumo2及znm2o4中的任意一种,厚度可以为10nm~1000nm。可采用溅射、pld、ald、ni自氧化中的任意一种方法制备p型介质层205。

90.一些实施例中,栅电极层206的厚度可以为50nm~10μm。栅电极层206的形成材料可以为pt或au。

91.6、参考图8,去除掩膜层204。

92.采用湿法腐蚀,选取合适的溶液与掩膜层204反应,从而去除掩膜层204而不损坏源电极。采用自对准技术,掩膜层204上的p型介质层205和栅电极层206随着掩膜层204一起剥离,仅保留沟槽300中的p型介质层205和栅电极层206,形成栅电极。

93.7、参考图9,在氧化镓衬底201的下表面制备漏电极207。

94.可以采用电子束蒸法制备漏电极207。

95.其中,漏电极207可以由多层金属形成,例如可以为ti和au,或ti、al、ni和au,用于与氧化镓衬底201形成欧姆接触。

96.一些实施例中,在s105之后,上述方法还可以包括:

97.s109:在p型介质层205上生长栅介质层208;

98.s106可以包括:在栅介质层208上生长栅电极层206。

99.一些实施例中,s107可以包括:

100.s1071:在沟槽300内形成光刻胶层209;

101.s1072:采用湿法腐蚀去除掩膜层204;

102.s1073:去除光刻胶层209。

103.本发明实施例中的场效应晶体管还可以包括栅介质层。基于以上,在图6所示的工序后还可以包括:

104.1、参考图10,在p型介质层205上生长栅介质层208。

105.栅介质层208的形成材料可以为al2o3、hfo2、sio2中的任意一种,也可以为al2o3和hfo2的复合介质。

106.一些实施例中,采用ald或pecvd法在p型介质层205上生长栅介质层208。

107.2、参考图11,在栅介质层208上生长栅电极层206。

108.其中,栅电极层206的厚度及形成材料等均同上。

109.3、参考图12及图13,由于栅介质层208的存在,为去除掩膜层204,同时使源电极暴露出来,在沟槽300内形成光刻胶层209,进而采用湿法腐蚀去除掩膜层204,再去除光刻胶层209,暴露出栅电极。其中,光刻胶层209的上表面应当与源电极层203的下表面齐平,保证源电极两侧的栅介质层208可以被去除,同时溶液不会腐蚀源区材料。

110.4、参考图14,同图9的工序,在氧化镓衬底201的下表面制备漏电极207。

111.一些实施例中,上述方法还可以包括:

112.s109:连接各个源电极。

113.参考图15,本发明实施例中,可在器件的侧面设置互联电极pad,以连接各个源电极。

114.对应于上述实施例,本发明实施例提供了一种场效应晶体管,采用如上述发明实施例提供的方法制备而成。

115.参考图9,本发明实施例还提供了一种场效应晶体管,包括:

116.氧化镓衬底201;

117.氧化镓沟道层202,形成于氧化镓衬底201的上表面,氧化镓沟道层202远离氧化镓衬底201的一侧设有多个沟槽300;

118.p型介质层205,形成于氧化镓沟道层202上,且位于多个沟槽300中;

119.栅电极层206,形成于p型介质层205上;

120.源电极层203,形成于多个沟槽300之间的凸台上;

121.漏电极207层,形成于氧化镓衬底201的下表面。

122.一些实施例中,上述场效应晶体管还包括:

123.栅介质层208,形成于p型介质层205上;

124.其中,栅电极层206,形成于栅介质层208之上。

125.以上实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。