1.本发明涉及半导体装置。

背景技术:

2.存在用于基于在部署在一个像素中的多个光电二极管中的每一个中产生的电荷来执行动态范围扩大、焦点检测、距离测量和深度信息获取的技术。

3.专利文献1公开了图像传感器以及用于图像传感器的像素电路(图3),该图像传感器包括各自具有多个嵌套的光电二极管(子像素)的像素。

4.非专利文献1公开了一种与根据专利文献1的像素电路类似的电路(图1),并公开了像素内的电路和低增益电容器布置在深度二极管的一部分上方。

5.引用列表

6.专利文献

7.ptl 1:美国专利申请公开no.2019/0131333

8.nptl 1:“pixel with nested photo diodes and 120db single exposure dynamic range”,manuel innocent,2019国际图像传感器研讨会第13页

技术实现要素:

9.技术问题

10.非专利文献1没有充分考虑电路组件的布置。取决于电路组件的布置,入射到像素的光和由光产生的电荷使电路操作不稳定,并且使从像素输出的信号的精度下降。因此,存在像素特性的劣化的问题。

11.本发明旨在提供有利于在半导体装置中获得优选的像素特性的技术。

12.问题的解决方案

13.作为用于解决上述问题的方法,提供了一种半导体装置,所述半导体装置包括半导体层,所述半导体层具有以矩阵形式布置的多个像素并且具有前表面和后表面。所述多个像素中的一个像素包括部署在半导体层中的多个光电二极管。通过将半导体层的后表面上的所述一个像素的光接收区域在行方向和列方向中的每个上划分成三个相等的区块而获得的九个区块包括第一区块和八个区块,所述八个区块包括第二区块、第三区块、第四区块、第五区块、第六区块、第七区块、第八区块和第九区块。第一区块位于第二区块和第三区块之间以及第四区块和第五区块之间。所述多个光电二极管的某个光电二极管中包括的第一光电转换构件部署在与后表面垂直的方向上与第一区块重叠的位置处。与所述某个光电二极管不同的光电二极管中包括的第二光电转换构件部署在与后表面垂直的方向上与第二区块重叠的位置处。与所述某个光电二极管不同的光电二极管中包括的第三光电转换构件部署在与后表面垂直的方向上与第三区块重叠的位置处。各自与半导体层一起形成金属-绝缘体-半导体mis结构的多个电极部署在半导体层的前表面上。所述多个电极中的至少一个电极在与后表面垂直的方向上与八个区块中的至少一个区块重叠。

14.本发明的有利效果

15.本发明使得能够提供有利于在半导体装置中获得优选的像素特性的技术。

附图说明

16.[图1a]图1a是图示了半导体装置的示例的示意图。

[0017]

[图1b]图1b是图示了半导体装置的示例的示意图。

[0018]

[图1c]图1c是图示了半导体装置的示例的示意图。

[0019]

[图2]图2是图示了半导体装置的示例的示意图。

[0020]

[图3]图3是图示了半导体装置的示例的示意图。

[0021]

[图4a]图4a是图示了半导体装置的示例的示意图。

[0022]

[图4b]图4b是图示了半导体装置的示例的示意图。

[0023]

[图5a]图5a是图示了半导体装置的示例的示意图。

[0024]

[图5b]图5b是图示了半导体装置的示例的示意图。

[0025]

[图6]图6是图示了半导体装置的示例的示意图。

[0026]

[图7]图7是图示了半导体装置的示例的示意图。

[0027]

[图8]图8是图示了半导体装置的示例的示意图。

[0028]

[图9a]图9a是图示了半导体装置的示例的示意图。

[0029]

[图9b]图9b是图示了半导体装置的示例的示意图。

[0030]

[图10]图10是图示了半导体装置的示例的示意图。

[0031]

[图11]图11是图示了半导体装置的示例的示意图。

[0032]

[图12]图12是图示了半导体装置的示例的示意图。

[0033]

[图13]图13是图示了半导体装置的示例的示意图。

[0034]

[图14]图14是图示了半导体装置的示例的示意图。

[0035]

[图15a]图15a是图示了半导体装置的示例的示意图。

[0036]

[图15b]图15b是图示了半导体装置的示例的示意图。

[0037]

[图16a]图16a是图示了具有半导体装置的设备的示例的示意图。

[0038]

[图16b]图16b是图示了具有半导体装置的设备的示例的示意图。

[0039]

[图16c]图16c是图示了具有半导体装置的设备的示例的示意图。

具体实施方式

[0040]

以下,将参考附图来描述本发明的示例性实施例。在以下的描述和图中,多个图中相同的组件被分配相同的参考符号。因此,以下将交叉参考多个图来描述相同的组件,并且将适当地省略被分配相同的参考符号的组件的描述。尽管被分配相同的名称的元件可以由提供给这些元件的参考符号来区别地表示,但元件也可以由先前序号来表示,例如,第一元件、第二元件和第n元件。

[0041]

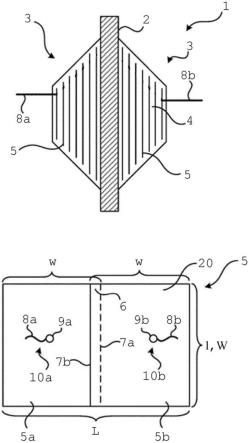

图1a和图1b是图示了主要包括半导体装置930中包括的以矩阵形式布置的多个像素之中的四个像素(呈2行2列)的区域的平面图。图1c是图示了沿着图1a中的s-s'线截取的半导体装置930的截面图。

[0042]

如图1c中图示的,半导体装置930包括具有前表面fs和后表面bs的半导体层10。后

表面bs是与前表面fs相对的表面,并且后表面bs和前表面fs大致彼此平行。图1a是图示了后表面bs的平面图,并且图1b是图示了前表面fs的平面图。半导体装置930是在后表面bs上具有光接收区域11的背面照明型半导体装置。平行于前表面fs和/或后表面bs的方向被称为x方向和y方向,并且垂直于前表面fs和/或后表面bs的方向被称为z方向。x方向是行方向和列方向中的一个,并且y方向是行方向和列方向中的另一个。在该示例中,x方向是行方向,并且y方向是列方向。然而,x方向可以是列方向,并且y方向可以是行方向。像素行包括布置在行方向(x方向)上的像素,并且像素列包括布置在列方向(y方向)上的像素。多个像素行布置在y方向(列方向)上,并且多个像素列布置在x方向(行方向)上。通过在列方向上扫描像素行来读取多个像素的信号,并且可以通过与像素列对应的多个列电路来处理读取的信号。

[0043]

x方向与y方向彼此相交(通常,垂直相交)。在该示例中,x方向、y方向与z方向彼此相交。当像素以方形格子形式布置时,行方向与列方向彼此垂直相交。然而,行方向和列方向可以不需要彼此垂直相交。像素阵列不限于方形格子,而可以是正交格子,菱形格子、中心矩形格子、等腰三角形格子、六边形格子、等边三角形格子、矩形格子、原始矩形格子,平行格子或扭曲倾斜格子。

[0044]

在以下描述中,z方向上“a与b重叠”的情况是指在z方向上a与b彼此重叠。半导体层10的厚度t是指半导体层10在z方向上的尺寸,并被定义为前表面fs与后表面bs之间的距离。例如,半导体层10的厚度t为1μm至10μm,通常2μm至5μm。平行于前表面fs并处于与半导体层10的前表面fs相距距离t/4处的虚拟平面被称为平面fq。平行于后表面bs并处于与半导体层10的后表面bs相距距离t/4处的虚拟平面被称为平面bq。平面fq与后表面bs之间的距离为t

×

3/4,并且平面bq与前表面fs之间的距离为t

×

3/4。与前表面fs和后表面bs平行并处于平面bq与平面fq之间的虚拟平面被称为平面hp。平面hp的通常位置与前表面fs和后表面bs等距。更具体地,平面hp与前表面fs之间的通常距离为t/2,并且平面hp与后表面bs之间的通常距离为t/2。

[0045]

多个像素中的至少一个像素(在该示例中,像素pr、像素pg和像素pb中的每一个)包括部署在半导体层10中的多个光电二极管pd1和pd2。光电二极管pd1和pd2可以具有嵌套的结构。更具体地,光电二极管pd2可以围绕光电二极管pd1。尽管在这种情况下,一个像素包括两个光电二极管,但一个像素可以包括三个或更多个光电二极管。嵌套的结构可以使得两个或更多个光电二极管围绕一个光电二极管pdl。在这种情况下,一个光电二极管pd1可以被夹在两个光电二极管之间。

[0046]

以下,将描述一个像素(作为示例的像素pg)的光接收区域11。半导体层10的后表面bs上的一个像素的光接收区域11在行(x)方向和列(y)方向中的每一个上被划分成三个相等的区块(section),以获得九个区块b1至b9。该九个区块被大致分组为区块b1以及其他八个区块b2、b3、b4、b5、b6、b7、b8和b9。区块b1位于区块b2和区块b3之间以及区块b4和区块b5之间。区块b1也位于区块b6和区块b7之间以及区块b8和区块b9之间。在该示例中,区块b2位于区块b6和区块b9之间,区块b3位于区块b8和区块b7之间,区块b4位于区块b6和区块b8之间,并且区块b5位于区块b7和区块b9之间。以这种方式,位于九个区块b1至区块b9的中心处的区块b1可以被称为中心区块。位于区块b1周围的八个区块b2至区块b9可以被称为周边区块。由于区块b1被八个区块b2至区块b9围绕,因此八个区块b2至区块b9也可以被称为外

部区块,并且区块b1也可以被称为内部区块。

[0047]

光电二极管pd1和pd2中的每一个具有光电转换构件。参考图1c,可以存在形成光电二极管pd1的光电转换构件的范围由双点划线围绕,并且可以存在形成光电二极管pd2的光电转换构件的范围由点划线围绕。图1a图示了存在于图1c中的平面hp上从而与后表面bs重叠的光电转换构件。图1b图示了存在于图1c中的平面hp上从而与前表面fs重叠的光电转换构件。当在图1a和图1b中双点划线围绕点划线时,形成光电二极管pd2的光电转换构件可以存在于点划线与双点划线之间的部分中。

[0048]

在以下的描述中,光电二极管pd1和pd2的光电转换构件是通过像素内的位置来区分的。多个光电二极管中的光电二极管pd2中包括的光电转换构件部署在在与后表面bs垂直的z方向上与区块b1重叠的位置处。多个光电二极管中的与光电二极管pd2不同的光电二极管(光电二极管pd1)中包括的光电转换构件部署在在与后表面bs垂直的z方向上与区块b2重叠的位置处。多个光电二极管中的与光电二极管pd2不同的光电二极管(光电二极管pd1)中包括的光电转换构件部署在在与后表面bs垂直的z方向上与区块b3重叠的位置处。同样,多个光电二极管中的与光电二极管pd2不同的光电二极管(光电二极管pd1)中包括的光电转换构件部署在在与后表面bs垂直的z方向上与区块b4至区块b9重叠的位置处。以这种方式,重要的是,至少与不同于光电二极管pd2的光电二极管(光电二极管pd1)对应的光电转换构件部署在与光电二极管pd2的光电转换构件对应的区块b1两侧的区块中。在该示例中,与作为外部区块的区块b2至区块b9重叠的多个光电转换构件中的每一个被包括在单个光电二极管pd1中。更具体地,光电二极管pd2包括与区块b1重叠的光电转换构件,并且光电二极管pd1包括与区块b2重叠的光电转换构件以及与区块b3重叠的光电转换构件。然而,与作为外部区块的区块b2至b9重叠的多个光电转换构件中的一部分的光电转换构件和其另一部分的光电转换构件可以被包括在不同的光电二极管中。例如,包括与区块b6、b2和b9重叠的光电转换构件的光电二极管可以不同于包括与b8、b3和b7重叠的光电转换构件的光电二极管。不同的光电二极管中包括的多个光电转换构件可以与一个区块重叠。例如,与区块b9侧的区块b5的一半重叠的光电转换构件可以与和区块b7侧的区块b5的一半重叠的光电转换构件分离。

[0049]

在半导体层10的前表面fs上,部署与半导体层10一起形成金属-绝缘体-半导体(mis)结构的多个电极25。电极25对应于mis结构的金属,并通常由多晶硅制成。然而,电极25可以由金属或诸如硅化物之类的金属化合物制成。mis结构可以不仅用作mis场效应晶体管(fet)的栅极,而且用作mis型电容器。形成晶体管的mis型栅极的电极25可以被称为栅电极,并且形成mis型电容器的电极25可以被称为电容器电极。传输的类型包括用于传输电荷的传输晶体管、用于执行开关的开关晶体管、以及用于执行放大的放大晶体管。作为传输晶体管的栅电极的电极25被称为传输电极。电极25的一部分可以用作布线或电阻器。mis结构的绝缘体例如是厚度为约1nm至10nm的氧化硅膜,并可以是诸如氧化铪膜之类的金属氧化物膜。作为mis结构的绝缘体的氧化硅膜可以包含比氧和硅的量少的氮的量(例如,10%原子或更少)。形成晶体管的mis型栅极的绝缘体被称为栅极绝缘膜。

[0050]

半导体层10的前表面fs包括元件区域12和13。元件区域12和13不仅包括具有mis结构的半导体区域,而且包括源极、漏极和阱(well)。元件区域12和13也可以被称为有源区。mis结构的半导体由半导体层10形成。具有绝缘体分离结构的元件分离部23部署在半导

体层10上的前表面fs侧。元件分离部23设置在元件区域12和13之间。元件分离部23限定元件区域12和13。绝缘体分离结构包括浅沟槽隔离(sti)结构和硅的局部氧化(locos)结构,并且sti结构是优选的。具有sti结构的元件分离部23的深度例如等于或大于电极25的厚度h的1/2倍并且等于或小于电极25的厚度h的10倍,优选地5倍,或更优选地2倍。元件分离部23的深度例如为50nm至500nm。电极25的厚度h例如为50nm至250nm。具有pn结分离结构的元件分离部可以部署在半导体层10中。元件分离可以仅由具有pn结分离结构的元件分离部执行,而不部署具有绝缘体分离结构的元件分离部23。

[0051]

多个电极25中的至少一个在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个重叠。以该方式部署电极25以便与八个区块b2至b9中的至少一个重叠使得能够获得优选的像素特性。

[0052]

如果对应于一个像素的所有电极25被部署为与区块b1重叠,则包括电极25的mis结构的操作因入射光和由入射光产生的电荷而不稳定。出于以下原因,与和区块b2至b9重叠的部分相比,与区块b1重叠的部分更有可能受光和电荷的影响。首先,由于区块b1位于像素的中心,因此与区块b2至b9相比,区块b1经受较大量的入射光。如果入射到周边区块b2至b9的光被漫射,则漫射光容易进入与区块b1重叠的部分。由于与区块b1重叠的光电二极管pd2的体积小,因此光电二极管pd2的电荷有可能从光电二极管pd2溢出。另外,从与区块b2至b9重叠的光电转换构件溢出的电荷与相邻的像素相比,更有可能流入同一像素中的与区块b1重叠的部分。

[0053]

如果对应于一个像素的所有电极25被部署为与九个区块b1至b9都不重叠,则多个像素的光接收区域之间的间隙增大。维持像素的数量使得需要减小光接收区域的面积,从而导致光利用效率降低。维持光接收区域的面积导致像素数量的减少和装置尺寸的增加。

[0054]

因此,通过将多个电极25的至少一部分部署为与区块b2至b9重叠,可以消除或减少与区块b1重叠的电极25,并且可以有效地利用与区块b2至b9重叠的区域。这使得能够获得优选的像素特性。例如,参考图1c,作为电极25之一的电极254与区块b2至b9中的任一个(例如,区块b4)重叠。

[0055]

多个电极25中的至少一个可以在与后表面bs垂直的z方向上与区块b1重叠。与区块b1重叠的电极25可以是多个电极25之中的与光电二极管pd2特别紧密相关的元件。例如,优选的是,具有光电二极管pd2作为源极的晶体管的栅电极与区块b1重叠。例如,参考图1c,作为电极25之一的电极251与区块b1重叠。

[0056]

与一个像素关联的多个电极25中的至少一个可以部署在垂直于前表面fs的方向上不与半导体层10的前表面fs上的一个像素的光接收区域11重叠的区域(非重叠区域)中。不与一个像素的光接收区域11重叠的非重叠区域可以是与其他像素的光接收区域11重叠的区域,或者可以是像素之间的遮光区域。例如,参考图1c,作为电极25之一的电极250与区块b1至b9都不重叠。例如,电极250是生成基于光电二极管pd1的电荷的信号和基于光电二极管pd2的电荷的信号的放大晶体管的栅电极。

[0057]

多个电极25中的至少一个可以在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个重叠,并且在垂直于前表面fs的z方向上与具有绝缘体分离结构的元件分离部23重叠。与元件分离部重叠的电极25可以是晶体管的栅电极,其沟道宽度期望需要受元件分离部23精确地控制。需要精确地控制沟道宽度的晶体管例如是将信号放大的放大晶体

管。例如,参考图1c,作为电极25之一的电极250与元件分离部23重叠。

[0058]

多个电极25中的至少一个不需要在垂直于后表面bs的z方向上与元件分离部23重叠。元件分离部23可能成为噪声源。因此,不与元件分离部23重叠的电极25可以是期望需要防止可能作为噪声的电荷的混合的晶体管的栅电极。期望需要防止可能作为噪声的电荷的混合的晶体管例如是传输电荷的传输晶体管。因此,利用传输晶体管,优选的是使用具有pn结分离结构的元件分离部,而不使用具有绝缘体分离结构的元件分离部23。例如,参考图1c,作为电极25的一部分的电极251和252不与元件分离部23重叠。

[0059]

在前表面fs上,部署有与半导体层10或电极25接触的多个接触插塞24。接触插塞24部署在设置在绝缘膜pmd中的接触孔中。接触插塞24可以包括由诸如钨之类的金属制成的导电构件、以及部署在导电构件与绝缘膜pmd之间并由诸如钛之类的金属和诸如氮化钛之类的金属化合物制成的阻挡金属构件。接触插塞24的阻挡金属构件可以与绝缘膜pmd和半导体层10接触。多个接触插塞24的一个部分可以被部署为与作为内部区块的区块b1重叠。多个接触插塞24的另一部分可以被部署为与作为外部区块的八个区块b2至b9中的至少任一个重叠。多个接触插塞24的另一部分可以被部署为与遮光区域重叠。

[0060]

在绝缘膜pmd上,部署与接触插塞24连接的布线层m1。布线层m1例如可以是具有单个波纹结构的铜布线层。在布线层m1的上方,部署通过通孔插塞与布线层m1连接的布线层m2。在布线层m2的上方,部署通过通孔插塞与布线层m2连接的布线层m3。布线层m2和m3可以是具有双波纹结构的铜布线层。布线层m1、m2和m3可以是铝布线层。层间绝缘膜ild部署在布线层m1、m2和m3之间。

[0061]

半导体装置930可以设置有基板sub。基板sub接合到包括布线层m1、m2和m3以及层间绝缘膜ild的多层布线结构。基板sub可以是没有诸如晶体管之类的有源元件的简单支撑基板,或者是包括形成集成电路的晶体管的集成电路基板。如果基板sub是集成电路基板,则通过使用诸如凸块、布线层之间的金属接合以及贯通电极之类的方法,布线层m1至m3中的任一个与基板sub彼此电连接。

[0062]

图1a中的左上部分处的像素pr是用于光电转换红光的红色像素,并且如图1c中图示的,包括红色滤色器cfr。图1a中的左下部分处的像素pg和右上部分处的像素是用于光电转换绿光的绿色像素,并且如图1c中图示的,包括绿色滤色器cfg。图1a中的右下部分处的像素pb是用于光电转换蓝光的蓝色像素,并且如图1c中图示的,包括蓝色滤色器cfb。因此,半导体装置930可以设置有包括在半导体层10的后表面bs上以拜耳阵列布置的滤色器cfr、cfg和cfb的滤色器阵列。滤色器cfr、cfg和cfb中的每一个在和这些滤色器相关联的像素的光接收区域11中的九个区块b1至b9之中在垂直于后表面bs的z方向上与至少四个区块重叠。该示例图示了滤色器cfr、cfg和cfb中的每一个与所有九个区块b1至b9重叠的像素区域的中心部分。为了使得光接收区域11能够在像素区域的周边接收倾斜的入射光,滤色器cfr、cfg和cfb中的每一个可以偏离光接收区域11的中心。在这种情况下,例如,滤色器cfr、cfg和cfb可以仅与四个区块b1、b3、b5和b7重叠,而不与区块b2、b4、b6、b8和b9重叠。优选的是,滤色器cfr、cfg和cfb中的每一个在和这些滤色器相关联的像素的光接收区域11之中与至少区块b1重叠。滤色器阵列使得能够提供能够获取彩色图像的半导体装置930。然而,在获取单色图像时,可以省略滤色器阵列。

[0063]

半导体装置930可以包括由通过滤色器阵列二维地布置在半导体层10的后表面bs

上方的多个微透镜mlr、mlg和mlb形成的微透镜阵列。微透镜mlr与像素pr关联,微透镜mlg与像素pg关联,并且微透镜mlb与像素pb关联。微透镜mlr、mlg和mlb中的每一个在和这些微透镜相关联的像素的光接收区域11中的九个区块b1至b9之中在垂直于后表面bs的z方向上与至少四个区块重叠。该示例图示了微透镜mlr、mlg和mlb中的每一个与所有九个区块b1至b9重叠的像素区域的中心部分。为了使得光接收区域11能够在像素区域的周边接收倾斜的入射光,微透镜mlr、mlg和mlb中的每一个可以偏离光接收区域11的中心。在这种情况下,例如,微透镜mlr、mlg和mlb可以仅与四个区块b1、b3、b5和b7重叠,而不与区块b2、b4、b6、b8和b9重叠。优选的是,微透镜mlr、mlg和mlb中的每一个在和这些滤色器相关联的像素的光接收区域11之中与至少区块b1重叠。如果每个像素的光接收区域11足够宽,则可以省略微透镜阵列。

[0064]

半导体装置930可以包括部署在半导体层10的后表面bs上的遮光部22。如图1a中图示的,遮光部22可以具有格子形状,以针对像素pr、pg和pb中的每一个限定后表面bs上的光接收区域11。在后表面bs中,与遮光部22重叠的区域是设置在光接收区域11外侧的遮光区域。在该示例中,在像素pg的光接收区域11和与像素pg相邻的像素pr的光接收区域11之间设置遮光区域,并且在像素pg的光接收区域11和与像素pg相邻的像素pr的光接收区域11之间设置遮光区域。遮光部22减少了后表面bs上的光学串扰(或颜色混合)。虽然在该示例中,遮光部22部署在滤色器cfr、cfg和cfb之间,但遮光部22可以部署在滤色器阵列和半导体层10之间。可以省略遮光部22。如果省略了遮光部22,则例如,在后表面bs上,像素pg的光接收区域11与和像素pg相邻的像素pr的光接收区域11是连续的,并且与和像素pg相邻的像素pb的光接收区域11也是连续的。

[0065]

在遮光部22的下方,半导体层10设置有在后表面bs上具有连续侧面的凹槽dt。凹槽dt的侧面不被包括在光接收区域11中。凹槽dt减少了半导体层10中的光学串扰和电串扰。优选的是,凹槽dt从后表面bs起的深度为半导体层100的厚度t的至少四分之一。更具体地,优选的是,凹槽dt穿过平面bq。优选的是,凹槽dt从后表面bs起的深度为半导体层100的厚度t的至少一半。更具体地,优选的是,凹槽dt穿过平面hp。凹槽dt可以与元件区域12重叠。凹槽dt也可以与元件区域13重叠。凹槽dt从后表面bs起的深度可以为半导体层100的厚度t的至少3/4倍。凹槽dt可以穿透半导体层100。然而,优选的是,在减少可能通过凹槽dt施加到部署在元件区域12和13中的元件(晶体管)的损坏和噪声时,凹槽dt从后表面bs起的深度小于半导体层100的厚度t的3/4倍。更具体地,优选的是,凹槽dt不穿过平面fq,并且平面fq设置在凹槽dt的底部和前表面fs之间。该配置使得能够减小凹槽dt对部署在前表面fs上的元件的影响。可以省略凹槽dt。如果省略了凹槽dt,则后表面bs在多个像素上是连续的。在后表面bs上,电介质膜21被部署以覆盖后表面bs。在该示例中,电介质膜21在凹槽dt中扩展,并覆盖凹槽dt的侧表面。代替在凹槽dt中提供电介质膜21,电介质膜21可以被部署为阻挡凹槽dt的入口。在这种情况下,在凹槽dt中可以存在空腔。电介质膜21可以是单层膜或多层膜。电介质膜21中包括的层是诸如氧化硅层和氮化硅层之类的硅化合物层,和/或诸如氧化铝层、氧化铪层、氧化钽层和氧化钛层之类的金属氧化物层。氧化铝层和氧化铪层可用于将在后表面bs附近产生的噪声电荷固定到后表面bs附近。氧化钽层和氧化钛层可用于防止后表面bs的光反射。尽管图示了后表面bs上的配置,但本发明不限于此。

[0066]

图2图示了作为从一个像素pg读取信号的像素电路300的示例的电路图。一个像素

pg可以包括多个光电二极管pd1、pd2和pd3。当光电二极管pd1和pd3具有比光电二极管pd2高的灵敏度时,像素电路300是优选的。然而,光电二极管pd1和pd3可以具有比光电二极管pd2低的灵敏度。传输栅极304连接到光电二极管pd1,传输栅极306连接到光电二极管pd2,并且传输栅极310连接到光电二极管pd3。传输栅极304包括用于将在光电二极管pd1的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷存储部fd的传输电极tx1。传输栅极306包括用于将在光电二极管pd2的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷存储部fd的传输电极tx2。传输栅极310包括用于将在光电二极管pd3的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷存储部fd的传输电极tx3。以上参考图1c描述的多个电极25包括这些传输电极tx1、tx2和tx3。例如,以上参考图1c描述的电极254例如是传输电极tx1,并且以上参考图1c描述的电极251例如是传输电极tx2。像素电路300可以被认为包括以传输栅极304、306和310作为栅极,以光电二极管pd1、pd2和pd3作为源极并且以电荷存储部fd作为漏极的三个不同的晶体管。电荷存储部fd和/或传输栅极304、306和310的半导体区域(沟道区域)可以部署在图1b中的元件区域12中。传输电极tx1、tx2和tx3可以被部署为不与元件分离部23重叠。这在防止当可能在半导体层10的元件分离部23附近产生的噪声电荷进入电荷存储部fd时出现的信噪(s/n)比劣化方面是有利的。

[0067]

传输栅极302连接到光电二极管pd1,并且传输栅极308连接到光电二极管pd3。传输栅极302包括用于将在光电二极管pd1的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷排出部cd1的传输电极ab1。传输栅极308包括用于将在光电二极管pd2的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷排出部cd3的传输电极ab3。电荷排出部cd1和cd3被供应有作为固定电位的电源电位vdd。像素电路300可以被认为包括以传输栅极302和308作为栅极,以光电二极管pd1和pd3作为源极并且以电荷排出部cd1和cd3作为漏极的两个不同的晶体管。电荷排出部cd1和cd3以及/或传输栅极302和308的半导体区域(沟道区域)部署在图1b中的元件区域12中。

[0068]

传输栅极305连接到光电二极管pd2。传输栅极305包括用于将在光电二极管pd2的光电转换构件中产生的电荷传输到部署在半导体层10中的电荷排出部cd2的传输电极ab2。像素电路300可以被认为包括以传输栅极305作为栅极,以光电二极管pd2作为源极并且以电荷排出部cd2作为漏极的一个晶体管。电荷排出部cd2和传输栅极305的半导体区域(沟道区域)部署在图1b中的元件区域12中。

[0069]

电荷存储部fd是具有信号电荷是多数载流子的导电类型的半导体区域(例如,电子是多数载流子的n型区域)。电荷存储部fd与信号电荷是少数载流子的导电类型(例如,p型)的半导体区域形成pn结,从而形成pn结类型的电容器cfd。电荷存储部fd连接到放大晶体管316的栅电极sf。包括电荷存储部fd和放大晶体管316的栅电极sf的节点被称为检测节点。因此,电荷存储部fd也可以被称为电荷检测部。检测节点的电位是浮动电位,并且基于检测节点的电荷和检测节点的电容来确定。放大晶体管316形成源极跟随器电路,并且放大晶体管316的漏极被供应有作为固定电位的电源电位vdd。信号输出线322经由执行开关的选择晶体管318连接到放大晶体管316的源极,并且像素信号pix经由信号输出线322输出。放大晶体管316生成基于光电二极管pd1的电荷的信号和基于光电二极管pd2的电荷的信号。放大晶体管316还生成基于光电二极管pd3的电荷的信号。选择晶体管318的开/关状态

受供应到选择晶体管318的栅电极sel的选择信号控制。以上参考图1c描述的多个电极25包括这些栅电极sf和sel。选择晶体管318和/或放大晶体管316的半导体区域(沟道区域以及源极和漏极区域)部署在图1b中的元件区域13中。放大晶体管316的栅电极sf和选择晶体管318的栅电极sel可以与图1b和图1c中的元件分离部23重叠。因此,元件分离部23可以设置在电荷存储部fd与放大晶体管316和/或选择晶体管318的半导体区域之间。以上参考图1c描述的电极250例如是栅电极sf。基于元件分离部23限定放大晶体管316的沟道宽度有利于减小放大晶体管316的特性变化。

[0070]

mis型电容器cinc1和/或mis型电容器cinc2经由执行开关的控制晶体管314连接到电荷存储部fd和栅电极sf。mis型电容器cinc1的一个电极被称为电容器电极cel1。mis型电容器cinc2的一个电极被称为电容器电极cel2。以上参考图1c描述的多个电极25可以包括分别形成连接到电荷存储部fd的mis型电容器cinc1和cinc2的电容器电极cel1和cel2。控制晶体管314在电荷存储部fd侧的端子是源极端子和漏极端子中的任一个。mis型电容器cinc1的一个端子连接到控制晶体管314的源极端子和漏极端子中的另一个,并且电容器cinc1的另一个端子是电容器电极cel1。在使用电容器cincl的时段中,电容器电极cel1被供应有固定电位。供应到电容器电极cel1的电位在使用电容器cinc1的时段和不使用电容器cinc1的时段之间可以是不同的。电容器电极cel1可以被施加有与栅电极ctrl和/或栅电极res相同的电位。电容器电极cel1可以与栅电极ctrl或res一体地形成。mis型电容器cinc2的电容器电极cel2连接到控制晶体管314的源极端子和漏极端子中的另一个,并且固定电位被供应到电容器cinc2的另一个端子。尽管在该示例中,电容器cinc2的另一个端子被供应有接触电位vss,但该另一个端子可以被供应有电源电位vdd或者被供应有在电源电位vdd与接触电位vss之间的中间电位。执行开关的复位晶体管312的源极端子和漏极端子中的一个连接到控制晶体管314的源极端子和漏极端子中的另一个。复位晶体管312的源极端子和漏极端子中的另一个被供应有作为固定电位的电源电位vdd。以上参考图1c描述的多个电极25包括控制晶体管314的栅电极ctrl和复位晶体管312的栅电极rst。控制晶体管314和/或复位晶体管312的半导体区域(沟道区域以及源极和漏极区域)可以部署在图1b中的元件区域13中。复位晶体管312的栅电极res和控制晶体管314的栅电极ctrl可以与图1b和图1c中的元件分离部23重叠。因此,元件分离部23可以部署在电荷存储部fd与复位晶体管312和/或控制晶体管314的半导体区域之间。

[0071]

当控制晶体管314导通时,电容器cinc1和/或电容器cinc2经由控制晶体管314连接到电容器cfd。因此,电容器cinc1和/或电容器cinc2与电容器cfd并联连接。然后,检测节点的电容增大至电容器cfd的电容与电容器cinc1的电容和/或电容器cinc2的电容之和。换句话说,当控制晶体管314导通时,检测节点的电容c增大。当检测节点的电容c增大时,如δv=δq/c表示的,每检测节点的电荷量q的检测节点的电位v的移位减小。因此,在大电荷量q的情况下,可以在检测节点的增益减小的情况下输出像素信号pix。大电荷量q的示例情况包括捕获亮场景的情况以及通过传输栅极304传输由高灵敏度光电二极管pdl产生的电荷的情况。另一方面,在小电荷量q的情况下,当控制晶体管314截止时,检测节点的电容c减小。当检测节点的电容c减小时,如δv=δq/c表示的,每检测节点的电荷量q的检测节点的电位v的移位增大。因此,在小电荷量q的情况下,可以在检测节点的增益增大的情况下输出像素信号pix。小电荷量q的示例情况包括捕获暗场景的情况以及通过传输栅极306传输由

低灵敏度光电二极管pd2产生的电荷的情况。列电路(未图示)连接到信号输出线322。列电路可以包括芯片关断(csd)电路、模拟放大器和/或模数(ad)转换器。基于光电二极管pd1的电荷输出的像素信号pix的信号电平与基于光电二极管pd2的电荷输出的像素信号pix的信号电平可以被组合(相加)。可以在像素信号pix是模拟信号的状态下或者在(在通过ad转换器进行ad转换之后)作为数字信号的像素信号pix经历逻辑运算的状态下执行信号电平的相加。以这种方式组合信号电平使得能够扩大动态范围。

[0072]

由于电容器cinc1和cinc2在像素电路300中具有等同的功能,因此像素电路300可以设置有电容器cinc1和cinc2中的任一个。

[0073]

参考图2,可以省略设置在被虚线围绕的部分v处的组件。更具体地,在像素电路300中,可以省略传输栅极305和电荷排出部cd2。

[0074]

参考图2,可以省略设置在由虚线围绕的部分w处的组件。更具体地,在像素电路300中,可以省略光电二极管pd3、传输栅极310和308、以及电荷排出部cd3。

[0075]

以下,将描述适用于以上参考图1和图2描述的示例性实施例的更具体的第一示例性实施例至第九示例性实施例。(下述的)半导体装置930可以是互补金属氧化物半导体(cmos)图像传感器。cmos图像传感器目前在像素的数量和小型化方面正在增加。这也应用于车载相机应用的图像传感器。特别地,用于具有多个光电二极管的车载相机的图像传感器具有比普通cmos图像传感器包括更多的像素晶体管的趋势。因此,用于减小像素区域的技术是重要的。本示例性实施例是鉴于上述问题而设计的,并提供防止包括多个嵌套型光电二极管的cmos图像传感器中的像素区域的增加的像素结构。

[0076]

《第一示例性实施例》

[0077]

以下,将参考图3、图4和图5描述第一示例性实施例。根据第一示例性实施例,半导体装置930不需要包括设置在由图2中虚线围绕的部分v处的组件和设置在由虚线围绕的部分w处的组件。图3是图示了根据第一示例性实施例的像素的平面图。图3的上部部分图示了前表面fs侧的组件,并且图3的下部部分图示了平面hp上的组件。在前表面fs侧和平面hp侧,以重叠的方式示出了后表面bs上的光接收区域11中的九个区块b1至b9。在前表面fs侧和平面hp侧,以重叠的方式示出了前表面fs之中的不与后表面bs上的光接收区域11(区块b1至b9)重叠的非重叠区域b0。在后表面bs上,非重叠区域b0与由遮光部22遮蔽的遮光区域或与具有区块b1至b9的像素不同的像素的光接收区域重叠。

[0078]

在平面hp上,包括与作为内部区块的区块b1重叠的光电二极管pd2的内部光电二极管pd2部署在中心处,并且外部光电二极管pd1被部署为围绕内部光电二极管pd2。外部光电二极管pd1与作为外部区块的区块b2至b9重叠。分离区域iso部署在内部光电二极管pd2和外部光电二极管pd1之间。分离区域iso将内部光电二极管pd2和外部光电二极管pd1彼此电分离和/或光学分离。

[0079]

另一方面,在前表面fs侧,外部光电二极管pd1以类似的方式部署为围绕内部光电二极管pd2。内部光电二极管pd2经由包括传输电极tx2的传输栅极连接到电荷存储部fd。外部光电二极管pd1经由包括传输电极tx1的传输栅极连接到电荷存储部fd。为了防止溢出,外部光电二极管pd1经由包括传输电极ab1的传输栅极302连接到电荷排出部cd1。用于供应电源电位vdd的接触插塞pdd连接到电荷排出部cd1。包括栅电极res的复位晶体管312的一端连接到用于供应电源电位vdd的接触插塞pdd。复位晶体管312的另一端与控制晶体管314

的一端共享。控制晶体管314的另一端经由接触插塞pfd和布线(未图示)连接到电荷存储部fd。放大晶体管316的栅电极sf也连接到电荷存储部fd。放大晶体管316的漏极连接到用于供应电源电位vdd的接触插塞pdd,并且放大晶体管316的源极连接到具有栅电极sel的选择晶体管318的一端。选择晶体管318的另一端连接到用于输出的接触插塞out,并且接触插塞out连接到信号输出线322。

[0080]

外部光电二极管pd1和内部光电二极管pd2具有不同的光敏性,即,在本示例性实施例中,外部光电二极管pd1具有比内部光电二极管pd2高的光敏性。这是因为使外部光电二极管pd1的面积和/或体积大于内部光电二极管pd2的面积和/或体积。该配置还通过优化微透镜阵列和滤色器阵列的布置和形状来实现,以与向内部光电二极管pd2引导的相比,向外部光电二极管pd1引导较大的光量。通过外部光电二极管pd1与内部光电二极管pd2之间的灵敏度的差异以及通过控制晶体管314的控制的增益的增大和减小的组合来实现广动态范围内的信号读取。

[0081]

尽管在图3中,光电二极管具有多边形形状,但它们可以具有诸如圆形形状或环形形状之类的不同形状。像素晶体管的大小和取向、单位像素中的布置和相互位置关系、以及共享源极端子和漏极端子的方式将被视为示例,并且不限于此。

[0082]

如从图3中理解的,传输电极tx2在垂直于后表面bs的z方向上与区块b2重叠。传输电极tx1在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个重叠。在该示例中,传输电极tx1与区块b4重叠。传输电极ab1在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个重叠。在该示例中,传输电极ab1与区块b4重叠。以这种方式,传输电极tx1和ab1与八个区块b2至b9中的至少同一区块(在该示例中,区块b4)重叠。这提高了通过传输电极tx1从光电二极管pd1到电荷存储部fd的电荷传输的效率以及通过传输电极ab1从光电二极管pd1到电荷排出部cd1的电荷传输的效率。连接到电荷存储部fd的接触插塞pfd在垂直于后表面bs的z方向上与区块b1重叠。连接到电荷存储部fd的接触插塞pfd设置在传输电极tx1和tx2之间。这提高了通过传输电极tx1从光电二极管pd1到电荷存储部fd的电荷传输的效率以及通过传输电极tx2从光电二极管pd2到电荷存储部fd的电荷传输的效率。

[0083]

电容器电极cel1在垂直于后表面bs的方向上与八个区块b2至b9中的至少两个重叠。在该示例中,电容器电极cel1与两个区块b2和b6重叠。然而,与八个区块b2至b9重叠的部分小于电容器电极cel1的一半。电容器电极cel1的主要部分与非重叠区域b0重叠。在该示例中,电容器电极cel1与图1中的栅电极ctrl一体地形成。图2中图示的电容器电极cel1和栅电极ctirl在图3中被图示为一体形成的电极ctrl和cel1。栅电极res、sf和sel的与八个区块b2至b9重叠的部分分别小于栅电极res、sf和sel的一半。栅电极res、sf和sel的主要部分与非重叠区域b0重叠。接触插塞pdd、pfd和out与非重叠区域b0重叠。

[0084]

图4a是示意性图示了沿着图3中的a-a'线截取的像素的截面图。图4b是示意性图示了沿着图3中的b-b'线截取的像素的截面图。图5是示意性图示了沿着图3中的a-c-d-e-f-g-h线截取的像素的截面图。参考图4和图5,半导体层10中的非阴影区域是第一导电类型(在该示例中,n型)的半导体区域。参考图4和图5,半导体层10中的非阴影区域的一部分是第二导电类型(在该示例中,p型)的半导体区域。

[0085]

如图4a中图示的,外部光电二极管pd1和内部光电二极管pd2通过从平面hp直至半导体层10中的一定深度的分离区域iso彼此电分离和光学分离。分离区域iso可以包括具有

与电荷存储部fd的导电类型(在该示例中,n型)相反的导电类型(在该示例中,p型)的半导体区域和/或绝缘体区域。可以形成分离区域iso的绝缘体区域可以部署在上述凹槽dt中。

[0086]

另一方面,如图4a和图4b中图示的,n型半导体区域cb1部署在半导体层10中,从而在垂直于后表面bs的z方向上与八个区块b2至b9重叠。半导体区域cb1部署在至少与前表面fs的距离为d或更大且小于3

×

d的范围内。距离d由d=t/4表示,其中,t表示图1c中图示的半导体层10的厚度t(前表面fs与后表面bs之间的距离)。由于平面fq与前表面fs之间的距离为t/4,因此与前表面fs的距离小于d的范围是指平面fq与前表面fs之间的范围,并且与前表面fs的距离为d或更大的范围是指平面fq与后表面bs之间的范围。同样,与前表面fs的距离小于3

×

d的范围是指平面bq与前表面fs之间的范围,并且与前表面fs的距离为3

×

d或更大的范围是指平面bq与后表面bs之间的范围。因此,与前表面fs的距离为d或更大且小于3

×

d的范围是指平面fq与平面bq之间的范围。半导体区域cb1部署在至少平面fq与平面bq之间的范围内。在该示例中,半导体区域cb1也部署在平面fq与前表面fs之间的范围内以及平面bq与后表面bs之间的范围内。在半导体层10中,n型半导体区域ca1被部署为在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个(在该示例中,区块b4)重叠。半导体区域ca1部署在至少与前表面fs的距离小于d的范围内。n型半导体区域cb1和ca1是光电二极管pd1的阴极并且可以用作光电转换构件。由于半导体区域ca1具有比半导体区域cb1高的杂质浓度,因此半导体区域ca1用作收集在半导体区域cb1中产生的电荷的电荷收集部。在半导体区域cb1中产生的电荷被收集到半导体区域ca1中,并且然后从半导体区域ca1传输到电荷存储部fd。由于收集在电荷收集部中的电荷被累积在电荷收集部中,因此半导体区域ca1也可以被称为电荷累积区域。半导体区域cb1也部署在与前表面fs的距离小于d的范围内,并且半导体区域cb1与半导体区域ca1是连续的。半导体区域cb1也部署在与前表面fs的距离为3

×

d或更大的范围内。半导体区域cb1与非重叠区域b0重叠。当半导体区域cb1扩大直至非重叠区域b0时,光电二极管pd1的阴极的体积增加。然后,光电二极管pd1的pn结表面的面积增大,以使光电二极管pd1的结电容增大。这增加了可以被累积在光电二极管pd1中的最大电荷量(饱和电荷量)。当基于光电二极管pd1的电荷的信号与基于光电二极管pd2的电荷的信号组合时,增加光电二极管pd1的饱和电荷量有利于扩大通过组合获得的信号的动态范围。与在光电二极管pd1具有比光电二极管pd2高的灵敏度的情况下相比,在光电二极管pd1具有比光电二极管pd2低的灵敏度的情况下,增大光电二极管pd1的饱和电荷量在扩大动态范围方面较有利。

[0087]

使用图1c中图示的半导体层10的厚度t(前表面fs与后表面bs之间的距离)由d=t/4表示距离d(μm)。由于平面hp与前表面fs之间的距离为t/2或更大,因此与前表面fs的距离为d或更大的范围是指平面hp与后表面bs之间的范围。与前表面fs的距离小于d/2的范围是指平面fq与前表面fs之间的范围。与前表面fs的距离为d/2或更大且小于d的范围是指平面fq与hp之间的范围。

[0088]

同样,在半导体层10中,n型半导体区域cb2被部署为在垂直于后表面bs的z方向上与区块b1重叠。半导体区域cb2部署在至少与前表面fs的距离为d或更大且小于3

×

d的范围内。在半导体层10中,n型半导体区域ca2被部署为在垂直于后表面bs的z方向上与区块b1重叠。半导体区域ca2部署在至少与前表面fs的距离小于d的范围内。n型半导体区域cb2和ca2是光电二极管pd2的阴极并可以用作光电转换构件。由于半导体区域ca2具有比半导体区域

cb2高的杂质浓度,因此半导体区域ca2用作收集在半导体区域cb2中产生的电荷的电荷收集部。更具体地,在半导体区域cb2中产生的电荷被收集到半导体区域ca2中,然后从半导体区域ca2传输到电荷存储部fd。由于收集在电荷收集部中的电荷被累积在电荷收集部中,因此半导体区域ca2也可以被称为电荷累积区域。半导体区域cb2也部署在与前表面fs的距离小于d(μm)的范围内,并且半导体区域cb2与半导体区域ca2是连续的。半导体区域cb2也部署在与前表面fs的距离为3

×

d或更大的范围内。

[0089]

在半导体层10中,p型半导体区域wl在垂直于前表面fs的z方向上部署在半导体区域cb1和前表面fs之间。半导体区域wl部署在至少与前表面fs的距离小于d的范围内。更具体地,半导体区域wl部署在至少平面fq与前表面fs之间的范围内。半导体区域wl既部署在比图1中的元件分离部23的底部浅的范围内又部署在比元件分离部23的底部深的范围内。元件分离部23的深度可以近似于电极25的厚度h(参见图1c)。因此,半导体区域wl部署在与前表面fs的距离小于等于厚度h的距离s的范围内以及与前表面fs的距离等于或大于等于厚度h的距离s的范围。半导体区域wl被部署为在垂直于后表面bs的z方向上与八个区块b2至b9中的至少一个重叠。在该示例中,半导体区域wl在垂直于后表面bs的z方向上与所有八个区块b2至b9重叠。然而,在该示例中,半导体区域wl在垂直于后表面bs的z方向上仅与八个区块b2至b9中的每个的一部分重叠。半导体区域wl在垂直于后表面bs的z方向上与非重叠区域b0重叠。半导体区域wl在前表面fs与平面fq之间围绕半导体区域ca1。半导体区域wl在前表面fs与平面fq之间围绕半导体区域cb1。半导体区域wl在前表面fs与平面fq之间还围绕作为光电二极管pd2的阴极的n型半导体区域。

[0090]

该p型半导体区域wl是与半导体区域cb1和ca1形成pn结的光电二极管pd2的阳极,并可以用作光电转换构件。半导体区域wl被供应有固定电位。供应到半导体区域wl的固定电位例如是如图2中图示的接触电位vss。p型半导体区域wl可以用作电荷存储部fd、电荷排出部cd1、放大晶体管316的漏极sfd、选择晶体管318的源极sls与半导体区域cb1和ca1之间的势垒。p型半导体区域wl还可以用作电极25下方的沟道形成区域。

[0091]

为了防止在前表面fs附近产生的噪声电荷进入半导体区域ca1,作为具有比p型半导体区域wl高的杂质浓度的p型半导体区域的前表面杂质区域(未图示)可以部署在半导体区域ca1和前表面fs之间。同样,为了防止在前表面fs附近产生的噪声电荷进入半导体区域cb1,作为具有比p型半导体区域wl高的杂质浓度的p型半导体区域的前表面杂质区域(未图示)可以部署在半导体区域cb1和前表面fs之间。这些前表面杂质区域的深度可以比图1中图示的元件分离部23的深度浅。更具体地,优选的是,前表面fs与n型杂质区域ca1之间的距离和/或前表面fs与n型杂质区域ca1之间的距离小于元件分离部23的深度。因此,前表面fs与n型杂质区域ca1之间的距离和/或前表面fs与n型杂质区域ca1之间的距离可以小于距离s,距离s等于电极25的厚度h。

[0092]

在半导体层10中,n型半导体区域在垂直于前表面fs的z方向上部署在半导体区域wl和前表面fs之间。半导体区域wl和前表面fs之间的n型半导体区域包括电荷存储部fd和电荷排出部cd1。半导体区域wl和前表面fs之间的n型半导体区域包括像素晶体管的源极和漏极。像素晶体管的源极和漏极的示例包括放大晶体管316的漏极sfd、由放大晶体管316和选择晶体管318共享的源极/漏极sd、以及选择晶体管318的源极sls。

[0093]

如从图3和图4b中理解的,栅电极res、ctrl和sel中的至少两个(在该示例中,三

个)沿着列方向(y方向)布置。三个栅电极res、ctrl和sel布置在一条直线上。栅电极res、ctrl和sel中的每一个与和像素行中包括的多个像素共同连接的行布线连接。将栅电极res、ctrl和sel沿着列方向布置和/或布置在一条直线上提高了像素电路300的操作精度。连接到栅电极res的行布线、连接到栅电极ctrl的行布线和连接到栅电极sel的行布线之间的间隙可以扩宽,使得可以减少行布线之间的串扰。出于类似原因,传输电极tx1、tx2和ab1中的至少两个(在该示例中,三个)沿着列方向(y方向)布置。三个传输电极tx1、tx2和ab1布置在一条直线上。

[0094]

如从图3和图4中理解的,p型半导体区域wl形成为在z方向上与外部光电二极管pd1的n型半导体区域cb1的一部分重叠。如上所述,像素晶体管形成在半导体区域wl的内部。更具体地,像素晶体管被部署为在平面hp中与由外部光电二极管pd1的n型半导体区域cb1占据的区域平面地重叠。与像素晶体管仅布置在外部光电二极管pd1外侧(非重叠区域b0)的情况相比,该布置使得能够减小单位像素面积。这使得能够防止芯片面积的增加和像素数量的减少。所有像素晶体管被部署为在平面hp中与外部光电二极管pd1的n型半导体区域cb1平面地重叠。然而,为了获得上述效果,像素晶体管的至少一部分需要与n型半导体区域cb1重叠。

[0095]

图5a和图5b图示了a-c-d-e-f-g-h截面中的外部光电二极管pd1的杂质浓度分布的示例。图5a图示了n型半导体区域cb1的杂质浓度,即,n型半导体区域cb1的每个部分的浓度n1、n2、n3、n4、n5、n6、n7和n8。图5b图示了n型半导体区域cb1的杂质浓度,即,n型半导体区域cb1的每个部分的浓度n11、n12、n13、n14、n15、n16、n17和n8。由于杂质浓度具有关系n1《n2《n3《n4《n5《n6《n7《n8,因此n型半导体区域cb1的电位深度具有关系n1《n2《n3《n4《n5《n6《n7《n8。电子的电位高度也具有关系n1《n2《n3《n4《n5《n6《n7《n8。由于杂质浓度具有关系n11《n12《n13《n14《n15《n16《n17《n18,因此n型半导体区域cb1的电位深度具有关系n11《n12《n13《n14《n15《n16《n17《n18。电子的电位高度也具有关系n11《n12《n13《n14《n15《n16《n17《n18。

[0096]

图5a和图5b中的关系可以被组合。例如,与区块b2和b3重叠的部分可以具有满足n3《n4'《n4《n4”《n5的浓度范围n4'《n4《n”。与区块b2和b3重叠的部分的浓度可以设置为满足n4'≤n11《n13《n16《n4”。

[0097]

以下,将描述图5a中的示例。图5a中的示例的特征在于,在平面fq与平面bq之间的范围内的半导体区域cb1的杂质浓度,并且以下将主要围绕该范围进行描述。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b4重叠的具有浓度n6的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b2重叠的具有浓度n4的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b3重叠的具有浓度n4的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b5重叠的具有浓度n2的部分。浓度n6的杂质浓度高于具有浓度n4的部分的杂质浓度。具有浓度n2的部分的杂质浓度低于具有浓度n4的部分的杂质浓度。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b6重叠的具有浓度n5的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b8重叠的具有浓度n5的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b7重叠的具有浓度n3的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b9重叠的具有浓度n3的部分。浓度n5的杂质浓度高于具有浓度n3的部分的杂质浓度。

[0098]

以下,将描述图5b中的示例。图5b中的示例的特征在于,在平面fq与前表面fs之间的范围内的半导体区域cb1的杂质浓度,并且以下将主要围绕该范围进行描述。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b4重叠的具有浓度n18的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b2重叠的具有浓度n16的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b3重叠的具有浓度n16的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b5重叠的具有浓度n14的部分。具有浓度n18的部分的杂质浓度高于具有浓度n16的部分的杂质浓度。具有浓度n14的部分的杂质浓度低于具有浓度n16的部分的杂质浓度。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b6重叠的具有浓度n17的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b8重叠的具有浓度n17的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b7重叠的具有浓度n15的部分。半导体区域cb1包括在垂直于后表面bs的z方向上与区块b9重叠的具有浓度n15的部分。浓度n17的杂质浓度高于具有浓度n15的部分的杂质浓度。

[0099]

通过从相对于作为外部光电二极管pd1的电荷收集部的半导体区域ca1的最远部分起顺次地增加杂质浓度和电位深度,可以有效地收集电荷。因此,可以预期改善饱和电荷量和灵敏度的效果。杂质浓度分布需要从相对于外部光电二极管pd1的半导体区域ca1的最远部分到较近部分顺次地增加。电位分布需要从相对于外部光电二极管pd1的半导体区域ca1的最远部分到较近部分顺次地增加。因此,形成杂质浓度分布的方法不限于图5中图示的形式。尽管在图5中,杂质浓度分布是逐渐改变的,但出于类似的原因,它可能递增地改变。

[0100]

《第二示例性实施例》

[0101]

以下,将参考图6描述第二示例性实施例。在第二示例性实施例的描述中,将省略可以与第一示例性实施例中的描述类似的点。

[0102]

第二示例性实施例与第一示例性实施例的不同之处在于电容器电极的布置。尽管在第一示例性实施例中使用了图2中图示的电容器cinc1,但在第二示例性实施例中将使用图2中图示的电容器cinc2。电容器电极cel2经由与包括栅电极ctrl的控制晶体管314的端子连接的接触插塞pcel连接到电容器电极cel2。与根据第一示例性实施例的电容器电极cel1相比,使根据第二示例性实施例的电容器电极cel2的面积较大,从而导致电容器cinc2的电容较大。这增加了动态范围扩大的效果。为了扩大高亮度方向上的动态范围,增加电容器cinc1或cinc2的电极cel1或cel2的面积以分别增大电容器cinc1或cinc2的电容是有效的。然而,为了在第一示例性实施例中实现这一点,需要增加与电容器电极cel1一体形成的栅电极ctrl的面积。这增加了连接到栅电极ctrl并传输用于控制控制晶体管314的导通/截止状态的信号的控制线上的负载。因此,增大栅电极ctrl的面积逐渐使得难以驱动控制线。另一方面,在根据第二示例性实施例的配置中,具有栅电极ctrl的控制晶体管314需要作为开关进行操作。为了增大电容器cinc2的电容,需要增大电容器电极cel2的面积。更具体地,容易在不增加连接到具有栅电极ctrl的控制晶体管314的控制线上的负载的情况下增大电容器cinc2的电容。这提供了执行高亮度方向上的动态范围扩大的优点。具有大面积的电容器电极cel2与五个区块b8、b3、b7、b5和b9重叠。电容器电极cel2的主要部分与非重叠区域b0重叠。尽管在该示例中,电容器电极cel2被划分为包括与区块b8和b3重叠的部分的电容器电极cel2、以及包括与区块b5和b9重叠的部分的电容器电极cel2,但它们可以一体地形

成。

[0103]

《第三示例性实施例》

[0104]

以下,将参考图7和图9描述第三示例性实施例。图9a是沿着图7中的a-g线截取的截面图。在第三示例性实施例的描述中,将省略可以与第二示例性实施例中的描述类似的点。第三示例性实施例与第二示例性实施例的不同之处在于,一个光电二极管pd1设置有两个传输电极tx1。电荷存储部fd与区块b4重叠。两个传输电极tx1中的一个与区块b4和/或区块b6重叠。两个传输电极tx1中的另一个与区块b4和/或区块b8重叠。如图9a中图示的,作为光电二极管pd1的电荷收集部的半导体区域ca1部署在两个不同位置处,以与区块b6和b8中的每个重叠。半导体区域wl和电荷存储部fd部署在与区块b6重叠的半导体区域ca1和与区块b8重叠的半导体区域ca1之间。在与区块b5、b9、b2、b6和b4重叠的光电转换构件中产生的电荷主要被收集到与区块b6重叠的半导体区域ca1中。在与区块b5、b7、b9、b2、b8和b4重叠的光电转换构件中产生的电荷主要被收集到与区块b8重叠的半导体区域ca1中。以这种方式部署多个作为电荷收集部的半导体区域ca1使得能够提高电荷收集效率。连接到电荷存储部fd的接触插塞pfd设置在两个传输电极tx中的一个和其另一个之间。以这种方式部署两个传输电极tx1使得能够提高从光电二极管pd1到电荷存储部fd的电荷传输的效率。本示例性实施例与第二示例性实施例的不同之处在于,一个光电二极管pd1设置有两对传输电极ab1和电荷排出部cd1。该配置使得能够防止来自光电二极管pd1的电荷的溢出。

[0105]

《第四示例性实施例》

[0106]

以下,将参考图8描述第四示例性实施例。根据第四示例性实施例,半导体装置930包括设置在由图2中的虚线围绕的部分w处的组件,但不需要包括设置在由图2中的虚线围绕的部分v处的组件。图9b是沿着图8中的a-f线截取的截面图。在第四示例性实施例的描述中,将省略可以与第三示例性实施例中的描述类似的点。第四示例性实施例包括部署在光电二极管pd2的两侧的光电二极管pd1和pd3。换句话说,光电二极管pd2设置在光电二极管pd1和pd3之间。光电二极管pd1具有与区块b6、b2、b9和b5重叠的光电转换构件。光电二极管pd3具有与区块b8、b3、b7和b5重叠的光电转换构件。为了使光电二极管pd1和pd2彼此分离,分离区域iso部署在与区块b5重叠的位置处、在光电二极管pd1的光电转换构件和光电二极管pd1的光电转换构件之间。以这种方式部署光电二极管pd1和pd3使得能够基于光电二极管pd1和pd3精确地执行光瞳分割。这使得可以精确地执行基于光电二极管pd1与pd3之间的输出的差异的相位差检测、焦点检测、距离测量和深度信息获取。

[0107]

包括传输电极tx1的传输栅极304(参见图2)连接到光电二极管pd1,并且包括传输电极tx3的传输栅极310(参见图2)连接到光电二极管pd3。传输电极tx1与区块b4和/或区块b6重叠,并且传输电极tx3与区块b4和/或区块b8重叠。如图9b中图示的,作为光电二极管pd1的电荷收集部的半导体区域ca1与区块b6重叠,并且作为光电二极管pd3的电荷收集部的半导体区域ca3与区块b8重叠。作为光电二极管pd1的光电转换构件的半导体区域cb1与区块b5、b9、b2和b6重叠。作为光电二极管pd3的光电转换构件的半导体区域cb3与区块b5、b7、b3和b8重叠。连接到电荷存储部fd的接触插塞pfd设置在传输电极tx1和tx3之间。

[0108]

《第五示例性实施例》

[0109]

以下,将参考图10和图11描述第五示例性实施例。图11是沿着图10中的a-f线截取的截面图。在第五示例性实施例的描述中,将省略可以与第二示例性实施例中的描述类似

的点。

[0110]

第五示例性实施例与第二示例性实施例的不同之处在于电容器电极cel和p型阱wel的布置。在该示例中,具有大面积的电容器电极cel2与五个区块b8、b3、b7、b5和b9重叠。区块b8、b3、b7、b5和b9中的每个的主要部分与电容器电极cel2重叠。与第二示例性实施例中相比,这使得高亮度方向上的动态范围能够扩大到较大的程度。如图11中图示的,半导体区域wl部署在电容器电极cel2的下方。因此,区块b8、b3、b7、b5和b9中的每个的绝对多数与半导体区域wl重叠。在该示例中,电荷排出部cd1与区块b5重叠。传输电极ab1与区块b4和/或区块b6重叠。栅电极res、ctrl、sf和sel的绝对多数与区块b2或b6重叠。

[0111]

《第六示例性实施例》

[0112]

以下,将参考图12描述第六示例性实施例。根据第六示例性实施例,半导体装置930包括设置在由图2中的虚线围绕的部分w处的组件,但不需要包括设置在由图2中的虚线围绕的部分v处的组件。在第六示例性实施例的描述中,将省略可以与第二示例性实施例中的描述类似的点。根据第六示例性实施例,光电二极管pd1设置在光电二极管pd2的两侧,并且光电二极管pd3设置在光电二极管pd2的两侧。光电二极管pd3设置在光电二极管pd1和pd2之间。为了使光电二极管pd1和pd2彼此分离,分离区域iso部署在与区块b5重叠的位置处、在光电二极管pd1的光电转换构件和光电二极管pd1的光电转换构件之间。光电二极管pd1和pd3具有与区块b2至b6、b2、b9和b5重叠的光电转换构件。光电二极管pd1的两个电荷收集部部署在非重叠区域b0中,并且光电二极管pd3的两个电荷收集部部署在区块b6和b8中。连接到传输电极ab1的电荷排出部cd1和连接到传输电极ab3的电荷排出部cd3是公共的。电荷存储部fd和接触插塞pfd与区块b4重叠。两个传输电极tx3与区块b4重叠。传输电极tx1与非重叠区域b0重叠。两个传输电极ab1中的一个与区块b6和/或非重叠区域b0重叠,并且两个传输电极ab1中的另一个与区块b8和/或非重叠区域b0重叠。

[0113]

《第七示例性实施例》

[0114]

以下,将参考图13和图15b描述第七示例性实施例。根据第七示例性实施例,半导体装置930包括设置在由图2中的虚线围绕的部分w处的组件,但不需要包括设置在由图2中的虚线围绕的部分v处的组件。图15b是沿着图13中的j-j'线截取的截面图。在第七示例性实施例的描述中,将省略可以与第六示例性实施例中的描述类似的点。第七示例性实施例与其他示例性实施例的不同之处在于,电荷存储部fd和/或电荷排出部cd1由多个像素px1至px4共享。

[0115]

图13图示了各自包括光电二极管pd1、pd2和pd3的四个像素px1、px2、px3和px4。光电二极管pd3具有较大的面积和较高的灵敏度,并且比光电二极管pd2更有可能饱和。然而,当饱和之后的信号流入光电二极管pd2时,因为面积小,具有低灵敏度的光电二极管pd2将立即饱和。因此,光电二极管pd2没有有效地操作。光电二极管pd1和pd3中的每一个设置有两个传输电极ab1和两个传输电极ab3。光电二极管pd1和pd3与图12中的电荷排出部cd1和cd3分开部署。可以基于从导通状态到非导通状态的传输电极ab1和ab3的电位来控制势垒。当传输电极ab1或ab3导通以设置光电二极管pd1或pd3与电荷排出部cd1和cd3之间的半导通状态(势垒的中间状态)时。在半导通状态下,当光电二极管pd1和pd3中的电荷超过预定量时,电荷泄漏到电荷排出部cd1和cd3中。这样使得即使光电二极管pd1和pd3的电荷达到饱和状态,也能够防止电荷泄漏到相邻的像素。以这种方式,可以进行控制以防止光电二极

管之间的饱和之后的泄漏。

[0116]

图14图示了四个像素。在图14中,上部两个像素px1和px2以相对于上部两个像素px3和px4平移对称的方式布置,但上部两个像素px1和px2可以以镜像目标布置。电荷排出部cd1和cd3由像素px2和px3共享。电荷存储部fd由像素px1和px2共享。电荷存储部fd由像素px3和px4共享。具有栅电极sel、sf、res和ctrl的像素晶体管可以由像素px2和px3共享或者由像素px3和px4共享。

[0117]

部署电荷排出部cd1和cd3可能有可能通过电荷排出部cd1和cd3的面积来减小光电二极管pd1、pd2和pd3的面积。然而,由多个像素共享电荷排出部cd1和cd3使得能够防止光电二极管pd1、pd2和pd3的面积减小。尽管在本实施例中,部署光电二极管pd3和电荷排出部cd3,但可以省略光电二极管pd3和电荷排出部cd3,并且电荷排出部cd1可以由多个像素共享。浮动扩散的共享单元不同于电荷排出部cd1和cd3的区域的共享单元。该布置使得能够减小电荷排出部cd1和cd3的区域对像素区域的占用比,并使得能够实现布线共享,从而使得可以减少布线数量并且减小布线之间的耦合电容。如果电荷存储部fd由多个像素共享,则信号读取变慢。因此,电荷排出部cd1可以由多个像素共享,而不由多个像素共享电荷存储部fd。

[0118]

光电二极管pd1和pd3中的每一个可以设置有一个传输电极ab1和一个传输电极ab3。由于在光电二极管饱和之后发生泄漏,因此至少一个位置需要被建立为泄漏路径。在这个意义上,在不需要双边对称性的情况下,栅极的数量可以是一个。

[0119]

《第八示例性实施例》

[0120]

以下,将参考图13和图15b描述第八示例性实施例。图15b是沿着图13中的k-k'线截取的截面图。在第八示例性实施例的描述中,将省略可以与第七示例性实施例中的描述类似的点。第八示例性实施例与其他示例性实施例的不同之处在于,设置了电荷排出部cd2。根据第八示例性实施例,半导体装置930包括设置在由图2中的虚线围绕的部分w处的组件以及设置在由图2中的虚线围绕的部分v处的组件。

[0121]

当使用如图1中图示的微透镜时,由于垂直入射光聚集在像素中心处,因此光电二极管pd2可以提供比光电二极管pd1高的灵敏度。优选的是,防止在具有较高的灵敏度的光电二极管pd2饱和之后电荷泄漏到相邻像素。因此,光电二极管pd2设置有作为饱和之后的泄漏路径的电荷排出部cd2。这使得能够减少在光电二极管pd2饱和之后泄漏到光电二极管pd1和pd3的电荷量。

[0122]

《第九示例性实施例》

[0123]

第九示例性实施例适用于第一示例性实施例至第八示例性实施例中的任一个。图16a是图示了包括根据本示例性实施例的半导体装置930的设备9191的示意图。以下将详细地描述包括半导体装置930的设备9191。如上所述,半导体装置930可以不仅包括具有半导体层10的半导体设备910,而且包括存储半导体设备910的封装件920。封装件920可以包括其上固定有半导体设备910的基座以及面对半导体设备910的由玻璃制成的封盖。封装件920可以包括用于将基座上的端子连接到半导体设备910上的端子的诸如接合线和凸块之类的接合构件。

[0124]

设备9191可以包括光学装置940、控制装置950、处理装置960、显示装置970、存储设备980和机械装置990中的至少任一个。光学装置940适用于半导体装置930。光学装置940

是例如透镜、快门或反射镜。控制装置950控制半导体装置930。控制装置950是例如诸如专用集成电路(asic)之类的半导体装置。

[0125]

处理装置960处理从半导体装置930输出的信号。处理装置960是用于配置模拟前端(afe)或数字前端(dfe)的诸如中央处理单元(cpu)或asic之类的半导体装置。显示装置970是显示由半导体装置930获得的信息(图像)的电致发光(el)显示装置或液晶显示装置。存储设备980是存储由半导体装置930获得的信息(图像)的磁性设备或半导体设备。存储设备980是诸如静态随机存取存储器(sram)或动态随机存取存储器(dram)之类的易失性存储器或诸如闪存或硬盘驱动器之类的非易失性存储器。

[0126]

机械装置990包括诸如电机或发动机之类的可移动单元或推进单元。设备9191将从半导体装置930输出的信号显示在显示装置970上,或者经由设备9191中包括的通信装置(未图示)将信号传输到外部。因此,优选的是,设备9191除了半导体装置930中包括的存储电路和计算电路之外,还包括存储设备980和处理装置960。可以基于从半导体装置930输出的信号来控制机械装置990。

[0127]

设备9191适于具有图像捕获功能的诸如信息终端(例如,智能电话和可穿戴终端)和相机(例如,可更换镜头的相机、紧凑型相机、视频相机和监控相机)之类的电子设备。相机中的机械装置990可以驱动光学装置940的部件以进行变焦、聚焦和快门操作。可替换地,相机中的机械装置990可以移动半导体装置930以进行图像稳定操作。

[0128]

设备9191可以是诸如车辆、船舶或飞行器之类的输送设备。输送设备中的机械装置990可以被用作移动装置。作为输送设备的设备9191对于半导体装置930的输送以及通过图像捕获功能辅助和/或自动进行驱动(操作)是优选的。用于辅助和/或自动进行驱动(操作)的处理装置960可以基于由半导体装置930获得的信息来执行用于操作作为移动装置的机械装置990的处理。可替换地,设备9191可以是诸如内窥镜之类的医疗装置、诸如距离测量传感器之类的测量装置、诸如电子显微镜之类的分析装置、以及诸如复印机之类的商业装置。

[0129]

上述示例性实施例使得可以获得优选的像素特性。因此,半导体装置的价值可以增强。这种情况下的价值增强是指功能增加、性能提高、特性改善、可靠性提高、生产良率提高、环境负荷降低、成本降低、小型化和重量节省中的至少任一个。

[0130]

因此,设备9191中的根据本示例性实施例的半导体装置930的使用还使得能够提高设备的价值。例如,将半导体装置930安装在输送设备上使得能够在对输送设备的外部进行成像和对外部环境进行测量时获得优异的性能。因此,在制造和销售输送设备中,确定将根据本示例性实施例的半导体装置安装在输送设备上有利于提高输送设备本身的性能。特别地,半导体装置930在通过使用由半导体装置获得的信息来支持输送设备的驱动和/或使输送设备的驱动自动化方面是优选的。

[0131]

图16a和图16b是图示了根据本示例性实施例的与车载相机相关的成像系统的框图。成像系统8包括使用根据上述示例性实施例的半导体装置的成像单元80。成像系统8包括使由成像单元80获取的多个图像数据经受图像处理的图像处理单元801、以及基于由成像系统8获取的多个图像数据来计算视差(视差图像的相位差)的视差计算单元802。成像系统8还包括基于计算出的视差来计算与目标对象的距离的距离测量单元803、以及基于计算出的距离来确定碰撞的可能性的碰撞确定单元804。视差计算单元802和距离测量单元803

是获取关于与目标对象的距离的信息的距离信息获取单元的示例。更具体地,距离信息是指关于视差、散焦量和与目标对象的距离的信息。碰撞确定单元804可以通过使用这些距离信息中的任一个来确定碰撞的可能性。距离信息获取单元可以由专用的硬件组件来实现或者由软件模块来实现。距离信息获取单元还可以由现场可编程门阵列(fpga)、专用集成电路(asic)或二者的组合来实现。

[0132]

成像系统8与车辆信息获取装置810连接,以获取诸如车辆速度、偏航率和转向角之类的车辆信息。成像系统8还与作为控制装置的控制电子控制单元(ecu)820连接,ecu 820基于碰撞确定单元804的确定结果来输出用于在车辆上产生制动力的控制信号。成像系统8还与警报装置830连接,警报装置830基于碰撞确定单元804的确定结果来向驾驶员产生警报。例如,如果基于碰撞确定单元804的确定结果,碰撞的可能性高,则控制ecu 820例如通过施加制动、释放加速器或保持发动机动力执行车辆控制以避免碰撞和减少损害。警报装置830通过产生警报声音、在汽车导航系统的画面上显示警报信息或者向安全带或方向盘施加振动来警告用户。如上所述,成像系统8用作控制用于控制车辆的操作的控制单元。

[0133]

根据本示例性实施例,成像系统8捕获车辆的周围的图像,例如,车辆前方或后方的图像。图16b图示了捕获车辆前方(成像范围850)的图像的成像系统。作为成像控制单元的车辆信息获取装置810向成像系统8或成像单元80传输指令,以执行根据上述第一示例性实施例至第七示例性实施例的操作。上述配置使得能够提高距离测量的精度。

[0134]

尽管以上围绕用于避免与其他车辆的碰撞的驱动支持控制描述了本示例性实施例,但本示例性实施例还适用于用于跟随另一车辆的自动化驾驶控制和用于将车辆保持在车道内的自动化驾驶控制。半导体装置930也适用于驾驶记录仪。成像系统不仅适用于诸如本车之类的车辆,而且适用于诸如船只、飞机、人造卫星、工业机器人和消费机器人之类的移动体(移动装置)。另外,成像系统不仅适用于移动体,而且还适用于智能输送系统(its)、监视系统和利用物体识别或生物识别的各种各样的装置。

[0135]

本发明不限于上述示例性实施例,而是可以按各种方式进行修改。例如,本发明还包括附加了另一示例性实施例的配置的一部分的示例性实施例或者配置的一部分被替换为另一示例性实施例的配置的一部分的示例性实施例。

[0136]

在不脱离本发明的技术思路的情况下,可以适当地改变本发明。本说明书的公开内容不仅包括本说明书中的描述,而且包括从本说明书和本说明书附带的图中可理解的所有内容。本说明的公开内容包括本说明书中描述的构思的互补集合。更具体地,如果说明书包括例如描述“a大于b”,则即便省略了描述“a不大于b”,本说明书也公开了描述“a不大于b”。这是因为描述“a大于b”的前提是考虑了“a不大于b”的情况。

[0137]

本发明不限于以上实施例,并且可以在本发明的精神和范围内进行各种改变和修改。因此,为了使公众知道本发明的范围,提出随附的权利要求书。

[0138]

本技术要求于2019年11月25日提交的日本专利申请no.2019-212300的优先权,该日本专利申请特此以引用方式并入本文。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。