1.本发明涉及半导体电力电子器件技术领域中的电导调制型高压功率器件领域,具体是一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管。

背景技术:

2.绝缘栅双极型晶体管(igbt:lateralinsulatedgatebipolartransistor)具有驱动简单,电流能力大,耐压能力高的优点,但是其关断速度远比双扩散金属-氧化物-半导体效应晶体管(dmos,double-diffusedmosfet)的关断速度慢,导致其开关损耗较大,这影响了缘栅双极性晶体管在电力电子系统中的应用。

3.提高igbt器件关断速度从而减小开关损耗的方法主要有三类:

4.一是降低漂移区内非平衡载流子的寿命,增加复合速率,以提高关断速度。事实上降低漂移区内非平衡载流子寿命的同时,其非平衡载流子总数也会减小,这将导致导通电阻增大,所以这种方法存在关断速度与导通电阻之间的折衷问题;

5.二是控制从阳极到漂移区的少数载流子注入水平,以达到导通电阻和关断时间的折衷;

6.三是在阳极区提供非平衡载流子抽出通道,在关断时迅速减少漂移区内非平衡载流子的总数,以提高器件的关断速度。非平衡载流子抽出通道的结构通常会影响少数载流子注入效率,即影响导通时漂移区内非平衡载流子总数,从而影响导通电阻。并且,在器件正向开启过程中,由于载流子从dmos导通模式向igbt导通模式的转换,导通过程中容易出现负阻效应。

7.针对通过在阳极区提供非平衡载流子抽出通道来提高igbt器件关断速度的方法,现有技术中比较典型的器件结构包括如图1所示的常规阳极短路结构、如图2所示的阳极辅助栅、如图3所示的集成超势垒整流器阳极结构、如图4所示的自驱动阳极辅助栅结构等。现有结构中要么器件正向导通能力弱,要么需要复杂的外部驱动电路,要么不能实现逆向导通性能,此外,导通态损耗和关断态损耗之间的折中关系也需要进一步优化。

技术实现要素:

8.本发明的目的是提供一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区、重掺杂第二导电类型阳极区、第一导电类型阳极缓冲区、第一导电类型漂移区、第二导电类型阴极阱区、重掺杂第一导电类型阴极区、重掺杂第二导电类型阴极区、阴极接触区、栅极介质层、栅极接触区、阳极辅助栅介质层、阳极辅助栅接触区和阳极肖特基接触区。

9.所述第一导电类型漂移区覆盖于第一导电类型阳极缓冲区之上。

10.所述第二导电类型阴极阱区覆盖于第一导电类型漂移区之上。

11.所述重掺杂第一导电类型阴极区和重掺杂第二导电类型阴极区覆盖于第二导电

类型阴极阱区之上。

12.所述阴极接触区覆盖于重掺杂第二导电类型阴极区之上。

13.所述栅极介质层覆盖于第二导电类型阴极阱区之上。

14.所述栅极接触区覆盖于栅极介质层之上。

15.所述重掺杂第二导电类型阳极区覆盖于第一导电类型阳极缓冲区之下。

16.所述阳极辅助栅介质层覆盖于第一导电类型阳极缓冲区之下的部分表面。所述阳极辅助栅接触区覆盖于阳极辅助栅介质层之下。

17.所述阳极接触区覆盖于第二导电类型阳极区之下。

18.所述阳极肖特基接触区覆盖于阳极辅助栅接触区之下,所述阳极肖特基接触区还覆盖于第一导电类型阳极缓冲区之下的部分表面。

19.所述阳极接触区和阳极肖特基接触区共同引出阳极电极。

20.所述阳极接触区和阳极肖特基接触区并列间隔排布。

21.所述第二导电类型阴极阱区覆盖于第一导电类型漂移区之上的部分表面。

22.所述重掺杂第一导电类型阴极区和重掺杂第二导电类型阴极区覆盖于第二导电类型阴极阱区之上的部分表面。

23.所述阴极接触区还覆盖于重掺杂第一导电类型阴极区之上的部分表面。

24.所述栅极介质层还覆盖于重掺杂第一导电类型阴极区之上的部分表面和第一导电类型漂移区之上的部分表面。

25.所述栅极介质层覆盖于第二导电类型阴极阱区之上的部分表面。

26.所述重掺杂第二导电类型阳极区覆盖于第一导电类型阳极缓冲区之下的部分表面。

27.优选的,所述阳极接触区和阳极肖特基接触区彼此接触。

28.优选的,所述阳极接触区和阳极肖特基接触区彼此不接触。

29.一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区、重掺杂第二导电类型阳极区、第一导电类型阳极缓冲区、第一导电类型漂移区、第二导电类型阴极阱区、重掺杂第一导电类型阴极区、重掺杂第二导电类型阴极区、阴极接触区、栅极介质层、栅极接触区、阳极辅助栅介质层和阳极肖特基接触区。

30.所述第一导电类型漂移区覆盖于第一导电类型阳极缓冲区之上。

31.所述第二导电类型阴极阱区覆盖于第一导电类型漂移区之上。

32.所述重掺杂第一导电类型阴极区和重掺杂第二导电类型阴极区覆盖于第二导电类型阴极阱区之上。

33.所述阴极接触区覆盖于重掺杂第二导电类型阴极区之上。

34.所述栅极介质层覆盖于第二导电类型阴极阱区之上。

35.所述栅极接触区覆盖于栅极介质层之上。

36.所述重掺杂第二导电类型阳极区覆盖于第一导电类型阳极缓冲区之下。

37.所述阳极辅助栅介质层覆盖于第一导电类型阳极缓冲区之下的部分表面。

38.所述阳极接触区覆盖于第二导电类型阳极区之下。

39.所述阳极肖特基接触区覆盖于阳极辅助栅介质层之下,所述阳极肖特基接触区还覆盖于第一导电类型阳极缓冲区之下的部分表面。

40.所述阳极接触区和阳极肖特基接触区共同引出阳极电极。

41.所述阳极接触区和阳极肖特基接触区并列间隔排布。

42.所述第二导电类型阴极阱区覆盖于第一导电类型漂移区之上的部分表面。

43.所述重掺杂第一导电类型阴极区和重掺杂第二导电类型阴极区覆盖于第二导电类型阴极阱区之上的部分表面。

44.所述阴极接触区还覆盖于重掺杂第一导电类型阴极区之上的部分表面。

45.所述栅极介质层还覆盖于重掺杂第一导电类型阴极区之上的部分表面和第一导电类型漂移区之上的部分表面。

46.所述栅极介质层覆盖于第二导电类型阴极阱区之上的部分表面。

47.所述重掺杂第二导电类型阳极区覆盖于第一导电类型阳极缓冲区之下的部分表面。

48.优选的,所述阳极接触区和阳极肖特基接触区彼此接触。

49.优选的,所述阳极接触区和阳极肖特基接触区彼此不接触。

50.本发明的技术效果是毋庸置疑的,本发明具有以下优点:

51.1)所述阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管采用阳极集成肖特基超势垒自驱动辅助栅的设计结构;

52.2)与现有技术中的常规短路阳极igbt器件、辅助栅极阳极igbt器件、集成超势垒整流器阳极igbt器件、自驱动阳极辅助栅igbt器件等相比,阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

53.3)本发明所述阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管采用阳极集成肖特基超势垒自驱动辅助栅的设计结构,在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

附图说明

54.图1为现有技术中短路阳极器件的结构示意图;

55.图2为现有技术中辅助栅阳极器件的结构示意图;

56.图3为现有技术中集成超势垒整流器阳极器件的结构示意图;

57.图4为现有技术中自驱动阳极辅助栅器件的结构示意图;

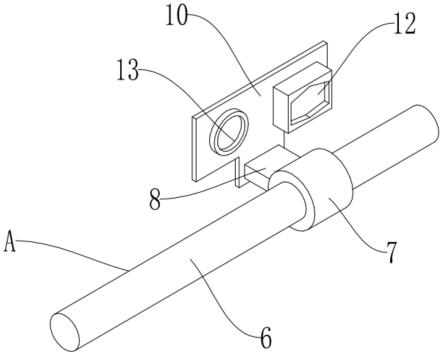

58.图5为本发明提供的igbt器件的实施例3结构示意图;

59.图6为本发明提供的igbt器件的实施例4结构意图;

60.图7为本发明提供的igbt器件的实施例5结构示意图;

61.图8为本发明提供的igbt器件的实施例6结构示意图;

62.图中:阳极接触区1、重掺杂第二导电类型阳极区2、第一导电类型阳极缓冲区3、第一导电类型漂移区4、第二导电类型阴极阱区5、重掺杂第一导电类型阴极区6、重掺杂第二

导电类型阴极区7、阴极接触区8、栅极介质层9、栅极接触区10、第二导电类型阳极阱区11、重掺杂第一导电类型阳极区12、阳极辅助栅介质层13、阳极辅助栅接触区14和阳极肖特基接触区15。

具体实施方式

63.下面结合实施例对本发明作进一步说明,但不应该理解为本发明上述主题范围仅限于下述实施例。在不脱离本发明上述技术思想的情况下,根据本领域普通技术知识和惯用手段,做出各种替换和变更,均应包括在本发明的保护范围内。

64.实施例1:

65.一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、重掺杂第二导电类型阳极区2、第一导电类型阳极缓冲区3、第一导电类型漂移区4、第二导电类型阴极阱区5、重掺杂第一导电类型阴极区6、重掺杂第二导电类型阴极区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13、阳极辅助栅接触区14和阳极肖特基接触区15。

66.所述第一导电类型漂移区4覆盖于第一导电类型阳极缓冲区3之上。

67.所述第二导电类型阴极阱区5覆盖于第一导电类型漂移区4之上。

68.所述重掺杂第一导电类型阴极区6和重掺杂第二导电类型阴极区7覆盖于第二导电类型阴极阱区5之上。

69.所述阴极接触区8覆盖于重掺杂第二导电类型阴极区7之上。

70.所述栅极介质层9覆盖于第二导电类型阴极阱区5之上。

71.所述栅极接触区10覆盖于栅极介质层9之上。

72.所述重掺杂第二导电类型阳极区2覆盖于第一导电类型阳极缓冲区3之下。

73.所述阳极辅助栅介质层13覆盖于第一导电类型阳极缓冲区3之下的部分表面。所述阳极辅助栅接触区14覆盖于阳极辅助栅介质层13之下。

74.所述阳极接触区1覆盖于第二导电类型阳极区2之下。

75.所述阳极肖特基接触区15覆盖于阳极辅助栅接触区14之下,所述阳极肖特基接触区15还覆盖于第一导电类型阳极缓冲区3之下的部分表面。

76.所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极。

77.所述阳极接触区1和阳极肖特基接触区15并列间隔排布。

78.所述第二导电类型阴极阱区5覆盖于第一导电类型漂移区4之上的部分表面。

79.所述重掺杂第一导电类型阴极区6和重掺杂第二导电类型阴极区7覆盖于第二导电类型阴极阱区5之上的部分表面。

80.所述阴极接触区8还覆盖于重掺杂第一导电类型阴极区6之上的部分表面。

81.所述栅极介质层9还覆盖于重掺杂第一导电类型阴极区6之上的部分表面和第一导电类型漂移区4之上的部分表面。

82.所述栅极介质层9覆盖于第二导电类型阴极阱区5之上的部分表面。

83.所述重掺杂第二导电类型阳极区2覆盖于第一导电类型阳极缓冲区3之下的部分表面。

84.所述阳极接触区1和阳极肖特基接触区15彼此接触。

85.实施例2:

86.一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、重掺杂第二导电类型阳极区2、第一导电类型阳极缓冲区3、第一导电类型漂移区4、第二导电类型阴极阱区5、重掺杂第一导电类型阴极区6、重掺杂第二导电类型阴极区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13和阳极肖特基接触区15。

87.所述第一导电类型漂移区4覆盖于第一导电类型阳极缓冲区3之上。

88.所述第二导电类型阴极阱区5覆盖于第一导电类型漂移区4之上。

89.所述重掺杂第一导电类型阴极区6和重掺杂第二导电类型阴极区7覆盖于第二导电类型阴极阱区5之上。

90.所述阴极接触区8覆盖于重掺杂第二导电类型阴极区7之上。

91.所述栅极介质层9覆盖于第二导电类型阴极阱区5之上。

92.所述栅极接触区10覆盖于栅极介质层9之上。

93.所述重掺杂第二导电类型阳极区2覆盖于第一导电类型阳极缓冲区3之下。

94.所述阳极辅助栅介质层13覆盖于第一导电类型阳极缓冲区3之下的部分表面。

95.所述阳极接触区1覆盖于第二导电类型阳极区2之下。

96.所述阳极肖特基接触区15覆盖于阳极辅助栅介质层13之下,所述阳极肖特基接触区15还覆盖于第一导电类型阳极缓冲区3之下的部分表面。

97.所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极。

98.所述阳极接触区1和阳极肖特基接触区15并列间隔排布。

99.所述第二导电类型阴极阱区5覆盖于第一导电类型漂移区4之上的部分表面。

100.所述重掺杂第一导电类型阴极区6和重掺杂第二导电类型阴极区7覆盖于第二导电类型阴极阱区5之上的部分表面。

101.所述阴极接触区8还覆盖于重掺杂第一导电类型阴极区6之上的部分表面。

102.所述栅极介质层9还覆盖于重掺杂第一导电类型阴极区6之上的部分表面和第一导电类型漂移区4之上的部分表面。

103.所述栅极介质层9覆盖于第二导电类型阴极阱区5之上的部分表面。

104.所述重掺杂第二导电类型阳极区2覆盖于第一导电类型阳极缓冲区3之下的部分表面。

105.所述阳极接触区1和阳极肖特基接触区15彼此不接触。

106.实施例3:

107.选择第一导电类型为n型,第二导电类型为p型。

108.如图5所示,一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、阳极p 区2、n型缓冲区3、n型漂移区4、p型阴极阱区5、阴极n 区6、阴极p 区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13、阳极辅助栅接触区14和阳极肖特基接触区15;

109.所述n型漂移区4覆盖于n型缓冲区3之上;

110.所述p型阴极阱区5覆盖于n型漂移区4之上的部分表面;所述阴极n 区6和阴极p 区7覆盖于p型阴极阱区5之上的部分表面;所述阴极接触区8覆盖于阴极p 区7之上,所述阴极接触区8还覆盖于阴极n 区6之上的部分表面;

111.所述栅极介质层9覆盖于p型阴极阱区5之上的部分表面,所述栅极介质层9还覆盖于阴极n 区6之上的部分表面和n型漂移区4之上的部分表面;所述栅极接触区10覆盖于栅极介质层9之上;

112.所述阳极p 区2覆盖于n型缓冲区3之下的部分表面;

113.所述阳极辅助栅介质层13覆盖于n型缓冲区3之下的部分表面;所述阳极辅助栅接触区14覆盖于阳极辅助栅介质层13之下;

114.所述阳极接触区1覆盖于阳极p 区2之下;所述阳极肖特基接触区15覆盖于阳极辅助栅接触区14之下,所述阳极肖特基接触区15还覆盖于n型缓冲区3之下的部分表面;所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极;

115.所述阳极接触区1和阳极肖特基接触区15并列间隔排布;所述阳极接触区1和阳极肖特基接触区15彼此接触。

116.本实施例给出的阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管,在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

117.实施例4:

118.选择第一导电类型为n型,第二导电类型为p型。

119.如图6所示,一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、阳极p 区2、n型缓冲区3、n型漂移区4、p型阴极阱区5、阴极n 区6、阴极p 区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13、阳极辅助栅接触区14和阳极肖特基接触区15;

120.所述n型漂移区4覆盖于n型缓冲区3之上;

121.所述p型阴极阱区5覆盖于n型漂移区4之上的部分表面;所述阴极n 区6和阴极p 区7覆盖于p型阴极阱区5之上的部分表面;所述阴极接触区8覆盖于阴极p 区7之上,所述阴极接触区8还覆盖于阴极n 区6之上的部分表面;

122.所述栅极介质层9覆盖于p型阴极阱区5之上的部分表面,所述栅极介质层9还覆盖于阴极n 区6之上的部分表面和n型漂移区4之上的部分表面;所述栅极接触区10覆盖于栅极介质层9之上;

123.所述阳极p 区2覆盖于n型缓冲区3之下的部分表面;

124.所述阳极辅助栅介质层13覆盖于n型缓冲区3之下的部分表面;所述阳极辅助栅接触区14覆盖于阳极辅助栅介质层13之下;

125.所述阳极接触区1覆盖于阳极p 区2之下;所述阳极肖特基接触区15覆盖于阳极辅助栅接触区14之下,所述阳极肖特基接触区15还覆盖于n型缓冲区3之下的部分表面;所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极;

126.所述阳极接触区1和阳极肖特基接触区15并列间隔排布;所述阳极接触区1和阳极肖特基接触区15彼此不接触。

127.本实施例给出的阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管,在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获

得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

128.实施例5:

129.选择第一导电类型为n型,第二导电类型为p型。

130.如图7所示,一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、阳极p 区2、n型缓冲区3、n型漂移区4、p型阴极阱区5、阴极n 区6、阴极p 区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13和阳极肖特基接触区15;

131.所述n型漂移区4覆盖于n型缓冲区3之上;

132.所述p型阴极阱区5覆盖于n型漂移区4之上的部分表面;所述阴极n 区6和阴极p 区7覆盖于p型阴极阱区5之上的部分表面;所述阴极接触区8覆盖于阴极p 区7之上,所述阴极接触区8还覆盖于阴极n 区6之上的部分表面;

133.所述栅极介质层9覆盖于p型阴极阱区5之上的部分表面,所述栅极介质层9还覆盖于阴极n 区6之上的部分表面和n型漂移区4之上的部分表面;所述栅极接触区10覆盖于栅极介质层9之上;

134.所述阳极p 区2覆盖于n型缓冲区3之下的部分表面;

135.所述阳极辅助栅介质层13覆盖于n型缓冲区3之下的部分表面;

136.所述阳极接触区1覆盖于阳极p 区2之下;所述阳极肖特基接触区15覆盖于阳极辅助栅介质层13之下,所述阳极肖特基接触区15还覆盖于n型缓冲区3之下的部分表面;所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极;

137.所述阳极接触区1和阳极肖特基接触区15并列间隔排布;所述阳极接触区1和阳极肖特基接触区15彼此接触。

138.本实施例给出的阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管,在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

139.实施例6:

140.选择第一导电类型为n型,第二导电类型为p型。

141.如图8所示,一种阳极集成肖特基超势垒辅助栅的逆导型绝缘栅双极型晶体管,包括阳极接触区1、阳极p 区2、n型缓冲区3、n型漂移区4、p型阴极阱区5、阴极n 区6、阴极p 区7、阴极接触区8、栅极介质层9、栅极接触区10、阳极辅助栅介质层13和阳极肖特基接触区15;

142.所述n型漂移区4覆盖于n型缓冲区3之上;

143.所述p型阴极阱区5覆盖于n型漂移区4之上的部分表面;所述阴极n 区6和阴极p 区7覆盖于p型阴极阱区5之上的部分表面;所述阴极接触区8覆盖于阴极p 区7之上,所述阴极接触区8还覆盖于阴极n 区6之上的部分表面;

144.所述栅极介质层9覆盖于p型阴极阱区5之上的部分表面,所述栅极介质层9还覆盖

于阴极n 区6之上的部分表面和n型漂移区4之上的部分表面;所述栅极接触区10覆盖于栅极介质层9之上;

145.所述阳极p 区2覆盖于n型缓冲区3之下的部分表面;

146.所述阳极辅助栅介质层13覆盖于n型缓冲区3之下的部分表面;

147.所述阳极接触区1覆盖于阳极p 区2之下;所述阳极肖特基接触区15覆盖于阳极辅助栅介质层13之下,所述阳极肖特基接触区15还覆盖于n型缓冲区3之下的部分表面;所述阳极接触区1和阳极肖特基接触区15共同引出阳极电极;

148.所述阳极接触区1和阳极肖特基接触区15并列间隔排布;所述阳极接触区1和阳极肖特基接触区15彼此不接触。

149.本实施例给出的阳极集成肖特基超势垒辅助栅的绝缘栅双极型晶体管,在保证器件较小的关断时间的前提下,可以消除器件导通时的负阻效应,提高器件的工作稳定性,获得更好的导通态损耗与关断态损耗之间的折衷关系;实现器件的逆向导通能力;并且,所述阳极集成肖特基超势垒辅助栅结构采用自驱动设计,能够消除常规辅助栅极阳极结构对额外驱动电路的要求。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。