自动化转换后备缓冲器集合再平衡

1.关于联邦资助的研发的声明

2.本发明是在由国防部授予的协议号h98230a-13-d-0124的政府支持下进行的。政府具有本发明的某些权益。

背景技术:

3.本公开总体上关于高效地设置转换后备缓冲器(tlb)中的再平衡,该tlb包含可配置成用于在引导后的不同时刻保存不同的页尺寸集的可配置的子tlb以及在引导后保存固定的页尺寸集的固定的子tlb。

4.本节旨在向读者介绍可能涉及当前技术的各方面的技术的各方面,这在下文描述和/或要求保护。相信该讨论有助于向读者提供促进对本公开的各方面更好的理解的背景信息。相应地,应当注意这些陈述应从这个角度来阅读,而不是作为任何种类的承认。

5.集成电路见于众多电子设备,这些电子设备来自手持式设备、计算机、游戏系统、机器人设备、汽车,等等。诸如微处理器之类的一些集成电路处理从存储器检取的数据。虽然数据被存储在表示存储器中的实际位置的物理存储器地址中,但是在集成电路上运行的软件可使用虚拟存储器地址来操作,当存储器被访问时,该虚拟存储器地址被转换为物理存储器地址。被称为转换后备缓冲器(tlb)的集成电路上的结构可通过存储虚拟存储器地址至其对应的物理存储器地址的近期使用的映射来减少访问存储器位置所花费的时间。虚拟至物理转换使用“页”来完成,其中,典型的x86页尺寸为4千位字节(kibibyte)(4kib)、2兆位字节(mebibyte)(2mib)、或1千兆位字节(gibibyte)(1gib)。用于页的tlb条目涵盖与页尺寸对应的地址范围。例如,如果tlb存储用于2mib页的转换,则存在可由同一tlb条目转换的2m虚拟地址的范围。当在集成电路上的软件请求对在近期被使用的且被存储在tlb中的页上的特定虚拟存储器地址的访问时,该tlb可迅速地将虚拟存储器地址转换为其对应的物理存储器地址。

6.以此方式,tlb可操作为从虚拟存储器地址向物理存储器地址的映射的高速缓存。在当前被存储在tlb中的映射被请求时,这可被称为“高速缓存命中”或“tlb命中”。然而,当tlb当前不具有被请求的映射时,这可被称为“高速缓存未命中”或“tlb未命中”。在转换发生前,所请求的映射可首先被加载到tlb中。一些软件应用会对tlb未命中损失显著的运行时间。

7.减少tlb未命中的一种方法涉及增加tlb的尺寸。然而,许多软件应用会由于差的参引局部性而触及存储器的许多页,从而使得建立“从不未命中”tlb是不可行的。进一步地,较大的硬件结构可具有较高的命中率但具有较慢的访问时间,从而导致性能的净损失。减小未命中率的其他方法可涉及使用具有不同页尺寸的tlb条目。遗憾的是,利用此结构提供性能优势的存储器用例可能难以实现。此外,诸如共享具有特定尺寸的单个子tlb之类的解决方案常引入重大的冲突或竞争,该冲突或竞争可能由于tlb未命中而引入附加的等待时间。

附图说明

8.在阅读下列具体实施方式时并在参考附图时,可更好地理解本公开的各方面,在附图中:

9.图1是根据实施例的寄存器架构的框图;

10.图2a是图示出根据实施例的有序流水线以及寄存器重命名的、乱序发布/执行流水线的框图;

11.图2b是图示出根据本公开的实施例的、要被包括在处理器中的有序架构核以及寄存器重命名的、乱序发布/执行架构核的框图;

12.图3a和图3b图示出根据实施例的更具体的示例有序核架构的框图,该核将是芯片中的若干逻辑块(包括相同类型和/或不同类型的其他核)中的一个逻辑块;

13.图4是根据实施例的可具有多于一个的核、可具有集成存储器控制器、以及可具有集成图形器件的处理器的框图;

14.图5示出的是根据实施例的系统的框图;

15.图6是根据实施例的第一更具体的示例系统的框图;

16.图7是根据实施例的第二更具体的示例系统的框图;

17.图8是根据实施例的芯片上系统(soc)的框图;

18.图9是根据实施例的对照使用软件指令转换器将源指令集中的二进制指令转换成目标指令集中的二进制指令的框图;

19.图10是图示根据实施例的、转换后备缓冲器(tlb)在所请求的tlb条目当前被存储在tlb中(“tlb命中”)时的操作的框图;

20.图11是图示根据实施例的、tlb在所请求的tlb条目当前不被存储在tlb中(“tlb未命中”)时的操作的框图;

21.图12是根据实施例的tlb的框图,该tlb使用以下各项来保存与多个存储器页尺寸对应的tlb条目、第一固定的集合相联的(set-associative)子tlb,其保存与第一页尺寸对应的条目;第二固定的集合相联的子tlb,其保存与第二页尺寸对应的条目;第三固定的集合相联的子tlb,其保存与第三页尺寸对应的条目;以及可配置的全相联的子tlb,其保存与全部三个页尺寸对应的条目;

22.图13是根据实施例的tlb的框图,该tlb使用以下各项来保存与多个存储器页尺寸对应的tlb条目:第一固定的集合相联的子tlb,其保存与第一页尺寸对应的条目;第二固定的集合相联的子tlb,其保存与第二页尺寸对应的条目;以及可配置的全相联的子tlb,其保存与全部三个页尺寸对应的条目;

23.图14是根据实施例的tlb的框图,该tlb使用以下各项来保存与多个存储器页尺寸对应的tlb条目:第一固定的集合相联的子tlb,其保存与第二页尺寸对应的条目;第二固定的集合相联的子tlb,其保存与第三页尺寸对应的条目;以及可配置的全相联的子tlb,其保存与全部三个页尺寸对应的条目;

24.图15是根据实施例的tlb的框图,该tlb使用以下各项来保存与多个存储器页尺寸对应的tlb条目:第一固定的集合相联的子tlb,其保存与第一页尺寸对应的条目;第二固定的集合相联的子tlb,其保存与第三页尺寸对应的条目;以及可配置的全相联的子tlb,其保存与全部三个页尺寸对应的条目;

25.图16是图示根据实施例的tlb的tlb条目的框图,该tlb具有一个或多个固定的集合相联的子tlb以及可配置的全相联的子tlb;

26.图17是图示根据实施例的用于利用tlb中的新tlb条目来驱逐并替换旧tlb的方法的流程图,该tlb具有一个或多个固定的集合相联的子tlb以及可配置全相联的子tlb;

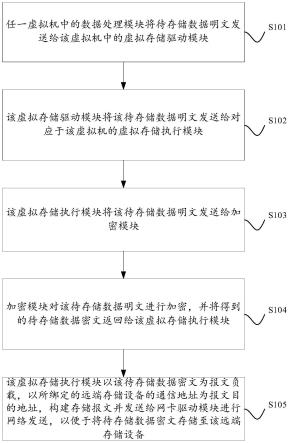

27.图18是图示根据实施例的用于利用tlb中的新tlb条目来驱逐并替换旧tlb的决策的框图,该tlb具有一个或多个固定的集合相联的子tlb以及可配置全相联的子tlb;

28.图19是根据实施例的对子tlb未命中率计数的tlb的框图;

29.图20是根据实施例的用于选择要用于利用新tlb条目来替换旧tlb条目的子tlb的方法的流程图;

30.图21是根据实施例的用于选择要用于利用新tlb条目来替换旧tlb条目的子tlb的另一方法的流程图;

31.图22是根据实施例的用于选择要用于利用新tlb条目来替换旧tlb条目的子tlb的另一方法的流程图;

32.图23是根据实施例的用于使用“抛硬币”方式选择要用于利用新tlb条目来替换旧tlb条目的子tlb的框图;

33.图24是根据实施例的用于选择tlb条目以利用可配置的全相联的子tlb中的新tlb条目来驱逐和替换的方法的流程图;

34.图25是根据实施例的tlb的框图,该tlb将可配置的全相联的子tlb的某些tlb条目定义为“粘性”且预留用于与特定的页尺寸对应的tlb条目;

35.图26是根据实施例的、用于将可配置的全相联的子tlb的某些tlb条目标记为“粘性”且预留用于与特定的页尺寸对应的tlb条目的方法的流程图;

36.图27是根据实施例的、用于将可配置的全相联的子tlb的某些tlb条目标记为“粘性”且预留用于与特定的页尺寸对应的tlb条目的另一方法的流程图;

37.图28是根据实施例的tlb的框图,该tlb对具有特定的页尺寸的tlb条目被存储在可配置的全相联的子tlb中的条目中的次数进行计数;

38.图29是根据实施例的、用于基于图28中的计数将可配置的全相联的子tlb的某些tlb条目标记为“粘性”的方法的流程图;

39.图30是根据实施例的tlb的框图,该tlb对具有特定的页尺寸的tlb条目被存储在可配置的全相联的子tlb中的任何条目中的次数进行计数;

40.图31是根据实施例的、用于基于图30中的计数将可配置的全相联的子tlb的某些tlb条目标记为“粘性”的方法的流程图;

41.图32是根据实施例的tlb的框图,该tlb对tlb请求或时钟周期的总数进行计数,以确定何时将可配置的全相联的子tlb的某些条目标记为“粘性”;

42.图33是根据实施例的、用于基于图32中的计数将可配置的全相联的子tlb的某些tlb条目标记为“粘性”的方法的流程图;

43.图34是根据实施例的、用于响应于上下文切换而将可配置的全相联的子tlb的某些tlb条目从“粘性”重置的方法的流程图;

44.图35是根据实施例的、用于响应于对粘性子tlb条目的显式无效而将可配置的全相联的子tlb的某些tlb条目从“粘性”重置的方法的流程图;

45.图36是根据实施例的、在阈值量的次数或tlb请求之后将可配置的全相联的子tlb的某些tlb条目从“粘性”重置的方法的流程图;

46.图37是根据实施例的、在后续被尝试的驱逐(“第二次机会”方式)之际将可配置的全相联的子tlb的某些tlb条目从“粘性”重置的方法的流程图;以及

47.图38是根据实施例的数据结构的框图,该数据结构可表示可配置的全相联的子tlb中的tlb条目。

具体实施方式

48.下文将描述一个或多个具体实施例。为了提供对这些实施例的简洁描述,说明书中并未描述实际实现方式的所有特征。应当领会,在任何此类实际实现方式的开发中,如同在任何工程或设计项目中一样,为了实现开发人员的特定目标,必须作出众多特定于实现方式的决策,诸如遵守与系统相关的约束和与业务相关的约束,这些约束可能因实现方式而有所不同。而且应当领会,此类开发工作可能是复杂且耗时的,但是对于受益于本公开的普通技术人员而言,这仍将是设计、制作和制造的例行任务。

49.当介绍本公开的各实施例的要素时,冠词“一(a、an)”、“该(the)”旨在意指存在这些要素中的一个或多个要素。术语“包括”、“具有”旨在是包含性的,并且意指除了所列举的要素之外还可能存在附加要素。另外,应当理解,对本公开的“一些实施例”、“诸实施例”、“一个实施例”或“实施例”的引用不旨在被解释为排除也包含所陈述的特征的附加实施例的存在。此外,短语a“基于”b旨在意指a至少部分地基于b。此外,术语“或”旨在是包含性的(例如,逻辑或)而并非排他性的(例如,逻辑异或)。换言之,短语a“或”b旨在意指a、b、或者a和b两者。此外,本公开描述了各种数据结构,诸如用于指令集架构的指令。这些被描述为具有某些域(例如,字段)和对应数量的位。然而,应当理解,这些域和按位计的尺寸旨在是示例,并且不旨在是排他性的。实际上,本公开的数据结构(例如,指令)可采取任何合适的形式。

50.如上文所述,集成电路见于众多电子设备,这些电子设备来自手持式设备、计算机、游戏系统、机器人设备、汽车,等等。诸如微处理器之类的一些集成电路处理从存储器检取的数据。虽然数据被存储在表示存储器中的实际位置的物理存储器地址中,但是在集成电路上运行的软件可使用虚拟存储器地址来操作,当存储器被访问时,该虚拟存储器地址被转换为物理存储器地址。被称为转换后备缓冲器(tlb)的集成电路上的结构可通过存储虚拟存储器地址至其对应的物理存储器地址的近期使用的映射来减少访问存储器位置所花费的时间。虚拟至物理转换使用“页”来完成,其中,典型的x86页尺寸为4千位字节(4kib)、2兆位字节(2mib)、或1千兆位字节(1gib)。用于页的tlb条目涵盖与页尺寸对应的地址范围。例如,如果tlb存储用于2mib页的转换,则存在可由同一tlb条目转换的2mib虚拟地址的范围。当数据利用电路(例如,在集成电路上的运行软件的处理电路)请求对在近期被使用的且被存储在tlb中的页上的特定虚拟存储器地址的访问时,该tlb可迅速地将虚拟存储器地址转换为其对应的物理存储器地址。

51.以此方式,tlb可操作为虚拟存储器地址至物理存储器地址的页的映射的高速缓存。当可见于当前被存储在tlb的条目中的特定的页上的虚拟至物理地址映射被请求时,这可被称为“高速缓存命中”或“tlb命中”。然而,当tlb当前不具有被请求的映射时,这可被称

为“高速缓存未命中”或“tlb未命中”。在转换发生前,所请求的映射可首先被加载到tlb中。一些软件应用会对tlb未命中损失选择的运行时间,因此减少tlb未命中的数量可增加tlb能够对tlb请求进行响应的速率。

52.与简单地增加tlb的尺寸来降低tlb未命中的可能性——这会占据集成电路的大量有价值的管芯面积——不同,tlb可具有若干子tlb,这些子tlb处置与存储器的特定页尺寸对应的特定tlb请求。具体而言,各种软件应用可使用具有按照各种尺寸(例如,4千位字节(4kib)、2兆位字节(2mib)、或1千兆位字节(1gib))的页表的存储器。这些在下文中将分别被称为4k、2m和1g。这些是512倍的尺寸比率——例如,2mib比4kib大512倍。在某些条件下,可使用较大的页尺寸来取代下一较小的尺寸。这移除约500倍页映射,因此减少对tlb空间的竞争。例如,如果触及100000倍的4kib页的应用可被提升以使用2mib页,则tlb仅需要约200个tlb条目,并且该应用将很少取得tlb未命中,并且因此将快得多地运行。

53.即便如此,一些软件应用可主要经由4k页尺寸来访问存储器,并且可以根本不使用1g页尺寸。其他软件应用可主要经由2m页尺寸来访问存储器,并且可不使用具有4k页尺寸的存储器。因此,可能难以预测存储器使用模式,预测存储器模式将允许tlb最高效地操作。

54.在本公开中,tlb可使用可配置的子tlb来降低tlb未命中的可能性,该可配置的子tlb可配置成用于在引导后的不同时刻保存不同的页尺寸集以与在引导后保存固定的页尺寸集的固定的子tlb互补。如本文中所使用,页尺寸集表示可由子tlb容纳的页尺寸的集合(其可以是单个页尺寸(例如,4k、2m、1g)或两个或更多个页尺寸(例如,4k 2m、2m 1g、4k 1g、4k 2m 1g))。如下文所讨论,由可配置的子tlb使用的页尺寸集中的页的数量在运行时期间可改变(例如,可配置的全相联的子tlb在运行时期间的不同时刻可以是可重新配置的,以保存1g tlb条目、1g 2m、1g 4k、1g 2m 4k)。

55.固定的子tlb是在引导后可仅保存一个页尺寸集的子tlb。一些固定的子tlb在设计时可以是固定的,而其他固定的tlb在引导时可以是固定的。在任何情况下,固定的子tlb在引导后可能无法被动态地重新配置以保存不同的页尺寸集。在一个示例中,固定的子tlb可以是被定义为保存具有4k页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存4k tlb条目,但是无法保存2m或1g tlb条目。在另一示例中,固定的子tlb可以是被定义为保存具有4k和2m页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存4k和2m tlb条目,但是无法保存1g tlb条目。在进一步的示例中,固定的子tlb可以是被定义为保存具有2m和1g页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存2m和1g tlb条目,但是无法保存4k tlb条目。一旦要由固定的子tlb使用的页尺寸集被固定(例如,在设计时,在制造时,在现场部署时,在引导时),该固定的tlb就无法保存具有与见于固定的页尺寸集中的页尺寸不同的页尺寸的tlb条目。

56.相比之下,可配置的子tlb是tlb的、在引导后能够被动态地配置以保存具有多于一个的页尺寸集的tlb条目的部分。以此方式,可配置的子tlb可在操作期间容纳变化的存储器使用。可配置的子tlb的示例包括可配置的集合相联的子tlb或可配置的全相联的子tlb。可配置的集合相联的子tlb可在任何一个时刻支持与存储器的一个特定的页尺寸集对应的tlb条目,但是在引导后可被动态地配置(例如,初始地配置,或从初始配置重新配置),以改变哪个页尺寸集由可配置的集合相联的子tlb保存(例如,在第一时刻仅4k条目,在第

二时刻仅2m条目,在第三时刻仅1g条目)一些可配置的集合相联的子tlb可以可配置成在任何一个时刻保存多个页尺寸,并且那多个页尺寸中的哪个页尺寸被配置为被包含在页尺寸集中可在引导后随着存储器使用条件在操作期间改变而被动态地配置(例如,4k和2m、4k和1g、2m和1g)。例如,全相联的子tlb在一个时刻可支持4k/2m/1g页,但是随后可被重配置以仅支持1g页;或者2尺寸集合相联的可配置的子tlb可在一个时刻被配置以支持4k 1g页,并在另一时刻被配置以支持2m 1g页。全相联的子tlb可支持与存储器的多个特定的页尺寸(例如,4k、2m和1g)对应的tlb条目。可配置的子tlb可针对具有不同存储器尺寸使用的不同用例提供附加的灵活性,但是可能涉及比固定集合的子tlb更多的开销。

57.固定的子tlb与可配置的子tlb之间的差异可进一步通过以下示例来解释。考虑可具有1536倍条目的子tlb,这些条目可保存4k页和2m页的任何混合。此类子tlb可被视为固定的子tlb,因为它可处置由4k页尺寸和2m页尺寸组成的固定的页尺寸集。即便子tlb可能能够处置具有两个页尺寸的页尺寸集,这也是“固定”的。注意,1536=1024 512。一个“可配置的”选项将是建立两个子tlb,一个处置具有1024倍的固定的4k 2m尺寸的第一页尺寸集,并且第二个处置具有512倍的可配置条目的第二页尺寸集,该512倍的可配置条目可在不同时刻被配置以保存尺寸中的任何两个尺寸(例如,4k 2m、4k 1g、2m 1g)。

58.固定的子tlb和可配置的子tlb的组合可允许尺寸指派在运行时而不是在建立时动态地进行。以此方式,资源可被引导向具有最高未命中率的页尺寸。例如,如果对于具有4k页尺寸的条目需求最大,则可配置的集合相联的子tlb可被配置成用于保存具有包括4k页尺寸(例如,而不是2m或1g)的页尺寸集的条目,或者可配置的全相联的子tlb条目可容纳更多的4k tlb条目和更少的2m或1g tlb条目。在另一示例中,可配置的集合相联的子tlb。虽然本公开提供了与具有涉及可配置的全相联的子tlb和一个或多个固定的集合相联的子tlb的特定的页尺寸的条目的动态分配有关的许多示例,但是应当理解,可使用任何其他合适类型的固定的或可配置的子tlb。例如,可使用可配置的集合相联的子tlb(例如,取代可配置的全相联的子tlb,或取代固定的集合相联的子tlb中的一个或多个)。

59.这些特征可在任何合适的集成电路器件中使用,合适的集成电路器件包括微处理器、专用基础电路(asic)、或现场可编程门阵列(fpga)。下文参考图1-图9讨论的以下架构旨在表示可被使用的一个示例。

60.寄存器架构

61.图1是根据实施例的寄存器架构10的框图。在所图示的实施例中,存在多个(例如,32个)向量寄存器12,这些向量寄存器12可以是多个位(例如,512位)宽的。在寄存器架构10中;这些寄存器被引用为zmm0至zmmi。较低的n个(例如,16个)zmm寄存器的较低阶的(例如,256个)位覆盖在对应的寄存器ymm上。较低的n个zmm寄存器的较低阶的(例如,128个位)(其也是ymm寄存器的较低阶的n个位)覆盖在对应的寄存器xmm上。

62.写掩码寄存器14可包括m个(例如,8个)写掩码寄存器(k0至km),这些写掩码寄存器各自具有多个(例如,64个)位。附加地或替代地,写掩码寄存器14中的至少一些可具有不同的尺寸(例如,16位)。向量掩码寄存器12中的至少一些(例如,k0)被禁止用作写掩码。当此类向量掩码寄存器被指示时,硬连线的写掩码(例如,0xffff)被选择,并且实际上禁用针对那条指令的写掩码。

63.通用寄存器16可包括具有对应的位尺寸(例如,64)的多个(例如,16个)寄存器,这

些对应的位尺寸与x86寻址模式一起使用以对存储器操作数寻址。这些寄存器可通过名称rax、rbx、rcx、rdx、rbp、rsi、rdi、rsp以及r8至r15来引用。这些寄存器中的至少一些寄存器的部分(例如,寄存器的32个位)可被用于比寄存器的完整长度短的模式(例如,32位模式)。

64.标量浮点栈寄存器堆(x87栈)18具有被混叠的mmx紧缩整数平坦寄存器堆20。x87栈18是用于使用x87指令集扩展对浮点数据执行标量浮点操作的八元素的(或其他数量的元素的)栈。浮点数据可具有各种精度水平(例如,16位、32位、64位、80位、或更多位)。mmx紧缩整数平台寄存器堆20被用于对64位紧缩整数数据执行操作,并且被用于保存用于在mmx紧缩整数平台寄存器堆20与xmm寄存器之间执行的一些操作的操作数。

65.替代实施例可以使用更宽的或更窄的寄存器。另外,替代实施例可以使用更多、更少或不同的寄存器堆和寄存器。

66.核架构、处理器和计算机架构

67.处理器核能以不同的方式、出于不同的目的并且在不同的处理器中实现。例如,此类核的实现可以包括:1)适用于通用计算的通用有序核;2)适用于通用计算的高性能通用乱序核;3)主要适用于图形和/或科学(吞吐量)计算的专用核。不同处理器的实现可包括:1)cpu,其包括适用于通用计算的一个或多个通用有序核和/或适用于通用计算的一个或多个通用乱序核;以及2)协处理器,其包括主要用于图形和/或科学(吞吐量)的一个或多个专用核。此类不同的处理器导致不同的计算机系统架构,这些计算机系统架构可包括:1)在与cpu分开的芯片上的协处理器;2)在与cpu相同的封装中但在分开的管芯上的协处理器;3)与cpu在相同管芯上的协处理器(在该情况下,此类协处理器有时被称为专用逻辑或被称为专用核,该专用逻辑诸如,集成图形和/或科学(吞吐量)逻辑);以及4)芯片上系统,其可以将所描述的cpu(有时被称为(多个)应用核或(多个)应用处理器)、以上描述的协处理器和附加功能包括在同一管芯上。接着描述示例核架构,随后描述示例处理器和计算机架构。

68.有序和乱序核架构

69.图2a是图示出根据本公开的实施例的有序流水线和寄存器重命名的、乱序发布/执行流水线的框图。图2b是图示出根据实施例的要包括在处理器中的有序架构核的实施例和示例寄存器重命名的、乱序发布/执行架构核两者的框图。图2a-图2b中的实线框图示有序流水线和有序核,而虚线框的任选增加图示寄存器重命名的、乱序发布/执行流水线和核。考虑到有序方面是乱序方面的子集,将描述乱序方面。

70.在图2a中,处理器中的流水线30包括取出级32、长度解码级34、解码级36、分配级38、重命名级40、调度(也被称为分派或发布)级42、寄存器读取/存储器读取级44、执行级46、写回/存储器写入级48、异常处置级50和提交级52。

71.图2b示出处理器核54,该处理器核54包括前端单元56,该前端单元56耦合到执行引擎单元58,并且前端单元56和执行引擎单元58两者都耦合到存储器单元6。处理器核54可以是精简指令集计算(risc)核、复杂指令集计算(cisc)核、超长指令字(vliw)核、或混合或替代的核类型。作为又一选项,处理器核54可以是专用核,诸如例如,网络或通信核、压缩引擎、协处理器核、通用计算图形处理单元(gpgpu)核、图形核,等等。

72.前端单元56包括分支预测单元62,该分支预测单元耦合到指令高速缓存单元64,该指令高速缓存单元64耦合到指令转换后备缓冲器(tlb)单元66。tlb 66耦合到指令取出单元68。指令取出单元68耦合到解码电路70。解码电路70(或解码器)可对指令解码,并且生

成从原始指令解码出的、或以其他方式反映原始指令的、或从原始指令导出的一个或多个微操作、微代码进入点、微指令、其他指令、或其他控制信号作为输出。解码电路70可使用各种不同的机制来实现。合适机制的示例包括但不限于,查找表、硬件实现、可编程逻辑阵列(pla)、微代码只读存储器(rom)等。处理器核54可包括存储用于宏指令的微代码的微代码rom或其他介质(例如,在解码电路70中,或以其他方式在前端单元56内)。解码电路70耦合到执行引擎单元58中的重命名/分配器单元72。

73.执行引擎单元58包括重命名/分配器单元72,该重命名/分配器单元72耦合到引退单元74和一个或多个调度器单元的集合76。(多个)调度器单元76表示任何数量的不同调度器,包括预留站、中央指令窗等。(多个)调度器单元76耦合到(多个)物理寄存器堆单元78。(多个)物理寄存器堆单元78中的每一个物理寄存器堆单元表示存储一种或多种不同数据类型的一个或多个物理寄存器堆,不同的数据类型诸如,标量整数、标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点,状态(例如,作为要执行的下一条指令的地址的指令指针)等等。在一个实施例中,(多个)物理寄存器堆单元78包括向量寄存器12、写掩码寄存器14、和/或x87栈18。这些寄存器单元可以提供架构向量寄存器、向量掩码寄存器和通用寄存器。(多个)物理寄存器堆单元78由引退单元74重叠,以图示可实现寄存器重命名和乱序执行的各种方式(例如,使用(多个)重排序缓冲器和(多个)引退寄存器堆;使用(多个)未来文件、(多个)历史缓冲器、(多个)引退寄存器堆;使用寄存器映射和寄存器池,等等)。

74.引退单元74和(多个)物理寄存器堆单元78耦合到(多个)执行集群80。(多个)执行集群80包括一个或多个执行单元的集合82以及一个或多个存储器访问电路的集合84。执行单元82可执行各种操作(例如,移位、加法、减法、乘法)并可对各种数据类型(例如,标量浮点、紧缩整数、紧缩浮点、向量整数、向量浮点)执行。尽管一些实施例可以包括专用于特定功能或功能集合的多个执行单元,但是其他实施例可包括仅一个执行单元或全都执行多个不同功能的多个执行单元。(多个)调度器单元76、(多个)物理寄存器堆单元78、以及(多个)执行集群80被示出为单数或附属,因为一些处理器核54为某些类型的数据/操作创建分开的流水线(例如,各自具有其自身的调度器单元、(多个)物理寄存器堆单元、和/或执行集群的标量整数流水线、标量浮点/紧缩整数/紧缩浮点/向量整数/向量浮点流水线、和/或存储器访问流水线。在分开的存储器访问流水线的情况下,用于该分开的存储器访问流水线的处理器核54是仅有的具有存储器访问电路84的执行集群80。还应当理解,在使用分开的流水线的情况下,这些流水线中的一个或多个可以是乱序发布/执行,并且其余流水线执行有序执行。

75.存储器访问电路84的集合耦合到存储器单元60。存储器单元60包括数据tlb单元86,该数据tlb单元86耦合到数据高速缓存单元88,该数据高速缓存单元88耦合到第二级(l2)高速缓存单元90。存储器访问单元84可包括加载单元、存储地址单元和存储数据单元,其中的每一个均耦合到存储器单元60中的数据tlb单元86。指令高速缓存单元64还耦合到存储器单元60中的第二级(l2)高速缓存单元90。l2高速缓存单元90到一个或多个其他级别的高速缓存,和/或耦合到主储器。

76.作为示例,寄存器重命名的乱序发布/执行核架构可如下所述地实现流水线30:1)指令取出68执行流水线30的取出级32和长度解码级34;2)解码电路70执行流水线30的解码级36;3)重命名/分配器单元72执行流水线的分配级38和重命名级40;4)(多个)调度器单元

76执行流水线30调度级42;5)(多个)物理寄存器堆单元78和存储器单元60执行流水线30的寄存器读取/存储器读取级44;执行集群80执行流水线30的执行级46);6)存储器单元60和(多个)物理寄存器堆单元78执行流水线30的写回/存储器写入级48;7)各单元可牵涉到流水线的异常处置级50;和/或8)引退单元74和(多个)物理寄存器堆单元78执行流水线30的提交级52。

77.处理器核54可支持一个或多个指令集(诸如,x86指令集(具有或不具有用于更新版本的附加扩展)、加利福尼亚州桑尼威尔的mips技术公司的mips指令集、加利福尼亚州桑尼威尔的arm控股公司的arm指令集(具有可选附加扩展,诸如neon))。附加地或替代地,处理器核54包括用于支持紧缩数据指令集扩展(例如,avx1、avx2)的逻辑,由此允许使用紧缩数据来执行由许多多媒体应用使用的操作。

78.应当理解,核可支持多线程化(执行两个或更多个并行的操作或线程的集合),并且可以按各种方式来完成该多线程化,各种方式包括时分多线程化、同时多线程化(其中单个物理核为物理核正在同时多线程化的线程中的每一个线程提供逻辑核)、或其组合(诸如,时分取出和解码以及超线程化技术中的同时多线程化)。

79.尽管在乱序执行的上下文中描述了寄存器重命名,但是可以在有序架构中使用寄存器重命名。尽管所图示的处理器的实施例还包括分开的指令高速缓存单元64、分开的数据高速缓存单元88、以及共享的l2高速缓存单元90,但是一些实施例可以具有用于指令和数据两者的单个内部高速缓存,诸如例如,第一级(l1)内部高速缓存或多个级别的内部高速缓存。在一些实施例中,该处理器可包括内部高速缓存和在处理器核54和/或处理器外部的外部高速缓存的组合。替代地,一些处理器可使用在处理器核54和/或处理器外部的高速缓存。

80.图3a和图3b图示出有序核架构的更详细的框图。处理器核54包括芯片中的一个或多个逻辑块(包括相同类型和/或不同类型的其他核)。取决于应用,逻辑块通过高带宽互连网络(例如,环形网络)与一些固定的功能逻辑、存储器i/o接口和其他i/o逻辑进行通信。

81.图3a是根据本公开的实施例的单个处理器核54以及它至管芯上互连网络100的连接及其第二级(l2)高速缓存的本地子集104的框图。在一个实施例中,指令解码器102支持具有紧缩数据指令集扩展的x86指令集。l1高速缓存106允许对进入标量和向量单元中的、对高速缓存存储器的低等待时间访问。尽管在一个实施例中(为了简化设计),标量单元108和向量单元110使用分开的寄存器集合(分别为标量寄存器112(例如,x87栈18)和向量寄存器114(例如,向量寄存器112)),并且在这些寄存器之间传输的数据被写入到存储器,并随后从第一级(l1)高速缓存106读回,但是本公开的替代实施例可以使用不同的方法(例如,使用单个寄存器集合或包括允许数据在这两个寄存器堆之间传输而无需被写入和读回的通信路径)。

82.l2高速缓存的本地子集104是全局l2高速缓存单元90的一部分,该全局l2高速缓存单元90被划分成多个分开的本地子集,每个处理器核一个本地子集。每个处理器核54具有到其自身的l2高速缓存的本地子集104的直接访问路径。由处理器核54读取的数据被存储在其l2高速缓存子集104中,并且可以与其他处理器核54访问其自身的本地l2高速缓存子集并行地被快速访问。由处理器核54写入的数据被存储在其自身的l2高速缓存子集104中,并在必要的情况下从其他子集转储清除。互连网络100确保共享数据的一致性。互连网

络100是双向的,以允许诸如处理器核、l2高速缓存和其他逻辑块之类的代理在芯片内彼此通信。每条数据路径在每个方向上可具有多个(例如,1012个)位的宽度。

83.图3b是根据本公开的实施例的图3a中的处理器核的一部分的展开图。图3b包括l1高速缓存106的l1数据高速缓存106a部分,以及关于向量单元110和向量寄存器114的更多细节。具体地,向量单元110可以是向量处理单元(vpu)(例如,向量算术逻辑单元(alu)118),该vpu执行整数、单精度浮点以及双精度浮点指令中的一条或多条。该vpu通过混合单元120支持对寄存器输入的混合,通过数值转换单元122a和122b支持数值转换,并且通过复制单元124支持对存储器输入的复制。写掩码寄存器14允许预测所得的向量写入。

84.图4是根据本公开的实施例的可具有多于一个的处理器核54、可具有(多个)集成存储器控制器单元132、以及可具有集成图形器件的处理器130的框图。图4中的实线框图示出具有单个核54a、系统代理单元134、一个或多个总线控制器单元的集合138的处理器130,而虚线框的任选的附加图示出具有多个核54a-54n、系统代理单元134中的一个或多个集成存储器控制器单元的集合132、以及专用逻辑136的处理器130。

85.因此,处理器130的不同实现可包括:1)cpu,其中专用逻辑136是集成图形和/或科学(吞吐量)逻辑(其可包括一个或多个核),并且核54a-n是一个或多个通用核(例如,通用有序核、通用乱序核、或其组合);2)协处理器,其中核54a-n是旨在主要用于图形和/或科学(吞吐量)的相对大量的专用核;以及3)协处理器,其中核54a-n是相对大量的通用有序核。因此,处理器130可以是通用处理器、协处理器或专用处理器,诸如例如,网络或通信处理器、压缩引擎、图形处理器、gpgpu(通用图形处理单元)、高吞吐量的集成众核(mic)协处理器(包括30个或更多核)、嵌入式处理器,等等。该处理器130可以被实现在一个或多个芯片上。处理器130可以是一个或多个基板的一部分,和/或可使用多种工艺技术(诸如例如,bicmos、cmos、或nmos)中的任何技术被实现在一个或多个基板上。

86.存储器层次结构包括核内的一个或多个高速缓存级别、一个或多个共享高速缓存单元的集合140、以及耦合到集成存储器控制器单元的集合132的外部存储器(未示出)。共享高速缓存单元的集合140可包括一个或多个中间级别的高速缓存,诸如,第二级(l2)、第三级(l3)、第四级(l4)或其他级别的高速缓存、末级高速缓存(llc)和/或以上各项的组合。虽然基于环的互连网络100可将集成图形逻辑136(集成图形逻辑136是其示例,并且在本文中还被称为专用逻辑136)、共享高速缓存单元的集合140和/或系统代理单元134/(多个)集成存储器控制器单元132互连,但是可使用任何数量的公知技术来互连此类单元。例如,可在一个或多个高速缓存单元142a-n与核54a-n之间维持一致性。

87.在一些实施例中,一个或多个核54a-n能够实现多线程化。系统代理单元134包括协调和操作核54a-n的那些组件。系统代理单元134可包括例如功率控制单元(pcu)和显示单元。pcu可以是或可包括用于对核54a-n以及集成图形逻辑136的功率状态进行调节的逻辑和组件,或可包括这些逻辑和组件。显示单元用于驱动一个或多个外部连接的显示器。

88.核54a-n在架构指令集方面可以是同构或异构的。也就是说,核54a-n中的两个或更多个可以能够执行同一指令集,而其他核可能仅能够执行单个指令集的子集或不同的指令集。

89.计算机架构

90.图5-图8是计算机架构的实施例的框图。这些架构可适于膝上型设备、台式机、手

持pc、个人数字助理、工程工作站、服务器、网络设备、网络集线器、交换机、嵌入式处理器、数字信号处理器(dsp)、图形设备、视频游戏设备、机顶盒、微控制器、蜂窝电话、便携式媒体播放器、手持设备以及各种其他电子设备的其他系统设计和配置。一般而言,能够并入处理器130和/或其他执行逻辑的各种广泛的系统或电子设备。

91.现在参考图5,所示出的是根据实施例的系统150的框图。系统150可以包括一个或多个处理器130a、130b,这些处理器耦合到控制器中枢152。控制器中枢152可包括图形存储器控制器中枢(gmch)154和输入/输出中枢(ioh)156(其可以在分开的芯片上);gmch 154包括存储器和图形控制器,存储器158和协处理器160耦合到该存储器和图形控制器;ioh 156将输入/输出(i/o)设备164耦合到gmch 154。或者,存储器和图形控制器中的一个或这两者被集成在(如本文中所描述的)处理器130内,存储器158和协处理器160耦合到(例如,直接耦合到)处理器130a,并且控制器中枢152与ioh 156处于单个芯片中。

92.附加的处理器130b的任选性在图5中通过虚线来表示。每一处理器130a、130b可包括本文中描述的处理核54中的一个或多个,并且可以是处理器130的某一版本。

93.存储器158可以是例如动态随机存取存储器(dram)、相变存储器(pcm)或其组合。对于至少一个实施例,控制器中枢152经由诸如前端总线(fsb)之类的多分支总线、诸如快速路径互连(qpi)之类的点对点接口、或者类似的连接162与(多个)处理器130a、130b进行通信。

94.在一个实施例中,协处理器160是专用处理器,诸如例如,高吞吐量mic处理器、网络或通信处理器、压缩引擎、图形处理器、gpgpu、嵌入式处理器,等等。在实施例中,控制器中枢152可以包括集成图形加速器。

95.在处理器130a、130b的物理资源之间可以存在包括架构、微架构、热、功耗特性等一系列品质度量方面的各种差异。

96.在一些实施例中,处理器130a执行控制一般类型的数据处理操作的指令。嵌入在这些指令内的可以是协处理器指令。处理器130a将这些协处理器指令识别为具有应当由附连的协处理器160执行的类型。因此,处理器130a在协处理器总线或者其他互连上将这些协处理器指令(或者表示协处理器指令的控制信号)发布到协处理器160。协处理器160接受并执行所接收的协处理器指令。

97.现在参见图6,所示出的是根据实施例的多处理器系统170的更详细的框图。如图6中所示,多处理器系统170是点对点互连系统,并且包括经由点对点接口190耦合的处理器172和处理器174。处理器172和174中的每一个都可以是处理器130的某一版本。在本公开的一个实施例中,处理器172和174分别是处理器130a和130b,而协处理器176是协处理器160。在另一实施例中,处理器172和174分别是处理器130a和协处理器160。

98.处理器172和174示出为分别包括集成存储器控制器(imc)单元178和180。处理器172还包括点对点(p-p)接口182和184作为其总线控制器单元的部分。类似地,处理器174包括p-p接口186和188。处理器172、174可经由使用p-p接口184、188的点对点接口190来交换信息。如图6中所示,imc178和180将处理器耦合到相应的存储器,即存储器192和存储器193,这些存储器可以是本地附连到相应处理器172、174的主存储器的不同部分。

99.处理器172和174可各自经由使用点对点接口182、200、186、202的各个p-p接口196、198与芯片组194交换信息。芯片组194可以任选地经由高性能接口204来与协处理器

174交换信息。在实施例中,协处理器176是专用处理器,诸如例如,高吞吐量mic处理器、网络或通信处理器、压缩引擎、图形处理器、gpgpu、嵌入式处理器,等等。

100.共享高速缓存(未示出)可被包括在任一处理器172或174中,或在这两个处理器172或174的外部的、经由相应的p-p互连与处理器172、174连接,使得如果相应的处理器被置于低功率模式,则任一个或这两个处理器的本地高速缓存信息可被存储在共享高速缓存中。

101.芯片组194可以经由接口208耦合到第一总线206。在实施例中,第一总线206可以是外围组件互连(pci)总线或诸如pci快速总线或另一第三代i/o互连总线之类的总线,但是本公开的范围不限于此。

102.如图6中所示,各种i/o设备210可连同总线桥212一起耦合到第一总线206,该总线桥212将第一总线206耦合到第二总线214。在实施例中,诸如协处理器、高吞吐量mic处理器、gpgpu、加速器(诸如例如,图形加速器或数字信号处理(dsp)单元)、现场可编程门阵列或任何其他处理器的一个或多个附加处理器216耦合到第一总线206。在实施例中,第二总线214可以是低引脚数(lpc)总线。在一个实施例中,各种设备可耦合到第二总线214,这些设备包括例如键盘和/或鼠标218、通信设备220以及存储单元222,该存储单元222诸如可包括指令/代码和数据224的盘驱动器或者其他大容量存储设备。此外,音频i/o 226可以被耦合到第二总线214。注意,可为多处理器系统170部署其他架构。例如,代替图6的点对点架构,多处理器系统170可以实现多分支总线或其他此类架构。

103.现在参考图7,所示出的是根据实施例的系统230的框图。图7和图8中的类似元件包含类似的附图标记,并且已从图7中省略了图6的某些方面以避免混淆图7的其他方面。

104.图7图示处理器172、174可分别包括集成存储器和i/o控制逻辑(“imc”)178和180。因此,imc 178、180包括集成存储器控制器单元,并包括i/o控制逻辑。图7示出不仅存储器192、193耦合至imc 178、180,而且i/o设备231也耦合至imc 178、180。传统i/o设备232经由接口208耦合至芯片组194。

105.现在参考图8,示出的是根据实施例的soc 250的框图。图4中的类似要素具有类似的附图标记。另外,虚线框是被包括在一些soc 250中的任选的特征。在图8中,(多个)互连单元252被耦合到:应用处理器254,其包括一个或多个核的集合54a-n的集合以及(多个)共享高速缓存单元140,一个或多个核的集合54a-n包括高速缓存单元142a-n;系统代理单元134;(多个)总线控制器单元138;(多个)集成存储器控制器单元132;一个或多个协处理器的集合256,其可包括集成图形逻辑、图像处理器、音频处理器和/或视频处理器;静态随机存取存储器(sram)单元258;直接存储器存取(dma)单元260;以及用于耦合到一个或多个外部显示器的显示单元262。在实施例中,(多个)协处理器256包括专用处理器,诸如例如,网络或通信处理器、压缩引擎、gpgpu、高吞吐量mic处理器、或嵌入式处理器,等等。

106.本文公开的机制的各实施例可以被实现在硬件、软件、固件或此类实现方式的组合中。本公开的实施例可实现为在可编程系统上执行的计算机程序和/或程序代码,该可编程系统包括至少一个处理器、存储系统(包括易失性和非易失性存储器和/或存储元件)、至少一个输入设备以及至少一个输出设备。

107.可将程序代码(诸如,图6中图示的数据224)应用于输入指令,以执行本文中描述的功能并生成输出信息。可以将输出信息应用于一个或多个输出设备。为了本技术的目的,

处理系统包括具有处理器的任何系统,该处理器诸如例如,数字信号处理器(dsp)、微控制器、专用集成电路(asic)或微处理器。

108.程序代码可以用高级的面向过程的编程语言或面向对象的编程语言来实现,以便与处理系统通信。程序代码还能以汇编语言或以机器语言来实现。事实上,本文中描述的机制不限于任何特定的编程语言的范围。在任何情况下,该语言可以是编译语言或解释语言。

109.至少一个实施例的一个或多个方面可以由存储在机器可读介质上的表示性指令来实现,该指令表示处理器中的各种逻辑,该指令在被机器读取时使得该机器制造用于执行本文中所述的技术的逻辑。被称为“ip核”的此类表示可以被存储在有形的机器可读介质上,并可被供应给各个客户或生产设施以加载到制造该逻辑或处理器的制造机器中。

110.此类机器可读存储介质可以包括但不限于通过机器或设备制造或形成的制品的非暂态、有形布置,其包括存储介质,诸如硬盘;任何其他类型的盘,包括软盘、光盘、紧致盘只读存储器(cd-rom)、可重写紧致盘(cd-rw)以及磁光盘;半导体器件,诸如,只读存储器(rom)、诸如动态随机存取存储器(dram)和静态随机存取存储器(sram)的随机存取存储器(ram)、可擦除可编程只读存储器(eprom)、闪存、电可擦除可编程只读存储器(eeprom);相变存储器(pcm);磁卡、光卡;或适于存储电子指令的任何其他类型的介质。

111.因此,本公开的实施例包括非暂态的有形机器可读介质,该介质包含指令或包含设计数据,诸如按照硬件描述语言(hdl)的设计,它可定义本文中描述的结构、电路、装置、处理器和/或系统特征。此类实施例也可被称为程序产品。

112.仿真

113.在一些情况下,指令转换器可用于将指令从源指令集转换至目标指令集。例如,指令转换器可以将指令变换(例如,使用静态二进制变换、包括动态编译的动态二进制变换)、变形、仿真或以其他方式转换成要由核处理的一条或多条其他指令。指令转换器可以用软件、硬件、固件、或其组合来实现。指令转换器可以实现在处理器上、在处理器外、或者部分在处理器上且部分在处理器外。

114.图9是根据本公开的实施例的对照使用软件指令转换器将源指令集中的二进制指令转换成目标指令集中的二进制指令的框图。在所图示的实施例中,指令转换器是软件指令转换器,但替代地,该指令转换器可以用软件、固件、硬件或其任何组合来实现。图9示出可使用x86编译器282来编译高级语言280形式的程序,以生成可由具有至少一个x86指令集核的处理器286原生执行的x86二进制代码284。具有至少一个x86指令集核的处理器286表示通过兼容地执行或以其他方式执行以下各项来执行与具有至少一个x86指令集核英特尔处理器基本相同的功能的任何处理器:1)英特尔x86指令集核的指令集的本质部分,或2)目标为在具有至少一个x86指令集核的英特尔处理器上运行以便取得与具有至少一个x86指令集核的英特尔处理器基本相同的结果的应用或其他软件的目标代码版本。x86编译器282表示可操作用于生成x86二进制代码284(例如,目标代码)的编译器,该二进制代码可通过或不通过附加的链接处理在具有至少一个x86指令集核的处理器286上执行。

115.类似地,图9示出可以使用替代的指令集编译器288来编译高级语言280形式的程序,以生成可以由不具有至少一个x86指令集核的处理器292(例如,具有执行加利福尼亚州桑尼维尔市的mips技术公司的mips指令集、和/或执行加利福尼亚州桑尼维尔市的arm控股公司的arm指令集的处理器核54的处理器)原生执行的替代的指令集二进制代码290。指令

转换器294用于将x86二进制代码284转换成可以由不具有x86指令集核的处理器292原生执行的代码。该转换后的代码不大可能与替代的指令集二进制代码290相同,因为能够这样做的指令转换器难以制造;然而,转换后的代码可完成一般操作,并且由来自替代指令集的指令构成。因此,指令转换器294通过仿真、模拟或任何其他过程来表示允许不具有x86指令集处理器或核的处理器或其他电子设备执行x86二进制代码284的软件、固件、硬件或其组合。

116.转换后备缓冲器(tlb)

117.如上文所讨论,集成电路可出于各种目的(例如,指令数据、用户数据)检取存储器。虽然数据被存储在表示存储器设备中的实际位置的物理存储器地址中,但是在集成电路上运行的软件可使用虚拟存储器地址来操作,当存储器被访问时,该虚拟存储器地址被转换为物理存储器地址。被称为转换后备缓冲器(tlb)(例如,指令tlb 66或数据tlb 86)的集成电路上的结构可通过存储虚拟存储器地址至其对应的物理存储器地址的近期使用的映射来减少访问存储器位置所花费的时间。虽然下文的公开内容专门参考tlb 86,但是应当理解,与tlb 86有关的架构和方法可在任何合适的tlb(其可包括tlb 66或其他tlb)中被使用。当数据利用电路(例如,运行软件的处理电路)请求对在近期被使用的且被存储在tlb中的特定虚拟存储器地址的访问时,该tlb可迅速地将虚拟存储器地址转换为其对应的物理存储器地址。

118.例如,如图10中所示,tlb 86可接收tlb请求300(例如,标识虚拟存储器地址的请求),该tlb请求300在tlb 86中具有对应的tlb条目。这可被称为“高速缓存命中”或“tlb命中”。tlb 86可利用响应302(例如,标识与虚拟存储器地址对应的物理地址)来作出响应。然而,如图11中所示,当tlb当前不具有与tlb请求300对应的tlb条目时,这可被称为“高速缓存未命中”或“tlb未命中”。tlb未命中处置过程被用于获得对应的tlb条目,包括地址映射和页尺寸(例如,可通过一个或多个页表306执行搜索304)两者以获得对应的tlb条目308tlb 86可将tlb条目308加载到tlb中,并且发布tlb响应302。

119.tlb86可使用可配置的子tlb来降低tlb未命中的可能性,该可配置的子tlb可配置成用于在引导后的不同时刻保存不同的页尺寸集以与在引导后保存固定的页尺寸集的固定的子tlb互补。如本文中所使用,页尺寸集表示可由子tlb容纳的页尺寸的集合(其可以是单个页尺寸(例如,4k、2m、1g)或两个或更多个页尺寸(例如,4k 2m、2m 1g、4k 1g、4k 2m 1g))。如下文所讨论,由可配置的子tlb使用的页尺寸集中的页的数量在运行时期间可改变(例如,可配置的全相联的子tlb在运行时期间的不同时刻可以是可重新配置的,以保存1g tlb条目、1g 2m、1g 4k、1g 2m 4k)。

120.如上文所提及,固定的子tlb是在引导后可仅保存一个页尺寸集的子tlb。一些固定的子tlb在设计时可以是固定的,而其他固定的tlb在引导时可以是固定的。在任何情况下,固定的子tlb可以在引导后不被动态地重新配置以保存不同的页尺寸集。在一个示例中,固定的子tlb可以是被定义为保存具有4k页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存4k tlb条目,但是无法保存2m或1g tlb条目。在另一示例中,固定的子tlb可以是被定义为保存具有4k和2m页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存4k和2m tlb条目,但是无法保存1g tlb条目。在进一步的示例中,固定的子tlb可以是被定义为保存具有2m和1g页尺寸的固定的页尺寸集的子tlb;在运行时期间,该固定的子tlb可保存2m和1g tlb条目,但是无法保存4k tlb条目。一旦要由固定的

子tlb使用的页尺寸集被固定(例如,在设计时,在制造时,在现场部署时,在引导时),该固定的tlb就无法保存具有与见于固定的页尺寸集中的页尺寸不同的页尺寸的tlb条目。

121.相比之下,可配置的子tlb是tlb的、在引导后能够被动态地配置以保存具有多于一个的页尺寸集的tlb条目的部分。以此方式,可配置的子tlb可在操作期间容纳变化的存储器使用。可配置的子tlb的示例包括可配置的集合相联的子tlb或可配置的全相联的子tlb。可配置的集合相联的子tlb可在任何一个时刻支持与存储器的一个特定的页尺寸集对应的tlb条目,但是在引导后可被动态地配置(例如,初始地配置,或从初始配置重新配置),以改变哪个页尺寸集由可配置的集合相联的子tlb保存(例如,在第一时刻仅4k条目,在第二时刻仅2m条目,在第三时刻仅1g条目)一些可配置的集合相联的子tlb可以被配置成在任何一个时刻保存多个页尺寸,并且那多个页尺寸中的哪个页尺寸被配置为被包含在页尺寸集中可在引导后随着存储器使用条件在操作期间改变而被动态地配置(例如,4k和2m、4k和1g、2m和1g)。例如,可配置的全相联的子tlb在一个时刻可支持4k/2m/1g页,但是随后可被重配置以仅支持1g页;或者2尺寸集合相联的可配置的子tlb可在一个时刻被配置以支持4k 1g页,并在另一时刻被配置以支持2m 1g页。可配置的全相联的子tlb可支持与存储器的多个特定的页尺寸(例如,4k、2m和1g)对应的tlb条目。可配置的子tlb可针对具有不同存储器尺寸使用的不同用例提供附加的灵活性,但是可能涉及比固定的子tlb更多的开销。

122.固定的子tlb与可配置的子tlb之间的差异可进一步通过以下示例来解释。考虑可具有1536倍条目的固定的子tlb,这些条目可保存4k页和2m页的任何混合。此类子tlb可被视为固定的子tlb,因为它可处置由4k页尺寸和2m页尺寸组成的固定的页尺寸集。即便子tlb可能能够处置具有两个页尺寸的页尺寸集,这也是“固定”的。注意,1536=1024 512。一个“可配置的”选项将是建立两个子tlb,一个处置具有1024倍的固定的4k 2m尺寸的第一页尺寸集,并且第二个处置具有512倍的可配置条目的第二页尺寸集,该512倍的可配置条目可在不同时刻被配置以保存尺寸中的任何两个尺寸(例如,4k 2m、4k 1g、2m 1g)。

123.为了进行重申,子tlb可在以下方面变化:(1)它支持的(多个)尺寸——可能是一个页尺寸,但是可能是若干个页尺寸;以及(2)所支持的页尺寸的集合是否是固定的设计时(或者说,引导时)选择,或它是否能够被动态地重新配置/调整。本公开的系统可与可使用以下各项的许多tlb(例如,某些第一级tlb(l1dtlb))的结构形成对照:(1)支持仅一个尺寸的固定的集合相联的子tlb,并且该尺寸在设计时被选择(“一个尺寸”使其更易于满足电路时序);或(2)小的全相联的子tlb。这些全相联的子tlb可以是单尺寸(如在许多情况下,其可使用1g fa子tlb)或多尺寸(如在许多情况下,其在fa tlb中支持4k/2m/1g)的,但是尺寸选择在设计时被固定,并且它们不使全尺寸fa子tlb与另一子tlb配对,因此它们没有决定要使用哪个子tlb来填充条目的问题/考量——l1dtlb仅是4k 2m 1g fa结构,因此没有它们能够选择的其他子tlb。

124.本公开的系统和方法还可与其他tlb的结构形成对照,其他tlb诸如使用支持两个尺寸的固定的集合相联的子tlb的许多第二级tlb(l2tlb),并且该尺寸在设计时被固定。对于许多处理器,存在支持4k 2m页的任何混合的l2子tlb。“两个尺寸”使得更难满足电路时序(因此不在l1tb中使用),但是能够更高效,因为所有条目能够被用于尺寸的任何混合。然而,虽然这是多个尺寸,但是尺寸在设计时被选择。

125.本文中所使用的是支持动态可配置的页尺寸的子tlb。这回避了一些电路设计问

题(例如,建立固定的2尺寸l2子tlb会具有一些弊端,建立固定的3尺寸l2子tlb会具有甚至更多弊端)。使用可配置的2尺寸tlb使我们挑选要支持的2个页(因此,它是3尺寸的,但一时刻仅具有2个尺寸),这放弃了一些灵活性,但是这是比固定的3尺寸子tlb更简单/更快的电路。考虑在其中本公开的tlb具有固定配置的2尺寸子tlb、固定配置的3尺寸子tlb、以及可在三个尺寸之间进行配置的(但是一个时刻仅具有两个尺寸)可配置的2尺寸子tlb的示例。在此,将该示例的可配置的子tlb视为是“2尺寸”的是言之有理的,因为它对于任何一个配置仅具有2个尺寸,但是它也是“3尺寸”的,因为它可在3个页尺寸之间进行重新配置(即便在任何给定的配置中它仅可支持2个页尺寸)。注意,在一些情况下,可配置的子tlb可以是能够保存一些尺寸的唯一的子tlb——例如,tlb可以是可配置的全相联的子tlb,其是用于保存1g tlb条目的唯一地方。因此在其中存在许多1g tlb条目(或对1g tlb条目的高未命中率)的情况下,期望防止4k/2m映射驱逐1g映射。因此,在诸如这些情况的情况下,一些页尺寸在某些条件下可被视为是“特殊的”(例如,它们可被标记为“粘性”,如下文进一步所讨论)。

126.固定的子tlb和可配置的子tlb的组合可允许尺寸指派在运行时而不是在建立时动态地进行。以此方式,资源可被引导向具有最高未命中率的页尺寸。例如,如果对于具有4k页尺寸的条目需求最大,则可配置的集合相联的子tlb可被配置成用于保存具有包括4k页尺寸(例如,而不是2m或1g)的页尺寸集的条目,或者可配置的全相联的子tlb条目可容纳更多的4k tlb条目和更少的2m或1g tlb条目。在另一示例中,可配置的集合相联的子tlb。虽然本公开提供了与具有涉及可配置的全相联的子tlb和一个或多个固定的集合相联的子tlb的特定的页尺寸的条目的动态分配有关的许多示例,但是应当理解,可使用任何其他合适类型的固定的或可配置的子tlb。例如,可使用可配置的集合相联的子tlb(例如,取代全相联的子tlb,或取代固定的集合相联的子tlb中的一个或多个)。

127.在图12-图15中示出tlb的若干非限制性示例,其中,可配置的全相联的子tlb与若干固定的集合相联的子tlb互补。虽然以下公开内容中的许多内容提供了与使用可配置的全相联的子tlb和一个或多个固定的集合相联的子tlb对具有特定页尺寸的条目进行动态分配的示例,但是应当理解,可是哟红可配置的集合相联的子tlb(例如,取代可配置的全相联的子tlb,或取代固定页尺寸的集合相联的子tlb中的一个或多个)。例如,常规tlb能以配置成用于保存1g映射的固定的子tlb建立。在较旧的软件上运行的较新的硬件可能经历在其中1g页从未被使用的用例,因此,替代地建立可配置的子tlb可能是优势,并且当没有1g页正在被使用时,它可被配置成保存全部4k或全部2k。类似地,可以存在3个页尺寸和4个子tlb,其中,子tlb中的一个是集合相联的且可配置的,并且“游走”在多个页尺寸之间,以助力解决当前具有最糟的未命中问题的无论什么页尺寸。

128.作为具体示例,tlb可使用保存4k和2m映射的固定的集合相联的子tlb、以及保存1g映射的全相联的子tlb。全相联的子tlb可用2尺寸固定的集合相联的子tlb替换,其中,尺寸可被重新配置为以下尺寸中的一些或全部:仅4k、仅2m、仅1g、4k 2m、4k 1g、或2m 1g。例如,如果没有1g页在使用中,则它可被配置为4k 2m;如果1g页在使用中,则取决于哪个页当前正在遭受最糟的未命中率,它可被配置为4k 1g或2m 1g。

129.转到图12,tlb 86包括与三个不同的存储器页对应的固定的集合相联的子tlb 320、322和324。在将在下文中讨论的示例中,固定的集合相联的子tlb 320、322和324可以

是支持具有单个相应的特定页尺寸的特定的页尺寸集的相应的固定的集合相联的子tlb。附加地或替代地,tlb 86可使用支持包括多个页尺寸的页尺寸集(例如,4k 2m、2m 1g、4k 1g)的一个或多个固定的集合向量的子tlb。此外,附加地或替代地,固定的集合相联的子tlb 320、322和324可以是可被改变(例如,在上下文切换时,或基于与针对特定的页尺寸的tlb未命中有关的计数)以在不同时刻支持不同的特定页尺寸集(例如,在以一个时刻全部为1g,在另一时刻全部为4k)的可配置的集合向量的子tlb。此外,虽然这三个存储器页尺寸被示出为4k、2m和1g,但是应当理解,可采用任何合适的页尺寸(其中的一些可具有对应的固定的子tlb,并且其中的一些或全部也可以是可存储在可配置的子tlb中的)。在图12的示例中,固定的集合相联的子tlb 320、322和324由可配置的全相联的子tlb 326互补。在该示例中的固定的集合相联的子tlb 320、322和324支持与存储器的以一个特定的页尺寸(例如,4k、2m或1g)对应的tlb条目。可配置的全相联的(fa)子tlb 326可支持与存储器的若干特定的页尺寸(例如,4k、2m和1g)对应的tlb条目,但是会涉及比固定的集合相联的子tlb320、322和324更多的开销。换言之,可配置的全相联的(fa)子tlb 326可支持至少部分地与由固定的集合相联的子tlb 320(4k 2m 1g相对于4k)、固定的集合相联的子tlb 322(4k 2m 1g相对于2m)和固定的集合相联的子tlb 324(4k 2m 1g相对于1g)支持的相应的页尺寸集不同的页尺寸集。

130.还可使用其他组合。例如,图13图示示例tlb 86,该示例tlb 86包括可配置的全相联的子tlb 326和固定的集合相联的子tlb 320和322。图14图示示例tlb 86,该示例tlb 86包括可配置的全相联的子tlb 326和固定的集合相联的子tlb 322和324。图15图示示例tlb 86,该示例tlb 86包括可配置的全相联的子tlb 326和固定的集合相联的子tlb 320和324。其他示例仍可包括更多或更少的子tlb,其由可配置的全相联的子tlb 326互补。

131.在继续之前,要注意由固定的集合相联的子tlb 320、322和324以及可配置的全相联的子tlb 326支持的条目的数量可有所不同。例如,子tlb 320可保存比子tlb 322更多的条目,并且子tlb 322可保存比子tlb 324更多的条目。由于可配置的全相联的子tlb 326可涉及更多开销(例如,由于其tlb条目或在操作它时所涉及的控制电路的尺寸可能占据更多管芯空间),因此在一些情况下,可配置的全相联的子tlb 326可保存比固定的集合相联的子tlb 320、322或324更少的条目。在其中可配置的全相联的子tlb 326取代固定的集合相联的子tlb 320、322或324的示例中,可配置的全相联的子tlb326可具有与那个固定的集合相联的子tlb 320、322或324对应的尺寸。例如,可配置的全相联的子tlb 326当取代固定的集合相联的子tlb 320时可以比当取代集合相联的子tlb 324时更大。此外,这些示例描述了tlb 86,其中,固定的集合相联的子tlb 320保持与4k存储器页尺寸对应的tlb条目,固定的集合相联的子tlb 322保存与2m存储器页尺寸对应的tlb条目,固定的集合相联的子tlb 324保存与1g存储器页尺寸对应的tlb条目,并且可配置的全相联的子tlb条目326保存与4k、2m和1g存储器页尺寸对应的tlb条目。然而,应当理解,可使用任何合适的存储器页尺寸、任何合适数量的存储器页尺寸,并且任何合适的页尺寸集合可分别由不同的子tlb支持。例如,可存在超出子tlb 320、322或324的附加或不同的固定的集合相联的子tlb。此外,全相联的tlb 326可保存针对不由任何其他固定的集合相联的子tlb保存的页尺寸的tlb条目。在一个示例中,可配置的全相联的子tlb 326可保存针对4kib、2mib、1gib和512gib页尺寸的tlb条目。

132.下文的示例将描述tlb 86,该tlb 86包括可配置的全相联的子tlb 326和固定的集合相联的子tlb 320和322(其中,可配置的全相联的子tlb 326取代固定的集合相联的子tlb 324)。然而,应当理解,本公开的系统和方法不限于该示例,并且可与任何合适的布置一起使用。在图16中示出的tlb 86中,固定的集合相联的子tlb 320保存4k tlb条目340,固定的集合相联的子tlb 322保存2m tlb条目342,并且可配置的全相联的子tlb 326保存4k tlb条目340、2m tlb条目342和1g tlb条目346。tlb控制电路348可包括控制tlb 86的操作的任何合适的电路,诸如,(多个)合适的状态机。虽然tlb控制电路348在逻辑上示出在tlb 86上的一个位置中,但是它可跨各子tlb 320、322和326分布。

133.新tlb条目后续将被存储在tlb 86中。为了这样做,现有的tlb条目被选择,该现有的tlb条目将被“驱逐”或“替换”以为新tlb条目腾出空间。在常规tlb中,仅有的替换候选来自与所指示的页尺寸相关联的固定的子tlb。为了获得来自可配置的全相联的子tlb的效率,新tlb条目可被选择以替换来自对应的固定的集合相联的子tlb或可配置的全相联的子tlb的tlb条目。一个示例由图17的流程图360示出。可接收tlb请求(框362)。如果存在与tlb请求对应的tlb条目(“tlb命中”)(决策框363),则tlb可基于所存储的tlb条目来作出响应(框364)。如果不存在与tlb请求对应的tlb条目(“tlb未命中”)(决策框363),则tlb可从适当的页表检取对应的tlb条目(框366)。tlb可使用任何合适的准则来选择在哪个子tlb中用于存储新tlb条目(决策368)。将在下文进一步讨论进一步的示例。

134.当与tlb请求的存储器页尺寸对应的固定的集合相联的(sa)子tlb被选择时,新tlb条目可以基于该固定的集合相联的子tlb的策略来替换该固定的集合相联的子tlb上的现有条目。例如,新tlb条目可按照近期最少使用(lru)或伪近期最少使用(plru)方案来替换现有tlb条目。当可配置的全相联的(fa)子tlb被选择时,新tlb条目可基于该可配置的全相联的子tlb的策略来替换现有条目(框372)。在下文还将进一步讨论这些策略的若干示例。

135.例如,如图18中所示,固定的集合相联的子tlb 320保存4k tlb条目340,固定的集合相联的子tlb 322保存2m tlb条目342,并且可配置的全相联的子tlb 326保存4k tlb条目340、2m tlb条目342和1g tlb条目346。tlb控制电路348可选择将新tlb条目308(此处示出为4k tlb条目)存储在子tlb 320或可配置的全相联的(fa)子tlb 326中。如果子tlb 320被选择,则新tlb条目308可替换现有的4k tlb条目340。如果可配置的全相联的子tlb 320被选择,则新tlb条目308可替换具有相同或不同的页尺寸的现有tlb条目。

136.固定的子tlb或可配置的子tlb的选择

137.可存在许多方式来选择将新tlb条目存储在对应的固定的子tlb中还是存储在可配置的子tlb中。这些可被单独地或组合地使用。图19图示在其中各种子tlb的未命中率被跟踪并在决策中被考虑的一个示例。在此,“未命中率”一般是指近期未命中的比率——在某个阈值时间量之前(例如,数分钟或数小时)发生的未命中可被忽略。在图19中示出的tlb 86中,固定的集合相联的子tlb 320保存4k tlb条目340,固定的集合相联的子tlb 322保存2m tlb条目342,并且可配置的全相联的子tlb 326保存4k tlb条目340、2m tlb条目342和1g tlb条目346。tlb 86可跟踪表示子tlb 320的近期未命中率的4k未命中率380、以及表示子tlb 322的近期未命中率的2m未命中率382。附加地或替代地,tlb 86还可跟踪表示可配置的全相联的(fa)子tlb 326的近期未命中率的fa未命中率384。在一个示例中,未命中率

382、384和386可表示指数移动平均(ema)。在一些情况下,未命中率382、384或386可替代地对指数移动平均进行近似,这可以需要承担较低的硬件成本。

138.通过跟踪子tlb的未命中率,全相联的tlb可被预留用于具有当前正在经历最高需求的页尺寸(例如,4k或2m)的tlb条目。图20和图21表示用于决定将新tlb条目存储到哪个子tlb中的决策368(在图17中图示)对应的示例流程图。在图20中,决策368可涉及:跟踪固定的集合相联的子tlb的未命中率(框402)。如果新tlb条目不与当前正在经历最高未命中率的子tlb的页尺寸对应(决策404),则可选择与新tlb的页尺寸相关联的固定的集合相联的子tlb(框406)。这有效地减少了对可配置的全相联的子tlb的竞争。也就是说,如果新tlb条目与当前正在经历最高未命中率的子tlb的页尺寸对应(决策404),则可选择可配置的全相联的子tlb或与新tlb的页尺寸相关联的固定的集合相联的子tlb(框408)。

139.在一些情况下,可考虑可配置的全相联的子tlb的未命中率。例如,如图21中所示,决策368可涉及:跟踪固定的集合相联的子tlb和可配置的全相联的子tlb的未命中率(框422)。当可配置的全相联的子tlb具有最大未命中率(决策424)时,可选择可配置的全相联的子tlb或与新tlb的页尺寸相关联的固定的集合相联的子tlb(框426)。否则,如果新tlb条目不与当前正在经历最高未命中率的子tlb的页尺寸对应(决策428),则可选择与新tlb的页尺寸相关联的固定的集合相联的子tlb(框430)。如果新tlb条目与当前正在经历最高未命中率的子tlb的页尺寸对应(决策428),则可选择可配置的全相联的子tlb或与新tlb的页尺寸相关联的固定的集合相联的子tlb(框432)。

140.附加地或替代地,tlb可取决于在对应的固定的集合相联的tlb与可配置的全相联的tlb之间的条目的可用性比率来选择将新tlb条目存储在固定的集合相联的子tlb中还是存储在可配置的全相联的子tlb中。图22的流程图可表示决策368和/或框408、426或432的操作。可确定对应的固定的集合相联的tlb与可配置的全相联的tlb之间的可用条目的比率(框440),并且可基于比率被随机地或伪随机地选择特定的子tlb(对应的固定的集合相联的子tlb或可配置的全相联的子tlb)(框442)。这可被称为“抛硬币”方式。

141.图23提供示例。在此,在tlb 86中,4k子tlb可保存64个4k tlb条目340,子tlb 322可保存32个2m tlb条目342,并且可配置的全相联的子tlb 326可保存总共8个的以下各项:4k tlb条目340、2m tlb条目342、以及1g tlb条目346。因此,当决定在何处存储具有4k页尺寸的新tlb条目308时,对于该示例,该新tlb条目308可按以下比例被伪随机地指派给子tlb 320或可配置的全相联的子tlb 326:64/(64 8)指派给子tlb 320,并且8/(64 8)指派给可配置的全相联的子tlb 326。

142.附加地或替代地,向可配置的全相联的子tlb 326的分配可小于100%。在一个示例中,可用条目在可配置的全相联的子tlb 326中的分配可在固定的集合相联的子tlb 320与322之间划分(例如,50%分配给4k,并且50%分配给2m)。在另一示例中,如下文进一步所讨论,全相联的tlb 326的一些tlb条目可被标记为针对另一页尺寸是“粘性”的且因此不可用。划分对可配置的全相联的子tlb 326的tlb条目的指派可产生不同结果。例如,如果可配置的全相联的子tlb 326的tlb条目被划分为50%给4k尺寸且50%给2m尺寸,则用于指派具有4k尺寸的新tlb条目的比例可以是64/(64 4)给子tlb320且4/(64 4)给可配置的全相联的子tlb 326。

143.用于可配置的子tlb和“粘性”条目的替换策略

144.还可存在许多方式来替换可配置的子tlb中的条目,并且这些方式也可被单独地或组合地使用。在一个示例中,如由图24的流程图460所示,可监测新tlb条目被添加到可配置的全相联的子tlb所按照的顺序(框464)。可基于该顺序、使用近期最少使用(lru)或伪近期最少使用(plru)用新tlb条目来替换可配置的全相联的子tlb中的现有tlb条目。

145.另一示例涉及:将可配置的全相联的子tlb的某些tlb条目或条目位置指定为“粘性”,或指定为被预留用于仅具有特定的一个或多个页尺寸的tlb条目。由此,“粘性”tlb条目可仅由具有相同的一个或多个“粘性”页尺寸的新tlb条目替换。例如,当可配置的全相联的子tlb取代2m固定的集合相联的子tlb和1g固定的集合相联的子tlb时,可能期望防止由4k条目支配2m和1g tlb条目。在该示例中,将1g和2m tlb条目标记为“粘性”可防止4k条目(“非粘性”页尺寸)驱逐2m tlb条目或1g tlb条目。在另一示例中,当可配置的全相联的子tlb取代1g固定的集合相联的子tlb时,1g页尺寸可被视为“粘性”,并且2m和4k页尺寸可被视为“非粘性”。在该示例中,将1g tlb条目标记为“粘性”可防止1g tlb条目被2m或4kb tlb条目驱逐。附加地或替代地,将tlb条目或条目位置标记为“粘性”可防止tlb条目被无论具有什么页尺寸的新tlb条目驱逐。

146.图25图示tlb 86的示例,其中,tlb控制电路348可设置一个或多个“粘性”位470,以预留用于具有特定的页尺寸的tlb条目的特定的子tlb条目或条目位置。在图25的示例中,固定的集合相联的子tlb 320保存4k tlb条目340,固定的集合相联的子tlb 322保存2m tlb条目342,并且可配置的全相联的子tlb 326保存4k tlb条目340、2m tlb条目342和1g tlb条目346。在该示例中,由于1g tlb条目346不具有为它们指定的单独的固定的集合相联的子tlb,因此可使用一个或多个粘性位470来预留用于1g tlb条目346的可配置的全相联的子tlb 326的子tlb条目。在其他示例中,可使用一个或多个粘性位470来预留可配置的全相联的子tlb 326的子tlb条目,以用于与一个或多个其他页尺寸相关联的任何条目。例如,当可配置的全相联的子tlb 326取代不同的固定的集合相联的子tlb 320或322时(例如,如在图14或图15中),与那个页尺寸相关联的条目可通过一个或多个粘性位470被预留。在另一示例中,由一个或多个粘性位470预留的一个或多个页尺寸可以是尤其被需要的某个或某些页尺寸(例如,由未命中率来衡量,或由基于来自操作系统的指令而被编程的寄存器来指示)。

147.一个或多个粘性位470能以各种方式来实现和使用。在一个示例中,一个或多个粘性位470可与每个tlb条目相关联,但是仅在某些条件下被设置(例如,当1g tlb被存储在特定的tlb条目位置中时)。在另一示例中,可存在仅一个全局粘性位。一旦特定的页尺寸(例如,1g)已在任何tlb条目中被使用,该全局粘性位就可使tlb不使具有不同页尺寸(例如,4k或2m)的tlb条目驱逐具有该特定页尺寸(例如,1g)的tlb条目。在另一示例中,针对每个页尺寸可存在一个粘性位。例如,如果4k页是高未命中“问题”且2m页不是该问题,则粘性位可防止2m页绝不驱逐2m页,但是可允许4k页驱逐2m页。

148.在一些情况下,如由图26的流程图480所述,当具有特定的页尺寸集的新tlb条目308被存储到可配置的全相联的子tlb中时(框482),它可被标记为“粘性”,使得它将不由具有“非粘性”页尺寸集的tlb条目替换(例如,在“粘性”页尺寸集仅是1g的情况下,被标记为粘性的1g tlb条目可仅由1g tlb条目替换,而不由4k或2m tlb条目替换;在“粘性”页尺寸集仅是2m和1g的情况下,被标记为粘性的2m或1g tlb可仅由2m或1g tlb条目替换,而不由

4k tlb条目替换)(框484)。在由图27的流程图490示出的另一示例中,但具有特定页尺寸的新tlb条目308被存储到可配置的全相联的子tlb 326中时,它还不可被标记为“粘性”(框492)。此后,响应于针对该tlb条目的tlb命中,该tlb条目可被标记为“粘性”(框494),使得它将不被具有“非粘性”页尺寸集的tlb条目替换(框496)。

149.可基于与tlb的特定度量的使用有关的计数(例如,使用的直接计数、每许多次使用被递增的技术、与特定的使用的数量有关的某个其他代理指示)将可配置的全相联的子tlb的某些tlb条目标记为“粘性”。图28图示tlb 86的示例,其中,tlb控制电路348可使用计数器500,该计数器500与可配置的全相联的子tlb 326的tlb条目位置相关联。一个或多个“粘性”位可被设置,以基于计数器500在某个时间段内达到阈值来预留用于具有特定页尺寸的tlb条目的特定的子tlb条目位置。例如,如由图29的流程图510所示,可对每个全相联的子tlb条目位置被用于具有一个或多个特定的尺寸(例如,4k、2m、1g、2m或1g、4k或2m、4k或1g)的tlb条目的次数进行计数(框512)。这可被视为可对具有感兴趣的单个页尺寸或若干页尺寸的tlb条目计数的“根据使用”计数器。例如,当可配置的全相联的子tlb取代1g固定的集合相联的子tlb时,可对1g tlb条目被存储的次数进行计数(例如,逐条目地或全局地)。在另一示例中,当可配置的全相联的子tlb取代2m固定的集合相联的子tlb和1g固定的集合相联的子tlb时,可期望防止2m和1g tlb条目由4k条目支配,因此可对1g tlb条目或2m tlb条目被存储的次数计数(例如,逐条目地或全局地)。响应于计数器达到特定的阈值数量——例如,当可配置的全相联的子tlb的tlb条目位置被用于存储具有那一个或多个页尺寸的tlb条目某个次数时——那个子tlb条目位置可针对那一个或多个页尺寸被标记为“粘性”(框514)。此后,被标记为“粘性”的条目位置中的tlb条目将不由具有“非粘性”页尺寸的tlb条目替换(框516)。例如,当可配置的全相联的子tlb取代2m固定的集合相联的子tlb和1g固定的集合相联的子tlb时,可能期望防止由4k条目支配2m tlb条目和1g tlb条目,因此这一个或多个粘性位可防止4k条目驱逐2m tlb条目或1g tlb条目。

150.在一些情况下,一个或多个“粘性”位以及“计数器”可被统一,例如,保存值0..7的3位的计数器,并且其中0..6指示非粘性且计数进行中,而7指示粘性。

151.虽然这些示例已描述了逐条目的粘性,但是一个或多个粘性位可定义贯穿可配置的全相联的子tlb的粘性。例如,可存在用于可配置的全相联的子tlb的一个或多个全局“粘性”位,这一个或多个全局“粘性”位可定义具有特定页尺寸的任何条目是否可被驱逐。例如,设置全局“粘性”位可使可配置的全相联的子tlb的所有1g tlb条目不能够被4k或2m tlb条目驱逐。在另一示例中,设置全局“粘性”位可使所有2m和1g tlb条目不能够被4k tlb条目驱逐。

152.在一些情况下,是否将可配置的全相联的子tlb的tlb条目标记为“粘性”可基于可配置的全相联的子tlb的总使用的计数来确定。图30提供tlb 86的示例,其中,tlb控制电路348可使用计数器520来维护对具有特定页尺寸的可配置的全相联的子tlb 326的所有访问的近期(例如,在几秒内,在几分钟内,在几小时内)计数。在一些情况下,由计数器520作出的计数可包括针对所有页尺寸对可配置的全相联的子tlb 326的所有访问。在其他情况下,由计数器520作出的计数可包括针对仅某个或某些页尺寸(例如,将被标记为“粘性”的一个或多个页尺寸,诸如,1g、2m或4k)对可配置的全相联的子tlb326的所有访问。例如,如果tlb具有4k固定的集合相联的子tlb以及2m 1g全相联的子tlb,则2m tlb条目和1g tlb条目可“竞争”空间——也就是说,2m tlb条目和1g tlb条目可彼此替换。在该示例中,1g tlb条目能够替换“粘性”2m tlb条目,但是4k tlb条目不能够替换“粘性”2m tlb条目。

153.计数器520能以各种方式实现。在一个示例中,计数器520可表示用于对该示例中的具有除1g之外的所有尺寸的tlb条目计数的一个计数器,由于没有用于放置1g映射的地方,因此可能期望朝向相对于非1g偏好1g来“偏置”。在另一示例中,针对每个页尺寸可存在一个计数器。在某种程度上,这近似于针对每个条目一个计数器,但基于页尺寸来概况。这对一个计数器作出了改进,因为tlb可针对不成问题的无论什么尺寸早“放弃”,并且保持尝试成问题的无论什么尺寸。

154.如由图31的流程图530所提供,可维护可配置的全相联的子tlb被用于一个或多个特定页尺寸的次数的计数(框532),并且响应于达到那一个或多个页尺寸的近期使用的阈值数量,可将当前与那一个或多个尺寸相关联的所有tlb条目标记为“粘性”(框534)。被标记为“粘性”的条目将不被具有“非粘性”页尺寸的tlb条目替换(框536)。

155.在一些情况下,是否将可配置的全相联的子tlb的tlb条目标记为“粘性”可基于tlb的总使用的计数或某个数量的时钟周期的计数来确定。例如,如在图32中所示,tlb 86的tlb控制电路348可使用计数器540来维护对tlb86的所有访问的近期(例如,在几秒内,在几分钟内,在几小时内)计数。在一些示例中,计数器540可对自从一个或多个粘性位470的重置起已经经过的某个数量的时钟周期进行计数。在一些情况下,由计数器540作出的计数可包括对除可配置的全相联的子tlb 326之外的子tlb 320和322的所有访问。图33中示出的流程图550提供使用诸如计数器540之类的计数器来标记“粘性”tlb条目的方法。tlb可对tlb近期被访问的次数计数,或可对时钟周期计数(框552)。响应于达到近期访问的阈值数量,可将当前与所选择的页尺寸(例如,1g)相关联的所有tlb条目标记为“粘性”(框554)。被标记为“粘性”的条目后续将不被具有“非粘性”页尺寸的tlb条目替换(框556)。

156.重置“粘性”位

157.虽然“粘性”位的使用可防止具有某些页尺寸(例如,1g)的条目随着时间推移被具有其他页尺寸(4k或2m)的条目支配,但是粘性条目的数量可以占主导。相应地,可时不时地重置粘性位。例如,如由图34中示出的流程图560所指示,响应于由集成电路作出的上下文切换(框562),可重置所有粘性条目或粘性条目中的一些(框564)。上下文切换可由tlb以任何合适的方式来检测。例如,tlb可通过从集成电路的其他电路接收指令,通过检查tlb中的寄存器的设置的变化,或通过检查某个阈值数量的连续的tlb未命中已发生来检测上下文切换。

158.在图35的流程图570中示出的另一示例中,响应于执行对当天被标记为“粘性”的tlb条目的显式无效(框572),可重置所有粘性条目或粘性条目中的一些(框574)。如在图36的流程图580中所示,可周期性地重置“粘性”位。例如,定时器可被设置,或计数器可对时钟周期计数(框582)。响应于定时器期满或计数器达到时钟周期的阈值数量,可重置所有粘性条目或粘性条目中的一些(框584)。

159.附加地或替代地,可使用“第二次机会”方案。“第二次机会”方案可在特定的“粘性”tlb条目尝试被重置某个阈值次数之后重置粘性位。例如,如在图37的流程图590中所示,当确定是否替换可配置的全相联的子tlb的特定tlb条目时,被标记为“粘性”的条目可被包括。如果被标记为“粘性”的tlb条目被选择(例如,通过近期最少使用(lru)或伪近期最

少使用(plru)或另一驱逐算法)(框592),然而,那个条目可不被驱逐。相反,一个或多个“粘性”位可被递减或清除(框594)。在一个示例中,在“粘性”tlb条目第一次被选择用于驱逐时,一个或多个“粘性”位可被清除,但是该tlb条目可不被驱逐,并且替代地,不同的tlb条目可被驱逐。在其他示例中,一个或多个“粘性”位可指示一些tlb条目可被标记为比其他tlb条目“更具粘性”的计数。在选择用于驱逐之际,“粘性”位可被递减,并且仅在某个阈值数量的递减之后被清除。

160.全相联的子tlb条目的数据结构

161.可配置的全相联的子tlb的tlb条目可采用任何合适的数据结构。一个示例出现在图38中,其对比了用于1g子tlb的tlb条目结构600的示例以及用于可配置的全相联的tlb的tlb条目结构602。这两者都包括有效位604、权限位(rwx u/s)606、地址空间标识符(asid)607、以及物理属性表(pat)610。然而,用于1g子tlb的tlb数据结构600可具有较小的虚拟存储器地址标签(vtag)613和较小的物理存储器地址标签(ptag)614。这是因为用于可配置的全相联的子tlb的tlb条目结构604尺寸可设定为容纳较小的页尺寸。较小的页尺寸在页内具有较小的偏移。利用较小的页,虚拟地址提供较少的地址位,并且物理标签因此供应较多的地址位。因此,用于可配置的全相联的子tlb的tlb条目结构602可具有足够大以容纳例如4k页尺寸的虚拟存储器地址标签(vtag)616和物理存储器地址标签(ptag)617。当被用于其他页尺寸(例如,2m或1g)时,附加的未使用的位可被忽略。

162.tlb条目结构602还可包括尺寸状态字段(sz)620,其可表示tlb条目的页尺寸。例如,当两个页尺寸在可配置的全相联的子tlb中被使用时,该字段可以是1位宽。当tlb条目结构602容纳三个页尺寸(例如,4k、2m、1g)中的任一页尺寸时,该字段可以是2位或更多位宽。该尺寸还可经由某个其他机制来指示。作为示例,考虑具有指示符[0..16]的16条目的fa子tlb,其表明低于该指示符的每个事物都是1g;并且处于或高于该指示符的每个事物都是2m。在该示例中,填充1g映射将递增该指示符,并将条目置于“新”位置处;而填充2m映射将从处于或高于该指示符处的条目选择。

[0163]

如上文所述,tlb条目结构602还可包括粘性字段622。粘性字段622可以是单个位(即,“粘性”或“非粘性”),或者可占据多于一个位以提供不同程度的“粘性”(例如,其可在“第二次机会”重置技术中被使用,其可定义条目位置是粘性的还是恰是当前被存储的tlb条目,或者其可在tlb命中之际被递增并在tlb未命中之际被递减)。tlb条目结构602还可具有未在图38中示出的其他字段。例如,可存在能够按照图28中的计数器500的方式被更新的计数器字段。在一些情况下,“粘性”字段和“计数器”字段可以是统一的。例如,3位的计数器可保存值0..7,其中,0..6指示非粘性且计数进行中,而7指示粘性。

[0164]

实验结果

[0165]

利用工作负载踪迹的集合测试了上述方式。测试开始于标准踪迹库,并且涉及选择那些踪迹,那些踪迹在周期准确的模拟中使用与某些当前可用的处理器类似的基线tlb配置来花费等待tlb未命中的挂钟时间的10%或更多。功能(计数,但非周期准确的)模拟器被修改用于实现所公开的设计的一个办呢。值得注意的是,1gib子tlb被修改位接受所有页尺寸。模拟器实现简单的伪随机选择和针对fa中的1g页的简单的“粘性”实现方式。(例如,没有未命中率跟踪、没有复杂的“粘性”老化)。考虑三个版本的所公开的方法:(a)fa阵列中的4kib和1gib页映射;(b)fa阵列中的2mib和1gib页映射;以及(c)fa阵列中的全部三个页

尺寸。

[0166]

功能模拟器没有时间概念,因此使用度量mpki或“每千条指令未命中”来评估该方式。mpki变化不直接转换为性能变化——对于任何给定的工作负载,mpki变化的尺寸可比性能变化的尺寸更大或更小。然而,mpki改善典型地与性能改善相关联。

[0167]

对于上述配置和工作负载,我们看到:

[0168]

·

对于上述配置:(a)接受4kib和1gib的fa条目具有约8%几何平均mpki改善;(b)2mib和1gib具有约2.5%几何平均mpki改善;并且(c)4kib、2mib和1gib一起具有约10%几何平均mpki改善。

[0169]

·

在每个配置中存在显示出接近30%的mpki降低的特定工作负载。2m fa几何平均改善中的大多数改善是由于一些大的改善,并且大多数工作负载没有改善。

[0170]

·

不存在对于配置中的任何配置在其中mpki变得更糟(总体上,或对于任何子tlb)的情况。

[0171]

关于第一级数据tlb描述了上文,但是其他tlb可使用类似的方式。这些还可包括完全由固定的集合相联的子tlb(无全相联的子tlb)建立的tlb以及包括一个或多个可配置的集合相联的子tlb的tlb。

[0172]

示例实施例

[0173]

示例实施例1:一种集成电路,包括转换后备缓冲器(tlb),所述tlb包括:

[0174]

第一固定的子tlb,所述第一固定的子tlb在运行时期间存储与第一页尺寸集对应的第一多个tlb条目;以及

[0175]

可配置的子tlb,所述可配置的子tlb在运行时期间可配置成用于存储具有第二页尺寸集的第二多个tlb条目,所述第二页尺寸集包括所述第一页尺寸集的至少第一页尺寸并包括不是所述第一页尺寸集的至少第二页尺寸。

[0176]

示例实施例2:如示例实施例1的集成电路,其中,所述第一固定的子tlb包括固定的集合相联的子tlb。

[0177]

示例实施例3:如示例实施例1的集成电路,其中,所述可配置的子tlb包括可配置的集合相联的子tlb。

[0178]

示例实施例4:如示例实施例1的集成电路,其中,所述可配置的子tlb包括可配置的全相联的子tlb。

[0179]

示例实施例5:如示例实施例1的集成电路,其中,所述第一页尺寸集的所述第一页尺寸包括4kib页尺寸,并且所述第二页尺寸集的所述第二页尺寸包括1gib页尺寸。

[0180]

示例实施例6:如示例实施例5的集成电路,其中,所述第二页尺寸集包括第三页尺寸,其中,所述第三页尺寸包括2mib页尺寸,并且其中,所述第一页尺寸集不包括所述1gib页尺寸且不包括所述2mib页尺寸。

[0181]

示例实施例7:如示例实施例1的集成电路,其中,所述第二页尺寸集包括不由所述tlb的任何其他子tlb支持的至少一个页尺寸。

[0182]

示例实施例8:如示例实施例1的集成电路,其中,所述第一固定的子tlb比所述可配置的子tlb保存更多的tlb条目。

[0183]

示例实施例9:如示例实施例1的集成电路,其中,所述tlb包括控制电路,所述控制电路至少部分地基于所述第一固定的子tlb和所述可配置的子tlb中的可用条目的比率来

选择将与所述第一页尺寸集对应的新tlb条目存储在所述第一固定的子tlb中还是存储在所述可配置的子tlb中。

[0184]

示例实施例10:如示例实施例1的集成电路,其中:

[0185]

所述固定的子tlb包括第一固定的集合相联的子tlb,所述第一固定的集合相联的子tlb在运行时期间被配置成用于存储与所述第一页尺寸集对应的所述第一多个tlb条目;

[0186]

所述第一页尺寸集仅包括第一页尺寸;

[0187]

所述tlb包括第二固定的集合相联的子tlb,所述第二固定的集合相联的子tlb在运行时期间被配置成用于存储与第三页尺寸集对应的第三多个tlb条目;并且

[0188]

所述第三页尺寸集仅包括第三页尺寸。

[0189]

示例实施例11:如示例实施例10的集成电路,其中,所述第二页尺寸集包括所述第三页尺寸。

[0190]

示例实施例12:如示例实施例11的集成电路,其中,所述第一页尺寸集包括4kib的页尺寸,所述第二页尺寸集包括1gib的页尺寸,并且所述第三页尺寸集包括2mib的页尺寸。

[0191]

示例实施例13:如示例实施例11的集成电路,其中,所述tlb包括控制电路,所述控制电路监测所述第一集合相联的tlb的第一未命中率以及所述第二集合相联的tlb的第二未命中率,并且其中,所述控制电路配置成用于:至少部分地基于所述第一未命中率是否高于所述第二未命中率,选择将与所述第一页尺寸对应的新tlb条目存储在所述第一固定的集合相联的子tlb中还是存储在所述可配置的子tlb中。

[0192]

示例实施例14:如示例实施例13的集成电路,其中,所述tlb包括控制电路,所述控制电路监测所述可配置的子tlb的第三未命中率,并且其中,所述控制电路配置成用于:至少部分地基于所述第三未命中率是否高于所述第一未命中率和所述第二未命中率,选择将与所述第一页尺寸集对应的所述新tlb条目存储在所述第一固定的集合相联的子tlb中还是存储在所述可配置的子tlb中。

[0193]

示例实施例15:如示例实施例1的集成电路,其中,所述集成电路包括处理器,并且其中,所述tlb操作为用于所述处理器的指令tlb。

[0194]

示例实施例16:如示例实施例1的集成电路,其中,所述集成电路包括存储器访问电路,并且其中,所述tlb操作为用于所述存储器访问电路的数据tlb。

[0195]

示例实施例17:一种方法,包括:

[0196]

在转换后备缓冲器(tlb)处接收导致tlb未命中的tlb请求;

[0197]

从页表检取与所述tlb请求对应的新tlb条目;以及

[0198]

在以下两个步骤之间选择:

[0199]

利用所述新tlb条目替换来自所述tlb的第一固定的子tlb的第一旧tlb条目;以及

[0200]

利用所述新tlb条目替换来自所述tlb的可配置的子tlb的第二旧tlb条目。

[0201]

示例实施例18:如示例实施例17的方法,其中,所述选择至少部分地基于所述第一固定的子tlb和所述可配置的子tlb中的可用条目的比率。

[0202]

示例实施例19:如示例实施例18的方法,其中,所述可配置的子tlb中的条目如果被标记为“粘性”则不被视为可用,并因此被预留用于与所述新tlb条目不同的页尺寸。

[0203]

示例实施例20:一种方法,包括:

[0204]

在转换后备缓冲器(tlb)处接收tlb请求,所述tlb包括与第一页尺寸集对应的第

一固定的子tlb以及与所述第一页尺寸集和第二页尺寸集对应的可配置的子tlb,所述tlb请求与导致tlb未命中的所述第二页尺寸集对应;

[0205]

从页表检取与所述tlb请求对应的新tlb条目;

[0206]

利用所述新tlb条目替换来自所述可配置的子tlb的旧tlb条目;以及

[0207]

将所述可配置的子tlb中的所述新tlb条目标识为“粘性”,使得所述新tlb条目不被驱逐从而被不与所述第二页尺寸集对应的另一tlb条目替换。

[0208]

示例实施例21:如示例实施例20的方法,其中,所述新tlb条目响应于被存储在所述可配置的子tlb中且与所述第二页尺寸集对应而被标识为“粘性”。

[0209]

示例实施例22:如示例实施例20的方法,包括:在将所述可配置的子tlb中的所述新tlb条目标识为“粘性”之前,在所述tlb处接收与导致tlb命中的所述新tlb条目对应的tlb请求,其中,所述新tlb条目响应于针对所述新tlb条目的所述tlb命中而被标识为“粘性”。

[0210]

示例实施例23:示例实施例20的方法,包括:

[0211]

维护与对应于所述新tlb条目的所述可配置的子tlb的条目位置被用于存储具有所述第二页尺寸集的tlb条目的次数有关的计数,其中,所述新tlb条目响应于所述计数超出阈值数量而被标识为“粘性”。

[0212]

示例实施例24:示例实施例20的方法,包括:

[0213]

维护与所述可配置的子tlb的条目位置被用于存储具有所述第二页尺寸集的tlb条目的次数有关的计数,其中,所述新tlb条目响应于所述计数超出阈值数量而被标识为“粘性”。

[0214]

示例实施例25:示例实施例20的方法,包括:维持与由所述tlb接收的tlb请求有关的第一计数,或维持与时钟周期的数量有关的第二计数,其中,所述新tlb条目响应于所述第一计数超出第一阈值或所述第二计数超出第二阈值而被标识为“粘性”。

[0215]

示例实施例26:示例实施例20的方法,包括:

[0216]

检测上下文切换;以及

[0217]

响应于检测到所述上下文切换,停止将所述新tlb条目标识为“粘性”。

[0218]

示例实施例27:示例实施例20的方法,包括:

[0219]

执行对所述新tlb条目的显式无效;以及

[0220]

响应于执行对所述新tlb条目的所述无效,停止将所述新tlb条目标识为“粘性”。

[0221]

示例实施例28:示例实施例20的方法,包括:

[0222]

启动定时器或维护与时钟周期有关的计数;以及

[0223]

响应于所述定时器期满或所述计数超出阈值,停止将所述新tlb条目标识为“粘性”。

[0224]

示例实施例29:示例实施例20的方法,包括:

[0225]

选择所述新tlb条目用于驱逐;

[0226]

不驱逐所述新tlb条目,停止将所述新tlb条目标识为“粘性”。

[0227]

示例实施例30:一种集成电路器件,包括转换后备缓冲器(tlb),所述tlb包括可配置的子tlb,所述可配置的子tlb存储第一条目,所述第一条目包括:

[0228]

虚拟存储器地址字段;

[0229]

物理存储器地址字段,与所述虚拟存储器地址字段对应;以及

[0230]

粘性字段,所述粘性字段至少部分地基于第二条目相对于所述第一条目的页尺寸来指示所述第一条目是否被准许由所述第二条目驱逐。

[0231]

示例实施例31:如示例实施例30的集成电路器件,其中,所述粘性位包括单个位。

[0232]

示例实施例32:如示例实施例31的集成电路器件,其中,所述粘性位包括多个位。

[0233]

示例实施例33:如示例实施例32的集成电路器件,其中,所述粘性字段指示所述第一条目被准许由与同由所述页尺寸字段指示的页尺寸不同的页尺寸相关联的第二条目驱逐的程度。

[0234]

示例实施例34:如示例实施例30所述的集成电路器件,其中,所述第一条目包括计数器字段,所述计数器字段配置成用于存储与所述第一条目被用于存储与特定页尺寸对应的虚拟存储器地址或物理存储器的次数有关的计数。

[0235]

示例实施例35:如示例实施例30的集成电路器件,其中,所述粘性字段包括存储计数的多个位,其中,所述计数的值指示“粘性”或“非粘性”。

[0236]

示例实施例36:如示例实施例30的集成电路器件,其中,搜索第一字段包括页尺寸字段,所述页尺寸字段指示与所述虚拟存储器地址字段和所述物理存储器地址字段相关联的页尺寸。

[0237]

尽管本公开中阐述的实施例易于具有各种修改和替代形式,但是,特定实施例已作为示例在附图中示出并已在本文中详细描述。然而,应当理解,本公开不旨在被限于所公开的特定形式。本公开将涵盖落入如由所附权利要求所限定的本公开的精神和范围内的所有修改、等效方案和替代方案。

[0238]

本文所提出和要求保护的技术被引用并应用于实际性质的实物和具体示例,这些实物和具体示例明显改善了当前技术领域,因此不是抽象的、无形的或纯理论的。进一步地,如果本说明书末尾所附的任何权利要求包含一个或多个被指定为“用于[执行][功能]的装置”或“用于[执行][功能]的步骤”的要素,则其旨在基于35u.s.c.112(f)来解释此类要素。然而,对于包含以任何其他方式指定的要素的任何权利要求,其旨在不基于35u.s.c.112(f)来解释此类要素。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。