包括有源电感器的运算跨导放大器电路

1.相关申请的交叉引用

2.本技术是基于并要求于2020年12月29日向韩国知识产权局提交的韩国专利申请no.10-2020-0186784和于2021年6月2日向韩国知识产权局提交的韩国专利申请no.10-2021-0071710的优先权,其全部内容通过引用结合于此。

技术领域

3.本发明构思涉及放大器电路,并且更具体地,涉及包括有源电感器的运算跨导放大器电路(operational transconductance amplifier circuit)。

背景技术:

4.双倍数据速率(double data rate,ddr)5对于数据发送和接收具有高数据速率,并且因此,确定运算跨导放大器的输出的电路径的长度彼此不同,导致占空比的失真。电感器可以包括在放大器中以减小失真,但是一般地,随着频率降低,需要具有高电感的电感器来将所有阻抗维持在恒定电平,并且当电感器的电感增加时,电感器占据大的面积,从而阻碍集成电路的小型化。因此,需要有效地使用包括电阻器和电容器的有源电感器。

技术实现要素:

5.本发明构思提供了具有增加的带宽和改进的占空比特性的运算跨导放大器电路。

6.根据一个实施例,一种运算跨导放大器可以包括:被配置为基于差分输入信号对来生成第一差分电流和第二差分电流的输入电路;被配置为基于第一差分电流来生成第一镜电流并且经由第一输出端子来输出第一镜电流的第一电流镜电路;以及被配置为基于第二差分电流来生成第二镜电流并且经由第三电流镜电路的第一节点来输出第二镜电流的第二电流镜电路。第二电流镜电路和第三电流镜电路通过第一节点彼此连接。第三电流镜电路被配置为基于第二镜电流来生成第三镜电流并且经由第一输出端子来输出第三镜电流。第一电流镜电路和第二电流镜电路可以分别包括每个都包括p沟道晶体管的第一有源电感器和第二有源电感器。第三电流镜电路可以包括第三有源电感器,该第三有源电感器包括n沟道晶体管。

7.根据另一个实施例,放大器电路可以包括第一单元电路和第二单元电路。第一单元电路可以包括第一电流镜电路和第一输入电路,该第一电流镜电路包括第一有源电感器,该第一有源电感器包括p沟道晶体管,该第一输入电路被配置为基于差分输入信号对来生成第一差分电流和第二差分电流。第二单元电路可以包括第二电流镜电路和第二输入电路,该第二电流镜电路包括第二有源电感器,该第二有源电感器包括p沟道晶体管,该第二输入电路被配置为基于差分输入信号对来生成第三差分电流和第四差分电流。

8.根据另一个实施例,一种存储器设备可以包括:包括多个存储器块,并且被配置为通过使用内部电源电压来对多个存储器单元执行写入操作和读取操作的存储器单元阵列,每个存储器块包括连接到以行和列布置的字线和位线的多个存储器单元;以及被配置为接

收具有时钟信号和反相时钟信号的差分输入信号对并且校正时钟信号的占空比的时钟缓冲器;其中,时钟缓冲器可以包括:被配置为基于时钟信号和反相时钟信号来生成第一差分电流和第二差分电流的输入电路;包括第一有源电感器并且被配置为基于第一差分电流来生成第一镜电流和第二镜电流的第一电流镜电路,该第一有源电感器包括p沟道晶体管;包括第二有源电感器并且被配置为基于第二差分电流来生成第三镜电流和第四镜电流的第二电流镜电路,该第二有源电感器包括p沟道晶体管;包括第三有源电感器并且被配置为基于第三镜电流来生成第五镜电流的第三电流镜电路,该第三有源电感器包括n沟道晶体管;以及包括第四有源电感器并且被配置为基于第二镜电流来生成第六镜电流的第四电流镜电路,该第四有源电感器包括n沟道晶体管。

附图说明

9.根据以下结合附图的详细描述,将更清楚地理解本发明构思的实施例,其中:

10.图1a示出了包括根据本发明构思的示例实施例的存储器设备的系统;

11.图1b示出了根据本发明构思的示例实施例的存储器设备;

12.图2示出了根据比较示例的运算跨导放大器;

13.图3a示出了根据示例实施例的nmos有源电感器;

14.图3b示出了根据示例实施例的pmos有源电感器;

15.图3c示出了根据示例实施例的包括有源电感器的晶体管的小信号等效电路;

16.图3d示出了根据本发明构思的示例实施例的频率和输入阻抗的图;

17.图4示出了根据本发明构思的示例实施例的包括有源电感器的运算跨导放大器;

18.图5示出了根据本发明构思的示例实施例的上电流和下电流的电路径;

19.图6a是示出了根据比较示例的占空比的失真的图;

20.图6b是示出了根据示例实施例的基于nmos有源电感器的占空比的失真减小的图;

21.图6c是示出了根据示例实施例的基于pmos有源电感器的占空比的失真减小的图;

22.图6d是示出了根据本发明构思的示例实施例的基于nmos有源电感器和pmos有源电感器的占空比的失真减小的图;

23.图7a是示出了当仅包括pmos有源电感器时的占空比的失真的图;

24.图7b是示出了根据本发明构思的示例实施例的当包括nmos有源电感器和pmos有源电感器两者时的占空比的失真的图;

25.图8示出了根据本发明构思的示例实施例的包括nmos有源电感器和pmos有源电感器的放大器电路;

26.图9是示出了根据本发明构思的示例实施例的频率和增益的图;以及

27.图10是示出了根据本发明构思的示例实施例的转换速率(slew rate)的改进的图。

具体实施方式

28.在下文中,将参考附图详细描述本发明构思的示例实施例。

29.图1a示出了根据本发明构思的示例实施例的包括存储器设备的系统。

30.参考图1a,系统10可以包括主机设备100和存储器设备200。主机设备100可以通过

存储器总线120连接到存储器设备200并与其通信。存储器设备200可以包括存储器单元阵列210。

31.将理解的是,当元件被称为“连接”或“耦合”到另一个元件或者在另一个元件“上”时,其可以直接连接或耦合到另一个元件或在另一个元件上、或者中间元件可以存在。相反地,当元件被称为“直接连接”或“直接耦合”到另一个元件或者“接触”另一个元件或“与”另一个元件“接触”时,在接触点处不存在中间元件。

32.主机设备100可以是例如计算系统,诸如计算机、笔记本计算机、服务器、工作站、便携式通信终端、个人数字助理(pda)、便携式多媒体播放器(pmp)、智能电话或可穿戴设备。可替代地,主机设备100可以是包括在计算系统中的组件之一,诸如图形卡。主机设备100可以用作用于执行系统10的通用计算机操作的功能块,并且可以对应于中央处理单元(cpu)、数字信号处理器(dsp)、图形处理单元(gpu)或应用处理器(ap)。

33.存储器总线120可以包括用于发送时钟信号clk、数据选通信号dqs、命令信号cmd、地址(或地址信号)addr和控制信号ctrl的信号线,以及用于发送输入/输出(i/o)数据dq的数据线(或数据总线)。为了简洁起见,主机设备100与存储器设备200之间的信号线和数据线每个都被示出为一条信号线,但实际上,主机设备100可以通过多条信号线连接到存储器设备200。

34.在主机设备100的控制下,i/o数据dq可以被写入到存储器设备200中、或者数据可以从存储器设备200中被读取。例如,存储器设备200可以包括动态随机访问存储器(dram)设备。

35.尽管上述实施例示出了存储器设备200与dram相对应,但是本发明构思的存储器设备200不限于此。根据各种实施例,存储器设备200可以对应于易失性存储器设备(诸如同步dram(sdram)、双倍数据速率sdram(ddr sdram)、低功率ddr sdram(lpddr sdram)、图形ddr sdram(gddr sdram)、宽i/odram、高带宽存储器(hbm)和混合存储器立方体(hmc))中的至少一个。根据实施例,存储器设备200可以对应于非易失性存储器设备(诸如闪存、相变ram(pram)、磁ram(mram)、电阻式ram(rram)和铁电ram(fram))中的任一个。

36.图1b示出了根据本发明构思的示例实施例的存储器设备。

37.参考图1b,存储器设备200可以包括存储器单元阵列210、行解码器202、字线解码器204、列解码器206、i/o门控电路208、控制逻辑电路220、地址缓冲器230、参考电压生成电路250、数据输入缓冲器260、数据输出缓冲器270,以及i/o焊盘290。

38.存储器单元阵列210包括以矩阵形式的行和列布置的多个存储器单元。存储器单元阵列210包括连接到多个存储器单元的多条字线wl和多条位线bl。多条字线wl可以连接到成行的多个存储器单元,并且多条位线bl可以连接到成列的多个存储器单元。

39.行解码器202可以选择连接到存储器单元阵列210的多条字线wl中的任一条。行解码器202可以解码从地址缓冲器230接收到的行地址row_addr,来选择与行地址row_addr相对应的一条字线wl并且将所选字线wl连接到字线解码器204,以激活该所选字线wl。列解码器206可以从存储器单元阵列210的多条位线bl中选择特定位线bl。列解码器206可以对从地址缓冲器230接收到的列地址col_addr进行解码以生成列选择信号csl,并且将由列选择信号csl选择的位线bl连接到i/o门控电路208。

40.根据实施例,地址缓冲器230可以包括第一运算跨导放大器231。第一运算跨导放

大器231可以接收输入到地址缓冲器230的地址信号addr。第一运算跨导放大器231可以接收地址信号addr作为第一输入并且接收具有特定电平的参考电压作为第二输入。例如,第一运算跨导放大器231可以将参考电压电平与地址信号addr的电压电平进行比较。当参考电压电平高于地址信号addr的电压电平时,第一运算跨导放大器231可以将输出线驱动为“逻辑高”。当参考电压电平低于地址信号addr的电压电平时,第一运算跨导放大器231可以将输出线驱动为“逻辑低”。第一运算跨导放大器231可以校正地址信号addr和参考电压电平之间的占空比的失配,从而即使在输出线必须被驱动为“逻辑高”的情况下也防止输出线被驱动为“逻辑低”、或者即使在输出线必须被驱动为“逻辑低”的情况下也防止输出线被驱动为“逻辑高”。尽管在上述实施例中描述了第一运算跨导放大器231包括在地址缓冲器230中,但是本发明构思不限于此。根据各种实施例,第一运算跨导放大器231可以被布置在地址缓冲器230的前一级中以校正地址信号addr的占空比错误并且可以将校正后的地址信号addr发送到地址缓冲器230。

41.控制逻辑电路220可以接收时钟信号clk和命令信号cmd并且生成用于控制存储器设备200的操作定时和/或存储器操作的控制信号ctrls。控制逻辑电路220可以通过使用控制信号ctrl来从存储器单元阵列210读取数据以及向存储器单元阵列210写入数据。根据一个实施例,控制逻辑电路220可以包括接收命令信号cmd作为输入的第二运算跨导放大器221,以及接收时钟信号clk或写入时钟信号wclk作为输入的第三运算跨导放大器222。

42.第二运算跨导放大器221可以接收被发送到控制逻辑电路220的命令信号cmd。第二运算跨导放大器221可以接收差分输入信号。例如,第二运算跨导放大器221可以接收命令信号cmd作为第一输入并且接收具有特定电平的参考电压作为第二输入。第二运算跨导放大器221可以校正命令信号cmd与参考电压电平之间的占空比的失配,以防止由于命令信号cmd的定时失配而导致的操作错误。例如,第二运算跨导放大器221可以将参考电压电平与命令信号cmd的电压电平进行比较。当参考电压电平高于命令信号cmd的电压电平时,第一运算跨导放大器231可以将输出线驱动为“逻辑高”。当参考电压电平低于命令信号cmd的电压电平时,第二运算跨导放大器221可以将输出线驱动为“逻辑低”。第二运算跨导放大器221可以校正命令信号cmd与参考电压电平之间的占空比的失配,从而即使在输出线必须被驱动为“逻辑高”的情况下也防止输出线被驱动为“逻辑低”、或者即使在输出线必须被驱动为“逻辑低”的情况下也防止输出线被驱动为“逻辑高”。尽管在上述实施例中描述了第二运算跨导放大器221包括在控制逻辑电路220中,但是本发明构思不限于此。根据各种实施例,第二运算跨导放大器221可以被布置在控制逻辑电路220的前一级中以校正命令信号cmd的占空比错误,并且可以将其占空比错误被校正了的命令信号cmd发送到控制逻辑电路220。

43.第三运算跨导放大器222可以接收被发送到控制逻辑电路220的时钟信号clk或数据选通信号dqs。第三运算跨导放大器222可以接收差分输入信号。例如,第三运算跨导放大器222可以接收时钟信号clk作为第一输入以及反相时钟信号clkb作为第二输入。在这种情况下,第三运算跨导放大器222可以用作时钟缓冲器。可替代地,第三运算跨导放大器222可以接收数据选通信号dqs作为第一输入以及反相数据选通信号dqsb作为第二输入。在这种情况下,第三运算跨导放大器222可以用作dqs缓冲器。第三运算跨导放大器222可以校正时钟信号clk或数据选通信号dqs的占空比失配。

44.i/o门控电路208可以包括用于存储由列选择信号csl选择的位线bl的读取数据的

读取数据锁存器,以及用于将写入数据写入存储器单元阵列210的写入驱动器。可以通过输出缓冲器270和i/o焊盘290来将存储在i/o门控电路208的读取数据锁存器中的读取数据提供给数据总线(或数据线)。可以通过连接到数据总线的i/o焊盘290、数据输入缓冲器260和i/o门控电路208的写入驱动器来将写入数据施加到存储器单元阵列210。

45.根据各种实施例,第四运算跨导放大器280可以被布置在发送数据dq的信号线上。例如,运算跨导放大器280可以包括在数据输入缓冲器260中。运算跨导放大器280可以接收被发送到数据输入缓冲器260的差分输入信号。例如,运算跨导放大器280可以接收数据dq作为第一输入以及反相数据dqb作为第二输入。

46.参考电压生成电路250可以提供用于存储器设备200的电路的参考电压vref。例如,控制逻辑电路220可以使用参考电压vref来与从命令总线接收到的信号的电压进行比较,以确定接收到的信号的逻辑值。

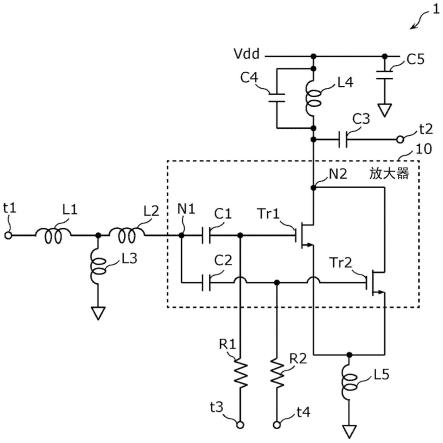

47.图2示出了根据比较示例的运算跨导放大器2000。

48.参考图2,运算跨导放大器电路2000可以包括多个电流镜电路、差分输入电路2100以及反馈电路2200。多个电流镜电路可以包括第一电流镜电路2310、第二电流镜电路2320、第三电流镜电路2330和第四电流镜电路2340。

49.差分输入电路2100可以包括第一晶体管m1、第二晶体管m2和第三晶体管m3。可替代地,差分输入电路2100可以包括第一级和第二级。例如,第一级可以包括串联连接的第一晶体管m1和第二晶体管m2,并且第二级可以包括串联连接的第一晶体管m1和第三晶体管m3。第一晶体管m1的栅极端子可以接收偏置电压v

bias

。第一晶体管m1可以基于偏置电压v

bias

来生成偏置电流i

bias

。差分输入对可以分别被输入到第二晶体管m2的栅极端子和第三晶体管m3的栅极端子。差分输入对可以对应于时钟信号clk和反相时钟信号clkb的信号对、数据选通信号dqs和反相数据选通信号dqsb的信号对、地址addr和反相地址addrb的信号对、或者数据dq和反相数据dqb的信号对。流经第二晶体管m2的电流和流经第三晶体管m3的电流的总和可以对应于偏置电流i

bias

。

50.第一电流镜电路2310可以包括第五晶体管m5、第七晶体管m7、和第九晶体管m9。第五晶体管m5、第七晶体管m7和第九晶体管m9可以每个都对应于p沟道晶体管。第五晶体管m5的栅极端子可以连接到第七晶体管m7的栅极端子和第九晶体管m9的栅极端子。也就是说,第五晶体管m5、第七晶体管m7和第九晶体管m9可以形成公共栅极。第一电流镜电路2310可以基于第一参考电流i

ref1

来生成镜电流。第五晶体管m5可以基于第一参考电流i

ref1

来生成第一偏置电压v

bias1

。第一偏置电压v

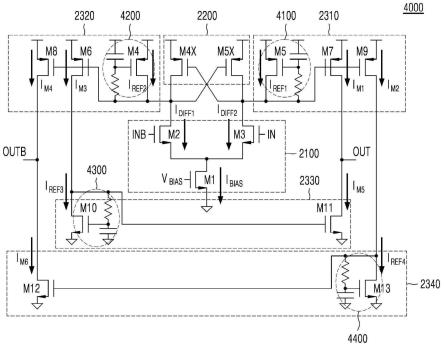

bias1

可以对应于第一电流镜电路2310的公共栅极的电压。第七晶体管m7和第九晶体管m9可以基于第一偏置电压v

bias1

来分别生成第一镜电流i

m1

和第二镜电流i

m2

。当第七晶体管m7和第九晶体管m9具有相同的特性时,第一镜电流i

m1

的幅度可以与第二镜电流i

m2

的幅度相同。当第七晶体管m7的宽度与长度之间的比不同于第九晶体管m9的宽度与长度之间的比时,第一镜电流i

m1

可以被生成为与第七晶体管m7的宽度与长度之间的比成比例,并且第二镜电流i

m2

可以被生成为与第九晶体管m9的宽度与长度之间的比成比例。

51.第二电流镜电路2320可以包括第四晶体管m4、第六晶体管m6和第八晶体管m8。第四晶体管m4、第六晶体管m6以及第八晶体管m8可以每个都对应于p沟道晶体管。第四晶体管m4的栅极端子可以连接到第六晶体管m6的栅极端子和第八晶体管m8的栅极端子。也就是

说,第四晶体管m4、第六晶体管m6以及第八晶体管m8可以形成公共栅极。第二电流镜电路2320可以基于第二参考电流i

ref2

来生成镜电流。第四晶体管m4可以基于第二参考电流i

ref2

来生成第二偏置电压v

bias2

。第二偏置电压v

bias2

可以对应于第二电流镜电路2320的公共栅极的电压。第六晶体管m6和第八晶体管m8可以基于第二偏置电压v

bias2

来分别生成第三镜电流i

m3

和第四镜电流i

m4

。

52.第三电流镜电路2330可以包括第十晶体管m10和第十一晶体管m11。第十晶体管m10和第十一晶体管m11可以每个都对应于n沟道晶体管。第十晶体管m10的栅极端子可以连接到第十一晶体管m11的栅极端子。也就是说,第十晶体管m10和第十一晶体管m11可以形成公共栅极。第三电流镜电路2330可以基于第三参考电流i

ref3

来生成镜电流。第三参考电流i

ref3

可以与通过第六晶体管m6生成的第三镜电流i

m3

相同。第十晶体管m10可以基于第三参考电流i

ref3

来生成第三偏置电压v

bias3

。第三偏置电压v

bias3

可以对应于第三电流镜电路2330的公共栅极的电压。第十一晶体管m11可以基于第三偏置电压v

bias3

生成第五镜电流i

m5

。

53.第四电流镜电路2340可以包括第十二晶体管m12和第十三晶体管m13。

54.第十二晶体管m12和第十三晶体管m13可以每个都对应于n沟道晶体管。

55.第十二晶体管m12的栅极端子可以连接到第十三晶体管m13的栅极端子。也就是说,第十二晶体管m12和第十三晶体管m13可以形成公共栅极。第四电流镜电路2340可以基于第四参考电流i

ref4

来生成镜电流。第四参考电流i

ref4

可以与通过第九晶体管m9生成的第二镜电流i

m2

相同。第十三晶体管m13可以基于第四参考电流i

ref4

(或第二镜电流i

m2

)来生成第四偏置电压v

bias4

。第四偏置电压v

bias4

可以对应于第四电流镜电路2340的公共栅极的电压。第十二晶体管m12可以基于第四偏置电压v

bias4

来生成第六镜电流i

m6

。

56.反馈电路2200可以包括第四反馈晶体管m4x和第五反馈晶体管m5x。第四反馈晶体管m4x和第五反馈晶体管m5x可以每个都对应于p沟道晶体管。第一电流镜电路2310的第五晶体管m5可以通过第四反馈晶体管m4x连接到第二电流镜电路2320。第二电流镜电路2320的第四晶体管m4可以通过第五反馈晶体管m5x连接到第一电流镜电路2310。

57.第九晶体管m9的漏极端子可以对应于第十三晶体管m13的漏极端子。也就是说,第九晶体管m9可以与第十三晶体管m13形成公共漏极。由第九晶体管m9生成的第二镜电流i

m2

可以作为通过公共漏极而输入到第十三晶体管m13的第四参考电流i

ref4

来操作。

58.第六晶体管m6的漏极端子可以对应于第十晶体管m10的漏极端子。也就是说,第六晶体管m6可以与第十晶体管m10形成公共漏极。由第六晶体管m6生成的第三镜电流i

m3

可以作为通过公共漏极而输入到第十晶体管m10的第三参考电流i

ref3

来操作。

59.输出端子out可以基于通过第七晶体管m7生成的第一镜电流i

m1

和通过第十一晶体管m11生成的第五镜电流i

m5

之间的差值来输出信号。在下文中,为了便于描述,可以互换地使用输出端子out和输出信号out的术语。

60.反相输出端子outb基于在通过第八晶体管m8生成的第四镜电流i

m4

与通过第十二晶体管m12生成的第六镜电流i

m6

之间的差值来输出信号。在下文中,为了便于描述,可以互换地使用反相输出端子outb和反相输出信号outb的术语。

61.图3a示出了根据示例实施例的nmos有源电感器,并且图3b示出了根据示例实施例的pmos有源电感器。

62.参考图3a,图3a的nmos有源电感器可以包括n沟道晶体管nmos、电阻器r和电容器

c。这里,电容器c可以包括寄生电容或所采用的电容。n沟道晶体管nmos可以连接到电阻器r和电容器c。例如,n沟道晶体管nmos的栅极端子可以连接到电容器c和电阻器r。电容器c可以连接在地gnd与n沟道晶体管nmos的栅极端子之间。在下文中,为了便于描述,可以互换地使用地gnd、地节点gnd和地线gnd的术语。电阻器r可以将n沟道晶体管nmos的栅极端子连接到n沟道晶体管nmos的漏极端子。如下参考图4所描述的,图3a中所示的nmos有源电感器可以替换图4的第十晶体管m10和第十三晶体管m13。

63.参考图3b,图3b的pmos有源电感器可以包括p沟道晶体管pmos、电阻器r和电容器c。p沟道晶体管pmos可以进一步连接到电阻器r和电容器c。例如,p沟道晶体管pmos的栅极端子可以连接到电容器c和电阻器r。电容器c可以连接在正电源电压vdd与栅极端子之间。在下文中,为了便于描述,可以互换地使用正电源电压vdd、电源电压节点vdd和电源电压线vdd的术语。电阻器r可以将p沟道晶体管pmos的栅极端子连接到漏极端子。如下参考图4所描述的,图3b中所示的pmos有源电感器可以替换图4的第四晶体管m4和第五晶体管m5。

64.图3c示出了根据示例实施例的包括有源电感器的晶体管的小信号等效电路,并且图3d是示出了根据本发明构思的示例实施例的频率和输入阻抗(zin)的图。

65.图3c示出了图3a中连接到电阻器r和电容器c的n沟道晶体管nmos的小信号等效电路。从施加了输入电压的节点看,输入阻抗z

in

可以总结如下。

66.等式1

[0067][0068]

这里,s表示复数,c表示电容值,r表示电阻,并且gm表示跨导。

[0069]

根据一个实施例,当输入低频信号或直流(dc)信号时,s收敛到约为0,因此,z

in

的值可以对应于1/gm。根据另一个实施例,当输入高频信号时,s收敛到无穷大,并且因此,z

in

的值可以对应于r。

[0070]

根据各种实施例,可以看出,图3a中连接到电阻器r和电容器c的n沟道晶体管nmos在预定义部分的频率下以电感器的方式来感应地(inductively)操作。

[0071]

预定义部分可以对应于输入阻抗的零点频率和极点频率中的每一个。零点频率wz可以是1/rc,并且极点频率w

p

可以是gm/c。也就是说,当满足r》1/gm并且输入信号的频率大于零点频率且小于极点频率时,图3a的等效电路和图3b的等效电路可以以与电感器相同的方式来操作。

[0072]

参考图3d的图,虚线示出了当仅连接n沟道晶体管或p沟道晶体管时根据频率变化的阻抗变化。当输入信号是低频信号时,输入阻抗z

in

可以对应于1/gm。因此,当仅连接n沟道晶体管或p沟道晶体管时,不存在作为电感器操作的部分(wz《w《w

p

),并且频率(即,带宽)也减小。

[0073]

参考图3d的图,实线示出了当连接图3a的nmos有源电感器或图3b的pmos有源电感器时根据频率变化的输入阻抗z

in

变化。如上所述,在图3c的小信号等效电路中,可以看出,nmos有源电感器或pmos有源电感器不仅在预定义部分的频率下作为电感器来操作,而且频率(即,带宽)增加。

[0074]

图4示出了根据本发明构思的示例实施例的包括有源电感器的运算跨导放大器

4000。图4中示出的运算跨导放大器4000可以对应于图1b中示出的第一运算跨导放大器至第四运算跨导放大器231、221、222和280。

[0075]

参考图4,根据本发明构思的示例实施例的运算跨导放大器电路4000还可以包括多个有源电感器。例如,运算跨导放大器电路4000可以包括第一有源电感器4100、第二有源电感器4200、第三有源电感器4300和第四有源电感器4400。

[0076]

根据各种实施例,第一有源电感器4100和第二有源电感器4200可以对应于pmos有源电感器。例如,第一有源电感器4100和第二有源电感器4200可以每个都包括p沟道晶体管、电阻器和电容器。例如,第一有源电感器4100可以包括第五晶体管m5、电阻器和电容器。例如,通过将第五晶体管m5的栅极端子连接到电容器和电阻器,第五晶体管m5可以作为第一有源电感器4100来操作。第一电流镜电路2310可以包括第一有源电感器4100、第七晶体管m7和第九晶体管m9。在另一个示例中,第二有源电感器4200可以包括第四晶体管m4、电阻器和电容器。通过将第四晶体管m4的栅极端子连接到电容器和电阻器,第四晶体管m4可以作为第二有源电感器4200来操作。第二电流镜电路2320可以包括第二有源电感器4200、第六晶体管m6和第八晶体管m8。

[0077]

根据各种实施例,第三有源电感器4300和第四有源电感器4400可以对应于nmos有源电感器。例如,第三有源电感器4300和第四有源电感器4400可以每个都包括n沟道晶体管、电阻器和电容器。例如,第三有源电感器4300可以包括第十晶体管m10、电阻器和电容器。通过将第十晶体管m10的栅极端子连接到电容器和电阻器,第三有源电感器4300可以作为nmos有源电感器来操作。第三电流镜电路2330可以包括第三有源电感器4300和第十一晶体管m11。在另一个示例中,第四有源电感器4400可以包括第十三晶体管m13、电阻器和电容器。通过将第十三晶体管的栅极端子连接到电容器和电阻器,第四有源电感器4400可以作为nmos有源电感器来操作。第四电流镜电路2340可以包括第四有源电感器4400和第十二晶体管m12。

[0078]

图5示出了根据本发明构思的示例实施例的图4的运算跨导放大器4000中的上电流和下电流的电路径。

[0079]

参考图5,输出端子out可以基于第一路径的上电流和第二路径的下电流之间的差值来输出信号。例如,输出端子out可以基于通过第七晶体管m7生成的第一镜电流i

m1

和通过第十一晶体管m11生成的第五镜电流i

m5

之间的差值来输出信号。

[0080]

第二晶体管m2可以基于反相输入信号inb来生成第一差分电流i

diff1

。第三晶体管m3可以基于输入信号in来生成第二差分电流i

diff2

。在下文中,为了便于描述,可以互换地使用术语输入信号in和输入端子in,并且可以互换地使用反相输入信号inb和反相输入端子inb。

[0081]

第二差分电流i

diff2

可以与由第一电流镜电路2310的第五晶体管m5生成的第一参考电流i

ref1

相同。第七晶体管m7可以基于第五晶体管m5的第一参考电流i

ref1

来生成第一镜电流i

m1

。例如,假设第五晶体管m5的宽度与长度的比与第七晶体管m7的宽度与长度的比相同,则第一镜电流i

m1

可以等于第一参考电流i

ref1

。例如,流经输出端子out的两个电流当中的、通过其第一镜电流i

m1

被镜像的第一路径可以对应于通过输入端子in、第一电流镜电路2310的公共漏极节点和第七晶体管m7的电路径。

[0082]

第一差分信号i

diff1

可以与由第二电流镜电路2320的第四晶体管m4生成的第二参

考电流i

ref2

相同。第六晶体管m6可以基于第四晶体管m4的第二参考电流i

ref2

来生成第三镜电流i

m3

。第三镜电流i

m3

可以通过第六晶体管m6和第十晶体管m10的公共漏极节点输入到第十晶体管m10。例如,第三镜电流i

m3

可以对应于第十晶体管m10的第三参考电流i

ref3

。第三镜电流i

m3

(其是第三参考电流i

ref3

)可以由第十一晶体管m11的第五镜电流i

m5

来镜像。例如,流经输出端子out的两个电流当中的、通过其第五镜电流i

m5

被镜像的第二路径可以对应于通过反相输入端子inb、第二电流镜电路2320的公共漏极节点、第六晶体管m6、第十晶体管m10和第十一晶体管m11的电路径。

[0083]

第一电流镜电路2310可以基于第二差分电流i

diff2

来生成第一镜电流i

m1

并且经由输出端子out来输出第一镜电流i

m1

。第二电流镜电路2320可以基于第一差分电流i

diff1

来生成第三镜电流i

m3

并且经由第三电流镜电路2330的第十一晶体管m11的栅极端子来输出第三镜电流i

m3

。第三电流镜电路2330可以基于第三镜电流i

m3

来生成第五镜电流i

m5

并且经由输出端子out来输出第五镜电流i

m5

。

[0084]

在上述实施例中,针对输出端子out示出了第一路径的上电流和第二路径的下电流,但是本发明构思不限于此。反相输出端子outb可以基于第三路径的上电流和第四路径的下电流之间的差值来输出信号。例如,第四电流镜电路2340可以基于第二镜电流i

m2

来生成第六镜电流i

m6

并且经由反相输出端子outb来输出第六镜电流i

m6

。

[0085]

差分输入电路2100可以包括第一级和第二级。例如,第一级可以包括第二晶体管m2,并且第二级可以包括第三晶体管m3。

[0086]

差分输入电路2100的第一级可以根据反相输入信号inb来输出第一差分电流i

diff1

。反馈电路2200可以基于反相输入信号inb来放大第一差分电流i

diff1

。

[0087]

例如,第二晶体管m2可以根据反相输入信号inb来生成第一差分电流i

diff1

。第一差分信号i

diff1

可以等于由第二电流镜电路2320的第四晶体管m4生成的第二参考电流i

ref2

。第八晶体管m8可以基于第四晶体管m4的第二参考电流i

ref2

来生成第四镜电流i

m4

。第四镜电流i

m4

可以对应于第三路径的上电流。例如,第三路径可以包括反相输入端子inb、第二电流镜电路2320的公共漏极节点、第八晶体管m8以及反相输出端子outb。

[0088]

差分输入电路2100的第二级可以根据输入信号in来输出第二差分电流i

diff2

。反馈电路2200可基于输入信号in来放大第二差分电流i

diff2

。

[0089]

例如,第三晶体管m3可以根据输入信号in来生成第二差分电流i

diff2

。第二差分信号i

diff2

可以等于由第一电流镜电路2310的第五晶体管m5生成的第一参考电流i

ref1

。第九晶体管m9可以基于第五晶体管m5的第一参考电流i

ref1

来生成第二镜电流i

m2

。第二镜电流i

m2

可以通过由第十三晶体管m13和第九晶体管m9共享的漏极节点、作为第十三晶体管m13的第四参考电流i

ref4

而被输入。第十二晶体管m12可以基于第十三晶体管m13的第四参考电流i

ref4

来生成第六镜电流i

m6

。第六镜电流i

m6

可以对应于第四路径的下电流。例如,第四路径可以包括输入端子in、第一电流镜电路2310的公共漏极节点、第九晶体管m9、第十三晶体管m13、第十二晶体管m12以及反相输出端子outb。

[0090]

这里,输入信号in和反相输入信号inb可以对应于时钟信号clk和反相时钟信号clkb的信号对、数据选通信号dqs和反相数据选通信号dqsb的信号对、地址addr和反相地址addrb的信号对、或数据dq和反相数据dqb的信号对。

[0091]

根据各种实施例,在上电流和下电流之间可能出现失配。在失配中,上电流和下电

流可以流经不同的电路径。例如,第一路径的上电流可以通过一次电流镜像(第一电流镜电路2310)被输入到输出端子out,并且第二路径的下电流可以通过两次电流镜像(第二电流镜电路2320和第三电流镜电路2330)被输入到输出端子out。例如,第一路径的上电流可以通过一次电流镜像(第一电流镜电路2310)经由输出端子out来输出,并且第二路径的下电流可以通过两次电流镜像(第二电流镜电路2320和第三电流镜电路2330)经由输出端子out来输出。

[0092]

图6a是示出了根据比较示例的占空比的失真的图。

[0093]

参考图6a,示出了上电流和下电流的瞬态响应的图。横轴表示时间,纵轴表示电压。

[0094]

图2的运算跨导放大器电路2000可能引起占空比错误。参考图5中的上电流和下电流,图2的运算跨导放大器电路2000具有不同长度的上电流和下电流的电路径。具体地,上电流可以对应于通过第一电流镜电路2310被镜像一次的电流,而下电流可以对应于通过第二电流镜电路2320和第三电流镜电路2330被镜像两次的电流。镜像的次数改变,因此,上电流开始转变的时间点可以先于下电流开始转变的时间点。也就是说,在上电流等于下电流的时间点处的输出端子out的电压可能不对应于正电源电压vdd的一半。也就是说,当输出端子out的电压不是正电源电压vdd的一半时,上电流与下电流切换,因此可能出现占空比错误。在上电流与下电流交叉的时间点,占空比错误可能由于输出端子out的电压与正电源电压vdd的一半之间的差而出现。

[0095]

图6b是示出了根据示例实施例的基于nmos有源电感器的占空比的失真减小的图,图6c是示出了根据示例实施例的基于pmos有源电感器的占空比的失真减小的图,以及图6d是示出了根据本发明构思的示例实施例的基于nmos有源电感器和pmos有源电感器的占空比的失真减小的图。

[0096]

图6b可以是与仅包括nmos有源电感器的运算跨导放大器电路4000相对应的图。例如,参考图4,图6b示出了在第三电流镜电路2330和第四电流镜电路2340分别包括第三有源电感器4300和第四有源电感器4400的情况下的占空比错误校正。

[0097]

根据各种实施例,当参考图5时,上电流可以对应于通过第一电流镜电路2310被镜像一次的电流。因此,图6b的上电流开始转变的时间点不改变,并且上电流的转变斜率可以不改变。下电流可以对应于通过第二电流镜电路2320和第三电流镜电路2330被镜像两次的电流。因此,下电流基于第三电流镜电路2330的第三有源电感器4300开始转变的时间点可以向前移动,并且下电流的转变斜率也可以增加。

[0098]

图6c可以是与仅包括pmos有源电感器的运算跨导放大器电路4000相对应的图。例如,当参考图4时,图6c示出了在第一电流镜电路2310和第二电流镜电路2320分别包括第一有源电感器4100和第二有源电感器4200的情况下的占空比错误校正。

[0099]

根据各种实施例,当参考图5时,上电流可以对应于通过第一电流镜电路2310被镜像一次的电流。因此,图6c的上电流基于第一有源电感器4100开始转变的时间点可以向前移动,并且上电流的转变斜率也可以增加。此外,下电流可以对应于通过第二电流镜电路2320和第三电流镜电路2330被镜像两次的电流。因此,下电流基于第二电流镜电路2320的第二有源电感器4200开始转变的时间点可以向前移动,并且下电流的转变斜率也可以增加。然而,如图6a所示,即使由于上电流的快速转变时间而出现占空比错误,也通过使用一

次有源电感器来改进上电流和下电流的占空比,并且可以看出,占空比错误仍然存在。

[0100]

图6d可以是与包括pmos有源电感器和nmos有源电感器两者的运算跨导放大器电路4000相对应的图。例如,参考图4,图6d示出了在第一电流镜电路2310至第四电流镜电路2340分别包括第一有源电感器4100至第四有源电感器4400的情况下的占空比错误校正。

[0101]

如在图6c中,上电流基于第一有源电感器4100开始转变的时间点可以向前移动,并且上电流的转变斜率也可以增加。然而,可以通过使用与第二电流镜电路2320的第二有源电感器4200和第三电流镜电路2330的第三有源电感器4300相对应的两个有源电感器来校正下电流的占空比错误。例如,与图6b的下电流相比,图6d的下电流可以具有更快的转变时间点,并且转变斜率可以进一步增加。例如,因为通过使用两个有源电感器来改进了转变特性,因此下电流与上电流之间的占空比错误可以被校正。

[0102]

图7a是示出了当仅包括pmos有源电感器时的占空比的失真的图。

[0103]

参考图7a,运算跨导放大器电路4000可以仅包括pmos有源电感器。

[0104]

参考图4,第一电流镜电路2310可以包括第一有源电感器4100、第七晶体管m7和第九晶体管m9。第一有源电感器4100可以对应于pmos有源电感器。第二电流镜电路2320可以包括第二有源电感器4200、第六晶体管m6和第八晶体管m8。第二有源电感器4200可以对应于pmos有源电感器。第三电流镜电路2330可以仅包括第十晶体管m10和第十一晶体管m11而没有第三有源电感器4300,并且第四电流镜电路2340可以仅包括第十二晶体管m12和第十三晶体管m13而没有第四有源电感器4400。也就是说,第三电流镜电路2330和第四电流镜电路2340可以不包括电容器和电阻器。

[0105]

图7a示出了根据各种实施例的执行工艺、电压和温度(process,voltage,and temperature,pvt)的变体的结果。横轴可以对应于指示传输速率的数据速率。纵轴可以指示占空比是否彼此匹配。当占空比匹配时,占空比(即,匹配)可以是50%。

[0106]

根据各种实施例,“sslvct”指示在有源电感器的p沟道晶体管是缓慢的(ss)、电源电压低(lv)并且操作温度低(ct)的环境中随着数据速率增加的占空比之间的匹配程度。当数据速率低至800时,上电流和下电流之间的匹配可以对应于51。然而,当数据速率增加到6400时,上电流和下电流之间的匹配可以增加到58.8。

[0107]

根据各种实施例,“ffhvht”指示在有源电感器的p沟道晶体管是快速的(ff)、电源电压高(hv)并且操作温度高(ht)的环境中随着数据速率增加的占空比之间的匹配程度。当数据速率低至800时,上电流和下电流之间的匹配可以对应于50。然而,当数据速率增加到6400时,上电流和下电流之间的匹配可以降低到45.9。也就是说,“ffhvht”和“sslvct”中的占空比匹配之间的差可以宽至12.9。

[0108]

图7b是示出了根据本发明构思的示例实施例的当包括nmos有源电感器和pmos有源电感器两者时的占空比的失真的图

[0109]

参考图7b,运算跨导放大器电路4000可以包括pmos有源电感器和nmos有源电感器两者。

[0110]

参考图4,第一电流镜电路2310可以包括第一有源电感器4100、第七晶体管m7和第九晶体管m9。第二电流镜电路2320可以包括第二有源电感器4200、第六晶体管m6和第八晶体管m8。第三电流镜电路2330可以包括第三有源电感器4300和第十一晶体管m11,并且第四电流镜电路2340可以包括第十二晶体管m12和第四有源电感器4400。例如,第一电流镜电路

2310至第四电流镜电路2340中的所有都可以包括电容器和电阻器。

[0111]

根据各种实施例,“sslvct”指示在nmos有源电感器的晶体管和pmos有源电感器的晶体管是缓慢的(ss)、电源电压低(lv)并且操作温度低(ct)的环境中随着数据速率增加的占空比之间的匹配程度。当数据速率低至800时,上电流和下电流之间的匹配可以对应于50。然而,当数据速率增加到6400时,上电流和下电流之间的匹配可以增加到54.9。

[0112]

根据各种实施例,“ffhvht”指示在nmos有源电感器的晶体管和pmos有源电感器的晶体管是快速的(ff)、电源电压高(hv)并且操作温度高(ht)的环境中随着数据速率增加的占空比之间的匹配程度。当数据速率低至800时,上电流和下电流之间的匹配可以对应于50。然而,当数据速率增加到6400时,上电流和下电流之间的匹配可以降低到46.1。也就是说,“ffhvht”和“sslvct”中的占空比匹配之间的差可以宽至8.8。根据本发明构思的示例实施例,可以看出,当包括pmos有源电感器和nmos有源电感器两者时,而不是仅包括pmos有源电感器时或者仅包括nmos有源电感器,随着数据速率增加,上电流与下电流之间的占空比失配可以减小。

[0113]

图8示出了根据本发明构思的示例实施例的包括nmos有源电感器和pmos有源电感器的放大器电路。

[0114]

参考图8,放大器电路8000可以对应于差分输入-单端输出放大器。

[0115]

根据各种实施例的放大器电路8000可以包括第一单元电路8100和第二单元电路8200。第一单元电路8100可以被称为n型放大器。第二单元电路8200可以被称为p型放大器。包括第一单元电路8100和第二单元电路8200的放大器电路8000可以被称为np型放大器。

[0116]

第一单元电路8100可以包括用于生成偏置电流的第一晶体管m1和第三晶体管m3。第一晶体管m1可以对应于n沟道晶体管,并且第三晶体管m3可以对应于p沟道晶体管。第一偏置电压biasn可以被输入到第一晶体管m1的栅极端子。第一晶体管m1可以基于第一偏置电压biasn来生成第一偏置电流i

bias1

。第二偏置电压biasp可以被设置为等于第三晶体管m3的阈值电压。因此,第三晶体管m3可以被导通以将正电源电压vdd连接到第九晶体管m9和第十晶体管m10的源极节点。

[0117]

第一单元电路8100可以包括第一差分输入电路8110。第一差分输入电路8110可以包括第五晶体管m5和第六晶体管m6。第五晶体管m5和第六晶体管m6可以对应于n沟道晶体管。第五晶体管m5和第六晶体管m6可以接收差分输入对。例如,第五晶体管m5可以接收时钟信号clk,并且同时,第六晶体管m6可以接收反相时钟信号clkb。第五晶体管m5可以基于通过输入端子in接收到的差分输入信号来生成第一差分电流i

diff1

。第六晶体管m6可以基于通过反相输入端子inb接收到的差分输入信号来生成第二差分电流i

diff2

。第一差分电流i

diff1

和第二差分电流i

diff2

之和可以对应于第一偏置电流i

bias1

的幅度。

[0118]

第一单元电路8100可以包括第一电流镜电路8120。第一电流镜电路8120可以包括第九晶体管m9和pmos有源电感器8125。pmos有源电感器8125可以包括第十晶体管m10、电阻器和电容器。第十晶体管m10的栅极端子可以连接到pmos有源电感器8125的电阻器和电容器。pmos有源电感器8125的电阻器可以连接在第十晶体管m10的栅极端子与第十晶体管m10的漏极端子之间。pmos有源电感器8125的电容器可以连接在第十晶体管m10的栅极端子与正电源电压vdd之间。第十晶体管m10的漏极端子可以连接到第九晶体管m9的栅极端子。第十晶体管m10可以与第六晶体管m6共享漏极节点。因此,由第六晶体管m6生成的第二差分电

流i

diff2

可以等于第十晶体管m10的第一参考电流i

ref1

。第九晶体管m9可以基于第十晶体管m10的第一参考电流i

ref1

来生成第一镜电流i

m1

。反相输出端子outb可以基于第一镜电流i

m1

和第一差分电流i

diff1

之间的差来输出信号。

[0119]

第二单元电路8200可以包括用于生成偏置电流的第二晶体管m2和第四晶体管m4。第二晶体管m2可以对应于n沟道晶体管,并且第四晶体管m4可以对应于p沟道晶体管。第一偏置电压biasn可以被输入到第二晶体管m2的栅极端子。第二晶体管m2的阈值电压可以被设置为等于第一偏置电压biasn。因此,第二晶体管m2可以被导通以将第十一晶体管m11的源极节点连接到地节点gnd。第四晶体管m4可以基于第二偏置电压biasp来生成第二偏置电流i

bias2

。

[0120]

第二单元电路8200可以包括第二差分输入电路8210。第二差分输入电路8210可以包括第七晶体管m7和第八晶体管m8。第七晶体管m7和第八晶体管m8中的每一个可以对应于p沟道晶体管。第七晶体管m7和第八晶体管m8可以接收差分输入对。第七晶体管m7可以基于通过输入端子in接收到的差分输入信号来生成第三差分电流i

diff3

。第八晶体管m8可以基于通过反相输入端子inb接收到的差分输入信号来生成第四差分电流i

diff4

。第三差分电流i

diff3

和第四差分电流i

diff4

之和可以对应于第二偏置电流i

bias2

的幅度。

[0121]

第二单元电路8200可以包括第二电流镜电路8220。第二电流镜电路8220可以包括第十一晶体管m11和nmos有源电感器8225。nmos有源电感器8225可以包括第十二晶体管m12、电阻器和电容器。第十二晶体管m12的栅极端子可以连接到nmos有源电感器8225的电阻器和电容器。nmos有源电感器8225的电阻器可以连接在第十二晶体管m12的栅极端子和第十二晶体管m12的漏极端子之间。nmos有源电感器8225的电容器可以连接在第十二晶体管m12的栅极端子和地节点gnd之间。第十二晶体管m12的漏极端子可以连接到第十一晶体管m11的栅极端子。第十二晶体管m12可以与第八晶体管m8共享漏极节点。因此,由第八晶体管m8生成的第四差分电流i

diff4

可以等于第十二晶体管m12的第二参考电流i

ref2

。第十一晶体管m11可以基于第十二晶体管m12的第二参考电流i

ref2

来生成第二镜电流i

m2

。反相输出端子outb可以基于第二镜电流i

m2

和第三差分电流i

diff3

之间的差来输出信号。

[0122]

图9是示出了根据本发明构思的示例实施例的频率和增益的图。

[0123]

图9中示出了使用多个电阻值的频率和增益之间的关系。假设包括在图8的放大器电路8000中的nmos有源电感器8225和pmos有源电感器8125中的每一个的电容c为40ff。当nmos有源电感器8225和pmos有源电感器8125中的每一个的电阻值是8kω时,可以看出,与电阻值是4kω的情况相比,增益增加了2db。例如,当电阻值为4kω时,最大增益约为17db,并且当电阻值为8kω时,最大增益大约为19db。在图9中,当操作频率是2.4ghz并且电阻值是4kω、5kω、6kω、7kω以及8kω时,增益分别大约为15.3db、16db、16.7db、17db以及17.3db。诸如“大约”的术语可以反映仅以小的相对方式和/或以不显著改变特定元素的操作、功能或结构的方式而变化的量、尺寸、方向或布局。例如,从“大约0.1到大约1”的范围可以包含诸如在0.1附近的0%至5%偏差的范围以及在1附近的0%至5%偏差的范围,尤其是在这种偏差维持与所列出的范围相同的效果时。

[0124]

在不包括nmos有源电感器8225和pmos有源电感器8125的已知的np型放大器电路中,参考与0db相对应的频率的带宽可以对应于8.77ghz。根据各种实施例,可以看出,包括nmos有源电感器8225和pmos有源电感器8125的图8的放大器电路8000具有增加了大约33%

的11.7ghz的带宽。

[0125]

根据各种实施例,当操作频率是2.4ghz时,已知的np型放大器电路可以具有10.5db的增益,并且可以看出,包括nmos有源电感器8225和pmos有源电感器8125的图8的放大器电路8000具有增加了大约46%~65%的大约15.3db~17.3db的增益范围。

[0126]

图10是示出了根据本发明构思的示例实施例的转换速率的增加的图。

[0127]

图10示出了已知的np型放大器电路的转变模拟结果以及包括nmos有源电感器8225和pmos有源电感器8125的图8的放大器电路8000的转变模拟结果。

[0128]

已知的np型放大器电路的输出信号达到瞬态响应值的一半的时间点被称为时间点t1。图8的放大器电路8000的输出信号达到瞬态响应值的一半的时间点被称为时间点t2。如图10所示,可以看出,时间点t2比时间点t1早8.7ps。

[0129]

例如,在包括pmos有源电感器8125和nmos有源电感器8225的放大器电路8000中,可以在有源电感器操作的频率带宽中形成rl电路,并且可以看出,根据rl电路的低通滤波器(lpf)的特性,瞬态响应的特性得到改进并且转换速率增大。

[0130]

尽管已经参考本发明构思的实施例具体地示出和描述了本发明构思,然而,应当理解的是,在不脱离所附权利要求的精神和范围的情况下,可以在形式和细节上对本发明构思的实施例做出各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。