1.本发明涉及处理器核的设计技术领域,尤其是指一种基于处理器调试架构的指令可编程缓冲区设计系统。

背景技术:

2.在处理器的设计过程中,如果缺乏一个功能完善的调试系统,那么当设计从工具仿真发展到硬件验证,再到最后的硅实现时,设计者对于处理器当前状态的了解和控制会急剧下降,控制器在运行时其内部状态对于设计者而言等同于一个“黑盒子”。处理器软件和硬件的开发调试都会因为调试手段的缺乏而极大程度受限。

3.对于嵌入式平台而言,调试器软件一般运行于主机pc端,而被调试的处理器往往是在嵌入式开发板上,这是交叉编译和远程调试的一种典型场景。调试器软件需要硬件的支持才能取得处理器的控制权并对其进行调试,在处理器的硬件架构中,往往含有一个硬件调试模块。该调试模块通过物理介质(譬如jtag接口)与主机端的调试软件进行通信接受其控制,然后调试模块对处理器核进行控制。

4.常用的处理器调试机制分为两种,分别是“追踪调试”和“交互式调试”。追踪调试只跟踪记录处理器核执行过的所有程序指令,不会打断干扰处理器的执行过程。但是由于处理器的运行速度非常快,每秒钟能执行上百万条指令,产生的信息量非常巨大。追踪调试器的硬件单元需要记录下所有的指令,对于处理速度的要求,数据的压缩、传输和存储等都是极大挑战。追踪调试器的硬件实现会涉及相比交互调试器而言更加复杂的技术,同时硬件开销也更大,追踪调试器往往只在比较高端的处理器中使用。

5.交互式调试是最常见的一种处理器调试机制,从最低端到最高端的处理器,交互调试几乎是所有处理器必备的功能。调试器软件能够直接取得处理器的控制权,进而对其以一种交互的方式进行调试。交互式调试对于处理器的运行具有打扰性,在调试模式下和全速运行下的结果可能会出现差异。

6.交互式调试可以直接暂停当前处理器进程进入调试模式,也可以设置断点,当程序运行到断点时,处理器会产生异常并进入调试模式的异常服务程序。调试模式下,调试器软件获得处理器的控制权,可以查看和改变处理器的运行状态,也可以下载并运行一段程序,查看程序运行状态,完成调试后可以退出测试模式并恢复处理器正常运行状态。如何实现结构简单、功能多样且灵活易用的交互式调试机制是处理器调试架构设计中需要解决的重点技术问题。

技术实现要素:

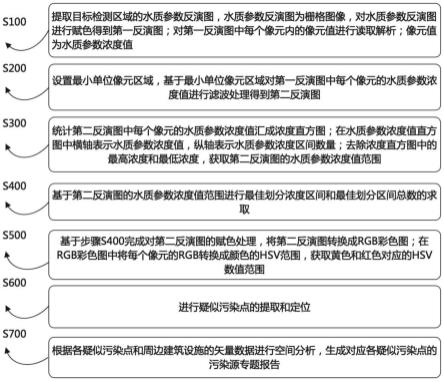

7.为此,本发明所要解决的技术问题在于克服现有技术中调试模式下,软件调试人员除了能够获得处理器当前运行状态之外,更希望可以控制处理器运行一条指令或者一段程序,详细观察处理器每运行完一条指令后的状态变化,从而更直观地复现处理器正常运行时程序进入异常的现场并定位异常原因的问题。

8.为解决上述技术问题,本发明的一种基于处理器调试架构的指令可编程缓冲区设计系统,所述设计系统中搭建的处理器核系统为本技术基本框架,服务于指令可编程缓冲区,所述的处理器核系统包括调试接口模块、接口转换模块、调试模块,其中在调试模块的硬件设计中增加指令可编程缓冲区设计,为软件调试人员提供调试模式下下载指令至处理器核执行的途径;

9.调试接口模块的寄存器组中包含一个操作access寄存器,该寄存器的位域分为三部分:地址、数据和读写类型。接口转换模块将操作寄存器值按照约定的格式转换成并行总线访问,并行总线访问操作的地址、数据和读写类型均由操作寄存器值来决定。

10.调试模块包含并行总线接口,实现与接口转换模块的并行总线通信。调试模块实现了处理器调试相关的寄存器组,与处理器核之间通过硬件控制和数据信号直接相连,这些控制和数据信号可以实现调试模块对处理器核的全部调试功能。

11.本发明实现了处理器调试架构交互式调试机制中的指令可编程缓冲区设计,提供了三种在调试模式下通过硬件调试模块控制处理器运行指令的方法。调试模式下,指令可编程缓冲区中的指令或者程序,可以直接下载至处理器流水线的取指缓存队列并执行。

12.第一种实现方法是调试模块的指令传输itr寄存器。该寄存器可以存储最多一条32位指令,向该寄存器写入想要执行的指令,调试模块会直接将该指令下载至处理器流水线的取指缓存队列,然后通过流水线执行该指令。

13.第二种实现方法是调试模块的程序缓冲pb[0:15]寄存器组。该寄存器组可以最多存储16条32位指令,预先将想要执行的一段程序(不超过16条指令)写入该寄存器组,然后配置指令长度位通知硬件想要执行的指令数,最后配置执行位。调试模块会按照配置的指令数逐条将程序缓冲寄存器组中的指令下载至流水线执行。

[0014]

第三种实现方法是调试模块的抽象命令,包括抽象命令cmd和抽象数据data[0:n]寄存器组。抽象命令实际上是通过配置上述寄存器,让调试模块自动产生处理器可执行的固定格式指令,然后下载至处理器流水线的取指缓存队列,并通过流水线执行该指令。指令一般分为两种类型:访问处理器的寄存器和访问内存空间。抽象命令类型通过抽象命令寄存器配置,抽象指令访问处理器寄存器时,寄存器索引值通过抽象命令寄存器配置,寄存器数据通过抽象数据寄存器配置或者返回。抽象指令访问内存空间时,地址和数据均通过不同的抽象数据寄存器配置或者返回。

[0015]

本发明的上述技术方案相比现有技术具有以下优点:本发明所述的基于处理器调试架构的指令可编程缓冲区设计系统,通过在处理器调试架构的调试模块中增加上述三种指令可编程缓冲区的设计,软件调试人员可以更加快速灵活地编辑指令或者一段程序,并下载至处理器核执行,然后观察执行结果。也可以快速地让处理器执行一些固定的指令,来实现对处理器寄存器或者内存空间的访问。该指令可编程缓冲区的设计覆盖了大多数的功能调试场景,具有结构简单、操作简易、灵活性高的特点。

附图说明

[0016]

为了使本发明的内容更容易被清楚的理解,下面根据本发明的具体实施例并结合附图,对本发明作进一步详细的说明。

[0017]

图1为本发明处理器调试架构框图;

[0018]

图2为本发明调试接口模块jtag状态跳转示意图;

[0019]

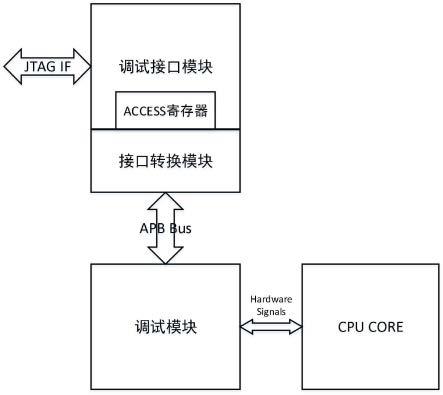

图3为本发明调试模块的指令可编程缓冲区结构图。

具体实施方式

[0020]

如图1所示的架构框图,本实施例提供一种基于处理器调试架构的指令可编程缓冲区设计系统,所述设计系统中搭建的处理器核系统为本技术基本框架,服务于指令可编程缓冲区,所述的处理器核系统包括调试接口模块、接口转换模块、调试模块,其中在调试模块的硬件设计中增加指令可编程缓冲区设计,为软件调试人员提供调试模式下下载指令至处理器核执行的途径;

[0021]

调试接口模块实现了符合ieeestd 1149.1-2013协议标准的jtag接口,包含tck、nreset、tms、tdi和tdo五个接口信号。tck、nreset是时钟和复位,tms用于控制器jtag状态机跳转,tdi和tdo分别为串行输入和输出数据。jtag状态跳转如图2所示,一次完整的jtag访问一般分为ir寄存器访问和dr寄存器访问两个阶段,ir寄存器访问用于确定需要访问得目标寄存器的索引,dr寄存器访问则是写入或读出的该目标寄存器的值。

[0022]

1、ir寄存器访问

[0023]

tms信号控制jtag状态机从idle直接跳转至select-ir,capture-ir将上一次访问的ir值从ir寄存器放入扫描链,shift-ir将本次访问的ir值从tdi移位进扫描链,并将上一次访问的ir值通过tdo输出,最后update-ir将本次访问的ir值从扫描链放入ir寄存器。如此实现将需要访问的目标寄存器的索引写入ir寄存器,也就是确定了需要访问哪个目标寄存器。

[0024]

2、dr寄存器访问

[0025]

tms信号控制jtag状态机跳转至select-dr,capture-dr将上一次访问的dr值从dr寄存器放入扫描链,shift-dr将本次访问的dr值移位进扫描链,并将上一次访问的dr值通过tdo输出,最后update-dr将本次访问的dr值从扫描链放入dr寄存器。如此实现对目标寄存器的读写数据的处理,写数据从tdi输入并写入目标寄存器,读数据在下一次shift-dr阶段从tdo输出。

[0026]

调试接口模块的access寄存器位域,包含16位地址address、32位数据data和2位操作类型op。接口转换模块将access寄存器的值转换成相应的apb总线访问操作并访问调试模块寄存器,apb访问的地址和数据由address和data决定,操作类型op分为读、写和无操作,调试接口模块的access寄存器位域如下表所示:

[0027][0028]

一般来说,处理器的五级流水线处理系统包括取指、译码、执行、访存及写回阶段。在调试模式下,处理器的流水线处于暂停状态,此时将想要执行的指令通过可编程缓冲区直接下载至取指阶段的指令缓存队列,然后拉高有效信号,就可以实现单独执行该调试指令。三种指令可编程缓冲区的实现形式不同,但都可以实现将软件调试人员想要执行的指令下载至取指队列中,如图3所示。

[0029]

1、调试模块的指令传输itr寄存器

[0030]

调试模式下,向itr寄存器写入想要执行的指令,调试模块会直接将该指令下载至处理器流水线的取指缓存队列,然后通过流水线执行该指令。调试模块的itr寄存器位域如下表所示,包含32位指令itr。

[0031][0032]

2、调试模块的程序缓冲pb[0:15]寄存器组

[0033]

调试模式下,预先将想要执行的一段程序(不超过16条指令)写入pb[0:15]寄存器组,pb寄存器位域如下表所示,包含32位指令data。

[0034][0035]

然后配置指令长度位通知硬件想要执行的指令数,指令长度位位于调试模块的抽象命令控制和状态寄存器,其位域如下表所示,包含5位指令数progbufsize。

[0036][0037]

最后配置执行位。调试模块会按照配置的指令数逐条将程序缓冲寄存器组中的指令下载至流水线执行。程序缓冲的执行位位于抽象命令寄存器,其位域如下表所示,control包含程序缓冲的执行位。

[0038][0039]

3、调试模块的抽象命令

[0040]

抽象命令通过配置抽象命令cmd寄存器和抽象数据data[0:n]寄存器组。让调试模块自动产生处理器可执行的固定格式指令,然后下载至处理器流水线的取指缓存队列,并通过流水线执行该指令。

[0041]

抽象命令的指令类型由cmdtype决定,如表5所示。一般分为访问处理器的寄存器和访问内存空间。当抽象指令访问处理器寄存器时,寄存器索引值通过control位域配置,寄存器数据通过抽象数据寄存器data0配置或者返回。抽象指令访问内存空间时,地址和数据通过抽象数据寄存器data0和data1配置或者返回,如下表所示。

[0042][0043]

最后,通过调试模块中三种指令可编程缓冲区的设计,软件调试人员可以更加方便快捷地让处理器在调试模式下运行特定的指令,从而调试软硬件功能。这三种设计可以单独使用,也可以相互配合使用。指令传输itr寄存器单独使用类似于单步调试;程序缓冲寄存器组和抽象命令可以配合使用,比如program buffer中运行的一段程序会使用处理器的通用寄存器,那么可使用抽象命令预先配置好通用寄存器值。

[0044]

显然,上述实施例仅仅是为清楚地说明所作的举例,并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。