1.本发明属于电子元器件测试领域,进一步来说涉及平面芯片电感测试领域,具体来说,涉及一种微型平面芯片电感测试定位模块及其制作方法。

背景技术:

2.平面芯片电感平面结构示意图如图1所示。目前,测试芯片电感常见的方法为:选择两端口微带线电路板夹具,微带线末端与转接头相连,夹具转接头与矢量网络分析仪转接头相连。两端微带线匹配阻抗为50ω,与网络分析仪相匹配。需对矢量网络分析仪进行同轴校准后再对电路板夹具去嵌处理,消除电路板夹具的影响。完成校准后将待测件粘合在电路板测试夹具上,再采用金丝键合方式将待测件的两个焊盘分别键合到测试夹具的微带线(镀金层)上,微带线接地处理。进行s参数测试,再由s参数根据公式计算出感量、q值等电性能。胶黏、键合,计算等工序严重影响测试效率。

3.另外一种常见的测试方法为:将探针台、探针与矢量网络分析仪组成测试系统,进行s参数测试,再由s参数导出感量与q值等电性能。这种测试方法省去金丝键合、胶黏等破坏性测试工序,但gsg结构射频探针仅适用于具有接地端平面芯片电感器的测试。只有信号输入端、输出端两个端口,没有接地端的芯片电感不能采用此种测试方式。

4.若采用lcr表及阻抗分析仪进行测试时,虽然可以直接读取出电感的感量、q值等电性能,但现有测试夹具只有测试带引脚的分立电感及smd电感,不能对平面结构芯片电感进行测试。

5.有鉴于此,特提出本发明。

技术实现要素:

6.本发明所要解决的技术问题是:解决现有lcr表或阻抗分析仪不能用于测试平面结构芯片电感的问题。

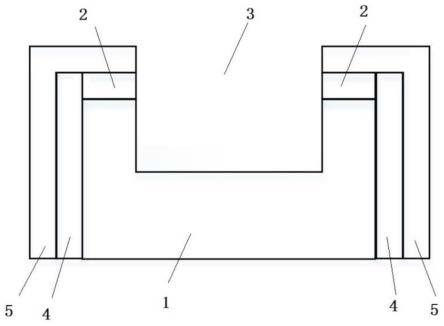

7.本发明提供一种微型平面芯片电感测试定位模块,如图2-图4所示,包括:基片1,表面电极打底层2,定位腔3,端面电极打底层4,电镀层5。

8.所述基片1为低介电常数绝缘基片。绝缘材质可以为但不限于熔融石英玻璃、氧化铝、氮化铝陶瓷等材质。

9.所述表面电极打底层2位于基片1的表面。表面电极打底层2的材料为tiw-au、镍铬-金或其他复合金属层。复合金属层的厚度为200nm-500nm。

10.所述定位腔3位于陶瓷基片1的中部区域,定位腔3的形状与平面芯片电感一致,平面尺寸略大于平面芯片电感,便于平面芯片电感的取放,定位腔3的深度小于陶瓷基片1的厚度,大于平面芯片电感的厚度,便于键合测试引线。

11.所述端面电极打底层4位于基片1对称的两端面(侧面)。端面电极打底层4的材料为tiw-au、镍铬-金或其他复合金属层。复合金属层的厚度为200nm-500nm。

12.所述电镀层5为金电镀层,完全覆盖表面电极打底层2和端面电极打底层4。所述电

镀层5的厚度为5μm-10μm。

13.所述电镀层5顶面经过键合丝与待测件连接,端面经过微带与高频测试夹具连接,高频测试夹具再与lcr表或阻抗分析仪连接。

14.所述定位腔3的长、宽尺寸大于待测件尺寸15μm-30μm,以便芯片电感可以放置于定位腔3内。

15.所述定位腔3的深度大于待测件高度300μm-600μm,以便金丝键合过程金丝长度尽量短(接近直线)的同时,防止金丝接触产品线圈造成断路。

16.表面电极打底层2和表面电镀层5构成表面电极,表面电极的宽度为50μm-100μm。

17.本发明提供一种所述一种微型平面芯片电感测试定位模块的制备方法,包括如下制备工艺:

18.(1)选取双面抛光的低介电常数材质的绝缘基板作基片,绝缘材质可以为但不限于熔融石英玻璃、氧化铝、氮化铝陶瓷等材质。

19.(2)在基片上溅射表面金属打底层。

20.(3)制作掩膜板,掩膜板图形由可以将基板切割为单颗测试定位模块的切割线图形、单颗测试定位模块表面电极图形组成。

21.(4)在基片光刻切割线及表面电极。

22.(5)划片切割为单颗测试定位模块主体。

23.(6)在单颗测试定位模块主体表面的中部区域制作定位腔。

24.单颗测试定位模块主体的长、宽、高尺寸大于定位腔尺寸。定位腔长、宽尺寸略大于待测件尺寸,以便芯片电感可以放置于定位腔内。定位腔深度略大于待测件高度,以便金丝键合过程金丝长度尽量短(接近直线)的同时,防止金丝接触产品线圈造成断路。定位腔使得金电极导体在定位腔处断开,且分割为前、后、左、右对称的金电极导体。

25.(7)采用专利的可以阻挡非溅射区域的溅射夹具,将单颗测试定位模块主体依次置于溅射夹具中,对单颗测试定位模块主体相对的两个侧边溅射金属打底层,两个侧边金属打底层及表面金属打底层连接导通。

26.(8)对两个侧边金属打底层及表面金属打底层镀金,即完成测试定位模块的制作。

27.测试定位模块的表面金电极电用于与芯片电感焊盘进行金丝键合,两个侧边金导体用于连接到与lcr表或阻抗分析仪匹配的高频测试夹具。

28.本发明提供另一种所述一种微型平面芯片电感测试定位模块的制备方法,包括如下制备工艺:

29.(1)选取低介电常数材质的绝缘基板作基片,绝缘材质可以为但不限于氧化铝、氮化铝陶瓷等材质。

30.(2)在基片上按测试定位模块的平面尺寸进行划线,分为若干个单元格备用。

31.(3)制作丝网网版,丝网图形为测试定位模块的表面电极图形。

32.(3)用金浆在基片上印刷电极图形,电极图形为使单颗测试定位模块主体左右贯穿、前后对称的金电极线条。

33.(4)沿基片划线方向分别进行裂片,使其裂为单颗测试定位模块主体。

34.(5)在单颗测试定位模块主体表面中间区域位置制作定位腔。

35.单颗测试定位模块主体的长、宽、高尺寸大于定位腔尺寸。定位腔长、宽尺寸略大

于待测件尺寸,以便芯片电感可以放置于定位腔内。定位腔深度略大于待测件高度,以便金丝键合过程金丝长度尽量短(接近直线)的同时,防止金丝接触产品线圈造成断路。定位腔使得金电极导体在定位腔处断开,且分割为前、后、左、右对称的金电极导体。

36.(6)采用专用的可以阻挡非溅射区域的溅射夹具,将单颗测试定位模块主体依次置于溅射夹具中,对单颗测试定位模块主体相对的两个侧边溅射金属打底层,两个侧边金属打底层及表面金属打底层连接导通。

37.(7)对两个侧边金属打底层及表面金属打底层镀金,即完成测试定位模块的制作。

38.测试定位模块的表面金电极电用于与芯片电感焊盘进行金丝键合,两个侧边金导体用于连接到与lcr表或阻抗分析仪匹配的高频测试夹具。

39.本发明提供一种使用所述微型平面芯片电感测试定位模块的测试方法,包括如下步骤:

40.(1)选定测试参数及高频测试夹具,高频测试夹具包括是德夹具。

41.(2)对lcr表或阻抗分析仪进行开路校准。

42.(3)将测试定位模块表面的两端金电极进行金丝键合使其导通,连接lcr表或阻抗分析仪的高频测试夹具进行短路校准。此方法消除本发明测试定位模块带来的测试误差,起到“清零”作用。

43.(4)校准完成后,取下测试定位模块。

44.(5)将待测件放置于本发明测试定位模块定位腔内,待测件两个焊盘分别与测试定位模块的对应金电极进行金丝键合。

45.(6)将本发明测试定位模块放置于lcr表或阻抗分析仪的高频测试夹具内,对待测件进行电性能测试。

46.与现有技术相比,本发明的有益效果如下:

47.(1)可以连接lcr表及阻抗分析仪附带的高频测试夹具直接读取芯片电感感量、q值等电性能参数,操作简单,无需计算等过程,提高测试效率。

48.(2)不需要价格昂贵的矢量网络分析仪,节约测试成本。

49.(3)测试小感量电感保持较高的测试精度,测试误差<

±

10%,

50.(4)测试芯片电感首先将其置于定位腔内,再采用金丝键合将芯片电感焊盘键合到测试夹具的金层上,可以测量焊盘尺寸<50μm的小尺寸芯片电感。

51.(5)可以测试只有信号输入端、输出端两个端口,没有接地端的平面芯片电感。

52.本发明测试定位模块具有精密定位、重复性高、一致性高、可靠性高等特点,可进行批量性、规模化测试。同样适用于平面型两端口的其他电子器件电性能测试。

附图说明

53.图1为平面芯片电感结构示意图。

54.图2为测试定位模块结构示意图。

55.图3为测试定位模块短路校准状态结构示意图。

56.图4为测试定位模块使用状态结构示意图。

57.图中1为基片,2为表面电极打底层,3为定位腔,4为端面电极打底层,5为电镀层,6为校准电感线,7为待测件,8为待测件测试键合引线。

具体实施方式

58.如图2-图4所示,本发明技术方案的具体实施方式如下:

59.实施例1:所述一种微型平面芯片电感测试定位模块的制备方法如下:

60.(1)选取双面抛光的低介电常数材质的氧化铝绝缘基板作基片。

61.(2)在基片上依次溅射tiw-au复合金属层作为打底层,复合金属层的厚度为200nm-500nm。

62.(3)制作掩膜板(即光刻版),掩膜板图形由可以将基板切割为单颗测试定位模块的切割线图形、单颗测试定位模块表面电极图形组成。

63.(4)匀胶(选用正性光刻胶)。

64.(5)曝光(曝光时间10s-20s)。

65.(6)显影(显影时间1min-2min)。

66.(7)刻蚀(刻蚀时间1min-2min)。使基板上只留下切割线与夹具表面电极。

67.(8)采用切割方式,将基板按照切割线图形切割(切割速度0.6mm/s-1mm/s)为单颗测试定位模块主体。

68.(9)采用刻槽的方式在单颗测试定位模块主体表面中间区域位置制作定位腔。

69.按照切割线进行切割使得单颗测试定位模块主体长、宽、高尺寸大于定位腔长、宽、高1mm-2mm。

70.定位腔的长、宽尺寸大于待测件尺寸15μm-30μm,以便芯片电感可以放置于定位腔内。

71.定位腔深度大于待测件高度300μm-600μm,以便金丝键合过程金丝长度尽量短(接近直线)的同时,防止金丝接触待测件线圈造成断路。

72.定位腔使得金电极导体在定位腔处断开,且分割为前、后、左、右对称的金电极导体,宽度为50μm-100μm。

73.(10)制作专用的可以阻挡非溅射区域的溅射夹具,将单颗测试定位模块主体依次置于溅射夹具中,其中溅射区域为单颗夹具主体两个侧边部分区域,其位置为可以与单颗测试定位模块主体表面金属线条连接导通的位置。其余部分为阻挡溅射部分。

74.(11)对单颗测试定位模块主体左右两个侧边依次溅射tiw-au复合金属层作为打底层,复合金属层厚度为200nm-500nm,高度为单颗测试定位模块主体的高度,宽度与单颗测试定位模块主体表面电极线条宽度相同。

75.(12)通过在金导体电极加镀金的方式,使得左右两个侧边金导体分别与单颗测试定位模块主体表面金电极连接导通,并使表面金导体、和左右两个侧边电极厚度均增加5μm-10μm,即完成本发明单颗测试定位模块的制作。

76.本发明单颗测试定位模块主体表面金电极用于与芯片电感焊盘进行金丝键合,两个侧边金导体用于连接到与lcr表或阻抗分析仪匹配的高频测试夹具。

77.实施例2:所述一种微型平面芯片电感测试定位模块的另一种制备方法如下:

78.(1)选取低介电常数材质的氮化铝绝缘基板作基片。

79.(2)在基片上按测试定位模块的平面尺寸进行划线,分为若干个单元格备用。

80.(3)制作丝网网版,丝网图形为测试定位模块的表面电极图形。

81.(3)用金浆在基片上印刷电极图形,电极图形为使单颗测试定位模块主体左右贯

穿、前后对称的金电极线条,烧结后其宽度为50μm-100μm,厚度约为5μm,长度为单颗测试定位模块主体长度。

82.(4)沿基片划线方向分别进行裂片,使其裂为单颗测试定位模块主体。

83.(5)在单颗测试定位模块主体表面中间区域位置制作定位腔。

84.裂片使得单颗测试定位模块主体的长、宽、高尺寸大于定位腔长、宽、高1mm-2mm。定位腔长、宽尺寸略大于待测件尺寸15μm-30μm,以便芯片电感可以放置于定位腔内。定位腔深度略大于待测件高度约300μm-600μm,以便金丝键合过程金丝长度尽量短(接近直线)的同时,防止金丝接触产品线圈造成断路。定位腔使得金电极导体在定位腔处断开,且分割为前、后、左、右对称的金电极导体。

85.(6)采用专利的可以阻挡非溅射区域的溅射夹具,将单颗测试定位模块主体依次置于溅射夹具中,对单颗测试定位模块主体相对的两个侧边依次溅射tiw-au复合金属层作为打底层,其厚度为200nm-500nm,高度为单颗测试定位模块主体高度,宽度与单颗测试定位模块主体表面电极线条宽度相同。两个侧边金属打底层与表面金属打底层连接导通。

86.(7)通过在金导体电极加镀金的方式,使得左右两个侧边金导体分别与单颗测试定位模块主体表面金电极连接导通,并使左右两个侧边电极厚度均增加5μm-10μm,即完成单颗测试定位模块的制作。

87.本发明测试定位模块表面金电极电用于与芯片电感焊盘进行金丝键合,两个侧边金导体用于连接到与lcr表或阻抗分析仪匹配的高频测试夹具。

88.实施例3:一种使用所述无损平面芯片电感测试组件的测试方法如下:

89.(1)选定16192a(dc-2ghz)、16194a(dc-2ghz)、16197a(dc-3ghz)、16092a(dc-500mhz)等型号是德夹具作为高频测试夹具。

90.(2)对lcr表或阻抗分析仪进行开路校准。

91.(3)将测试定位模块表面的两端金电极进行金丝键合使其导通,将端电极与lcr表或阻抗分析仪高频测试夹具连接进行短路校准。此方法消除本发明测试定位模块带来的测试误差,起到“清零”作用。

92.(4)校准完成后,取下用于校准的测试定位模块。

93.(5)将待测件放置于本发明测试定位模块定位腔内,待测件两个焊盘分别与测试定位模块的对应金电极进行金丝键合,

94.(6)将本发明测试定位模块放置于lcr表或阻抗分析仪的高频测试夹具内进行待测件的电性能测试。测试过程发现,校准时与测试时金丝键合中金丝长度差异带来的感量、q值等测试误差可忽略不计。

95.测试小感量电感能保持较高的测试精度,对于测试标称值为150nh@250mhz,q值标称值为18@250mhz的芯片电感,随机抽测5只感量误差<

±

1%,q值的测试值为18-20,略大于标称值(q值越大损耗越小,通常情况下q值的标称值为电感最小的q值,一般样品测试q值均大于标称值);对测试标称值为2nh@250mhz、5nh@250mhz的芯片电感,随机抽测5只感量误差<

±

10%。

96.由于测试芯片电感首先将其置于测试定位模块定位腔内,再采用金丝键合将芯片电感焊盘键合到测试夹具的金层上,因此可以测量焊盘尺寸<50μm的小尺寸芯片电感。

97.本发明测试定位模块在不放置产品情况下,连接lcr表或阻抗分析仪高频测试夹

具进行短路校准,能够大大减小测试夹具带来的误差。在提高测试精度的同时,也可以使芯片电感在dc-500mhz、dc-2ghz、dc-3ghz频率范围内进行电感量、q值等电性能测试,阻抗分析仪的扫频功能也可以读取芯片电感谐振频率在夹具测试频率范围内的谐振频率点。

98.综上所述,标称值为2nh、5nh、20nh、30nh、150nh规格的芯片电感分别各随机抽测5只样品,采用本发明夹具分别在10mhz、30mhz、100mhz、250mhz、1ghz频率进行电感量、q值测试,在不同频率下测试感量测试精度高,不同频率下测试芯片电感的感量值与仿真值或标称值间的误差<

±

10%。

99.最后应说明的是:上述实施例仅仅是为清楚地说明所作的举例,本发明包括但不限于以上实施例,这里无需也无法对所有的实施方式予以穷举。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。凡符合本发明要求的实施方案均属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。