多柱扫描式电子显微镜系统

1.分案申请的相关信息

2.本技术是申请日为2018年2月2日、申请号为201880015469.9、发明名称为“多柱扫描式电子显微镜系统”的发明专利申请的分案申请。

3.相关申请案的交叉参考

4.本技术案根据35u.s.c.

§

119(e)规定主张名叫罗伯特

·

海恩斯(robert haynes)、阿伦

·

韦尔克(aron welk)及迈赫兰

·

纳塞尔

·

戈德希(mehran nasser ghodsi)的发明者的名称为“柱四极或八极对准、接合及后加工方法(method of column quadrupole or octupole alignment,bonding and post-machining)”的2017年2月3日申请的第62/454,715号美国临时专利申请案及名叫阿伦

·

韦尔克、罗伯特

·

海恩斯、托马斯

·

普勒特(tomas plettner)及约翰

·

吉尔利(john gerling)的发明者的名称为“柱制造及组装(column manufacturing and assembly)”的2017年2月7日申请的第62/455,955号美国临时专利申请案的优先权,所述申请案各自以全文引用的方式并入本文中。

技术领域

5.本发明大体上涉及晶片及光掩模/光罩检验及重检,且更特定来说,本发明涉及一种用于在晶片及光掩模/光罩检验及重检期间使用的多柱扫描式电子显微镜系统的柱组合件。

背景技术:

6.半导体装置(例如逻辑及存储器装置)的制造通常包含:使用大量半导体制造工艺来处理半导体装置以形成半导体装置的各种特征及多个层级。一些制造工艺利用光掩模/光罩来将特征印刷于例如晶片的半导体装置上。随着半导体装置大小变得越来越小,发展增强型检验及重检装置及程序以提高分辨率、速度及晶片及光掩模/光罩检验过程的处理量变得极为重要。

7.一种检验技术包含例如扫描式电子显微术(sem)的基于电子束的检验。在一些例子中,通过将单个电子束分成数个电子束且利用单个电子光学柱个别调谐及扫描所述数个电子束来执行扫描式电子显微术(例如多电子束sem系统)。然而,将电子束分成n个较低电流束通常会降低多电子束sem系统的分辨率,这是因为n个电子束在全局范围内调谐且无法优化个别图像。另外,将电子束分成n个电子束导致需要更多扫描及平均来获得图像,其降低多电子束sem系统的速度及处理量。这些问题随着电子光学柱阵列大小增大而增加。

8.在其它例子中,经由包含增加数目的电子光学柱的sem系统(例如多柱sem系统)执行扫描式电子显微术。通常,这些电子光学柱是金属、陶瓷环及电磁铁的个别堆叠。这些个别堆叠因太大而无法以使晶片、光掩模/光罩扫描速度优化的理想节距放置在一起且无法经小型化以允许在可用面积中堆积大量电子光学柱,从而导致多柱sem系统中的堆叠数目受限制(例如4个堆叠)。另外,具有个别堆叠导致电子光学柱匹配、柱之间的串扰及错误充电的问题。

9.此外,随着电子光学柱变得越来越小,制造个别组件(例如电子光学柱的多极电子束偏转器(例如四极或八极电子束偏转器)元件)时存在大小限制。制造多极电子束偏转器的一种方法包含:在使多极电子束偏转器的极分段及电隔离的金属通孔中制造临界容限透镜孔及径向槽的阵列。随着电子光学柱大小减小,多极电子束偏转器变得更易受可能会使整个元件不可用(其随后降低制造工艺的良率)的制造误差影响。制造多极电子束偏转器的另一方法包含:预先制造多极电子束偏转器的个别极,且接着将个别极接合在一起(个别成对或经由对准夹具)。此方法在制造时间方面是有限制的且归因于个别极的紧密接近而仅限于选择制造方法。另外,此方法易受维持制造容限的误差影响,这是因为容限会受多极电子束偏转器的个别极的相对放置误差影响。此外,在使多极电子束偏转器的个别极对准及接合时维持所要临界容限将需要精确、微小工具加工。此工具加工会在接合过程期间增加大量热质量,且工具加工所需的空间会限制后续电子光学柱间距。

10.因此,将有利地提供克服上述缺点的系统。

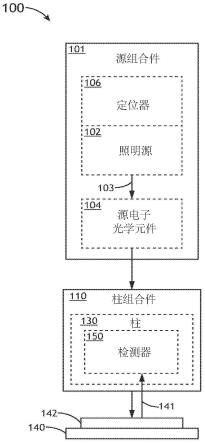

技术实现要素:

11.根据本发明的一或多个实施例,揭示一种衬底阵列。在一个实施例中,所述衬底阵列包含由多个衬底层形成的复合衬底。在另一实施例中,所述复合衬底包含多个孔。在另一实施例中,所述衬底阵列包含嵌入所述多个衬底层内的多个电组件。在另一实施例中,所述衬底阵列包含耦合到所述复合衬底的顶面或底面中的至少一者的至少一个接地接合垫。在另一实施例中,所述衬底阵列包含耦合到所述复合衬底的所述顶面或所述底面中的至少一者的至少一个信号接合垫。在另一实施例中,所述衬底阵列包含多个柱电子光学元件。在另一实施例中,所述多个柱电子光学元件定位于所述复合衬底中的所述多个孔上方。在另一实施例中,所述多个柱电子光学元件中的每一者接合到耦合到所述复合衬底的所述顶面或所述底面中的至少一者的特定接地接合垫及特定信号接合垫。

12.根据本发明的一或多个实施例,揭示一种多柱扫描式电子显微镜(sem)系统。在一个实施例中,所述系统包含柱组合件。在另一实施例中,所述柱组合件包含第一衬底阵列组合件。在另一实施例中,所述柱组合件包含至少一第二衬底阵列组合件。在另一实施例中,所述第一衬底阵列组合件或所述至少一第二衬底阵列组合件中的至少一者包含衬底阵列。在另一实施例中,所述衬底阵列包含由多个衬底层形成的复合衬底。在另一实施例中,所述复合衬底包含多个孔。在另一实施例中,所述衬底阵列包含嵌入所述多个衬底层内的多个电组件。在另一实施例中,所述衬底阵列包含耦合到所述复合衬底的顶面或底面中的至少一者的至少一个接地接合垫。在另一实施例中,所述衬底阵列包含耦合到所述复合衬底的所述顶面或所述底面中的至少一者的至少一个信号接合垫。在另一实施例中,所述衬底阵列包含多个柱电子光学元件。在另一实施例中,所述多个柱电子光学元件定位于所述复合衬底中的所述多个孔上方。在另一实施例中,所述多个柱电子光学元件中的每一者接合到耦合到所述复合衬底的所述顶面或所述底面中的至少一者的特定接地接合垫及特定信号接合垫。

13.在另一实施例中,所述系统包含源组合件。在另一实施例中,所述源组合件包含经配置以产生两个或两个以上电子束的两个或两个以上电子束源。在另一实施例中,所述两个或两个以上电子束源中的每一者经配置以产生电子束。在另一实施例中,所述源组合件

包含两组或两组以上的多个定位器。在另一实施例中,每一组的所述多个定位器经配置以在多个方向上调整所述两个或两个以上照明源的特定照明源的位置。在另一实施例中,所述系统包含经配置以固定样本的载物台。在另一实施例中,所述柱组合件经配置以将所述两个或两个以上电子束的至少一部分引导到所述样本的一部分上。

14.根据本发明的一或多个实施例,揭示一种方法。在一个实施例中,所述方法可包含(但不限于):形成多个衬底阵列。在另一实施例中,形成所述多个衬底阵列的衬底阵列可包含(但不限于):将一或多个组件嵌入多个衬底层内。在另一实施例中,形成所述多个衬底阵列的所述衬底阵列可包含(但不限于):由所述多个衬底层形成复合衬底。在另一实施例中,形成所述多个衬底阵列的所述衬底阵列可包含(但不限于):在所述复合衬底中钻多个孔。在另一实施例中,形成所述多个衬底阵列的所述衬底阵列可包含(但不限于):将至少一个接地接合垫耦合到所述复合衬底的顶面或底面中的至少一者。在另一实施例中,形成所述多个衬底阵列的所述衬底阵列可包含(但不限于):将至少一个信号接合垫耦合到所述复合衬底的所述顶面或所述底面中的至少一者。另一实施例中,形成所述多个衬底阵列的所述衬底阵列可包含(但不限于):将多个柱电子光学元件接合到耦合到所述复合衬底的所述顶面或所述底面中的至少一者的特定接地接合垫及特定信号接合垫。在另一实施例中,所述多个柱电子光学元件中的每一者定位于所述复合衬底中的所述多个孔上方。

15.在另一实施例中,所述方法可包含(但不限于):将所述多个衬底阵列分类成第一衬底阵列组合件及至少一第二衬底阵列组合件。在另一实施例中,所述方法可包含(但不限于):由所述第一衬底阵列组合件及所述至少一第二衬底阵列组合件形成柱组合件。

16.应理解,以上一般描述及以下详细描述两者仅供示范及解释且未必限制本发明。并入本发明中且构成本发明的部分的附图说明本发明的标的物。描述及图式一起用于解释本发明的原理。

附图说明

17.所属领域的技术人员可通过参考附图来较好理解本发明的众多优点,其中:

18.图1是根据本发明的一或多个实施例的配备有柱组合件的多柱扫描式电子显微镜(sem)系统的简化示意图。

19.图2a是根据本发明的一或多个实施例的多柱sem系统的柱组合件的横截面图。

20.图2b是根据本发明的一或多个实施例的柱组合件的衬底阵列。

21.图2c是根据本发明的一或多个实施例的柱组合件的衬底阵列的横截面图。

22.图3a是根据本发明的一或多个实施例的经部分制造多极电子束偏转器的等角视图。

23.图3b是根据本发明的一或多个实施例的经部分制造多极电子束偏转器的仰视图。

24.图3c是根据本发明的一或多个实施例的经部分制造多极电子束偏转器的横截面图。

25.图3d是根据本发明的一或多个实施例的配备有经完全制造多极电子束偏转器的衬底阵列。

26.图4是根据本发明的一或多个实施例的用于制造多柱sem系统的柱组合件的方法。

具体实施方式

27.现将详细参考附图中所说明的揭示标的物。

28.大体上参考图1到4,描述根据本发明的多柱扫描式电子显微镜(sem)系统。

29.本发明的实施例涉及一种多柱sem系统,其包含柱组合件。本发明的额外实施例涉及一种制造柱组合件的方法。本发明的额外实施例涉及用于电子光学柱中的衬底阵列。

30.名叫罗伯特

·

海恩斯等人的发明者的名称为“多柱扫描式电子显微镜系统(multi-column scanning electron microscopy system)”的代理人案号为kla p5068,且美国专利申请号为15/616,749中详细描述多柱扫描式电子显微镜,所述案以全文引用的方式并入本文中。

31.图1说明根据本发明的一或多个实施例的用于执行样本的sem成像的电子光学系统100。在一个实施例中,电子光学系统100是多柱扫描式电子显微镜(sem)系统。尽管本发明主要聚焦于与多柱sem系统相关联的电子光学布置,但本文中应注意,此不表示对本发明的范围的限制,而是仅供说明。另外,本文中应注意,通过本发明所描述的实施例可扩展到任何电子光学系统配置。本文中应进一步注意,本发明中所描述的实施例可扩展到用于显微术及/或成像的任何光学系统配置。

32.在一个实施例中,系统100包含源组合件101。在另一实施例中,源组合件101包含一或多个照明源102。例如,一或多个照明光束源102可包含一或多个电子束源102。通过另一实例,一或多个照明光束源102可包含所属领域中已知的任何照明光束源。在另一实施例中,一或多个电子束源102产生一或多个电子束103且将一或多个电子束103引导到一或多组源电子光学元件104。在另一实施例中,一或多个电子束源102耦合到一或多组定位器106。

33.在另一实施例中,系统100包含具有一或多个电子光学柱130的柱组合件110。在另一实施例中,一或多组源电子光学元件104引导一或多个电子束103通过柱组合件110。

34.在另一实施例中,系统100包含经配置以固定样本142的载物台140。在另一实施例中,柱组合件110将一或多个电子束103引导到样本142的表面。在另一实施例中,柱组合件110包含一或多个电子检测器150,其用于检测响应于电子束103而从样本142的表面发射及/或散射的一或多个电子141。

35.一或多个电子束源102可包含适合于产生一或多个电子束103的所属领域中已知的任何电子束源。例如,一或多个电子束源102可包含用于产生多个电子束103的多个电子束源102,其中每一电子束源102产生电子束103。通过另一实例,一或多个电子束源102可包含产生单个电子束103的单个电子束源102,其中经由一或多个照明源光学组件(例如孔隙阵列)将单个电子束103分成多个电子束103。

36.在另一实施例中,电子束源102包含一或多个电子发射器。例如,一或多个发射器可包含(但不限于)一或多个场发射枪(feg)。例如,一或多个feg可包含(但不限于)一或多个肖特基(schottky)型发射器。应注意,肖特基型发射器的直径可经选择以装配于电子光学柱130的节距间隔内,同时提供足够空隙量来对准电子光学柱130。另外,一或多个feg可包含(但不限于)一或多个碳纳米管(cnt)发射器、一或多个纳米结构碳膜发射器及/或一或多个穆勒(muller)型发射器。通过另一实例,一或多个发射器可包含(但不限于)一或多个光电阴极发射器。通过另一实例,一或多个发射器可包含(但不限于)一或多个硅发射器。

37.在一个实施例中,源组合件101包含用于致动电子束源102的一或多组定位器106。例如,源组合件101可包含多组定位器106,其中每一组定位器106经配置以致动电子束源102。通过另一实例,源组合件101可包含经配置以致动多个电子束源102(例如,经配置以致动全局范围内的多个电子束源102)的单组定位器106。在另一实施例中,一或多组定位器106电耦合到一或多个电子束源102。在另一实施例中,一或多组定位器106机械地耦合到一或多个电子束源102。

38.在另一实施例中,每一组定位器106包含经配置以使电子束源102沿一或多个线性方向(例如x方向、y方向及/或z方向)平移的一或多个定位器106。例如,三个定位器106可经配置以平移电子束源102。例如,三个定位器可包含(但不限于):第一定位器106,其经配置以在x方向上调整电子束源102;第二定位器106,其经配置以在y方向上调整电子束源102;及第三定位器106,其经配置以在z方向上调整电子束源102。本文中应注意,一或多组定位器中的每一者内的定位器的堆叠顺序仅供说明,且不应被理解为对本发明的限制。

39.在一个实施例中,源组合件101包含一或多组源电子光学元件104。例如,源组合件101可包含用于多个电子束103中的每一者的一组源电子光学元件104。在另一实施例中,一或多组源电子光学元件104包含适合于将电子束103的至少一部分聚焦及/或引导到柱组合件110的所属领域中已知的任何电子光学元件。例如,一或多组源电子光学元件104可包含(但不限于)一或多个电子光学透镜(例如一或多个磁聚光透镜及/或一或多个磁聚焦透镜)。通过另一实例,一或多组源电子光学元件104可包含一或多个提取器(或提取器电极)。本文中应注意,一或多个提取器可包含所属领域中已知的任何电子束提取器配置。例如,一或多个提取器可包含一或多个平面提取器。另外,一或多个提取器可包含一或多个非平面提取器。2013年8月20日发布的第8,513,619号美国专利中大体上描述电子束源中的平面及非平面提取器的使用,所述专利以全文引用的方式并入本文中。

40.在另一实施例中,源组合件101不包含任何源电子光学元件104。在此实施例中,一或多个电子束103由定位于柱组合件110的每一电子束柱130内的一或多个柱电子光学元件210聚焦及/或引导。例如,一或多个柱电子光学元件210可包含(但不限于)本文先前所详细描述的一或多个提取器。因此,以上描述不应被解译为对本发明的范围的限制,而是仅为说明。

41.第kla p5068号代理档案中进一步详细描述源组合件101,所述案先前已以其全文并入本文中。

42.在一个实施例中,系统100包含柱组合件110。在另一实施例中,柱组合件110包含一或多个衬底阵列组合件120。在另一实施例中,一或多个衬底阵列组合件120包含一或多个衬底阵列200。在另一实施例中,柱组合件110包含用于电子束103中的每一者的电子光学柱130。在另一实施例中,一或多个电子光学柱130通过将一或多组柱电子光学元件210接合到一或多个衬底阵列200来形成。在另一实施例中,一或多个电子光学柱130将一或多个电子束103的至少一部分引导到样本142的表面。应注意,本文将进一步详细描述柱组合件110、衬底阵列组合件120、电子光学柱130、衬底阵列200及柱电子光学元件210。

43.在一个实施例中,载物台140经配置以固定样本142。在另一实施例中,样本载物台140为可致动载物台。例如,样本载物台140可包含(但不限于)适合于可选择地使样本142沿一或多个线性方向(例如x方向、y方向及/或z方向)平移的一或多个平移载物台。通过另一

实例,样本载物台140可包含(但不限于)适合于选择性地使样本142沿旋转方向旋转的一或多个旋转载物台。通过另一实例,样本载物台140可包含(但不限于)适合于可选择地使样本沿线性方向平移及/或使样本142沿旋转方向旋转的旋转载物台及平移载物台。

44.样本142包含适合于使用电子束显微镜来检验/重检的任何样本。在一个实施例中,样本包含晶片。例如,样本可包含(但不限于)半导体晶片。如通过本发明所使用,术语“晶片”是指由半导体及/或非半导体材料形成的衬底。例如,半导体或半导体材料可包含(但不限于)单晶硅、砷化镓及磷化铟。

45.在另一实施例中,样本142响应于电子束103而发射及/或散射电子141。例如,电子141可为二次电子141及/或反向散射电子141。

46.在一个实施例中,一或多个电子检测器150定位于一或多个电子光学柱130内,使得每一电子光学柱130包含一或多个电子检测器150。一或多个电子检测器150可包含能够检测电子141的所属领域中已知的任何类型的电子检测器组合件。例如,一或多个检测器150可包含(但不限于)一或多个单件式环形二次电子检测器。通过另一实例,一或多个检测器150可包含(但不限于)一或多个多件式环形二次电子检测器。例如,一或多个多件式环形二次电子检测器可包含(但不限于)一或多个二次电子四重阵列、一或多个二次电子八重阵列及类似物。

47.通过另一实例,可使用一或多个微通道板(mcp)来收集及成像电子141。本文中应注意,2008年2月26日发布的第7,335,895号美国专利中大体上描述使用基于mcp的检测器来检测电子,所述专利以全文引用的方式并入本文中。通过另一实例,可使用例如二极管或二极管阵列的一或多个pin或p-n结检测器来收集及成像电子141。通过另一实例,可使用一或多个雪崩光电二极管(apd)来收集及成像电子141。

48.在另一实施例中,系统100包含检验光掩模/光罩而非样本142所需的一或多个组件。

49.在另一实施例中,系统100包含真空组合件以在系统100的操作及/或柱组合件110的维护期间使源组合件101与柱组合件110隔离。就此来说,减少使系统100恢复操作所需的时间量。本文中应注意,2012年1月31日发布的第8,106,358号美国专利中大体上描述使用真空组合件来产生多柱sem系统中的差动泵浦,所述专利以全文引用的方式并入本文中。

50.在另一实施例中,源组合件101包含陶瓷支座以使一或多个电子束源102与系统100的一组相应定位器106及周围结构电及热隔离。

51.在另一实施例中,系统100包含控制器(未展示)。在一个实施例中,控制器通信地耦合到系统100的一或多个组件。例如,控制器可通信地耦合到源组合件101、源组合件101的组件、柱组合件110、一或多个电子光学柱130、一或多个电子光学柱130的组件(例如一或多个柱电子光学元件210)及/或载物台140。就此来说,控制器可指导系统100的任何组件实施本文先前所描述的各种功能中的任何一或多者。例如,控制器可指导耦合到一或多个电子束源102的一或多组定位器106使一或多个电子束源102在x方向、y方向及/或z方向中的一或多者上平移以校正由源组合件101、柱组合件110的组件、柱组合件110、一或多个电子光学柱130、一或多个电子光学柱130的组件(例如一或多个柱电子光学元件210)及/或载物台140的任何组件产生的电子束未对准。

52.在另一实施例中,控制器包含一或多个处理器,其经配置以执行适合于引起一或

多个处理器执行本发明中所描述的一或多个步骤的程序指令。在一个实施例中,控制器的一或多个处理器可与存储器媒体(例如非暂时性存储媒体)通信,所述存储器媒体含有经配置以引起控制器的一或多个处理器实施本发明中所描述的各种步骤的程序指令。

53.图2a说明根据本发明的一或多个实施例的柱组合件110的横截面图。

54.在一个实施例中,柱组合件110包含一或多个衬底阵列组合件120。例如,柱组合件110可包含第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b。在另一实施例中,一或多个衬底阵列组合件120各自包含一或多个衬底阵列200。例如,衬底阵列组合件120可包含衬底阵列200a。通过另一实例,衬底阵列组合件120可包含第一衬底阵列200a及至少一第二衬底阵列200b。在另一实施例中,一或多个衬底阵列组合件200各自包含一或多个孔201。

55.在另一实施例中,一或多个衬底阵列200的顶面及/或底面的至少一部分由金属层遮蔽以防止一或多个衬底阵列200之间、一或多个衬底阵列200与接合到一或多个衬底阵列200的一或多个组件之间及/或接合到一或多个衬底阵列200的一或多个组件之间的错误充电。在另一实施例中,当衬底阵列组合件120包含两个或两个以上衬底阵列200时,一或多个金属遮蔽件212定位于两个或两个以上衬底阵列200之间。例如,一或多个金属遮蔽件212可经配置以防止一或多个衬底阵列组合件120及/或柱组合件110中的一或多个衬底阵列组合件120的组件之间的串扰或错误充电。

56.在另一实施例中,一或多组柱电子光学元件210接合到一或多个孔201上方的衬底阵列200。例如,一或多组柱电子光学元件210中的至少一者可包含一或多个三维柱电子光学元件210。通过另一实例,一或多组柱电子光学元件210可包含(但不限于)一或多个检测器150、一或多个枪多极电子束偏转器、一或多个提取器、一或多个磁聚光透镜、一或多个枪聚光透镜、一或多个阳极、一或多个上电子束偏转器、一或多个下电子束偏转器、一或多个动态聚焦透镜及/或一或多个磁聚焦透镜。应注意,本文将进一步详细描述多极电子束偏转器。

57.在另一实施例中,第一柱电子光学元件210接合到一或多个衬底阵列200中的至少一些的顶面或底面。在另一实施例中,第一及第二柱电子光学元件210分别接合到一或多个衬底阵列200中的至少一些的顶面及底面。

58.本文中应注意,2006年9月19日发布的第7,109,486号美国专利中大体上描述将电子光学元件接合到衬底阵列以形成柱组合件,所述专利以全文引用的方式并入本文中。

59.在另一实施例中,柱组合件110包含一或多个电子光学柱130。例如,柱组合件110可包含第一电子光学柱130a及至少一第二电子光学柱130b。通过另一实例,柱组合件110可包含(但不限于)2个到60个电子光学柱130。在另一实施例中,柱组合件110包含用于一或多个电子束103中的每一者的电子光学柱130。在另一实施例中,一或多个电子光学柱130将电子束103的至少一部分引导到样本142的表面。

60.在另一实施例中,一或多个电子光学柱130由一或多组柱电子光学元件210形成。例如,电子光学柱130可由包含(但不限于)第一元件210a、第二元件210b、第三元件210c及至少一第四元件210d的一组柱电子光学元件210形成。在另一实施例中,电子光学柱130由用于一或多个电子束103中的每一者的一组柱电子光学元件210形成。

61.在代理人案号第kla p5068中进一步详细描述形成一或多个电子光学柱130的一

或多组柱电子光学元件210的顺序及布置,所述案先前已以全文并入本文中。

62.在一个实施例中,将一或多个衬底阵列200分组成第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b。在另一实施例中,在将一或多个衬底阵列200分组成第一衬底阵列组合件120及至少一第二衬底阵列组合件120b之前检验一或多个衬底阵列组合件200的一或多个容限特性。例如,可根据所需容限来检验一或多个衬底阵列200的节距间隔。例如,节距间隔容限可包含一或多个单位数微米特征容限。

63.在一个实施例中,将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一衬底阵列堆叠。在另一实施例中,第一衬底阵列堆叠安装于第一框架中。在另一实施例中,将至少一第二衬底阵列组合件120b的一或多个衬底阵列200布置成至少一第二衬底阵列堆叠。在另一实施例中,至少一第二衬底阵列堆叠安装于至少一第二框架中。在另一实施例中,第一框架及至少一第二框架经耦合以形成柱组合件110。

64.在另一实施例中,当执行将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一衬底阵列堆叠、将至少一第二衬底阵列组合件120b的一或多个衬底阵列200布置成至少一第二衬底阵列堆叠及/或将第一框架及至少一第二框架耦合在一起的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

65.在一个实施例中,将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一接合衬底阵列堆叠。在另一实施例中,将至少一第二衬底阵列组合件120b的一或多个衬底阵列200布置成至少一第二接合衬底阵列堆叠。在另一实施例中,第一接合衬底阵列堆叠及至少一第二接合衬底阵列堆叠经接合以形成柱组合件110。

66.在另一实施例中,当执行将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一接合衬底阵列堆叠、将至少一第二衬底阵列组合件120b的衬底阵列200布置成至少一第二接合衬底阵列堆叠及/或接合第一接合衬底阵列堆叠及至少一第二接合衬底阵列堆叠中的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

67.在一个实施例中,将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一衬底阵列堆叠。在另一实施例中,第一衬底阵列堆叠安装于框架中。在另一实施例中,将至少一第二衬底阵列组合件120b的一或多个衬底阵列200布置成至少一第二衬底阵列堆叠。在另一实施例中,至少一第二衬底阵列堆叠安装于相同框架中。

68.在另一实施例中,当执行将第一衬底阵列组合件120a的一或多个衬底阵列200布置成第一衬底阵列堆叠或将至少一第二衬底阵列组合件120b的一或多个衬底阵列200布置成至少一第二衬底阵列堆叠中的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

69.图2b及2c说明根据本发明的一或多个实施例的一或多个衬底阵列的衬底阵列200。

70.在一个实施例中,衬底阵列200包含具有一或多个孔201的复合层202。在另一实施例中,复合层202由一或多个衬底层形成。例如,复合层202可包含(但不限于)第一衬底层202a、第二衬底层202b及至少一第三衬底层202c。在另一实施例中,一或多个衬底层由共烧

陶瓷制造。在另一实施例中,复合层202由多个衬底层经由制造工艺形成。例如,制造工艺可包含(但不限于):将多个衬底层压合在一起、将多个衬底层烧结在一起及/或经由共烧工艺将多个衬底层结合在一起。

71.在另一实施例中,衬底阵列200包含耦合到复合层202的顶面及/或底面中的一或多者的一或多个电接触层204。例如,衬底阵列200可包含接触层204a,其具有耦合到复合层202的顶面的一或多个电接点。通过另一实例,衬底阵列200可包含接触层204b,其具有耦合到复合层202的底面的一或多个电接点。在另一实施例中,一或多个电接点包含一或多个接地接合垫(例如接地接触垫)。在另一实施例中,一或多个电接点包含一或多个信号接合垫(例如信号接触垫),其中一或多个信号接合垫与一或多个接地接合垫电隔离。

72.在另一实施例中,一或多个接触层204包含金属化涂层或金属板。在另一实施例中,一或多个接触层204经由制造工艺耦合到复合层202的顶面及/或底面。例如,制造工艺可包含(但不限于)压合工艺、烧结工艺、粘合工艺(例如经由环氧树脂结合)、厚膜工艺及/或薄膜工艺。在另一实施例中,一或多个接触层204经配置以防止错误充电及负电子束相互作用。

73.在另一实施例中,复合层202包含嵌入一或多个衬底层内的一或多个电组件206。在另一实施例中,一或多个电组件206包含一或多个接地迹线220、一或多个接地通孔222、一或多个信号迹线230及/或一或多个信号通孔232。在另一实施例中,在形成复合层202之前将一或多个电组件206嵌入多个衬底层内。

74.在另一实施例中,一或多个接地迹线220经由一或多个接地通孔222电耦合到一或多个接触层204中的一或多个接地接合垫。在另一实施例中,一或多个信号迹线230经由一或多个信号通孔232电耦合到一或多个接触层204中的一或多个信号接合垫。

75.本文中应注意,尽管一或多个接地通孔222及一或多个信号通孔232展示于衬底阵列200的相同横截面内,但一或多个接地通孔222及一或多个信号通孔232可经布置使得衬底阵列200的横截面将仅包含一或多个接地通孔222或一或多个信号通孔232。另外,本文中应注意,尽管一或多个接触层204中的一或多个接地接合垫及一或多个信号接合垫两者展示于衬底阵列200的相同横截面中,但一或多个接触层204中的一或多个接地接合垫及一或多个信号接合垫可经布置使得衬底阵列200的横截面将仅包含一或多个接地接合垫或一或多个信号接合垫。因此,以上描述不应被解译为对本发明的范围的限制,而是仅为说明。

76.在另一实施例中,一或多个电组件206电耦合到一或多个电接触垫208。例如,一或多个接地迹线220可电耦合到一或多个接地接触垫208。通过另一实例,一或多个信号迹线230可电耦合到一或多个信号接触垫208。

77.在另一实施例中,一或多个电接触垫208定位于未由接触层204遮蔽的复合层202的顶面及/或底面的一部分(例如衬底阵列200的无遮蔽部分)上。然而,本文中应注意,复合层202的顶面及/或底面的大部分经遮蔽以防止错误充电。

78.在一个实施例中,一或多个柱电子光学元件210接合到衬底阵列200。例如,一或多个柱电子光学元件210可接合到衬底阵列200的顶面及/或底面。通过另一实例,一或多个柱电子光学元件210可接合到耦合到衬底阵列200的顶面或底面的特定接地接合垫及特定信号接合垫。在另一实施例中,一或多个柱电子光学元件210经由接合工艺接合到衬底阵列200。例如,接合工艺可包含(但不限于)焊接工艺、铜焊工艺或粘合工艺(例如,经由环氧树

脂结合)。

79.在另一实施例中,一或多个柱电子光学元件210中的至少一些在接合到衬底阵列200之前被完全制造。在另一实施例中,一或多个柱电子光学元件210中的至少一些在接合到衬底阵列200之前经由第一组制造工艺来部分制造,且在接合到衬底阵列200之后经由一第二组制造工艺来完全制造。应注意,本文中将进一步详细描述第一组制造工艺及第二组制造工艺。

80.在另一实施例中,检验一或多个柱电子光学元件210以满足个别容限。例如,个别容限可包含一或多个单位数微米特征容限。在另一实施例中,一或多个柱电子光学元件210在接合到衬底阵列200时经由对准工艺对准。例如,对准工艺可包含(但不限于)用于使多个光刻目标特征对准的对准工艺或光学叠加对准工艺。

81.图3a到3c说明根据本发明的一或多个实施例的经部分制造多极电子束偏转器210。

82.在一个实施例中,多极电子束偏转器210包含圆筒部分302及圆盘部分306。例如,当多极电子束偏转器210接合到衬底阵列200时,圆筒部分302可插入到衬底阵列200的孔中。

83.在另一实施例中,多极电子束偏转器210包含钻穿圆筒部分302的顶部及圆盘部分306的底部的孔304。例如,孔304可允许电子束103通过多极电子束偏转器210。在另一实施例中,孔304具有一或多个临界容限。例如,一或多个临界容限可包含(但不限于)孔径及/或孔形。

84.在另一实施例中,多极电子束偏转器210包含一或多个狭槽308。例如,一或多个狭槽308可部分切入到多极电子束偏转器210中,使得一或多个狭槽308切穿多极电子束偏转器210的圆筒部分302及圆盘部分306且不延伸到圆盘部分306的边缘。本文中应注意,如果一或多个狭槽308延伸到圆盘部分306的边缘,那么多极电子束偏转器210将被分段成多个个别电子束偏转器极。

85.在另一实施例中,多极电子束偏转器210在圆盘部分306的外部区域上包含凸起区域310。例如,凸起区域310可使圆盘部分306的内部区域从衬底阵列200的顶面或底面偏移等于凸起区域310的高度的距离。在另一实施例中,多极电子束偏转器210在凸起区域310中包含一或多个凹槽312。例如,凸起区域310中的一或多个凹槽312可为一或多个接合后制造工艺的工作区域,其用于确保一或多个接合后制造工艺不损坏衬底阵列200(或以其它方式干扰衬底阵列200的操作)。

86.图3d说明根据本发明的一或多个实施例的接合到衬底阵列200的一组经完全制造多极电子束偏转器。

87.在一个实施例中,一或多个经部分制造多极电子束偏转器210接合到衬底阵列200的接触层204。在另一实施例中,一或多个狭槽308经由切割工艺延伸到一或多个凹槽312处的一或多个经部分制造多极电子束偏转器210的边缘,其中切割工艺将一或多个经部分制造多极电子束偏转器210分段成个别电子束偏转器极210a以因此完全制造一或多个多极电子束偏转器210。例如,一或多个经部分制造多极电子束偏转器210可包含(但不限于)2个到12个狭槽308,其在延伸到多极电子束偏转器210的边缘时将经部分制造多极电子束偏转器210分段成4个到24个个别电子束偏转器极(例如导致四极电子束偏转器、八极电子束偏转

器及类似物)以完全制造一或多个多极电子束偏转器210。

88.本发明的实施例的优点包含以减小节距间隔及更严格容限制造及对准多柱sem系统。本发明的优点还包含通过检验衬底阵列且基于检验结果将衬底阵列分类来形成更佳匹配衬底阵列组合件。本发明的优点还包含通过以下操作来提高所制造的电子光学元件的良率:经由第一组制造工艺部分制造电子光学元件;检验经部分制造的电子光学元件;基于检验结果来将经部分制造的电子光学元件分类到匹配组;使经部分制造电子光学元件的匹配组对准、将经部分制造的电子光学元件接合到衬底阵列;及经由第二组制造工艺完全制造经接合的电子光学元件。本发明的优点还包含防止充电及减少多个电子光学柱波束信号之间的串扰。

89.图4说明描绘用于制造多柱sem系统100的柱组合件110的方法400的工艺流程图。方法还可包含可由本文所描述的输出获取子系统及/或(若干)计算机子系统或系统执行的任何其它步骤。

90.在步骤402中,形成一或多个衬底阵列200。在一个实施例中,形成一或多个衬底阵列200包含:将一或多个电组件206嵌入一或多个衬底层202内,其中一或多个衬底层202中的至少一些由共烧陶瓷制成。在另一实施例中,一或多个电组件206包含一或多个接地迹线220、一或多个信号迹线230、一或多个接地通孔222及/或一或多个信号通孔232。

91.在另一实施例中,形成一或多个衬底阵列200包含:由多个衬底层形成复合衬底202。例如,由衬底层形成复合衬底可包含(但不限于):将衬底层压合在一起、将衬底层烧结在一起或经由共烧工艺将衬底层结合在一起。在另一实施例中,形成一或多个衬底阵列200包含:在复合衬底202中钻多个孔201。

92.在另一实施例中,形成一或多个衬底阵列200包含:将一或多个接触层204耦合到复合衬底202的顶面或底面中的至少一者,其中一或多个接触层204包含金属化涂层及/或金属板。例如,耦合一或多个接触层204可包含压合工艺、烧结工艺、粘合工艺、厚膜工艺及/或薄膜工艺。例如,粘合工艺可为(但不限于)使用环氧树脂结合。在另一实施例中,一或多个接触层204包含一或多个接地接合垫。例如,可经由一或多个接地通孔222将一或多个接地迹线220电耦合到一或多个接地接合垫。在另一实施例中,接触层204包含一或多个信号接合垫,其中一或多个信号接合垫与一或多个接地接合垫电隔离。例如,可经由一或多个信号通孔232将一或多个信号迹线230电耦合到一或多个信号接合垫。

93.在另一实施例中,形成一或多个衬底阵列200包含:将一或多个柱电子光学元件210中的每一者定位于复合衬底202中的孔201上方。在另一实施例中,形成一或多个衬底阵列200包含:将一或多个柱电子光学元件210接合到耦合到复合衬底202的顶面或底面中的至少一者的一或多个接地接合垫的特定接地接合垫及一或多个信号接合垫的特定信号接合垫。例如,将一或多个柱电子光学元件210中的每一者接合到特定接地接合垫及特定信号接合垫可包含(但不限于)焊接工艺、铜焊工艺或粘合工艺(例如,经由环氧树脂结合)。通过另一实例,将一或多个柱电子光学元件210中的每一者接合到特定接地接合垫及特定信号接合垫可包含对准工艺,例如(但不限于)用于使多个光刻目标特征对准的对准工艺或光学叠加对准工艺。

94.在另一实施例中,柱电子光学元件210中的至少一些在接合到特定接地接合垫及特定信号接合垫之前被完全制造。在另一实施例中,柱电子光学元件210中的至少一些(例

如多极电子束偏转器210)在将柱电子光学元件210中的至少一些接合到特定接地接合垫及特定信号接合垫之前经由第一组制造工艺部分制造,且在将柱电子光学元件210中的至少一些接合到特定接地接合垫及特定信号接合垫之后经由第二组制造工艺完全制造。

95.例如,第一组制造工艺可包含:在柱电子光学元件210中基于一或多个临界容限(例如孔径及/或孔形)来钻孔304,且在柱电子光学元件210中切割一或多个狭槽308。例如,一或多个狭槽308可包含第一狭槽308及至少一第二狭槽308。另外,第一狭槽308及至少一第二狭槽308可穿过孔304的一部分。此外,第一狭槽308及至少一第二狭槽308可不延伸到柱电子光学元件210的边缘。通过另一实例,第二组制造工艺可包含:切割延伸到柱电子光学元件210的边缘的一或多个狭槽308,使得柱电子光学元件210被分段成一或多个电子束偏转器极(例如,2个到12个狭槽将柱电子光学元件210分段成4个到24个电子束偏转器极)。

96.在步骤404中,将所形成的衬底阵列200分类成第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b。在一个实施例中,在将所形成的衬底阵列200分类成第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b之前检验所形成的衬底阵列200。在另一实施例中,所形成的衬底阵列200的分类是基于检验结果。

97.在步骤406中,由第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b形成柱组合件110。在一个实施例中,柱组合件110包含由接合到第一衬底阵列组合件120a及至少一第二衬底阵列组合件120b的一或多个衬底阵列200的一或多个柱电子光学元件210形成的一或多个电子光学柱130,如本文先前所描述。

98.在一个实施例中,形成柱组合件110包含:将第一衬底阵列组合件120a布置成第一衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:将第一衬底阵列堆叠安装于第一框架中。在另一实施例中,形成柱组合件110包含:将至少一第二衬底阵列组合件120b布置成至少一第二衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:将至少一第二衬底阵列组合件安装于至少一第二框架中。在另一实施例中,形成柱组合件110包含:耦合第一框架及至少一第二框架。在另一实施例中,当执行布置第一衬底阵列组合件120a、布置至少一第二衬底阵列组合件120b或耦合第一框架及至少一第二框架中的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

99.在一个实施例中,形成柱组合件110包含:将第一衬底阵列组合件120a布置成第一接合衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:将至少一第二衬底阵列组合件120b布置成至少一第二接合衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:接合第一接合衬底阵列堆叠及至少一第二接合衬底阵列堆叠。在另一实施例中,当执行布置第一衬底阵列组合件120a、布置至少一第二衬底阵列组合件120b或接合第一接合衬底阵列堆叠及至少一第二接合衬底阵列堆叠中的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

100.在一个实施例中,形成柱组合件110包含:将第一衬底阵列组合件120a布置成第一衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:将第一衬底阵列堆叠安装于框架中。在另一实施例中,形成柱组合件100包含:将至少一第二衬底阵列组合件120b布置成至少一第二衬底阵列堆叠。在另一实施例中,形成柱组合件110包含:将至少一第二衬底阵列

组合件安装于相同框架中。在另一实施例中,当执行布置第一衬底阵列组合件120a或布置至少一第二衬底阵列组合件120b中的至少一者时,经由最小平方最适对准工艺减小一或多个对准误差。例如,一或多个对准误差可包含(但不限于)x方向上的偏移距离、y方向上的偏移距离及/或偏移旋转角。

101.所属领域的技术人员将认识到,本文所描述的组件(例如操作)、装置、对象及其伴随讨论是用作为用于使概念清楚的实例且可预期各种配置修改。因此,如本文所使用,所陈述的特定范例及其伴随讨论希望表示其更一般类别。一般来说,所使用的任何特定范例希望表示其类别,且不包含的特定组件(例如操作)、装置及对象不应被视为限制。

102.关于本文所使用的基本上任何复数及/或单数项,所属领域的技术人员可根据上下文及/或应用将复数转化为单数及/或将单数转化为复数。为清楚起见,本文未明确陈述各种单数/复数排列。

103.本文所描述的标的物有时说明含于不同其它组件内或与不同其它组件连接的不同组件。应理解,所描绘的此类架构仅供例示,且事实上可实施实现相同功能性的许多其它架构。就概念来说,用于实现相同功能性的任何组件布置经有效“相关联”使得实现所要功能性。因此,本文中经组合以实现特定功能性的任何两个组件可被视为彼此“相关联”使得实现所要功能性,不管架构或中间组件如何。同样地,如此相关联的任何两个组件也可被视为彼此“可操作连接”或“可操作耦合”以实现所要功能性,且能够如此相关联的任何两个组件也可被视为彼此“可操作耦合”以实现所要功能性。可操作耦合的特定实例包含(但不限于)可物理配合及/或物理相互作用组件及/或可无线相互作用及/或无线相互作用组件及/或逻辑相互作用及/或可逻辑相互作用组件。

104.在一些例子中,一或多个组件在本文中可被认为是“经配置以

…”

、“可经配置以

…”

、“可操作/经操作以

…”

、“经调适/可调适”、“能够

…”

、“可与/与

…

等形”等等。所属领域的技术人员将认识到,除非上下文另有要求,否则此类术语(例如“经配置以

…”

)一般可涵盖有源状态组件及/或非有源状态组件及/或备用状态组件。

105.尽管已展示及描述本文所描述的本发明标的物的特定方面,但所属领域的技术人员应明白,基于本文的教示,可在不背离本文所描述的标的物及其更广泛方面的情况下进行改变及修改,因此,所附权利要求书将落于本文所描述的标的物的真实精神及范围内的所有此类改变及修改涵盖于其范围内。所属领域的技术人员应理解,一般来说,本文及尤其是所附权利要求书(例如所附权利要求书的主体)中所使用的术语一般希望为“开放式”术语(例如,术语“包含”应被解译为“包含(但不限于)”,术语“具有”应被解译为“至少具有”,等等)。所属领域的技术人员应进一步理解,如果想要引入权利要求叙述的特定数目,那么此意图要明确叙述于权利要求中,且如果无此叙述,那么不存在此意图。例如,为助于理解,以下所附权利要求书可含有使用引入式词组“至少一”及“一或多个”来引入权利要求叙述。然而,使用此类词组不应被解释为隐含由不定冠词“一(a/an)”引入的权利要求叙述使含有此引入权利要求叙述的任何特定权利要求仅限为含有唯一此叙述的权利要求,即使相同权利要求包含引入式词组“一或多个”或“至少一”及例如“一”的不定冠词(例如,“一”通常应被解译为意味着“至少一”或“一或多个”);此同样适用于用于引入权利要求叙述的定冠词的使用。另外,即使明确叙述引入权利要求叙述的特定数目,但所属领域的技术人员将认识到,此叙述通常应被解译为意味着至少叙述数目(例如无其它修饰词的“两个叙述”的裸叙

述通常意味着至少两个叙述或两个或两个以上叙述)。此外,在其中使用类似于“a、b及c等等中的至少一者”的惯用表达的例子中,此结构一般希望为所属领域的技术人员所理解的惯用意义(例如,“具有a、b及c中的至少一者的系统”将包含(但不限于)仅具有a的系统、仅具有b的系统、仅具有c的系统、同时具有a及b的系统、同时具有a及c的系统、同时具有b及c的系统及/或同时具有a、b及c的系统等等)。在其中使用类似于“a、b或c等等中的至少一者”的惯用表达的例子中,此结构一般希望为所属领域的技术人员所理解的惯用意义(例如,“具有a、b或c中的至少一者的系统”将包含(但不限于)仅具有a的系统、仅具有b的系统、仅具有c的系统、同时具有a及b的系统、同时具有a及c的系统、同时具有b及c的系统及/或同时具有a、b及c的系统等等)。所属领域的技术人员应进一步理解,除非上下文另有指示,否则无论在具体实施方式、权利要求书或图式中,呈现两个或两个以上替代项的转折连词及/或词组通常应被理解为涵盖包含所述项中的一者、所述项中的任一者或两个项的可能性。例如,词组“a或b”通常将被理解为包含“a”或“b”或“a及b”的可能性。

106.关于所附权利要求书,所属领域的技术人员应了解,一般可以任何顺序执行权利要求书中的叙述操作。另外,尽管以(若干)序列呈现各种操作流程,但应理解,可以除说明顺序之外的其它顺序执行各种操作或可同时执行各种操作。除非上下文另有指示,否则此类替代排序的实例可包含重叠、交错、中断、重新排序、递增、预备、补充、同时、反向或其它变型排序。此外,除非上下文另有指示,否则如“响应于”、“涉及”或其它过去式形容词的术语一般不希望排除此类变型。

107.据信,本发明及其许多伴随优点将通过以上描述来理解,且应明白,可在不背离所揭示的标的物或不牺牲其所有材料优点的情况下对组件的形式、构造及布置作出各种改变。所描述的形式仅供说明,且所附权利要求书希望涵盖及包含此类改变。因此,本发明的范围应仅受限于其所附权利要求书。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。