一种基于dsp内部总线接口的处理系统

技术领域

1.本实用新型涉及dsp内核及内部总线接口技术领域,具体涉及一种基于dsp内部总线接口的处理系统。

背景技术:

2.随着科学技术的不断推进,用户对业务处理能力的要求也逐渐提高,为顺应用户需求,作为数字信号处理的核心数字信号处理器dsp得到了快速的发展和应用。

3.现有技术中,dsp处理器大多只能在某一时刻进行数据的接收和发送,致使总线的传输带宽利用率变低,为了克服利用率低的现象常采用添加辅助通道的形式,然而这些接口的速率不高,从而并不能有效满足现有信号处理的需求。

技术实现要素:

4.实用新型目的:针对现有技术中对信号处理的需求,提出一种基于dsp内部总线接口的处理系统 ,通过内部指令缓存模块和数据内存模块,访问所有硬件处理线程,以及从外部访问资源。另外,通过高速总线接口完成与外部加速器的实时通信,实现对加速器的实时控制,与加速器的耦合实现数据的有效传输,提高传输效率。

5.技术方案:一种基于dsp内部总线接口的处理系统 ,用于访问硬件处理线程和与外部部件的相互协调,该处理系统包括:数据接收模块、环状总线模块、dsp处理器核模块。

6.具体的,数据接收模块,与外部数据传输接口连接,用于接收外部数据传输接口传输过来的地址和数据信息;环状总线模块,通过axi总线协议与所述数据接收模块进行通信连接,用于根据数据接收模块接收到的地址高位选择dsp处理器核模块;dsp处理器核模块,通过注册指令与所述环状总线模块连接,用于接收环状总线模块传输的数据,选择数据通路,以及生成片选信号与外部部件进行通信。

7.在进一步的实施例中,环状总线模块进一步包括:地址选择模块,用于根据所述数据接收模块接收到的地址高位选择对应编号的dsp处理器核模块;第一环状总线接口,与所述地址选择模块连接,用于传输对应的数据至所述dsp处理器核模块;第一数据存储模块,与所述地址选择模块和第一环状总线接口连接,用于对接收到的数据信息进行缓存。

8.dsp处理器核模块具体包括:第二环状总线接口,与第一环状总线接口连接,用于进行数据传输;第二数据缓存模块,与第二环状总线接口连接,用于缓存第二环状总线接口传输过来的数据信息; dsp-im处理模块,与所述第二环状总线接口连接,用于根据所述数据接收模块接收到的地址低位进行通路的选择;dsp-core处理模块,与dsp-im处理模块连接,用于根据缓存指令进行指令以及数据的缓存;l1 mem缓存模块,与dsp-im处理模块和dsp-core处理模块连接,用于根据地址低位存储传输过来的数据信息;h bus总线模块,与所述第二数据缓存模块连接,用于根据接收到的地址低位生成片选信号与外部部件进行通信。

9.在进一步的实施例中,h bus总线模块包括:第三数据缓存模块,与第二数据缓存

模块连接,用于进行数据的读取过程中的缓存;信号生成模块,与第三数据缓存模块连接,用于根据接收到的地址低位生成所需的片选信号,并根据片选信号选择对应的外部加速器。

10.其中,第三数据缓存模块包括两个同步fifo模块,所述fifo模块深度为4,用于支持四线程同时访问加速器。

11.h bus总线模块与加速器通过9个时钟周期进行数据交互,采用直接读取或dam读取的连接交互方式进行通信。

12.有益效果:本实用新型基于多线程、低功耗的定点dsp处理器,具备四个独立的硬件线程,一方面,通过内部指令缓存模块和数据内存模块,访问所有硬件处理线程,以及从外部访问资源。另一方面通过高速总线接口完成与外部加速器的实时通信,实现对加速器的实时控制。

附图说明

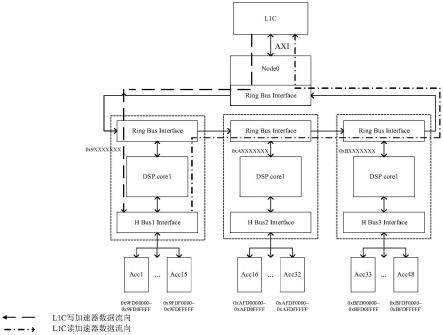

13.图1是本实用新型其中一实施例的处理系统组成简图。

14.图2是本实用新型其中一实施例的处理系统组成框图。

具体实施方式

15.在下文的描述中,给出了大量具体的细节以便提供对本实用新型更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本实用新型可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本实用新型发生混淆,对于本领域公知的一些技术特征未进行描述。附图中涉及到的英文字符释义如下:ring bus表示总线、reg表示register寄存器、dsp-im表示dsp internal bus mux内部数据选择器、fifo表示first in first out先进先出队列、interface表示接口、clk表示时钟信号、data in表示数据输入、i2c表示i2c总线、spi表示串行外设接口、psd表示数据交换接口、acc表示加速器。

16.本实施例基于一款多线程、低功耗的定点dsp处理器,提出一种基于dsp内部总线接口的处理系统,用于实现对所有硬件处理线程的访问,以及与加速器的实施通信,完成对加速器的实时控制。

17.具体的,本实施例提出的处理系统包括:数据接收模块、环状总线模块、dsp处理器核模块。其中在数据交互的过程中,数据接收模块,与外部数据传输接口连接,接收外部数据传输接口传输过来的地址和数据信息,环状总线模块,与数据接收模块连接,用于根据数据接收模块接收到的地址高位选择dsp处理器核模块;dsp处理器核模块,与环状总线模块连接,用于接收环状总线模块传输的数据,并根据接收到的数据选择数据通路,以及生成片选信号,从而与外部部件进行通信。

18.在进一步的实施例中,数据接收模块通过axi总线协议与环状总线模块连接,将接收到的数据传输至环状总线模块中。环状总线模块进一步包括:地址选择模块、第一环状总线接口和第一数据存储模块。

19.其中,地址选择模块,用于根据数据接收模块接收到的地址高位选择对应编号的dsp处理器核模块;第一环状总线接口,与地址选择模块连接,用于传输对应的数据至所述dsp处理器核模块;第一数据存储模块,与地址选择模块和第一环状总线接口连接,用于对

接收到的数据信息进行缓存。

20.在进一步的实施例中,dsp处理器核模块通过注册指令与环状总线模块进行通信连接,具体包括:第二环状总线接口、第二数据缓存模块、dsp-im处理模块、dsp-core处理模块、l1 mem缓存模块和h bus总线模块。其中,第二环状总线接口,与第一环状总线接口连接,用于进行数据传输;第二数据缓存模块,与第二环状总线接口连接,用于缓存第二环状总线接口传输过来的数据信息;dsp-im处理模块,与所述第二环状总线接口连接,用于根据所述数据接收模块接收到的地址低位进行通路的选择;dsp-core处理模块,与dsp-im处理模块连接,用于根据缓存指令进行指令以及数据的缓存;l1 mem缓存模块,与dsp-im处理模块和dsp-core处理模块连接,用于根据地址低位存储传输过来的数据信息;h bus总线模块,与第二数据缓存模块连接,用于根据接收到的地址低位生成片选信号与外部部件进行通信。

21.在进一步的实施例中,h bus总线模块包括:第三数据缓存模块,与第二数据缓存模块连接,用于进行数据的读取过程中的缓存;信号生成模块,与第三数据缓存模块连接,用于根据接收到的地址低位生成所需的片选信号,并根据片选信号选择对应的外部加速器。

22.其中,第三数据缓存模块包括两个同步fifo模块,fifo模块深度为4,用于支持四线程同时访问加速器。

23.h bus总线模块与加速器通过9个时钟周期进行数据交互,并采用直接读取或dam读取的连接交互方式进行通信。

24.优选实施例中,本新型提出的处理系统在数据处理的过程中涉及到的结构如图1所示。其中,l1c表示发出地址和数据信息的外部部件,与本新型的数据接收模块连接,在接收到相应的地址和数据信息后,环状总线模块根据地址高位选择对应的dsp处理器核模块,具体的,地址0x9开头选择node1地址空间,地址0xa开头选择node2的地址空间,地址0xb开头选择node3地址空间。完成dsp处理器核模块的选择后,将对应的数据传输至dsp处理器核模块中的dsp-core处理模块中,随后采用dsp-im处理模块根据地址进行路由选择,具体的,地址低32位为0x00000~0x3ffff则数据将先路由到dsp内部的l1 memory,然后再通过h bus总线模块控制外部挂载的加速器;当地址超过这个范围则直接通过h bus总线模块控制外部挂载的加速器。

25.其中,如图2所示,h bus总线模块即h bus1(high performance bus)interface根据接收到的地址范围生成不同的片选信号,片选信号ce共16bit,每一位可以片选一个加速器,因此实施例在具备3个dsp处理器核模块时,最多可以挂载16个加速器。

26.每个dsp处理器核模块都有独立的h bus总线模块,其中的信号生成模块,根据地址范围生成不同的片选信号,片选信号ce共16bit,每一位可以片选一个对应的加速器,因此最多可以挂载16个加速器。

27.h bus工作频率为dsp的二分之一。dsp通过加载存储指令,将addr地址信息传给dsp internal bus mux,数据由h bus与外接加速器交互,h bus通过load指令读取数据,通过store指令写入数据。h bus包含两个同步fifo,fifo的深度均为4,可支持四线程同时访问加速器,通过h bus内核与加速器之间的数据交互时间为9个时钟周期。在内核工作频率为1ghz的条件下,h bus支持最大传输速率可达16gbps。

28.在进一步的实施例中,h bus总线模块与加速器之间的通信模式有两种,分别为直接读取和dma读取:直接读取模式下,dsp内核直接通过load/store指令对加速器进行数据读写和寄存器控制;在dma读取模式下,dsp内核通过线程dma直接存储器访问实现对加速器的数据空间和寄存器的读写。

29.综上,本实施例提出的处理系统通过与加速器的连接,可以在实现实时通信的前提下完成对加速器的实时控制。

30.如上所述,尽管参照特定的优选实施例已经表示和表述了本实用新型,但其不得解释为对本实用新型自身的限制。在不脱离所附权利要求定义的本实用新型的精神和范围前提下,可对其在形式上和细节上做出各种变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。