1.本技术涉及计算机系统,尤其涉及一种内存模组、内存总线信号处理方法和计算机系统。

背景技术:

2.双倍速率同步动态随机存储存储器(double data rate synchronous dynamicrandom access memory,ddr sdram)标准的产品已经广泛应用于计算机系统中。目前ddr sdram标准已经演进到ddr5标准,数据率最高到6400兆传输每秒 (mega-transfer per second,mt/s)。

3.ddr5标准的内存颗粒产品的推出进度慢于支持ddr5标准的处理器产品的推出速度。例如现在已有支持ddr5标准的处理器产品的内存总线支持数据率最高 6400mt/s的信号,但是ddr5标准的内存颗粒目前只支持最高3200mt/s的信号。这样的内存颗粒无法在计算机系统中充分发挥处理器的内存总线的性能优势。

技术实现要素:

4.本技术公开了一种内存模组、内存总线信号处理方法和计算机系统。通过处理器的内存总线的信号转换成内存颗粒的内存总线上的信号,可以有效解决内存颗粒的内存总线支持的信号和处理器的内存总线支持的信号的最高数据率不匹配的问题。

5.第一方面,提供了一种内存模组,内存模组包括:缓冲器、多个内存颗粒;

6.缓冲器以第一内存总线连接到处理器,同时以第二内存总线连接到多个内存颗粒,其中,第一内存总线和第二内存总线支持相同的标准;

7.缓冲器用于将第一内存总线上的信号转换成第二内存总线上的信号,其中,第一内存总线上的信号的数据率和第二内存总线上的信号的数据率不同。

8.支持同等数据率规格的内存颗粒开发进度慢于处理器,通过该技术方案,可以将不同数据率规格的内存颗粒和处理器集成到一个计算机系统中。

9.一种可能的实现方式中,缓冲器以第一内存总线连接到处理器包括:

10.缓冲器以第一内存总线连接到处理器的单个内存控制器。

11.一种可能的实现方式中,第二内存总线包括多个子总线,多个子总线中的任意两个子总线用于连接不同内存颗粒;

12.多个子总线中任意子总线上信号的数据率和第一内存总线上信号的数据率都不同。

13.一种可能的实现方式中,第一内存总线上的信号的数据率为第二内存总线中所有子总线上的信号的数据率之和。缓冲器两侧的内存总线上信号的数据率之和相等,可以保证计算机系统中处理器到内存颗粒的内存总线的数据传输没有瓶颈。

14.一种可能的实现方式中,内存模组还包括印制电路板;

15.印制电路板上有多组焊盘,每组焊盘与一个子总线连接;

16.多组焊盘中的至少一组焊盘上没有焊接内存颗粒,以及多组焊盘中的至少一组焊盘焊接有内存颗粒。

17.通过该技术方案,可以在共用同一个印制电路板的情况下,开发不同规格的内存模组,降低内存模组的整体成本。

18.一种可能的实现方式中,多个子总线包括:第一子总线和第二子总线;

19.第一子总线上信号的数据率高于第二子总线上信号的数据率。

20.一种可能的实现方式中,

21.与第一子总线连接的内存颗粒用于存储访问频率高于阈值的数据;或,

22.与第二子总线连接的内存颗粒用于存储访问频率低于阈值的数据。

23.通过该技术方案,可以让访问频率高的数据,能够更快的读取和写入。针对访问频率低的数据,使用低规格的内存颗粒,可以降低内存模组的整体成本。

24.一种可能的实现方式中,缓冲器包括:数据缓冲器和/或寄存器时钟驱动器。

25.第二方面,提供了一种内存总线信号处理方法,方法包括:获取第一内存总线上的信号,将第一内存总线上的信号转换成第二内存总线上的信号;

26.第一内存总线上的信号和第二内存总线上的信号遵循相同的协议;

27.第一内存总线上的信号的数据率和第二内存总线上的信号的数据率不同。

28.支持同等数据率规格的内存颗粒开发进度慢于处理器,通过该技术方案,可以将不同数据率规格的内存颗粒和处理器集成到一个计算机系统中,并且处理器的内存总线能够达到标准中最大的数据率。

29.一种可能的实现方式中,第二内存总线包括第一子总线和第二子总线;

30.第一子总线上信号的数据率高于第二子总线上信号的数据率。

31.一种可能的实现方式中,统计数据的访问频率;

32.将访问频率高于阈值的数据存储于与第一子总线连接的内存颗粒;或,

33.将访问频率低于阈值的数据存储于与第二子总线连接的内存颗粒。

34.通过该技术方案,可以让访问频率高的数据,能够更快的读取和写入。针对访问频率低的数据,使用低规格的内存颗粒,可以降低内存模组的整体成本。

35.第三方面,提供了一种计算机系统,计算机系统包括内存模组和处理器,内存模组是如上述第一方面任一可能的实现方式中的内存模组。

36.第四方面,提供了一种计算机可读存储介质,计算机可读存储介质中存储有计算机程序,当程序被计算机系统执行时,使计算机系统执行如上述第二方面中任一可能的实现方式中的内存总线信号处理的方法。

附图说明

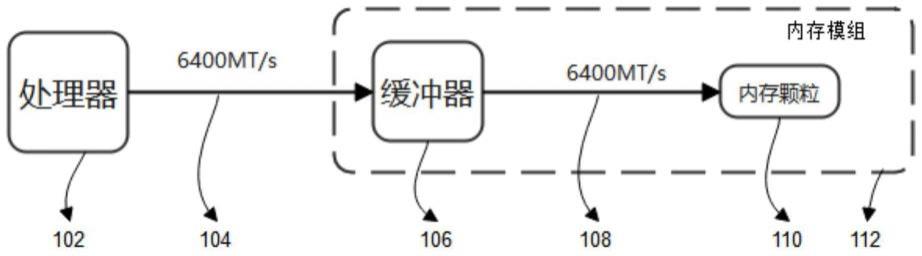

37.图1a:ddr5标准的内存模组和处理器的连接结构示意图;

38.图1b:ddr5标准的另一种内存模组和处理器的连接结构示意图;

39.图2a:本技术实施例提供的一种内存模组和处理器的连接结构示意图;

40.图2b:本技术实施例提供的另一种内存模组和处理器的连接结构示意图;

41.图3:本技术实施例提供的另一种内存模组和处理器的连接结构示意图;

42.图4:本技术实施例提供的另一种内存模组和处理器的连接结构示意图。

43.具体实施方式

44.本技术提供了一种技术方案,将处理器内存总线上信号的数据率和内存颗粒内存总线上的信号不同的数据率进行匹配。两侧的内存总线遵循相同的ddr标准。

45.首先对如下概念进行定义解释:

46.总线上信号的数据传输速率是数据率和总线位宽的乘积。数据传输速率的单位是比特每秒,即bit/s。总线位宽的单位是比特每次传输,即bit/t。数据率的单位是传输每秒,即t/s。其中bit是比特,s是秒,t是传输。

47.图1a所示,包括处理器102、处理器侧的内存总线104和内存模组112,其中内存模组112包括:缓冲器106,内存颗粒的内存总线108,以及内存颗粒110。处理器的内存总线104支持的信号的数据率最高速率是6400mt/s,理想情况下,内存颗粒的内存总线108支持的信号的数据率最高速率也是6400mt/s,这样就能最大程度发挥整个内存总线的数据传输能力。本技术中提到的内存模组是安装有内存颗粒的印制电路板,种类包括但不限于:无缓冲双线内存模块(unbuffereddual in-line memory module,udimm),带寄存器的双线内存模块(registereddual in-line memory module,rdimm),低负载双线内存模块(load-reduced dualin-line memory module,lrdimm)等等。

48.但是实际情况如图1b所示,处理器的内存总线124支持的信号的最高数据率是6400mt/s。但是因为内存颗粒的研发进度低于处理器,内存颗粒的内存总线支持的信号的最高数据率低于6400mt/s。例如图1b中,内存颗粒的内存总线128 支持的信号的最高数据率是3200mt/s。这种情况下,内存总线124和内存总线128 上的信号的数据率最高只能达到3200mt/s。处理器的内存总线的数据读写能力没有被完全利用。

49.本技术实施例提供了一种技术方案,如图2a所示,计算机系统包括处理器 202、处理器的内存总线204和内存模组210。其中内存模组210包括:缓冲器206,内存颗粒的内存总线208,以及内存颗粒212a和内存颗粒212b。缓冲器206通过内存总线204连接到处理器202。内存总线204支持的信号的最高数据率是 6400mt/s。内存颗粒212a和内存颗粒212b通过内存总线208连接到缓冲器206。内存总线208支持的信号的最高数据率是3200mt/s。可见,内存颗粒212a和内存颗粒212b的内存总线支持的信号的最高数据率低于处理器202的内存总线支持的信号的最高速率。缓冲器,将处理器侧的内存总线上的信号分发到两个内存颗粒的内存总线,使得内存颗粒的内存总线上信号的数据率只是处理器的内存总线上信号数据率的一半。例如内存总线204上信号的数据率是6400mt/s,而内存总线208上信号的数据率是3200mt/s。本技术实施例中使用低数据率规格的内存颗粒匹配有高数据率规格的内存总线的处理器,也能利用该处理器的性能优势。

50.在另外一个例子中,如果内存颗粒侧的内存总线支持的信号的最高数据率无法发挥到内存颗粒的最大能力(例如虽然内存颗粒的内存总线可以支持信号的最高数据率是3200mt/s,但是因为印制电路板的走线约束,内存总线上信号的工作数据率只能到1600mt/s),也可以通过缓冲器将处理器侧内存总线上的信号,分发到多个内存颗粒的内存总线上。如图2b所示,如果内存颗粒的内存总线上信号的工作数据率只能到1600mt/s,此时还是可以保证处理器的内存总线上信号速率达到最大。图2b中,展示了处理器222,处理器侧内存

总线224和内存模组230。其中内存模组230包括:缓冲器226,内存颗粒侧内存总线228a、228b、228c和 228d,以及内存颗粒232a、232b、232c和232d。其中内存总线224上信号的工作数据率是6400mt/s,而因为电路板导线走线约束,内存总线228a、228b、228c 和228d上信号的工作数据率是1600mt/s。

51.如图3所示,当内存颗粒的研发进度赶上来,在不重新开发内存模组电路板的情况下,只更换内存颗粒的种类,就可以减少内存颗粒的数量,降低成本和功耗,而且不影响内存总线数据最大传输能力。如图3所示,展示了处理器302,处理器侧内存总线304和内存模组310,其中内存模组310包括:缓冲器306、内存颗粒侧内存总线308a、308b、308c和308d,以及内存颗粒312a、312b、312c 和312d。其中内存总线304支持的信号的最高数据率是6400mt/s,而内存总线 308a、308b、308c和308d支持的信号最高数据率是1600mt/s。当内存颗粒的内存总线能支持的信号的最高数据率提升,例如提升到3200mt/s,则缓冲器306可以关闭两个内存总线上的信号,并选焊对应内存子总线上的内存颗粒。例如关闭内存子总线308c和内存子总线308d上的信号,并选焊内存颗粒312c和312d。一个内存颗粒通过一组焊盘,焊接在内存模组的印刷电路板上,从而与内存总线连接,选焊内存颗粒是指,在一组焊盘上不焊接对应的内存颗粒。

52.将两颗内存颗粒312a和312b更换成内存总线支持信号最高数据率为 3200mt/s的内存颗粒,这样就可以在不重新开发内存模组印制电路板的情况下,达到降低成本和功耗的目的。

53.这里进一步说明,内存总线308a、308b、308c和308d作为一个整体为缓冲器306内存颗粒侧内存总线,而308a、308b、308c和308d单独来看,每一个都是内存颗粒侧内存总线的子总线。

54.同理,如果内存颗粒的内存总线支持的信号最大数据率达到ddr5标准的最大值,和处理器侧内存总线支持的信号最大数据率保持一致,则可以只用一颗内存颗粒,选焊三颗内存颗粒,即可达到目的,另外不用重新设计内存模组的印制电路板。

55.在另外一个实施例中,可以选用两种不同的内存颗粒,它们的内存总线分别支持信号最高数据率不同。内存颗粒的内存总线支持信号最高速率的总和与处理器的内存总线支持信号最高速率相同。例如一颗内存颗粒的内存总线支持信号最高数据率达到4800mt/s,而另外一颗内存颗粒的内存总线支持信号最高数据达到一颗1600mt/s。由处理器来判断数据的访问频率,访问频率高的数据放到内存总线上信号的数据率高的内存颗粒中,访问频率低的数据放到内存总线上信号数据率低的内存颗粒中。如图4所示,展示了处理器402、处理器侧内存总线404和内存模组410,其中内存模组包括缓冲器406、内存总线408a和408b、以及内存颗粒412a和412b。其中,访问频率高的数据存储在内存颗粒412a中,而访问频率低的数据存储在内存颗粒412b中。在一种可能的实施方式中,由缓冲器406 去判断数据的访问频率。低规格的内存颗粒的成本更低,通过不同规格的内存颗粒的混用配置,可以实现内存模组410成本的降低,且仍旧保证cpu侧内存总线。上述缓冲器可以是数据缓冲器和/或寄存器时钟驱动器。

56.最后应说明的是:以上实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;

而这些修改或者替换,并不使相应技术方案脱离权利要求的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。