1.本发明涉及芯片设计技术领域,尤其涉及一种用以减小动态功耗的布线优化方法。

背景技术:

2.功耗是衡量一款芯片优劣的重要指标之一。由于芯片作为具有复杂功能的器件,其功耗会根据其不同时段的不同行为,不同的外部条件而发生很大的变化。在实际设计中,芯片的功耗通常从两方面进行考虑,即静态功耗和动态功耗。

3.静态功耗(static power),又称漏电流功耗(leakage power)。主要是由于mos管在导通下的漏电流所带来的。动态功耗(dynamic power),主要是由于芯片中的寄生rc电路的充放电引起的。也就是说当芯片中的电路出现任何信号翻转,都将会产生动态功耗。

4.在实际后端设计时,动态功耗由于和芯片的功能息息相关。在实际计算动态功耗的时候,会分成两个部分考虑:一部分为标准单元内部的动态功耗,又称为内部功耗(internal power),是在单元(cell)内部由于充放电而产生的功耗;另一部分为互连线(net)上的动态功耗,称为翻转功耗(switching power)。

5.可以理解,动态功耗的产生主要来源是以下两个方面:信号翻转时由于nmos和pmos同时导通而产生的短暂但巨大的贯穿电流;给内部和外部负载充放电所消耗的能量。

6.现今的低功耗设计中,减小功耗的主要方法包括:应用多个电源域(power domain)以便在芯片的某一部分功能不用的时候将其断电关闭;或者通过升级更先进的工艺来降低每个晶体管的尺寸从而降低整体面积;或者通过改善时钟树综合手段来降低芯片中占比很大的功率时钟网络(clock network power)。

7.在后端设计中,如果可以有更有效更直接的方式来降低功耗,特别是动态功耗,将是非常有意义的。

技术实现要素:

8.本发明的目的是提供一种用以减小动态功耗的布线优化方法。通过对布线过程进行优化,在预布线后找到动态功耗最大一些关键路径,对它们从走线金属层、耦合电容、线宽和迂回绕线几个方面考虑进行改进,从而减小这些关键路径的动态功耗,达到降低芯片整体动态功耗的目的。该方法易于实施,耗时少,节省设计周期,匹配兼容现有后端设计工艺,能够达到通过布线优化来减小动态功耗的效果。

9.为此,本发明实施例提供了一种用以减小动态功耗的布线优化方法,包括:

10.在时钟树综合后,执行预布线;

11.对预布线结果提取寄生参数,得到各条路径的金属走线上的电阻参数和电容参数;

12.根据所述电容参数,从各条路径中确定出关键路径;

13.获取各金属层阻容信息,根据所述金属层阻容信息,对所述关键路径的金属走线

在不同金属层的分布进行优化;和/或

14.获取线间距优化参数,根据所述线间距优化参数,对所述关键路径的金属走线与最接近所述关键路径的金属走线之间的间距进行优化;和/或

15.获取金属线宽优化参数,根据所述金属线宽优化参数,对所述关键路径的金属走线的线宽进行优化;和/或

16.计算所述关键路径的曼哈顿距离,根据所述曼哈顿距离和所述关键路径的金属走线在横向和纵向上的总长度确定所述关键路径是否存在迂回绕线,当存在迂回绕线时,对所述关键路径的金属走线进行重新布线。

17.优选的,根据所述电容参数,从各条路径中确定出关键路径具体包括:

18.确定所述电容参数是否大于预设电容值;

19.当一条路径的金属走线上的所述电容参数大于所述预设电容值时,确定所述路径为所述关键路径。

20.优选的,根据所述电容参数,从各条路径中确定出关键路径具体包括:

21.根据各条路径的金属走线上的电容参数的由大到小进行排序;

22.将排在最前面的第一数量条路径确定为所述关键路径。

23.优选的,所述预布线包括:

24.设置参数,执行预布线操作;

25.进行预布线后的基本优化。

26.优选的,所述获取各金属层阻容信息,根据所述金属层阻容信息,对所述关键路径的金属走线在不同金属层的分布进行优化具体为:

27.获取各金属层阻容信息,确定低阻容的金属层;

28.获取所述关键路径的金属走线的分布参数,根据所述分布参数重布所述关键路径的金属走线的路径,使得重步路径后的金属走线在所述低阻容的金属层上的路径长度占比比重布前的占比大,从而减小所述关键路径的金属走线的电容。

29.优选的,所述获取线间距优化参数,根据所述线间距优化参数,对所述关键路径的金属走线与最接近所述关键路径的金属走线之间的间距进行优化具体为:

30.获取线间距优化参数;

31.根据所述线间距优化参数,对所述关键路径的金属走线与最接近所述关键路径的金属走线之间的间距进行优化,使得优化后关键路径的金属走线与最接近所述关键路径的金属走线之间的间距大于优化前关键路径的金属走线与最接近所述关键路径的金属走线之间的间距,从而减小关键路径的金属走线与最接近所述关键路径的金属走线之间的耦合电容。

32.优选的,所述获取金属线宽优化参数,根据所述金属线宽优化参数,对所述关键路径的金属走线的线宽进行优化具体为:

33.所述获取金属线宽优化参数;

34.根据所述金属线宽优化参数,对所述关键路径的金属走线的线宽进行优化,使得优化后关键路径的金属走线的线宽小于优化前关键路径的金属走线的线宽,从而减小所述关键路径的金属走线的电容。

35.优选的,所述计算所述关键路径的曼哈顿距离,根据所述曼哈顿距离和所述关键

路径的金属走线在横向和纵向上的总长度确定所述关键路径是否存在迂回绕线,当存在迂回绕线时,对所述关键路径的金属走线进行重新布线具体为:

36.根据所述关键路径的金属走线的起点和终点计算所述关键路径的曼哈顿距离;

37.获取所述关键路径的金属走线在横向和纵向上的总长度;

38.确定所述总长度是否超出所述曼哈顿距离与预设长度之和;

39.如果超出,确定所述关键路径存在迂回绕线,并对所述关键路径的金属走线进行重新布线,使得重新布线后的金属走线在横向和纵向上的总长度不超出所述曼哈顿距离与预设长度之和,从而减少迂回绕线。

40.本发明实施例提供的用以减小动态功耗的布线优化方法,通过对布线过程进行优化,在预布线后找到动态功耗最大一些关键路径,对它们从走线金属层、耦合电容、线宽和迂回绕线几个方面考虑进行改进,从而减小这些关键路径的动态功耗,达到降低芯片整体动态功耗的目的。该方法易于实施,耗时少,节省设计周期,匹配兼容现有后端设计工艺,能够达到通过布线优化来减小动态功耗的效果。

附图说明

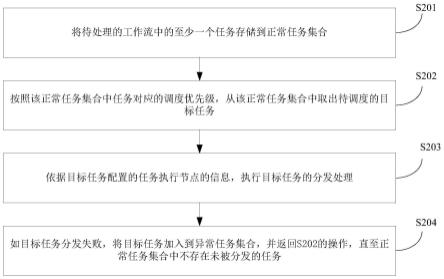

41.图1为本发明实施里提供的一种用以减小动态功耗的布线优化方法流程图。

具体实施方式

42.下面通过附图和实施例,对本发明的技术方案做进一步的详细描述。

43.本发明实施例提供了一种用以减小动态功耗的布线优化方法,其主要步骤流程如图1所示,包括:

44.步骤110,在时钟树综合后,执行预布线;

45.在大部分超大规模集成电路中,各功能元件之间的数据传输由一个同步信号控制,这个执行统一指挥的信号就是时钟信号,它是设计高性能芯片中必须非常重视的部分。时钟信号通常是整个芯片中有最大扇出、通过最长距离、以最高速度运行的信号。时钟信号必须保证在最差的条件下,关键时序要求能得到满足,否则对时钟信号任何不当的控制都可能导致芯片功能紊乱,将错误数据锁存到触发器导致功能错误。因此时钟树综合是后端设计中必要的一个步骤,本发明所提出的布线优化方法,是在时钟树综合后进行的。

46.布线是继布局规划和时钟树综合之后的重要物理实施过程,具体是将分布在芯片核内的模块、标准单元和输入输出接口单元按逻辑关系进行互连,以完成它们之间的所有逻辑信号互连,同时满足各种约束条件。

47.在这里所执行的预布线,是指不考虑解决设计规则检查(design rule check,drc)违反问题情况下的逻辑关系互联的建立。执行预布线的目的,主要是为了获得真实、相对准确的金属布线信息,包括金属走线的路径、每条路径所占用金属层、在每一层上的长度、金属线宽等等。

48.预布线的步骤可以包括:

49.1、设置参数,执行预布线操作;

50.2、进行预布线后的基本优化。

51.预布线的工作主要是在参数设置中根据具体需要设置相应的参数,比如考虑天线

效应、时序驱动、信号完整性等细节参数,指导工具(这里是指已有业内常用的后端设计工具)自动执行相应的策略,并通过工具自动对单元进行改动和调整。这一步骤是本领域技术人员在设计过程中已成熟实现的步骤,在此不再做过多说明。

52.步骤120,对预布线结果提取寄生参数,得到各条路径的金属走线上的电阻参数和电容参数;

53.在预布线后,工具自动进行寄生参数提取,可以得到各条路径的金属走线上的电阻参数和电容参数。电容参数包括对地电容参数和耦合电容参数。在实际计算负载的时候,耦合电容会被折算成对地电容来计算。

54.步骤130,根据电容参数,从各条路径中确定出关键路径;

55.前面已经介绍过,动态功耗(dynamic power)可以分为两部分,一是标准单元内部的动态功耗,又称为内部功耗(internal power),是在单元(cell)内部由于充放电而产生的功耗;另一部分为互连线(net)上的动态功耗,称为翻转功耗(switching power)。

56.内部功耗(internal power)主要产生于给内部和外部负载充放电所消耗的能量。

57.翻转功耗(switching power)主要产生于信号翻转时由于nmos和pmos同时导通而产生的短暂但巨大的贯穿电流带来的功耗。

58.因此,要降低功耗,就要从这两方面着手。本发明的思路,是解决动态功耗最大的一定数量路径的功耗问题,这样可以在耗时少的条件下有效的达到降低芯片整体动态功耗的目的。

59.翻转功耗(switching power)的计算公式为switching power=1/2cv2f。其中c为该路径对应的电容参数,v为该路径对应的电压,这个电压可以通过eda工具emir分析获得,f为该路径对应的信号翻转频率。由此可以看到,c减小,翻转功耗就会随之减小。

60.内部功耗(internal power)跟单元(cell)的输入信号的斜率有关,信号的斜率和驱动单元的驱动强度有关,同时跟这个驱动单元后面所挂的负载也有关系,因此归根到底还是和rc有关。因此c减小,内部功耗也会随之减小。

61.根据以上分析可以看出,在确定出关键路径后,只要能减小关键路径的电容参数,就能有效地减小芯片的动态功耗。

62.确定出关键路径的方式可包括至少以下两种,一种是根据电容参数的绝对值来确定,另一种是根据路径在全部路径中电容参数大小的排序顺序确定。

63.在第一种方式中,首先确定电容参数是否大于预设电容值;当一条路径的金属走线上的电容参数大于预设电容值时,确定路径为所述关键路径。预设电容值可以基于设计需求由设计人员自定义设置。

64.在第二种方式中,根据各条路径的金属走线上的电容参数的由大到小进行排序,将排在最前面的第一数量条路径确定为关键路径。第一数量可以由工具定义一个默认值,当然也可以由设计需求由设计人员自定义设置。

65.减小关键路径的电容参数可以实施的方法包括如下步骤140-170,在实际实施中,可以选择其中的一步或几步来实施,执行顺序可以以任意先后顺序执行。在此的步骤140-170的顺序仅为其中一种可能的方式。

66.步骤140,获取各金属层阻容信息,根据金属层阻容信息,对关键路径的金属走线在不同金属层的分布进行优化;

67.在芯片设计过程中,工艺库是已经确定的,设计采用几层金属,每层金属的具体属性都是已经确定的,因此可以获取到各金属层阻容信息。

68.获取各金属层阻容信息确定低阻容的金属层后,根据关键路径的金属走线的分布参数,来重布关键路径的金属走线的路径,使得重步路径后的金属走线在低阻容的金属层上的路径长度占比比重布前的占比大,从而减小关键路径的金属走线的电容。

69.关键路径的金属走线在不同金属层的分布通过工具可以提取到,因此也是已知的。比如一个设计采用7层金属,其中第5层到第7层(m5-m7)为低阻容层。一条被识别成关键路径的路径,在m5-m7的走线长度占比为30%,在m1-m4的走线长度占比为70%。可以通过工具指定该关键路径优先选择m5-m7布线,减小关键路径的金属走线的电容,从而达到减小关键路径的所产生的动态功耗效果。

70.步骤150,获取线间距优化参数,根据线间距优化参数,对关键路径的金属走线与最接近关键路径的金属走线之间的间距进行优化;

71.金属走线与金属走线之间的最小线宽是根据设计规则要求有所规定的,在自动布线时,相邻金属走线之间的线间距必须要满足大于等于最小线间距的要求。

72.金属走线间会产生耦合电容,加大相邻金属走线间距,可以减小耦合电容。因此,对于关键路径,可以通过增加线间距,来减小耦合电容。

73.在实际实施中,可以设定比最小线间距更大的线间距优化参数,对于关键路径以线间距优化参数来设置其与最接近关键路径的金属走线之间的间距。

74.获取线间距优化参数,根据线间距优化参数,对关键路径的金属走线与最接近关键路径的金属走线之间的间距进行优化,使得优化后关键路径的金属走线与最接近关键路径的金属走线之间的间距大于优化前关键路径的金属走线与最接近所述关键路径的金属走线之间的间距,从而减小关键路径的金属走线与最接近所述关键路径的金属走线之间的耦合电容。

75.例如,在优化前关键路径的金属走线与最接近关键路径的金属走线之间的间距为设计规则要求的最小线间距,通过优化,将关键路径的金属走线与最接近关键路径的金属走线之间的间距设定为最小线间距的两倍,从而减小耦合电容,达到减小关键路径的所产生的动态功耗效果。需要说明的是,线间距优化参数可以是一个具体的数值,也可以是一个用以扩大金属走线间距的倍数关系。

76.步骤160,获取金属线宽优化参数,根据金属线宽优化参数,对关键路径的金属走线的线宽进行优化;

77.同样的,获取金属线宽优化参数;根据金属线宽优化参数,对关键路径的金属走线的线宽进行优化,使得优化后关键路径的金属走线的线宽小于优化前关键路径的金属走线的线宽,从而减小关键路径的金属走线的电容。

78.金属线宽根据设计规则要求也有所规定的。在实际实施中,可以设定金属线宽优化参数,使得关键路径进行自动布线后的金属线宽更大的金属线宽优化参数,对于关键路径根据金属线宽优化参数来设置其线宽。

79.金属线宽优化参数可以是一个具体的数值,也可以是一个用以扩大金属线宽的倍数关系。

80.线宽越小,金属走线的对地电容越小,因此可以通过根据金属线宽优化参数在设

计规则允许范围内适当减小金属走线的线宽,来进一步减小电容,从而达到减小关键路径的所产生的动态功耗效果。

81.步骤170,计算关键路径的曼哈顿距离,根据曼哈顿距离和关键路径的金属走线在横向和纵向上的总长度确定关键路径是否存在迂回绕线,当存在迂回绕线时,对关键路径的金属走线进行重新布线。

82.自动布线过程因为考虑到种种约束以及单元布局的影响,金属走线的路径往往都不会是最短的路径,即一条路径上的起点到终点之间在水平面上的距离通常一定会大于这两点间的曼哈顿距离。

83.根据关键路径的金属走线的起点和终点计算关键路径的曼哈顿距离;获取关键路径的金属走线在横向和纵向上的总长度;确定总长度是否超出曼哈顿距离与预设长度之和;如果超出,确定所述关键路径存在迂回绕线,并对关键路径的金属走线进行重新布线,使得重新布线后的金属走线在横向和纵向上的总长度不超出所述曼哈顿距离与预设长度之和,减少迂回绕线,从而达到减小关键路径的所产生的动态功耗效果。

84.本发明实施例提出的用以减小动态功耗的布线优化方法,通过对布线过程进行优化,在预布线后找到动态功耗最大一些关键路径,对它们从走线金属层、耦合电容、线宽和迂回绕线几个方面考虑进行改进,从而减小这些关键路径的动态功耗,达到降低芯片整体动态功耗的目的。该方法易于实施,耗时少,节省设计周期,匹配兼容现有后端设计工艺,能够达到通过布线优化来减小动态功耗的效果。

85.专业人员应该还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本发明的范围。

86.结合本文中所公开的实施例描述的方法或算法的步骤可以用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(ram)、内存、只读存储器(rom)、电可编程rom、电可擦除可编程rom、寄存器、硬盘、可移动磁盘、cd-rom、或技术领域内所公知的任意其它形式的存储介质中。

87.以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。