基于bbpd模块实现自校准的时间交织flash adc电路

技术领域

1.本发明属于电子电路技术领域,具体涉及一种基于bbpd模块实现自校准的时间交织flash adc电路。

背景技术:

2.模拟数字转换器(analog to digital converter,adc)是当今许多技术的重要组成部分。本质上来说,从自然界到数字世界的转换必然会涉及到模拟到数字的转换。而随着通信技术的飞速发展,模拟信号的带宽不断向大宽带方向发展,从而导致adc采样速度要求也越来越高。然而,由于现有cmos电路设计的局限,单模块的高速adc难以实现。因此,多通道并行结构的时间交错adc(time-interleavedadc,ti-adc)是高速adc的主要设计方案之一。ti-adc由m个相同分辨率的单通道adc组成,且各个adc并行交替采样并转换输入信号,最后通过多路选择器(multiplexer,mux)将各个adc的输出交替输出,以此可以将系统的采样频率提升m倍。ti-adc虽然可以提高系统的采样率,但同样会带来新的问题。在实际ti-adc电路设计中,由于各个子adc都是单独的电路,难以做到性能完全一致,以及各自采样时刻的偏差,都会导致解交织后的总体转换结果在频谱上产生杂散失真,造成转换精度的下降。ti-adc的非理想效应主要有失调失配(offset error)、增益失配(gain error)和时延失配(timing skew)。其中,时延失配是ti-flash-adc最重要的非理想问题。目前在工业界和学术界已经提出了多种针对时延失配的校准方法。检测与消除ti-adc时延失配带来的误差的方法有模拟域校准、混合域校准和数字域校准。模拟域校准指的是完全在模拟域进行的失配误差检测与消除;混合域校准指的是先在数字域估计出失配误差大小,然后返回模拟域对误差进行校准;数字域校准指的是完全在数字域进行失配的检测和消除。然而,这些方法往往只能用于某些特定条件之下,并需要额外昂贵的电路。

技术实现要素:

3.本发明的目的在于提供一种基于bbpd模块实现自校准的时间交织flash adc电路,该电路结构简单,功耗低。

4.为实现上述目的,本发明采用的技术方案是:一种基于bbpd模块实现自校准的时间交织flash adc电路,包括电压时间转换器vtc、bang-bang鉴相器bbpd、时钟、电荷泵cp、低通滤波器lpf、环形振荡器rvco、rsg电路和多路选择器mux,输入信号x(t)先由vtc进行采样,其输出输送到bbpd,bbpd检测脉宽信号与时钟之间的相位误差,将相位误差信息转化为up或down信号,up或down信号控制cp对lpf进行充放电,lpf输出至rvco的电压vc发生变化,导致rvco的振荡角频率和相位随之变化,进而输出经过校准后的时钟,校准后的时钟重新回到vtc进行采样,经过量化器得到校准后的输出。

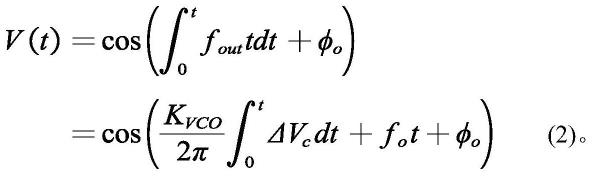

5.进一步地,rvco的振荡角频率和相位的变化满足下式:

6.7.其中,ωo、ω

out

分别是初始角频率和变化后的角频率;fo、f

out

分别是初始振荡频率和变化后振荡频率;k

rvco

是rvco的增益;当vc发生变化时,输出给vtc的采样时钟的相位随之改变;假设rvco初始输出为v(t)=cos(2πfot),根据频率f与相位φ的关系其中φo为初始相位,得到lpf上电压变化δvc时的输出为:

[0008][0009]

进一步地,所述vtc为3级级联动态比较器,由浮动反向放大器fla、动态锁存比较器和锁存器组成;为了提高动态比较器的分辨率,在动态锁存比较器前级联了fla;当比较器的控制时钟为高电平时,输入信号先经过fla放大,再送至动态锁存器进行比较,最后通过级联的锁存器保证当控制时钟为低电平时,动态比较器仍然保持比较后的结果输出。

[0010]

进一步地,所述bbpd用于检测输入的脉宽信号与采样时钟之间的相位误差信息,并将相位误差信息转化为相应的up或dn信号,用于驱动后续电路;所述bbpd共有两个部分,分别为用于采样的3组vtc和将相位误差转化为up或者dn信号的逻辑门阵列;其中每组vtc包括5个相同的vtc,每组vtc的参考电压不一样,分别为v

ref_h

、v

ref_m

和v

ref_l

;在每组vtc中,前4个vtc分别由数据采样时钟clk0~clk3来触发,clk0~clk3分别代表相位为0

°

、90

°

、180

°

、270

°

的时钟,而最后一个vtc则由边沿采样时钟clk

en

触发,clk

en

由相位为45

°

、135

°

、215

°

和315

°

的时钟组成;其中每个时钟周期有4个vtc输出的脉宽信号进入量化器得到量化后的输出,同时这4个脉宽信号又与其他vtc的输出一起参与时延失配的校准。

[0011]

进一步地,所述cp采用反相器作为开关,以此将输入管与其输出节点隔离开,从而降低开关管电流泄漏效应的影响;同时采用cascade结构的电流镜,使镜像的电流不受沟道调制效应的影响,保证cp的上拉电流和下拉电流严格匹配;为了保证镜像的栅极电压足够,偏置电路串联反相器;为了在有限的尺寸和压降的情况下得到较大电流,偏置使用栅压提升技术。

[0012]

进一步地,所述rvco用于为系统提供周期性的采样时钟,采用四级差分rvco结构,其中一级的连接不反相,以实现偶数级联的振荡器;所述rvco的延迟单元结构采用差分连接方式,以抑制共模噪声和衬底噪声。

[0013]

进一步地,所述rsg电路用于控制4个边沿采样时钟的工作顺序,4个边沿采样时钟分别是相位为45

°

、135

°

、225

°

、315

°

的时钟,每个时钟周期只通过一个边沿采样时钟触发vtc;所述rsg电路由2个d触发器和4个与门构成。

[0014]

与现有技术相比,本发明具有以下有益效果:提供了一种基于bbpd模块实现自校准的时间交织flash adc电路,可以同时实现adc的采样和量化。本发明通过电压时间转换器(vtc)将输入的模拟信号转化为不同宽度的脉冲宽度信号,利用bang-bang鉴相器来检测采样时钟与脉冲宽度信号之间的相位误差信息,随后将相位误差信息通过锁相环路来减小误差,从而达到时延失配的校准。与现有技术相比,本发明的电路结构更加简单,功耗更低,且没有输入依赖性,在高速、低功耗的采集设备、医疗器械及便携式终端等有良好的应用前

景。

附图说明

[0015]

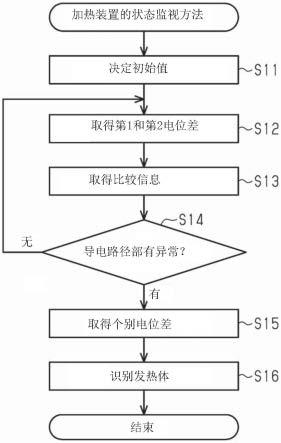

图1是本发明实施例的电路结构示意图。

[0016]

图2是本发明实施例中bang-bang鉴相器的结构示意图。

[0017]

图3是本发明实施例中vtc电路的结构示意图。

[0018]

图4是本发明实施例中bbpd电路的结构示意图。

[0019]

图5是本发明实施例中vtc比较时可能出现的情况。

[0020]

图6是本发明实施例中cp电路的结构示意图。

[0021]

图7是本发明实施例中四级差分ringvco电路拓扑结构图。

[0022]

图8是本发明实施例中延迟单元电路的结构示意图。

[0023]

图9是本发明实施例中rsg电路的结构示意图。

[0024]

图10是本发明实施例中系统时域输入输出波形以及ringvco控制电压的变化曲线图。

[0025]

图11是本发明实施例中输出信号的频谱图。

[0026]

图12是本发明实施例的电路版图。

具体实施方式

[0027]

下面结合附图及实施例对本发明做进一步说明。

[0028]

应该指出,以下详细说明都是示例性的,旨在对本技术提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本技术所属技术领域的普通技术人员通常理解的相同含义。

[0029]

需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用术语“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

[0030]

本发明为了解决ti-adc中时延失配对整个采样系统的影响,提出了一种新颖的时延失配校准方案。其原理是模拟信号先通过vtc转换成不同宽度的脉宽信号,当系统存在时延失配时,脉宽信号的宽度和位置会偏离理想情况,导致adc每位的输出之间可能存在交叠的现象,即ipi现象。针对这一现象,本发明提出使用锁相环路的负反馈特性来达到校准。

[0031]

如图1所示,本实施例提供了一种基于bbpd模块实现自校准的时间交织flash adc电路,包括电压时间转换器(voltage time converter,vtc)、bang-bang鉴相器(bang-bang phase detector,bbpd)、时钟、电荷泵(charge pump,cp)、低通滤波器(low pass filter,lpf)、环形振荡器(ring voltage controlled oscillator,rvco)、rsg电路和多路选择器mux。输入信号x(t)先由vtc进行采样,其输出输送到bbpd,bbpd检测脉宽信号与时钟之间的相位误差,将相位误差信息转化为up(当时延δt>0,即时钟相位滞后)或down(当时延δt<0,即时钟相位超前)信号,up或down信号控制cp对lpf进行充放电,lpf输出至rvco的电压vc发生变化,导致rvco的振荡角频率和相位随之变化,其变化满足下式:

[0032][0033]

其中,ωo、ω

out

分别是初始角频率和变化后的角频率;fo、f

out

分别是初始振荡频率和变化后振荡频率;k

rvco

是rvco的增益;当vc发生变化时,输出给vtc的采样时钟的相位随之改变;假设rvco初始输出为v(t)=cos(2πfot),根据频率f与相位φ的关系其中φo为初始相位,得到lpf上电压变化δvc时的输出为:

[0034][0035]

进而输出经过校准后的时钟,校准后的时钟重新回到vtc进行采样,经过量化器得到校准后的输出。

[0036]

图2为典型的bang-bang鉴相器——alexander鉴相器,该鉴相器会基于相位差的正负符号产生相应的二进制信号;此外,bang-bang型的鉴相器对数据模式、工艺和器件变化较不敏感。当ti-adc的输出经过dac恢复为连续信号时,会产生脉冲间干扰(inter-pulse interference,ipi)。也就是说,我们将时序偏差转化为ipi问题,利用锁相环路实现校准。

[0037]

以下结合实际电路设计,对本发明的详细电路及其结果作进一步说明。

[0038]

(1)vtc电路设计

[0039]

vtc的具体结构如图3所示,由一个浮动反向放大器(floating inverteramplifier,fla)、动态锁存比较器(strong-arm latch)和1个锁存器级联组成。为了提高动态比较器的分辨率,本发明在动态锁存比较器前级联了fla。其中,fla中的c2和c3上的电压作为动态锁存比较器的输入,分解连接至mp5和mp4的栅极,而动态锁存器的输出v

o

和v

o-则作为最后一级锁存器的控制电压,连接至mp7和mp8的栅极。假设v

inp

>v

inn

且输入大于阈值电压。其工作原理为:

[0040]

clk=0,处于复位阶段,fla左侧开关分别连接到vdd和gnd,将电容c1预充电充电至vdd;c2和c3处的开关闭合,电容c2和c3被预充电至v

cm

;动态锁存比较器尾电流源截止,mn5和mn8导通,将v

o

和v

o-处电压拉至gnd,使得最后锁存器比分处于锁存状态,v

out

输出保持不变。

[0041]

clk=1,进入比较阶段,由于v

inp

>v

inn

>v

th

,mn1和mn2导通,对电容c2和c3放电,且mn1和处电流更大,导致v

x->v

x

;mp3导通,动态锁存器开始工作,由于v

x->v

x

,mn6放电速度比mn7更快,使得v

o

=1,v

o-=0;此时最后一级锁存器中mp7、mn

11

截止,mp8、mn9导通,被mn9拉至gnd,随后mp

10

、mn

12

所构成的反相器将反向输出高电平v

out

,至此比较结束。

[0042]

(2)bbpd电路设计

[0043]

bbpd是本发明中非常重要的组成部分,其功能是检测输入的脉宽信号与采样时钟之间的相位误差信息,并将相位误差信息转化为相应的up和dn信号,用于驱动后续电路。

[0044]

如图4所示,bbpd由3组vtc和多个逻辑门组成,每组vtc包括5个vtc,共计15个vtc,

每组vtc的参考电压不一样,分别为v

ref_h

、v

ref_m

和v

ref_l

;在每组vtc中,前4个vtc分别由数据采样时钟clk0~clk3来触发,clk0~clk3分别代表相位为0

°

、90

°

、180

°

、270

°

的时钟,而最后一个vtc则由边沿采样时钟clk

en

触发,clk

en

由相位为45

°

、135

°

、215

°

和315

°

的时钟组成,由tn控制,n=0,1,2,3;根据不同的参考电压和采样时钟,我们将vtc的输出用符号为了便于区分不同vtc的输出,我们将用符号表示,其中i=h,m,l,表示不同的参考电压,n/en则表示采样时钟。vtc的输出随后经过逻辑门转化为up和dn信号,作为cp的控制信号。每个时钟周期有4个vtc输出的脉宽信号进入量化器得到量化后的输出,同时这4个脉宽信号又与其他vtc的输出一起参与时延失配的校准。

[0045]

3组vtc可能碰到的情况如图5所示,当触发vtc的时钟发生偏移时,偏移会被转化为相应up和dn信号,去驱动后续的cp电路,进入反馈环路进行失配校准。

[0046]

bbpd最终的输出up和dn可以由下式表示:

[0047][0048][0049]

(3)cp电路设计

[0050]

如图6所示,cp采用反相器作为开关,由bbpd输出的up和dn信号控制,即up和dn分别作为反相器的输入,以此将输入管与其输出节点隔离开,从而降低开关管电流泄漏效应的影响;同时采用cascade结构的电流镜,使镜像的电流不受沟道调制效应的影响,保证cp的上拉电流和下拉电流严格匹配;为了保证镜像的栅极电压足够,偏置电路串联反相器;为了在有限的尺寸和压降的情况下得到较大电流,偏置使用栅压提升技术,如mn4的栅极连接到了mn3的漏极,作为镜像管mn

10

和mn

12

的栅极电压,nmos的cascode管mn9和mn

11

的偏置由mn1的栅极提供,cascode管可以使用较小的宽长比,只需满足其“屏蔽”特性使共源管的漏极电压保持一致即可。

[0051]

从图中可以看出,当电荷泵处于充电状态时,up=1、upb=0、dn=0、dnb=1,inv1~inv4的输出皆为高电平,mp5~mp8的工作,mn9~mn

12

的处于截止区,充电电流对vc处充电,即对lpf充电;同时,当电荷处于放电状态时,up=0、upb=1、dn=1、dnb=0,inv1~inv4的输出皆为低电平,mp5~mp8处于截止区,mn9~mn

12

的处于饱和区,放电电流对vc处放电,即对lpf放电。

[0052]

(4)ring vco(rvco)电路设计

[0053]

ringvco的作用是为系统提供周期性的采样时钟,本发明的vtc一共需要用到8个相位的时钟,因此采用了四级差分ringvco结构。四级差分ringvco电路拓扑结构如图7所示,其中,只需将其中一级的连接不反相,即可实现偶数级联的振荡器。vc是lpf输出的电压,也是ring vco的控制电压,当vc改变时,ring vco的震荡频率也会跟着改变。

[0054]

图8所示是ringvco的延迟单元结构,采用的差分连接方式,可以很好地抑制共模噪声和衬底噪声。延迟单元共由8个mos管组成,其中,mn1和mn4组成差分输入对管,mp2和mp3交叉耦合,为电路提供偏置电流,mp1和mp4为可变负载对,其栅极连接至lpf的vc,受lpf输出电压vc控制,当vc发生变化时,mp1和mp4的阻抗会跟着发生变化,从而改变ring vco的振荡频率,二极管连接的mn2和mn3用于调整上下负载匹配,使振荡波形的上升时间与下降时间相等。最终4个延迟单元输出0、45

°

、90

°

、135

°

、180

°

、215

°

、270

°

、315

°

共8个相位时钟。

[0055]

(5)rsg电路设计

[0056]

rsg在本发明中的作用是控制4个边沿采样时钟的工作顺序,其输入时钟为rvco产生的0相位时钟。4个边沿采样时钟分别是相位为45

°

、135

°

、225

°

、315

°

的时钟,每个时钟周期只需要一个边沿采样时钟用于触发vtc即可。图9左半部分为rsg电路结构示意图,由2个d触发器(d flip-flop,dff)和4个与门构成。图9右半部分展示了rsg输入时钟clk与输出t0~t3之间的时序关系,可以看出,t0~t3互相交错为高电平,且每个高电平的宽度只有一个时钟周期,t0~t3分别对应控制相位为45

°

、135

°

、225

°

、315

°

的边沿采样时钟。

[0057]

实际电路仿真:

[0058]

本发明采用smic 180nm工艺,在cadence平台搭建所设计的基于bbpd技术自校准的时间交织flash adc电路,并且利用spectre仿真工具进行电路的仿真验证。

[0059]

当输入数据为500mhz的正弦信号时,经过环路校准之后,系统在ring vco震荡频率达到250mhz时候达到稳定。图10展示了系统时域输入输出波形以及ring vco控制电压vc的变化曲线图。从图中可以看出,当系统稳定时,vc控制线上的纹波电压小于3mv。图11为输出信号的频谱图,可以看出电路经过校准之后,sndr达到11.94db,sfdr达到61.01db,enob达到1.69bit。图12为本发明电路的版图,其面积大约为0.24mm2。

[0060]

以上所述,仅是本发明的较佳实施例而已,并非是对本发明作其它形式的限制,任何熟悉本专业的技术人员可能利用上述揭示的技术内容加以变更或改型为等同变化的等效实施例。但是凡是未脱离本发明技术方案内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与改型,仍属于本发明技术方案的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。