技术特征:

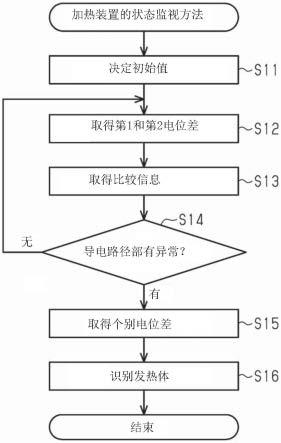

1.一种基于bbpd模块实现自校准的时间交织flash adc电路,其特征在于,包括电压时间转换器vtc、bang-bang鉴相器bbpd、时钟、电荷泵cp、低通滤波器lpf、环形振荡器rvco、rsg电路和多路选择器mux,输入信号x(t)先由vtc进行采样,其输出输送到bbpd,bbpd检测脉宽信号与时钟之间的相位误差,将相位误差信息转化为up或down信号,up或down信号控制cp对lpf进行充放电,lpf输出至rvco的电压v

c

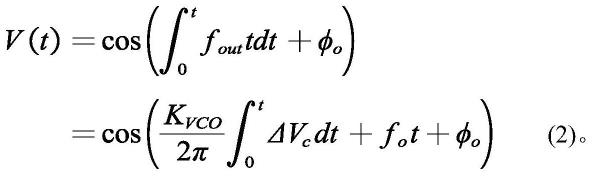

发生变化,导致rvco的振荡角频率和相位随之变化,进而输出经过校准后的时钟,校准后的时钟重新回到vtc进行采样,经过量化器得到校准后的输出。2.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flashadc电路,其特征在于,rvco的振荡角频率和相位的变化满足下式:其中,ω

o

、ω

out

分别是初始角频率和变化后的角频率;f

o

、f

out

分别是初始振荡频率和变化后振荡频率;k

rvco

是rvco的增益;当v

c

发生变化时,输出给vtc的采样时钟的相位随之改变;假设rvco初始输出为v(t)=cos(2πf

o

t),根据频率f与相位φ的关系其中φ

o

为初始相位,得到lpf上电压变化δv

c

时的输出为:3.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flashadc电路,其特征在于,所述vtc为3级级联动态比较器,由浮动反向放大器fla、动态锁存比较器和锁存器组成;当比较器的控制时钟为高电平时,输入信号先经过fla放大,再送至动态锁存器进行比较,最后通过级联的锁存器保证当控制时钟为低电平时,动态比较器仍然保持比较后的结果输出。4.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flash adc电路,其特征在于,所述bbpd用于检测输入的脉宽信号与采样时钟之间的相位误差信息,并将相位误差信息转化为相应的up或dn信号,用于驱动后续电路;所述bbpd共有两个部分,分别为用于采样的3组vtc和将相位误差转化为up或者dn信号的逻辑门阵列;其中每组vtc包括5个相同的vtc,每组vtc的参考电压不一样,分别为v

ref_h

、v

ref_m

和v

ref_l

;在每组vtc中,前4个vtc分别由数据采样时钟clk0~clk3来触发,clk0~clk3分别代表相位为0

°

、90

°

、180

°

、270

°

的时钟,而最后一个vtc则由边沿采样时钟clk

en

触发,clk

en

由相位为45

°

、135

°

、215

°

和315

°

的时钟组成;其中每个时钟周期有4个vtc输出的脉宽信号进入量化器得到量化后的输出,同时这4个脉宽信号又与其他vtc的输出一起参与时延失配的校准。5.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flash adc电路,其特征在于,所述cp采用反相器作为开关,以此将输入管与其输出节点隔离开,从而降低开关管电流泄漏效应的影响;同时采用cascade结构的电流镜,使镜像的电流不受沟道调制效应的影

响,保证cp的上拉电流和下拉电流严格匹配;为了保证镜像的栅极电压足够,偏置电路串联反相器;为了在有限的尺寸和压降的情况下得到较大电流,偏置使用栅压提升技术。6.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flash adc电路,其特征在于,所述rvco用于为系统提供周期性的采样时钟,采用四级差分rvco结构,其中一级的连接不反相,以实现偶数级联的振荡器;所述rvco的延迟单元结构采用差分连接方式,以抑制共模噪声和衬底噪声。7.根据权利要求1所述的基于bbpd模块实现自校准的时间交织flash adc电路,其特征在于,所述rsg电路用于控制4个边沿采样时钟的工作顺序,4个边沿采样时钟分别是相位为45

°

、135

°

、225

°

、315

°

的时钟,每个时钟周期只通过一个边沿采样时钟触发vtc;所述rsg电路由2个d触发器和4个与门构成。

技术总结

本发明涉及一种基于BBPD模块实现自校准的时间交织FLASH ADC电路,包括电压时间转换器VTC、Bang-Bang鉴相器BBPD、时钟、电荷泵CP、低通滤波器LPF、环形振荡器RVCO、RSG电路和多路选择器MUX,输入信号先由VTC进行采样,其输出输送到BBPD,BBPD检测脉宽信号与时钟之间的相位误差,将相位误差信息转化为UP或DOWN信号,UP或DOWN信号控制CP对LPF进行充放电,LPF输出至RVCO的电压发生变化,导致RVCO的振荡角频率和相位随之变化,进而输出经过校准后的时钟,校准后的时钟重新回到VTC进行采样,经过量化器得到校准后的输出。该电路结构简单,功耗低。低。低。

技术研发人员:钱慧 李登基

受保护的技术使用者:福州大学

技术研发日:2022.04.08

技术公布日:2022/6/21

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。