1.本技术涉及驱动技术领域,尤其涉及一种集成于双通道栅极驱动芯片的死区时间控制电路。

背景技术:

2.目为了快速切换功率晶体管并减少开关功率损耗,高电流栅极驱动芯片通常被放置在控制装置的输出和功率晶体管的栅极之间。灵活的栅极驱动芯片可适配各种电源和电机驱动,以及驱动几种类型的晶体管,包括碳化硅mosfets。在双通道栅极驱动芯片驱动半桥结构的功率开关晶体管时,为了防止两个晶体管同时导通,在驱动其中一个功率开关晶体管关断后会增加一段延时,确保该开关管完全关断之后再去打开另一个开关管,这段延时就是死区时间。

3.栅极驱动芯片中的死区时间控制电路框图如图1所示,其中栅极驱动芯片芯片电路框图省略了滤波、保护、高压隔离以及驱动等功能,仅展示了死区时间控制电路在栅极驱动芯片中的工作位置。信号控制装置输出双路控制信号 ina、inb进入栅极驱动芯片芯片,死区时间控制脚根据外部电路的时间控制信号dt,在死区时间控制模块电路中对双路输入控制信号in_a、in_b进行信号处理,得到拥有期望死区时间的双路输出信号out_a、out_b,栅极驱动芯片最终输出控制驱动信号outa、outb驱动后级的功率晶体管。

4.然而,双通道栅极驱动芯片针对应用场景的不同,对死区时间会有不同的要求。在现有技术中,通常会设计多个芯片引脚来提供不同的模式功能,这样做不仅使得所设计的电路复杂化,也增加了芯片的引脚数量,提高了封装成本。

技术实现要素:

5.鉴于此,有必要提供一种集成于双通道栅极驱动芯片的死区时间控制电路,仅复用单个引脚就能切换不同死区时间模式,以满足不同的应用场景,从而降低成本。

6.本技术为达上述目的所提出的技术方案如下:

7.一种集成于双通道栅极驱动芯片的死区时间控制电路,所述电路包括检测延时单元(1)和与所述检测延时单元(1)电连接的逻辑处理单元(2),所述检测延时单元(1)包括用于输入第一控制信号的第一输入端(11)、用于输入第二控制信号的第二输入端(12)及用于控制死区时间的第三输入端(13),所述检测延时单元(1)用于根据所述第三输入端(13)不同的连接方式输出对应的死区模式信号,以及用于对所述第一控制信号及第二控制信号进行延时处理,以对应输出第一延时控制信号及第二延时控制信号,所述逻辑处理单元(2)对所述第一控制信号、第二控制信号、第一延时控制信号、第二延时控制信号及所述死区模式信号进行逻辑处理,以输出不同死区时间模式的第一驱动控制信号及第二驱动控制信号;其中,所述第三输入端(13)具有三种连接方式,以对应控制死区时间的三种模式:

8.模式一:当所述第三输入端(13)连接栅极驱动芯片的高压电源时,所述第一驱动控制信号及第二驱动控制信号不具有死区时间,且两者允许同时有效;

9.模式二:当所述第三输入端(13)悬空时,所述第一驱动控制信号及第二驱动控制信号具有最小值的固定死区时间;

10.模式三:当所述第三输入端(13)通过电阻接地时,所述第一驱动控制信号及第二驱动控制信号具有可调节的死区时间。

11.进一步地,所述检测延时单元(1)包括检测模块(14)及延时模块(15),所述第三输入端(13)通过不同的连接方式提供不同的模拟信号,所述检测模块(14)根据所述模拟信号检测死区时间模式,并根据检测结果输出死区模式信号至所述逻辑处理单元(2),所述延时模块(15)在所述检测结果为模式三时对所述第一控制信号及所述第二控制信号进行延时处理,以输出所述第一延时控制信号及第二延时控制信号至所述逻辑处理单元(2)。

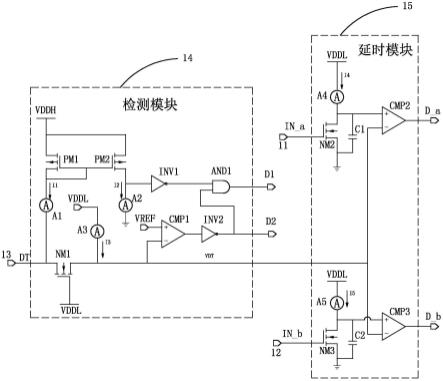

12.进一步地,所述检测模块包括mos管(pm1)、mos管(pm2)、mos管(nm1)、电流源(a1)、电流源(a2)、电流源(a3)、非门(inv1)、非门(inv2)、与门(and1)及比较器(cmp1),所述mos管(pm1)的栅极和漏极与所述 mos管(pm2)的栅极连接,所述mos管(pm1)的源极与所述mos管(pm2) 的源极连接,并电连接于栅极驱动芯片的高压电源(vddh),所述mos管(pm1) 的漏极通过所述电流源(a1)连接于所述mos管(nm1)的漏极,所述mos 管(pm2)的漏极通过所述电流源(a2)接地,所述mos管(pm2)的漏极还连接于所述非门(inv1)的输入端,所述非门(inv1)的输出端连接于所述与门(and1)的第一输入端,所述mos管(nm1)的漏极与所述第三输入端(13) 电连接,所述第三输入端(13)用于输入所述模拟信号,所述mos管(nm1) 的栅极电连接于栅极驱动芯片的低压电源(vddl),所述mos管(nm1)的源极通过电流源(a3)电连接于低压电源(vddl),所述mos管(nm1)的源极还连接于所述比较器(cmp1)的反相输入端,所述mos管(nm1)的源极还与所述延时模块(15)电连接,所述比较器(cmp1)的同相输入端用于输入电压为vref的参考电压,所述比较器(cmp1)的输出端与所述非门(inv2) 的输入端电连接,所述非门(inv2)的输出端与所述与门(and1)的第二输入端电连接,所述非门(inv2)的输出端及与门(and1)的输出端用于输出死区模式信号。

13.进一步地,所述延时模块(15)包括mos管(nm2)、mos管(nm3)、电流源(a4)、电流源(a5)、比较器(cmp2)、比较器(cmp3)、电容(c1) 及电容(c2),所述mos管(nm2)的栅极连接第一输入端(11),用于接收所述第一控制信号,所述mos管(nm2)的源极接地,所述mos管(nm2)的源极还通过所述电容(c1)连接于mos管(nm2)的漏极,所述mos管(nm2) 的漏极通过电流源(a4)电连接于低压电源(vddl),所述mos管(nm2) 的漏极还与所述比较器(cmp2)的同相输入端电连接,所述mos管(nm3) 的栅极连接第二输入端(12),用于接收所述第二控制信号,所述mos管(nm3) 的源极接地,所述mos管(nm3)的源极还通过所述电容(c2)连接于mos 管(nm3)的漏极,所述mos管(nm3)的漏极通过电流源(a5)电连接于栅极驱动芯片的低压电源(vddl),所述mos管(nm3)的漏极还与所述比较器(cmp3)的同相输入端电连接,所述比较器(cmp2)的反相输入端与所述比较器(cmp3)的反相输入端电连接,所述比较器(cmp2)的输出端用于输出所述第一延时控制信号,所述比较器(cmp3)的输出端用于输出所述第二延时控制信号。

14.上述集成于双通道栅极驱动芯片的死区时间控制电路通过复用一个输入端 (芯片引脚)的不同外部电路连接方式来切换三种不同的死区时间模式,灵活多变,减少了芯片的引脚数量及封装管脚数量,使芯片封装成本更低,同时简化了外部pcb电路设计。

附图说明

15.图1是现有技术中双通道栅极驱动芯片中的死区时间控制电路框图。

16.图2是本技术提供的集成于双通道栅极驱动芯片的死区时间控制电路的一较佳实施方式的电路单元示意图。

17.图3是图2中检测延时单元的一较佳实施方式的模块示意图。

18.图4是图3中检测模块与延时模块的一较佳实施方式的电路示意图。

19.图5是图4提供的实施方式中的各信号波形示意图。

20.主要元件符号说明

21.检测延时单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ122.第一输入端

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11

23.第二输入端

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12

24.第三输入端

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13

25.检测模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

14

26.延时模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15

27.逻辑处理单元

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ228.电容

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

c1、c2

29.mos管

ꢀꢀꢀꢀꢀꢀ

pm1、pm2、nm1、nm2、nm3

30.电流源

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

a1、a2、a3、a4、a5

31.比较器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

cmp1、cmp2、cmp3

32.非门

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

inv1、inv2

33.与门

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

and1

34.如下具体实施方式将结合上述附图进一步说明本技术。

具体实施方式

35.为了使本技术的目的、技术方案及优点更加清楚明白,下面结合附图和具体实施例对本技术作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

36.请参考图2,本技术提供一种集成于双通道栅极驱动芯片的死区时间控制电路。该电路包括检测延时单元(1)和与所述检测延时单元(1)电连接的逻辑处理单元(2)。所述检测延时单元(1)包括用于输入第一控制信号的第一输入端(11)、用于输入第二控制信号的第二输入端(12)及用于控制死区时间的第三输入端(13)。所述第一控制信号及第二控制信号为双通道栅极驱动芯片的两路驱动控制信号。所述检测延时单元(1)用于根据所述第三输入端(13)不同的连接方式输出死区模式信号,以及用于对所述第一控制信号及第二控制信号进行延时处理,以对应输出第一延时控制信号及第二延时控制信号。所述逻辑处理单元(2)对所述第一控制信号、第二控制信号、第一延时控制信号、第二延时控制信号及所述死区模式信号进行逻辑处理,以输出不同死区时间模式的第一驱动控制信号及第二驱动控制信号,从而实现控制栅极驱动芯片的双通道死区时间模式的目的。

37.其中,所述第三输入端(13)具有三种连接方式,从而实现控制死区时间的三种模式:

38.模式一:当所述第三输入端(13)连接栅极驱动芯片的高压电源时,所述第一驱动控制信号及第二驱动控制信号不具有死区时间,且两者允许同时有效 (即在时间上可重叠);

39.模式二:当所述第三输入端(13)悬空时,所述第一驱动控制信号及第二驱动控制信号具有最小值的固定死区时间,且两者不会同时有效(即在时间上不重叠);

40.模式三:当所述第三输入端(13)通过电阻接地时,所述第一驱动控制信号及第二驱动控制信号具有可调节的死区时间,且两者不会同时有效(即在时间上不重叠)。

41.进一步地,请参考图3,所述检测延时单元(1)包括检测模块(14)及延时模块(15),所述第三输入端(13)通过不同的连接方式提供不同的模拟信号,所述检测模块(14)根据所述模拟信号检测死区时间模式,以根据检测结果输出死区模式信号至所述逻辑处理单元(2)。所述延时模块(15)在检测结果为模式三时对所述第一控制信号及所述第二控制信号进行延时处理,以输出所述第一延时控制信号及第二延时控制信号至所述逻辑处理单元(2)。在本实施方式中,所述死区模式信号为两个数字信号。

42.如此,针对双通道栅极驱动芯片的不同应用场景,本技术能够复用一个输入端(芯片引脚),即通过不同的外部电路连接方式可切换三种不同的死区时间模式,灵活多变;同时简化电路设计,减少了芯片的引脚数量及封装管脚数量,使芯片封装成本更低。

43.请同时参考图4,在本实施方式中,所述检测模块(14)包括mos管(pm1)、 mos管(pm2)、mos管(nm1)、电流源(a1)、电流源(a2)、电流源(a3)、非门(inv1)、非门(inv2)、与门(and1)及比较器(cmp1)。

44.所述mos管(pm1)的栅极和漏极与所述mos管(pm2)的栅极连接,所述mos管(pm1)的源极与所述mos管(pm2)的源极连接,并电连接于栅极驱动芯片的高压电源(vddh),所述mos管(pm1)的漏极通过所述电流源(a1)连接于所述mos管(nm1)的漏极。所述mos管(pm2)的漏极通过所述电流源(a2)接地。所述mos管(pm2)的漏极还连接于所述非门(inv1) 的输入端,所述非门(inv1)的输出端连接于所述与门(and1)的第一输入端。

45.所述mos管(nm1)的漏极与所述第三输入端(13)电连接,所述第三输入端(13)用于输入时间控制信号dt。在本实施方式中,所述时间控制信号 dt为模拟信号。所述mos管(nm1)的栅极电连接于栅极驱动芯片的低压电源(vddl),所述mos管(nm1)的源极通过电流源(a3)电连接于栅极驱动芯片的低压电源(vddl)。所述mos管(nm1)的源极还连接于所述比较器(cmp1)的反相输入端。所述mos管(nm1)的源极还与所述延时模块(15) 电连接。

46.所述比较器(cmp1)的同相输入端用于输入电压为vref的参考电压。所述比较器(cmp1)的输出端与所述非门(inv2)的输入端电连接,所述非门 (inv2)的输出端与所述与门(and1)的第二输入端电连接,所述非门(inv2) 的输出端用于输出死区模式信号d1,所述与门(and1)的输出端用于输出死区模式信号d2。

47.在本实施方式中,所述延时模块(15)包括mos管(nm2)、mos管(nm3)、电流源(a4)、电流源(a5)、比较器(cmp2)、比较器(cmp3)、电容(c1) 及电容(c2)。

48.所述mos管(nm2)的栅极连接第一输入端(11),用于接收第一控制信号in_a。所述mos管(nm2)的源极接地,所述mos管(nm2)的源极还通过所述电容(c1)连接于mos管(nm2)的漏极,所述mos管(nm2)的漏极通过电流源(a4)电连接于栅极驱动芯片的低压电源(vddl)。所述mos 管(nm2)的漏极还与所述比较器(cmp2)的同相输入端电连接。

49.所述mos管(nm3)的栅极连接第二输入端(12),用于接收第二控制信号in_b,所述mos管(nm3)的源极接地,所述mos管(nm3)的源极还通过所述电容(c2)连接于mos管(nm3)的漏极,所述mos管(nm3)的漏极通过电流源(a5)电连接于栅极驱动芯片的低压电源(vddl)。所述mos 管(nm3)的漏极还与所述比较器(cmp3)的同相输入端电连接。

50.所述比较器(cmp2)的反相输入端与所述比较器(cmp3)的反相输入端电连接。所述比较器(cmp2)的输出端用于输出所述第一延时控制信号d_a,所述比较器(cmp3)的输出端用于输出所述第二延时控制信号d_b。

51.栅极驱动芯片的高压电源(vddh)与低压电源(vddl)分别提供的电源电压为vh和vl。电流源(a1)、电流源(a2)、电流源(a3)分别提供的电流为i1、i2、i3。

52.所述逻辑处理单元(2)为数字逻辑电路,所述逻辑处理单元(2)用于对所述第一控制信号in_a、第二控制信号in_b、第一延时控制信号d_a、第二延时控制信号d_b、死区模式信号d1及死区模式信号d2进行逻辑处理,以输出第一驱动控制信号out_a及第二驱动控制信号out_b。在本实施方式中,其输入与输出逻辑真值表如下:

53.表一:真值表

[0054][0055][0056]

需要说明的是,在本实施方式中,有效信号的逻辑值为1,无效信号的逻辑值为0;在其他实施方式中,有效信号的逻辑值为0,无效信号的逻辑值为1。

[0057]

因此,本实施方式所提供的模式一状态时,信号d1与d2均为1,此时信号out_a=in_a,out_b=in_b。

[0058]

在模式二状态时,信号d1为0,且信号d2为1,此时若in_a和in_b均为1,则信号out_a和out_b均为0,否则信号out_a=in_a,out_b=in_b。

[0059]

在模式三状态时,信号d1与d2均为0,此时若d_a为0,则out_b为0,否则信号out_b=in_b;若d_b为0,则out_a为0,否则信号out_a=in_a。

[0060]

下面详细说明本实施方式所提供的电路原理:

[0061]

当所述第三输入端(13),即时间控制信号dt输入端,连接栅极驱动芯片的高压电源(vddh)时,因mos管(nm1)的栅极接低压电源(vddl), mos管(nm1)的源极电压vdt将钳位在vl以下,以保护后级的低压器件,此时vdt》vref,所述非门(inv2)输出的死区模式信号d2为逻辑电平1。电流源(a1)的两端失去电压差,没有电流流动,所述mos管(pm1)及mos 管(pm2)组成的电流镜无法形成镜像电流,因此电流源(a2)将反相器(inv1) 的输入端拉至地。此时所述与门(and1)输出的死区模式信号d1为逻辑电平 1。

[0062]

当所述第三输入端(13)悬空时,电流源(a3)将mos管(nm1)的源极电压vdt上拉至接近vddl,此时vdt》vref,所述非门(inv2)输出的死区模式信号d2为逻辑电平1。所述mos管(pm1)及mos管(pm2)组成的电流镜将电流源(a1)提供的电流i1镜像,此时i1》i2,反相器(inv1)的输入端被上拉,所述与门(and1)输出的死区模式信号d1为逻辑电平0。

[0063]

当所述第三输入端(13)通过电阻(电阻值为r)接地时,电流源(a1) 与电流源(a3)共同作用在电阻上形成压降,此时mos管(nm1)的源极电压vdt=r*(i1 i3),且vdt《vref,所述非门(inv2)输出的死区模式信号 d2为逻辑电平0。反相器(inv1)的输入端处情形与悬空时相同,所述与门 (and1)输出的死区模式信号d1为逻辑电平0。

[0064]

在本实施方式中,可通过死区模式信号d1和死区模式信号d2可判断死区时间控制模式,具体如下表二:

[0065]

表二:死区时间控制模式对应表

[0066][0067]

在延时模块(15)中,当第一控制信号in_a或第二控制信号in_b的逻辑电平均为1时,所述mos管(nm2)或mos管(nm3)将导通,此时所述比较器(cmp2)或比较器(cmp3)的同相端拉至地,输出所述第一延时控制信号d_a或第二延时控制信号d_b的逻辑电平均为0。

[0068]

当第一控制信号in_a或第二控制信号in_b的逻辑电平均为0时,所述mos 管(nm2)或mos管(nm3)关断,电流源(i4)对电容(c1)充电或电流源 (i5)对电容(c2)充电,所述比较器(cmp2)或比较器(cmp3)产生关断延时翻转信号,其反相端的电压vdt越大时,延时时间越长。从第一控制信号 in_a或第二控制信号in_b的逻辑电平为0到第一延时控制信号d_a或第二延时控制信号d_b的逻辑电平为1的时间经过后级逻辑处理单元(2)叠加处理到输入的

控制信号上,便是具有死区时间的驱动控制信号。

[0069]

因此,当所述第三输入端(13)所接电阻的阻值r越大时,死区时间越长,其中r<vref/(i1 i3);当所述第三输入端(13)连接高压电源(vddh)与悬空时,mos管(nm1)的源极电压vdt(两个比较器的反相端的电压)电压近似于vddl,比较器(cmp2)与比较器(cmp3)的同相端电压无法大于反相端,第一延时控制信号d_a及第二延时控制信号d_b的逻辑电平保持为0。

[0070]

如此,通过后级的逻辑处理单元(2)的逻辑处理(请参考表1),将输出所需的第一驱动控制信号out_a及第二驱动控制信号out_b(请参考图5),在模式一时,输出的控制信号无死区时间,并允许双路输出信号同时有效;在模式二时,输出的控制信号不会同时有效,死区时间固定为最小值(此时的死区时间长度为信号传输延时,不另做延时);在模式三时,可通过调节外部接入电阻的阻值来调节死区时间的长短,阻值越大,死区时间越长,且输出信号不会同时有效。

[0071]

上述集成于双通道栅极驱动芯片的死区时间控制电路通过所述检测模块(14)上的第三输入端(13)不同的外部连接方式对应的时间控制信号dt来判断出死区时间控制模式,并根据判断结果输出死区模式信号;还设置有延时模块(15),以根据所述死区模式信号对两路控制信号进行延时处理,以输出延时控制信号。然后通过逻辑处理单元(2)的逻辑处理,为两路控制信号加入死区时间,从而输出拥有死区时间的控制信号。如此,仅复用单个引脚就能切换不同死区时间模式以及死区时间长度,以满足不同的应用场景,从而降低成本。

[0072]

以上所述仅为本技术的较佳实施例而已,并不用以限制本技术,凡在本技术的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。