1.本发明涉及一种基于混合型频率稳定控制系统的时延计算方法、装置及存储介质,属于电力系统技术领域。

背景技术:

2.大电网频率稳定控制系统一般由协控总站、控制主站、控制子站、切负荷执行站等组成,实现直流调制、减载、切机、解列等控制功能,避免严重功率缺额、频率过低、功角失稳、低频振荡等安全问题。现有大电网频率稳定控制系统,都是按照树状结构设计、垂直控制。当中间层故障后,上层厂站将失去对故障站点连接的下层厂站的控制。同时,频率稳定控制系统通信延时因受多因素影响而具有不确定性,为保证所属系统正常运行信息的提取、传输和处理周期必须设定在规定时间内完成,以保证获得系统完整的暂态信息,并在失稳或崩溃之前发出反事故紧急控制措施。因此,必须清楚地知道实时数据传输各个环节中存在的时延,并尽可能减少可避免的时延。

技术实现要素:

3.本发明的目的在于克服现有技术中的不足,提供一种基于混合型频率稳定控制系统的时延计算方法、装置及存储介质,可以计算出各控制总站至各执行站的信息传输时延,为混合型频率稳定控制系统设计和配置提供参考依据

4.为达到上述目的,本发明是采用下述技术方案实现的:

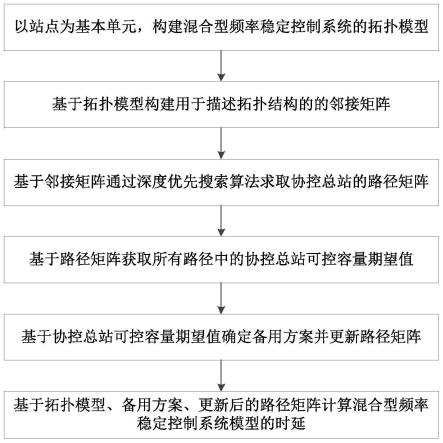

5.第一方面,本发明提供了一种基于混合型频率稳定控制系统的时延计算方法,包括:

6.以站点为基本单元,构建混合型频率稳定控制系统的拓扑模型;所述站点包括协控总站、控制总站和执行站;

7.基于拓扑模型构建用于描述拓扑结构的邻接矩阵;

8.基于邻接矩阵通过深度优先搜索算法求取协控总站的路径矩阵;

9.基于路径矩阵获取所有路径中的协控总站可控容量期望值;

10.基于协控总站可控容量期望值确定备用方案并更新路径矩阵;

11.基于拓扑模型、备用方案、更新后的路径矩阵计算混合型频率稳定控制系统模型的时延。

12.可选的,所述邻接矩阵为:

13.m=[m

ij

](i,j=1,2,...,n)

[0014]

其中,n为邻接矩阵的阶数,n=x y z,x为协控总站数量,y为控制主站数量,z为执行站数量。

[0015]

可选的,所述基于邻接矩阵通过深度优先搜索算法求取所述混合型频率稳定控制系统模型的路径矩阵包括:

[0016]

寻找并判断邻接矩阵m第i行中从t 1列至n列中是否存在非0元素c;

[0017]

若存在,则将元素c压入栈中,并判断元素c是否为待确定层级的站点m,若是,则从栈底到栈顶依次输入路径信息,并削去栈顶;若否,则将元素c赋值给行数i,并重复执行上述步骤;若不存在,则进入下一步;

[0018]

将栈顶元素赋值给t,削去栈顶,判断栈内是否为空,若是,则协控总站到待确定层级站点m的所有路径已经全部找到,并输出路径矩阵;若否,则将当前栈顶元素值赋值给行数i,并重复执行上述步骤;

[0019]

其中,初始化t=0,协控总站i=1为根节点。

[0020]

可选的,所述基于路径矩阵获取所有路径中的协控总站可控容量期望值包括:

[0021]

计算协控总站i对执行站j的可控容量期望值为:

[0022][0023]

其中,λ

station

表示站点故障率,o表示协控总站i对执行站j的路径总数,ms表示路径s经过的站点数,pj表示执行站j的可控容量;

[0024]

基于协控总站i对执行站j的可控容量期望值获取协控总站i的可控容量期望值为:

[0025][0026]

其中,w为协控总站i所有路径控制的执行站数量;

[0027]

基于协控总站i的可控容量期望值获取所有路径中的协控总站i可控容量期望值为:

[0028][0029]

其中,x为协控总站数量。

[0030]

可选的,所述基于协控总站可控容量期望值确定备用方案并更新路径矩阵包括:

[0031]

判断协控总站i可控容量期望值e(p)是否小于预设阈值f,

[0032]

若是,则启用备用方案,所述备用方案包括按照控制容量大小启动协控总站i的备用站,并逐步启动至协控总站i可控容量期望值e(p)达到阈值f要求;根据备用启动方案,更新路径矩阵;若否,则不启动协控总站i的备用站。

[0033]

可选的,所述基于拓扑模型、备用方案、更新后的路径矩阵计算混合型频率稳定控制系统模型的时延包括:

[0034]

计算通信通道的权值系数为:

[0035][0036]

其中,s

ms

和s

mn

表示协控总站和控制总站的站点容量,n

h,ms

表示第h条路径中协控总站的站点总数,n

h,mn

表示第h条路径中控制总站的站点总数;

[0037]

计算频率稳定控制系统协控总站p至执行站q通信时延t

p,q

为:

[0038][0039]

其中,t0在所述频率稳定控制系统运行时可视为常量;t0=t

send

t

equip

,t

send

为发送时延,t

equip

为装置时延,t

trans(h)

表示第h条路径上的传输时延。

[0040]

第二方面,本发明提供了一种基于混合型频率稳定控制系统的时延计算装置,所述装置包括:

[0041]

拓扑模型构建模块,用于以站点为基本单元,构建混合型频率稳定控制系统的拓扑模型;所述站点包括协控总站、控制总站和执行站;

[0042]

邻接矩阵构建模块,用于基于拓扑模型构建用于描述拓扑结构的邻接矩阵;

[0043]

路径矩阵获取模块,用于基于邻接矩阵通过深度优先搜索算法求取协控总站的路径矩阵;

[0044]

期望值获取模块,用于基于路径矩阵获取所有路径中的协控总站可控容量期望值;

[0045]

路径矩阵更新模块,用于基于协控总站可控容量期望值确定备用方案并更新路径矩阵;

[0046]

时延计算模块,用于基于拓扑模型、备用方案、更新后的路径矩阵计算混合型频率稳定控制系统模型的时延。

[0047]

第三方面,本发明提供了一种基于混合型频率稳定控制系统的时延计算装置,包括处理器及存储介质;

[0048]

所述存储介质用于存储指令;

[0049]

所述处理器用于根据所述指令进行操作以执行根据上述方法的步骤。

[0050]

第四方面,本发明提供了一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该程序被处理器执行时实现上述方法的步骤。

[0051]

与现有技术相比,本发明所达到的有益效果:

[0052]

本发明实施例提供的一种基于混合型频率稳定控制系统的时延计算方法、装置及存储介质,(1)本发明提出了一种树状和环状混合的频率稳定控制系统拓扑结构,相对于传统树状控制结构,环状结构优点在于大大提高了频率稳定控制系统的控制能力和可靠性,并且减少了系统层级,降低了故障概率与投资成本;(2)频率稳定控制系统为保证稳定运行,各级站点会设置备用站点,为降低备用启动成本,根据故障发生后运行的协控总站可控容量期望是否满足阈值条件确定协控总站的备用启动方案;(3)针对频率稳定控制系统时延问题,考虑协控总站的站点备用方案、控制路径传输时延,计算各协控总站到执行站的时延数据。计算结果可为混合型频率稳定控制系统结构设计提供参考。

附图说明

[0053]

图1是本发明实施例提供的一种基于混合型频率稳定控制系统的时延计算方法的流程图;

[0054]

图2是本发明实施例提供的现有电网频率稳定控制系统树状拓扑结构示意图;

[0055]

图3是本发明实施例提供的树状和环状混合的频率稳定控制系统拓扑结构示意图;

[0056]

图4是本发明实施例提供的通过深度优先搜索算法求取协控总站的路径矩阵的流程图。

具体实施方式

[0057]

下面结合附图对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

[0058]

实施例一:

[0059]

现有电网频率稳定控制系统树状拓扑结构,如图1所示,包括三个层级:协控层、控制层、执行层(v表示站点)。

[0060]

树状和环状混合的频率稳定控制系统拓扑结构,如图2所示,协控总站ms用于收集全网信息,自动识别电网运行方式,综合判断系统故障并控制决策,向控制站发送控制命令;控制主站mn用于接收协控总站下发的控制命令及其他重要信息,进行本站就地控制,向有关执行站发送控制命令,根据功能不同通常可分为直流、抽蓄和切负荷站;执行站ex用于接收上一级子站或主站下发的控制命令,并按要求选择被控对象,进行输出控制;

[0061]

树状和环状混合的频率稳定控制系统是指在连接多层级的控制主站同级站点间增加横向联系,形成环状控制网络,实现频率稳定控制系统的扁平化设计,并保留部分树状结构。考虑到直流控制站容量大,层级多,因此在直流控制站形成环状控制结构,。

[0062]

如图3所示,本发明提供的一种基于混合型频率稳定控制系统的时延计算方法,包括:

[0063]

s1、以站点为基本单元,构建混合型频率稳定控制系统的拓扑模型;所述站点包括协控总站、控制总站和执行站;

[0064]

设混合型频率稳定控制系统共有x个协控总站,y个控制主站,z个执行站,则所述协控总站可表示为:ms1,

…

,ms

x

,所述控制主站可表示为:mn1,

…

,mny,所述协控总站可表示为:ex1,

…

,exz。

[0065]

s2、基于拓扑模型构建用于描述拓扑结构的邻接矩阵;

[0066]

邻接矩阵为:

[0067]

m=[m

ij

](i,j=1,2,...,n)

[0068]

其中,n为邻接矩阵的阶数,n=x y z,x为协控总站数量,y为控制主站数量,z为执行站数量。

[0069]

s3、基于邻接矩阵通过深度优先搜索算法求取协控总站的路径矩阵;

[0070]

深度优先搜索算法求取过程,如图4所示:

[0071]

寻找并判断邻接矩阵m第i行中从t 1列至n列中是否存在非0元素c;

[0072]

若存在,则将元素c压入栈中,并判断元素c是否为待确定层级的站点m,若是,则从栈底到栈顶依次输入路径信息,并削去栈顶;若否,则将元素c赋值给行数i,并重复执行上述步骤;若不存在,则进入下一步;

[0073]

将栈顶元素赋值给t,削去栈顶,判断栈内是否为空,若是,则协控总站到待确定层级站点m的所有路径已经全部找到,并输出路径矩阵;若否,则将当前栈顶元素值赋值给行数i,并重复执行上述步骤;

[0074]

其中,初始化t=0,协控总站i=1为根节点。

[0075]

s4、基于路径矩阵获取所有路径中的协控总站可控容量期望值;

[0076]

计算协控总站i对执行站j的可控容量期望值为:

[0077][0078]

其中,λ

station

表示站点故障率,o表示协控总站i对执行站j的路径总数,ms表示路径s经过的站点数,pj表示执行站j的可控容量;

[0079]

基于协控总站i对执行站j的可控容量期望值获取协控总站i的可控容量期望值为:

[0080][0081]

其中,w为协控总站i所有路径控制的执行站数量;

[0082]

基于协控总站i的可控容量期望值获取所有路径中的协控总站i可控容量期望值为:

[0083][0084]

其中,x为协控总站数量。

[0085]

s5、基于协控总站可控容量期望值确定备用方案并更新路径矩阵;

[0086]

判断协控总站i可控容量期望值e(p)是否小于预设阈值f,

[0087]

若是,则启用备用方案,备用方案包括按照控制容量大小启动协控总站i的备用站,并逐步启动至协控总站i可控容量期望值e(p)达到阈值f要求;根据备用启动方案,更新路径矩阵;若否,则不启动协控总站i的备用站。

[0088]

s6、基于拓扑模型、备用方案、更新后的路径矩阵计算混合型频率稳定控制系统模型的时延。

[0089]

计算通信通道的权值系数为:

[0090][0091]

其中,s

ms

和s

mn

表示协控总站和控制总站的站点容量,n

h,ms

表示第h条路径中协控总

站的站点总数,n

h,mn

表示第h条路径中控制总站的站点总数;

[0092]

计算频率稳定控制系统协控总站p至执行站q通信时延t

p,q

为:

[0093][0094]

其中,t0在频率稳定控制系统运行时可视为常量;t0=t

send

t

equip

,t

send

为发送时延,t

equip

为装置时延,t

trans(h)

表示第h条路径上的传输时延。

[0095]

实施例二:

[0096]

本发明实施例提供了一种基于混合型频率稳定控制系统的时延计算装置,装置包括:

[0097]

拓扑模型构建模块,用于以站点为基本单元,构建混合型频率稳定控制系统的拓扑模型;站点包括协控总站、控制总站和执行站;

[0098]

邻接矩阵构建模块,用于基于拓扑模型构建用于描述拓扑结构的邻接矩阵;

[0099]

路径矩阵获取模块,用于基于邻接矩阵通过深度优先搜索算法求取协控总站的路径矩阵;

[0100]

期望值获取模块,用于基于路径矩阵获取所有路径中的协控总站可控容量期望值;

[0101]

路径矩阵更新模块,用于基于协控总站可控容量期望值确定备用方案并更新路径矩阵;

[0102]

时延计算模块,用于基于拓扑模型、备用方案、更新后的路径矩阵计算混合型频率稳定控制系统模型的时延。

[0103]

实施例三:

[0104]

基于实施例一,本发明提供了一种基于混合型频率稳定控制系统的时延计算装置,包括处理器及存储介质;

[0105]

存储介质用于存储指令;

[0106]

处理器用于根据指令进行操作以执行根据上述方法的步骤。

[0107]

实施例四:

[0108]

基于实施例一,本发明实施例提供了一种计算机可读存储介质,其上存储有计算机程序,其特征在于,该程序被处理器执行时实现上述方法的步骤。

[0109]

本领域内的技术人员应明白,本技术的实施例可提供为方法、系统、或计算机程序产品。因此,本技术可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本技术可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0110]

本技术是参照根据本技术实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0111]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特

定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0112]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0113]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。