1.本发明涉及磁敏器件领域,具体涉及一种平面化电极结构的立体硅磁敏三极管及制作工艺方法,其涉及soi工艺、cmos工艺和介质隔离工艺。

背景技术:

2.磁敏三极管主要应用于磁场测量,因其优异的灵敏度、稳定性以及低温漂的优点,在地磁勘测、机械检测、电子罗盘等领域具有重要作用。

3.立体结构磁敏三极管,即在soi器件硅层中具有立体结构的磁敏三极管,其中基区和集电区位于soi器件硅层上表面,发射区位于soi器件硅层下表面,与sio2绝缘层交界。立体硅磁敏三极管具有磁灵敏度高、温度系数低等优异特性,但由于芯片结构立体化的原因,在制作发射极时需采用背电极制作工艺,该工艺需要对器件硅层的下表面进行刻蚀和离子注入,可控性较低,对器件的灵敏度、准确度和良品率等产生较大的影响,尤其封装对磁敏特性产生影响,给立体硅磁敏三极管的集成化、小型化和批量化造成了阻碍。

4.为突破背电极制造工艺的技术瓶颈,需设计一种立体硅磁敏三极管的平面化电极结构,降低器件制造过程中背电极制造工艺难度,使得器件具有更优异的一致性和准确度。

技术实现要素:

5.基于上述技术背景,本发明人进行了锐意进取,提出了一种平面化电极结构的立体硅磁敏三极管及其制作方法,该平面化电极结构的立体硅磁敏三极管通过soi器件硅层层内引线将发射极从器件硅层的下表面引至器件硅层的上表面,使基极、集电极和发射极均位于器件硅层的上表面,实现立体硅磁敏三极管电极的平面化;同时设置sio2介质隔离环,抑制内引线区杂质的横向扩散,突破了背电极工艺的技术瓶颈,提高了立体结构磁敏三极管的一致性和测量磁场的准确度,具有广阔的应用前景,从而完成本发明。

6.本发明第一方面在于提供一种平面化电极结构的立体硅磁敏三极管,该平面化电极结构的立体硅磁敏三极管包括器件硅层内引线5、sio2介质隔离环6和磁敏感区。

7.本发明第二方面在于提供一种制作平面化电极结构的立体硅磁敏三极管的制作工艺方法,所述方法包括以下步骤:

8.步骤1、清洗硅片,0次光刻,在硅片上表面和下表面通过干法刻蚀对版标记;

9.步骤2、清洗硅片,一次光刻,在硅片的下表面光刻隔离槽窗口,沉积sio2隔离介质,制作sio2介质隔离环6,对硅片下表面进行平坦化工艺处理;

10.步骤3、清洗硅片,在硅片下表面热氧化法生长sio2氧化层,作为离子注入缓冲层;

11.步骤4、二次光刻,光刻内引线窗口,离子注入,形成n

型重掺杂,制作器件硅层内引线5并高温退火,对硅片下表面进行平坦化工艺处理;

12.步骤5、三次光刻,光刻发射区窗口,离子注入,形成n

型重掺杂,制作发射区4并高温退火,对硅片下表面进行平坦化工艺处理;

13.步骤6、清洗硅片和第二硅片2,在第二硅片2的上表面和下表面热生长sio2层,并

将第二硅片2的上表面与硅片的下表面键合;

14.步骤7、0'次光刻,双面光刻转移硅片上表面对版标记至第二硅片2下表面;

15.步骤8、减薄硅片上表面,形成soi晶圆,减薄后的硅片称为第一硅片1,即器件硅层;

16.步骤9、四次光刻,光刻集电极负载电阻r

l

窗口和基极负载电阻rb窗口,离子注入,在第一硅片1的上表面形成n-型掺杂,制作集电极负载电阻r

l

和基极负载电阻rb;

17.步骤10、五次光刻,光刻集电区窗口,离子注入,形成n

型重掺杂,制作集电区7并高温退火;

18.步骤11、六次光刻,光刻基区窗口,离子注入,形成p

型重掺杂,制作基区8并高温退火;

19.步骤12、清洗第一硅片1,在第一硅片1上表面沉积sio2层,作为绝缘层;

20.步骤13、七次光刻,在第一硅片1的上表面刻蚀引线孔,蒸镀金属al层;

21.步骤14、八次光刻,刻蚀金属,形成发射极e、集电极c、基极b、互连线和压焊点,金属合金化工艺,形成欧姆接触;

22.步骤15、清洗,在第一硅片1的上表面沉积氮化硅(si3n4),作为钝化层;

23.步骤16、九次光刻,刻蚀钝化层,形成压焊点;

24.步骤17、清洗键合片,中测,划片,无磁化封装。

25.本发明提供的平面化电极结构的立体硅磁敏三极管及制作工艺方法具有以下优势:

26.(1)本发明给出的立体硅磁敏三极管平面化电极结构,通过将发射极引至soi器件硅层上表面,降低了封装过程中发射极对器件特性的影响,提高了磁敏感特性一致性和准确度。

27.(2)本发明给出的平面化电极结构的立体硅磁敏三极管,实现了立体硅磁敏三极管的电极平面化制作,突破了背电极工艺的技术瓶颈。

28.(3)本发明基于soi工艺提出了平面化电极结构的立体硅磁敏三极管制作工艺方法,易于芯片集成化,为小型化、批量化生产提供了更广阔的前景。

附图说明

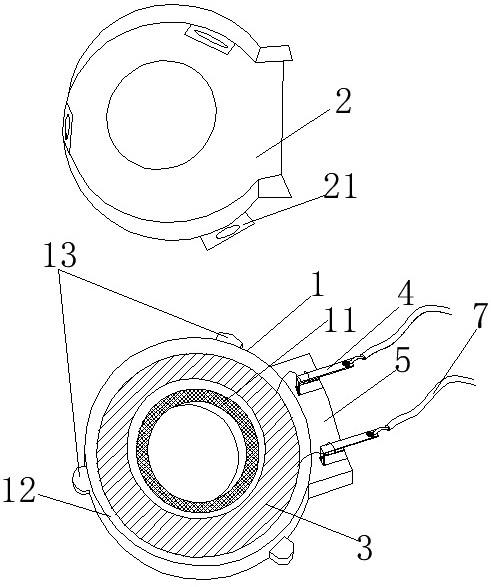

29.图1示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管示意图;

30.图2示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管俯视图;

31.图3示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管等效电路图;

32.图4-1~4-12示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管制作工艺流程图;

33.图5-1和图5-2示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管三维器件仿真模型图;

34.图6示出沿图5-1中剖视线aa'的剖视图;

35.图7-1示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管i

c-v

ce

特性曲线图;

36.图7-2示出一种立体硅磁敏三极管i

c-v

ce

特性曲线图;

37.图8-1示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管磁敏特性曲线图;

38.图8-2示出一种立体硅磁敏三极管磁敏特性曲线图;

39.图9-1示出本发明一种优选实施方式的平面化电极结构的立体硅磁敏三极管温度特性曲线图;

40.图9-2示出一种立体硅磁敏三极管温度特性曲线图。

41.附图标号说明

42.1-第一硅片;

43.2-第二硅片;

44.31-sio2绝缘层ι;

45.32-sio2绝缘层ⅱ;

46.33-sio2绝缘层ⅲ;

47.4-发射区;

48.5-器件硅层内引线;

49.6-sio2介质隔离环;

50.7-集电区;

51.8-基区;

52.e-发射极;

53.c-集电极;

54.b-基极;

55.r

b-基极负载电阻;

56.r

l-集电极负载电阻;

[0057]vdd-电源;

[0058]

gnd-接地;

[0059]vout-输出电压。

具体实施方式

[0060]

下面将对本发明进行详细说明,本发明的特点和优点将随着这些说明而变得更为清楚、明确。

[0061]

本发明第一方面在于提供一种平面化电极结构的立体硅磁敏三极管,所述平面化电极结构的立体硅磁敏三极管制作在第一硅片1和第二硅片2组成的soi晶圆(即soi器件硅层)上,第二硅片2位于第一硅片1的下方,第二硅片2的上表面与第一硅片1的下表面键合。

[0062]

所述第一硅片1的厚度为15~40μm,优选为15μm。

[0063]

第一硅片1优选为近本征p型单晶硅片,更优选为具有《100》晶向的近本征p型单晶硅片。

[0064]

第一硅片1的电阻率大于100ω

·

cm,优选为200ω

·

cm。

[0065]

第二硅片2的厚度为450~600μm,优选为500μm。

[0066]

优选地,在第一硅片1和第二硅片2之间设置sio2绝缘层ⅱ32,所述sio2绝缘层ⅱ32的厚度为0.3~1.2μm,优选为1μm。

[0067]

所述第一硅片1包括sio2介质隔离环6、磁敏感区和器件硅层内引线5,在第一硅片1的上表面设置sio2绝缘层ι31,sio2绝缘层ι31的厚度为0.1~0.2μm,优选厚度为0.1μm。

[0068]

所述sio2介质隔离环6位于第一硅片1,并贯穿第一硅片1,sio2介质隔离环6在第一硅片1中形成多个隔离区域,如图1和图2所示,磁敏感区位于该隔离区域中。

[0069]

通过设置sio2介质隔离环6可抑制杂质的横向扩散,并对磁敏感区起到隔离作用,有利于改善磁敏三极管性能。

[0070]

更优选地,设置sio2介质隔离环6将第一硅片1分隔成四个隔离区域,分别为第一区域、第二区域、第三区域和第四区域。

[0071]

进一步将磁敏感区等分别设置在上述四个区域中,可避免各部分之间出现干扰,进一步提高磁敏三极管磁敏特性。

[0072]

根据本发明一种优选地实施方式,所述磁敏感区包括基极b、集电极c、发射极e、发射区4、集电区7、基区8。

[0073]

所述基极b、集电极c和发射极e位于soi器件硅层(即第一硅片1)的上表面。

[0074]

本发明中器件硅层内引线5位于soi器件硅层内部,并贯穿第一硅片1,通过设置soi器件硅层内引线5将发射极e引至器件硅层的上表面,使基极b、集电极c和发射极e均位于soi器件硅层的上表面,即立体硅磁敏三极管的上表面,在同一平面上实现基极b、集电极c和发射极e的制作。有效避免了背电极工艺对磁敏特性的影响,提高了磁敏三极管特性的一致性和准确度,简化了磁敏器件的封装工艺。

[0075]

具体地,器件硅层内引线5位于发射极e和发射区4之间,所述发射区4位于第一硅片1下表面与sio2绝缘层ⅱ32的交界。本发明通过设置器件硅层内引线5实现了立体硅磁敏三极管的电极平面化。

[0076]

优选地,所述器件硅层内引线5为n

型重掺杂,掺杂浓度为1e19~1e20cm-3

,优选为1e20cm-3

。

[0077]

所述发射区4的掺杂类型为n

型重掺杂,掺杂浓度为1e19~1e20cm-3

,优选为1e20cm-3

。

[0078]

所述集电区7与集电极c相连,位于第一硅片1上表面并与sio2绝缘层ι31交界。

[0079]

优选地,所述集电区7的掺杂类型为n

型重掺杂,掺杂浓度为1e15~1e16cm-3

,优选为1e15cm-3

。

[0080]

所述基区8与基极b相连,位于第一硅片1上表面并与sio2绝缘层ι31交界。

[0081]

优选地,所述基区8的掺杂类型为p

型重掺杂,掺杂浓度为1e18~1e19cm-3

,优选掺杂浓度为1e18cm-3

。

[0082]

所述磁敏感区还包括基极负载电阻rb,基极负载电阻rb位于第一硅片1上表面并与sio2绝缘层ι31交界,基极负载电阻rb一端与基极b相连,另一端与电源v

dd

相连,如图1、图2和图3所示。

[0083]

所述磁敏感区还包括集电极负载电阻r

l

,集电极负载电阻r

l

位于第一硅片1上表面并与sio2绝缘层ι31交界,集电极负载电阻r

l

一端与集电极c相连,另一端与电源v

dd

相连,如

图1、图2和图3所示。

[0084]

优选地,所述集电极负载电阻r

l

和基极负载电阻rb均为n-型轻掺杂区,掺杂浓度均为5e14~5e15cm-3

,优选为5e14cm-3

,阻值均为1.0~3.0kω,优选为1.5kω。

[0085]

根据本发明一种优选地实施方式,所述基极b、集电极c、集电区7、基区8和发射区4位于第二区域内,发射极e和器件硅层内引线5位于第三区域内,集电极负载电阻r

l

位于第四区域内,基极负载电阻rb位于第一区域内。

[0086]

通过在上述各部分之间设置sio2介质隔离环6可进一步抑制磁敏感区内各部分介质的横向扩散,降低相互之间的影响,有利于磁敏三极管磁灵敏度的提高和温度漂移降低。

[0087]

位于器件硅层内引线5和发射区4相连区域不设置sio2介质隔离环6,避免sio2介质隔离环6阻断器件硅层内引线5和发射区4的连接。器件硅层内引线5和发射区4相连区域的宽度为3~5μm,优选为3μm。

[0088]

所述发射极e接地gnd,集电极c和集电极负载电阻r

l

连接处作为输出电压v

out

端。

[0089]

在第二硅片2的下表面设有sio2层ⅲ33,对该平面化电极结构的立体硅磁敏三极管起保护作用,sio2层ⅲ33的厚度为0.1~0.2μm,优选为0.1μm。

[0090]

本发明所述平面化电极结构的立体硅磁敏三极管的三维器件仿真模型图如图5-1和图5-2所示,其沿图5-1中剖视线aa'的剖视图如图6所示。

[0091]

本发明第二方面在于提供一种制作本发明第一方面所述平面化电极结构的立体硅磁敏三极管的制作工艺方法,所述方法包括以下步骤:

[0092]

步骤1、清洗硅片,0次光刻,在硅片上表面和下表面通过干法刻蚀对版标记。如图4-1所示。

[0093]

所述硅片优选为近本征p型单晶硅片,更优选为具有《100》晶向的近本征p型单晶硅片。

[0094]

硅片的电阻率大于100ω

·

cm,优选为200ω

·

cm。

[0095]

清洗工序优选采用rca标准清洗法。

[0096]

步骤2、清洗硅片,一次光刻,在硅片的下表面光刻隔离槽窗口,淀积sio2隔离介质,制作sio2介质隔离环6,对硅片下表面进行平坦化工艺处理。如图4-2所示。

[0097]

所述干法工艺对硅片刻蚀,刻蚀深度优选为15~40μm,更优选为15μm。

[0098]

所述sio2介质隔离环6位于硅片中,优选地,磁敏感区位于sio2介质隔离环6中。

[0099]

设置sio2介质隔离环6,将硅片分隔成四个隔离区域,分别为第一区域、第二区域、第三区域和第四区域,如图1、图2和图3所示。

[0100]

通过设置sio2介质隔离环6不但可以抑制杂质的横向扩散,对磁敏感区起到隔离作用,通过分隔成四个区域,可避免后续制作过程中离子注入产生的相互干扰,进而改善磁敏三极管的性能。

[0101]

在本发明一种优选地实施方式中,位于第二区域和第三区域之间的介质隔离槽在接近硅片下表面的位置预留空间,形成连接区域(请在附图中标示出预留区域的位置),如图1所示,预留区域宽度优选为3~5μm,更优选为3μm。方便后续制得的器件硅层内引线5和发射区4的连接。

[0102]

sio2介质隔离环6的宽度为1~3μm,优选为2μm。本发明人发现,sio2介质隔离环6的宽度为上述范围时即可有效起到隔离作用。

[0103]

步骤3、清洗硅片,在硅片下表面热氧化法生长sio2层,作为离子注入缓冲层。

[0104]

优选地,所述sio2氧化层由热氧化法制作得到,sio2层的厚度为30~50nm,优选厚度为30nm。

[0105]

步骤4、二次光刻,光刻器件硅层内引线窗口,离子注入,形成n

型重掺杂,制作器件硅层内引线5并高温退火,对硅片下表面进行平坦化工艺处理。如图4-3所示。

[0106]

离子注入从硅片的下表面掺杂,有利于提高器件硅层内引线5的掺杂浓度。

[0107]

优选地,通过磷注入,形成n

型重掺杂,所述掺杂浓度为1e19~1e20cm-3

,优选为1e20cm-3

。

[0108]

掺杂结束后于真空环境下进行高温退火,所述高温退火温度为900~1200℃,优选为1000℃。

[0109]

退火时间为20~50s,优选为30~40s。

[0110]

步骤5、三次光刻,光刻发射区窗口,离子注入,形成n

型重掺杂,制作发射区4并高温退火,对硅片下表面进行平坦化工艺处理。如图4-4所示。

[0111]

光刻窗口包括发射区、器件硅层内引线及二者连接区域,即通过离子注入工艺完成立体硅磁敏三极管发射区的制作以及发射区和器件硅层内引线的连接,从而实现发射区4和器件硅层内引线5的良好连接。

[0112]

根据本发明一种优选地实施方式,通过磷注入,形成n

型重掺杂,所述掺杂浓度为1e19~1e20cm-3

,优选为1e20cm-3

。

[0113]

所述掺杂结束后的退火处理在真空环境下进行,退火温度为1000~1200℃,优选退火温度为1000℃。

[0114]

退火时间为20~50s,优选为30~40s。

[0115]

步骤6、清洗硅片和第二硅片2,在第二硅片2的上表面和下表面热生长sio2层,并将第二硅片2的上表面与硅片的下表面键合。如图4-5所示。

[0116]

所述第二硅片2上表面热生长的sio2绝缘层ⅱ32的厚度为0.3~1.2μm,优选为1μm。

[0117]

第二硅片2下表面热生长的sio2绝缘层ⅲ33的厚度为0.1~0.2μm,优选厚度为0.1μm。

[0118]

步骤7、0'次光刻,双面光刻转移硅片上表面对版标记至第二硅片2下表面。

[0119]

步骤8、减薄硅片上表面,形成soi晶圆(即soi器件硅层),减薄后的硅片称为第一硅片1,如图4-6所示。

[0120]

减薄后,第一硅片1的厚度为15~40μm,优选为15μm。

[0121]

步骤9、四次光刻,光刻集电极负载电阻r

l

窗口和基极负载电阻rb窗口,离子注入,在第一硅片1的上表面形成n-型掺杂,制作集电极负载电阻r

l

和基极负载电阻rb,如图4-7所示。

[0122]

所述集电极负载电阻r

l

和基极负载电阻rb分别位于器件硅层内引线5的右侧和基区8一侧,集电极负载电阻r

l

和基极负载电阻rb分别位于sio2介质隔离环6内。

[0123]

根据本发明一种优选地实施方式,通过注入磷离子,形成n-型轻掺杂区,所述集电极负载电阻r

l

和基极负载电阻rb的掺杂浓度均为5e14~5e15cm-3

,优选为5e14cm-3

,阻值均为1.0~3.0kω,优选为1.5kω。

[0124]

步骤10、五次光刻,光刻集电区窗口,离子注入,形成n

型重掺杂,制作集电区7并高温退火。如图4-8所示。

[0125]

通过磷注入,形成n

型重掺杂,集电区7掺杂浓度为1e15~1e16cm-3

,优选为1e15cm-3

。

[0126]

所述掺杂结束后的退火处理在真空环境下进行,退火温度为1000~1200℃,优选退火温度为1000℃。

[0127]

退火时间为20~50s,优选为30~40s。

[0128]

步骤11、六次光刻,光刻基区窗口,离子注入,形成p

型重掺杂,制作基区8并高温退火。如图4-9所示。

[0129]

优选地,通过硼注入,形成p

型重掺杂。

[0130]

基区8的掺杂浓度为1e18~1e19cm-3

,优选为1e18cm-3

。

[0131]

所述掺杂结束后的退火处理在真空环境下进行,退火温度为1000~1200℃,优选退火温度为1000℃。

[0132]

退火时间为20~50s,优选为30~40s。

[0133]

步骤12、清洗第一硅片1,在第一硅片1的上表面沉积sio2层,作为绝缘层。

[0134]

所述清洗工序优选采用rca标准清洗法。

[0135]

sio2层优选采用化学气相沉积工艺制作,其厚度为0.1~0.2μm,优选厚度为0.1μm。

[0136]

步骤13、七次光刻,在第一硅片1的上表面刻蚀引线孔,蒸镀金属al层。

[0137]

优选al作为金属层。

[0138]

步骤14、八次光刻,刻蚀金属,形成发射极e、集电极c、基极b、互连线和压焊点,金属合金化工艺,形成欧姆接触。如图4-10所示。

[0139]

所述合金化工艺优选在真空或氮气环境下进行,合金化温度为300~500℃,优选为420℃,合金化时间为20~40min,优选为30min。

[0140]

步骤15、清洗,在第一硅片1的上表面沉积,作为钝化层。如图4-11所示。

[0141]

所述钝化层优选为si3n4层,沉积方式优选为化学气相沉积。

[0142]

钝化层的厚度为0.1~0.2μm,优选为0.1μm。

[0143]

步骤16、九次光刻,刻蚀钝化层形成压焊点。如图4-12所述。

[0144]

步骤17、清洗键合片,中测,划片,无磁化封装。

[0145]

本发明所具有的有益效果:

[0146]

本发明所述的平面化电极结构的立体硅磁敏三极管及制作工艺方法不仅具有立体硅磁敏三极管的i

c-v

ce

特性、磁敏特性以及温度特性,而且改善了磁敏三极管的i

c-v

ce

特性,提高了磁敏感特性一致性,降低了温度漂移。尤其本发明提出的平面化电极结构的立体硅磁敏三极管及其工艺方法解决了背电极工艺难题,有效提升了磁敏感三极管的性能,对立体硅磁敏三极管器件的集成化具有重要意义。

[0147]

实施例

[0148]

以下通过具体实例进一步阐述本发明,这些实施例仅限于说明本发明,而不用于限制本发明范围。

[0149]

实施例1

[0150]

采用下列步骤制作平面化电极结构的立体硅磁敏三极管:

[0151]

步骤1、采用rca标准清洗法清洗《100》晶向的近本征p型单晶硅片,0次光刻,在硅片上表面和下表面通过干法刻蚀对版标记,硅片杂质浓度1e11cm-3

。

[0152]

步骤2、清洗硅片,一次光刻,采用深槽刻蚀工艺在硅片的下表面刻蚀隔离槽窗口,刻蚀深度为15μm,通过化学气相沉积法沉积二氧化硅隔离介质,制作sio2介质隔离环6,sio2介质隔离环6的宽度为2μm。

[0153]

设置sio2介质隔离环6,将硅片分隔成四个隔离区域,从左至右分别为第一区域、第二区域、第三区域和第四区域,在位于第二区域和第三区域之间的介质隔离槽在接近硅片下表面的位置不沉积sio2,形成预留区域,预留区域宽度为3μm。

[0154]

步骤3、清洗硅片,在硅片的下表面通过热氧化法生长sio2氧化层,sio2层的厚度为30nm。

[0155]

步骤4、二次光刻,光刻器件硅层内引线窗口,通过磷注入,形成n

型掺杂,掺杂浓度为1e20cm-3

,于1000℃下在真空环境下高温退火30~40s。

[0156]

步骤5、三次光刻,光刻窗口,通过磷注入,形成n

型重掺杂,掺杂浓度为1e20cm-3

。制作发射区并高温退火,退火于真空环境下进行,退火温度为1000℃,退火时间为30~40s。退火结束后采用化学机械平坦化去除硅片下表面的二氧化硅层。

[0157]

步骤6、清洗第二硅片2,在第二硅片2的上表面热生长二氧化硅层,即sio2绝缘层ⅱ32的厚度为1μm,键合硅片下表面和第二硅片2上表面。

[0158]

第二硅片2下表面热生长的sio2绝缘层ⅲ33的厚度为0.1μm。

[0159]

步骤7、0'次光刻,双面光刻转移硅片上表面对版标记至第二硅片2下表面。

[0160]

步骤8、减薄硅片上表面,形成soi晶圆,减薄后的硅片称为第一硅片1,第一硅片1的厚度为15μm。

[0161]

步骤9、四次光刻,通过注入磷离子,在第一硅片1的上表面形成n-型轻掺杂区,制作集电极负载电阻r

l

和基极负载电阻rb,掺杂浓度均为5e14cm-3

,阻值均为1.5kω。

[0162]

所述集电极负载电阻r

l

窗口和基极负载电阻rb分别位于器件硅层内引线5右侧和基区8左侧。

[0163]

步骤10、五次光刻,光刻集电区窗口,通过磷注入,形成n

型重掺杂,掺杂浓度为1e15cm-3

,制作集电区7,掺杂后于1000℃退火30~40s。

[0164]

步骤11、六次光刻,光刻基区窗口,通过硼注入,形成p

型重掺杂,掺杂浓度为1e18cm-3

,制作基区8,掺杂后于1000℃,退火30~40s。

[0165]

步骤12、采用rca标准清洗法清洗第一硅片1,在第一硅片1的上表面沉积sio2氧化层,作为绝缘层,厚度为0.1μm。

[0166]

步骤13、七次光刻,在第一硅片1的上表面刻蚀引线孔,蒸镀金属al层。

[0167]

步骤14、八次光刻,刻蚀金属al,形成发射极e、集电极c、基极b、互连线和压焊点,于真空环境下进行金属合金化,合金化温度为420℃,合金化时间为30min,形成欧姆接触。

[0168]

步骤15、清洗,在第一硅片1的上表面通过化学气相沉积法沉积si3n4层,作为钝化层,厚度为0.1μm。

[0169]

步骤16、九次光刻,刻蚀钝化层形成压焊点。

[0170]

步骤17、清洗键合片,中测,划片,无磁化封装。

[0171]

对比例

[0172]

制作立体硅磁敏三极管用于对比分析,该器件除了不包括器件硅层内引线和sio2介质隔离环,其他工艺参数与实施例1所提出器件完全一致。发射区通过背电极制作工艺制作完成。

[0173]

实验例

[0174]

实验例1i

c-v

ce

特性测试

[0175]

对本发明实施例1和对比例的磁敏三极管进行i

c-v

ce

特性测试,在室温(t=300k)且无外加磁场条件下,设定如下条件:集电极电压v

ce

的范围为0~5v,步长为0.25v,基极电流ib的范围为0~5ma,步长为1ma。测试结果分别如图7-1和图7-2所示。

[0176]

由图7-1和图7-2可知,集电极电流ic低于基极电流ib,即立体硅磁敏三极管的电流放大系数β小于1。在ib=5ma,v

ce

=5v时,本发明实施例1所述的平面化电极结构的立体硅磁敏三极管集电极电流ic取得最大值3.15ma,在相同条件下立体硅磁敏三极管集电极电流ic为3.19ma。本发明实施例1所述的平面化电极结构的立体硅磁敏三极管i

c-v

ce

特性优于一般的立体硅磁敏三极管。

[0177]

实验例2磁灵敏度测试

[0178]

对本发明实施例1所述的平面化电极结构的立体硅磁敏三极管和对比例所述的立体硅磁敏三极管进行磁灵敏度测试,在室温(t=300k)时,设定如下条件:集电极电压v

ce

的范围为0~5v,步长为0.25v,基极电流ib为5ma,在磁敏感方向分别施加

±

0.3t的磁场。测试结果分别如图8-1和图8-2所示。

[0179]

由图8-1和图8-2可知,本发明实施例1所述的平面化电极结构的立体硅磁敏三极管磁灵敏度为0.41ma/t,立体硅磁敏三极管磁灵敏度为0.36ma/t,本发明提出的电极平面化方法可以有效提高立体硅磁敏三极管的磁灵敏度特性。

[0180]

实验例3温度特性测试

[0181]

图9-1和图9-2分别示出本发明实施例1所述平面化电极结构的立体硅磁敏三极管和对比例所述立体硅磁敏三极管的温度特性,在无外加磁场时,设定条件如下:集电极电压v

ce

的范围为0~5v,步长为0.25v,基极电流ib的范围为0~5ma,步长为1ma,环境温度的范围为-40℃~85℃,步长20℃。

[0182]

由图9-1和图9-2可知,立体硅磁敏三极管和本发明实施例1所述的平面化电极结构的立体硅磁敏三极管都具有负温度系数

ɑ

,其中平面化电极结构的立体硅磁敏三极管温度系数为-5235ppm/℃,立体硅磁敏三极管温度系数为-5342ppm/℃。平面化电极结构的立体硅磁敏三极管有效降低了温度漂移。

[0183]

在本发明的描述中,需要说明的是,术语“上”、“下”、“内”、“外”、“前”、“后”等指示的方位或位置关系为基于本发明工作状态下的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”、“第四”仅用于描述目的,而不能理解为指示或暗示相对重要性。

[0184]

在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”“相连”“连接”应作广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体的连接普通;可以是机械连接,也可以是电连接;可以是直接连接,也可以通过中间媒介间接连接,可

以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

[0185]

以上结合了优选的实施方式对本发明进行了说明,不过这些实施方式仅是范例性的,仅起到说明性的作用。在此基础上,可以对本发明进行多种替换和改进,这些均落入本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。