1.本实用新型涉及芯片烧录领域,尤其涉及一种芯片烧录电路和烧录器。

背景技术:

2.带芯片的pcba(printed circuit board assembly,装配印刷电路板)在出厂之前,需要在芯片中烧录程序代码,以便芯片能正常运行。工作人员一般使用烧录器对芯片进行烧录,当芯片插入到烧录器的插槽中时,工作人员按压烧录按钮后烧录器执行烧录过程,整个烧录过程效率不高。

技术实现要素:

3.本技术实施例提供了的芯片烧录电路和烧录器,可以解决相关技术中烧录芯片效率不高的问题。所述技术方案如下:

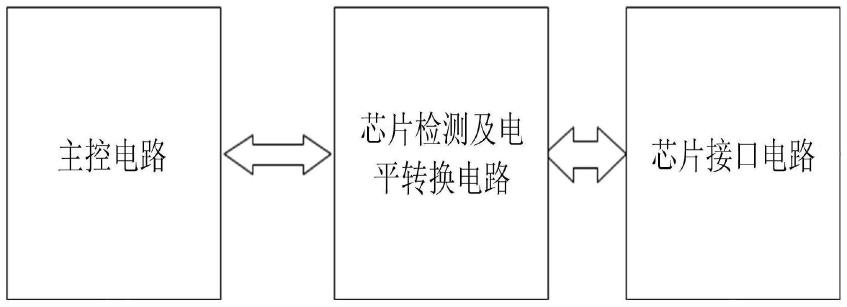

4.第一方面,本技术实施例提供了一种芯片烧录电路,包括:

5.主控电路、芯片检测及电平转换电路和芯片接口电路;

6.其中,所述主控电路包括微控制器;所述芯片检测及电平转换电路包括电平转换芯片、第一电阻、第二电阻、第三电阻、第四电阻、第一电容、第二电容和第一三极管,所述电平转换芯片的型号为sn74lvc1t45;所述芯片接口电路包括芯片插座,所述芯片插座用于插入待烧录的芯片;

7.所述第一电容的第一端接地,所述第一电容的第二端分别与第一直流电源和所述电平转换芯片的vcca引脚相连;所述第二电容的第一端分别与所述电平转换芯片的vcvb引脚和第二直流电源相连,所述第二电容的第二端接地;所述电平转换芯片的gnd引脚接地;所述电平转换芯片的dir引脚与所述微控制器的第一io引脚相连;所述电平转换芯片的a引脚通过所述第一电阻与所述微控制器的第二io引脚相连;所述电平转换芯片的b引脚通过所述第二电阻的第一端相连,所述第二电阻的第二端分别与所述芯片的swdio引脚和所述第三电阻的第一端相连,所述第三电阻的第二端通过所述第四电阻与所述第一三极管的射极相连;所述第一三极管的集电极与所述第二直流电源相连,所述第一三极管的基极与所述微控制器的第三io引脚相连。

8.第二方面,本技术提供了一种烧录器,包括:包括上述任意一种芯片烧录电路。

9.本技术一些实施例提供的技术方案带来的有益效果至少包括:

10.烧录器在上电后,微控制器通过芯片在io引脚上检测到低电平信号输入时,确定芯片插入芯片接口电路作好烧录准备,然后微控制器自动实现芯片裸片或芯片控制板的自动烧录功能,减少人为按压烧录开关控制烧录时间的操作,因此可以增加芯片烧录效率。

附图说明

11.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅

是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

12.图1~3是本实用新型实施例提供的芯片烧录电路的结构示意图;

13.图4是本实用新型提供的声音输出电路的结构示意图;

14.图5是本实用新型提供的指示灯电路的结构示意图。

具体实施方式

15.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

16.请参阅图1至图3,本实用新型提供实施例的一种芯片烧录电路的结构示意图,芯片烧录电路包括:主控电路、芯片检测及电平转换电路、芯片接口电路。

17.其中,主控电路包括微控制器u3;芯片检测及电平转换电路包括电平转换芯片u4、第一电阻r45、第二电阻r47、第三电阻r42、第四电阻r50、第一电容c34、第二电容c26和第一三极管q3,电平转换芯片u4的型号为sn74lvc1t45,电平转换芯片u4支持双向通信具有可配置电压转换和三态输出的单位双电源总线收发器。芯片接口电路包括芯片插座,芯片插座用于插入待烧录的芯片,芯片插座的数量可以为多个,以便芯片烧录电路同时对多个芯片进行烧录,提高烧录的效率。

18.上述部件的连接关系为:第一电容c34的第一端接地,第一电容c34的第二端分别与第一直流电源3v3和电平转换芯片u4的vcca引脚相连。第二电容c26的第一端分别与电平转换芯片u4的vcvb引脚和第二直流电源v_dut相连,第二电容c26的第二端接地,第一电容c34和第二电容c26的容值可以相等,例如:均为0.1μf。电平转换芯片u4的gnd引脚接地;电平转换芯片u4的dir引脚与微控制器u3的第一io引脚pc10相连;电平转换芯片u4的a引脚通过第一电阻r45与微控制器的第二io引脚swdio_i(即pb5引脚)相连;电平转换芯片u4的b引脚通过第二电阻r47的第一端相连,第二电阻r47的第二端分别与芯片的swdio引脚swdio和第三电阻r42的第一端相连,芯片的swdio引脚用于传输烧录数据,第三电阻r42的第二端通过第四电阻r50与第一三极管q3的射极相连;第一三极管q3的集电极与第二直流电源v_dut相连,第一三极管q3的基极与微控制器u3的第三io引脚pc0相连。芯片的swdio(serial wire debug input output,串行线调试输入输出)引脚是一种调试接口,通过swd协议进行通信,一般设置是arm芯片支持的一种协议。

19.需要说明的是,本技术的主控电路除包括上述的元器件之外,还可能包括其他外围器件(参见图2所示的外围器件),外围器件的类型和连接关系此处不再赘述。

20.其中,芯片烧录电路的工作过程包括:上电后,微控制器在第三io引脚pc0上输出低电平信号,第一三极管q3处于截止状态。当芯片未接入芯片接口电路时,芯片的swdio引脚swdio处于弱上拉状态,当芯片接入到芯片接口电路时,芯片的swdio引脚swdio转换为低电平状态,电平转换芯片u4检测到b引脚上输出低电平信号转换为微控制器u3匹配的低电平信号,微控制器u3在swdio_i引脚上检测到低电平信号时,确定有芯片接入,然后对芯片自动进行烧录,不需要用户按压烧录按钮执行烧录流程,从而提高烧录的效率。当不需要执

行自动化烧录功能时,微控制器u3可以在第三io引脚pc0上输出高电平信号。

21.在一个或多个可能的实施例中,主控电路还包括晶振电路,晶振电路包括第三电容c10、第四电容c11和晶振y1;晶振y1的第一端分别与微控制器u3的第一时钟引脚xo和第三电容c10的第一端相连,晶振y1的第二端分别与微控制器u3的第二时钟引脚xi和第四电容c11的第一端相连;第三电容c10的第二端接地,第四电容c11的第二端接地。晶振电源作为微控制器的外部时钟源,为微控制器提供精确的时钟信号。

22.在一个或多个可能的实施例中,第三电阻r42和第四电阻r50的阻值均为2兆欧姆,以便实现swdio引脚的弱上拉状态。

23.在一个或多个可能的实施例中,参见图4所示,芯片烧录电路还包括:声音输出电路;

24.其中,声音输出电路包括:第五电阻r35、第六电阻r36、第七电阻r37、第二三极管u6和蜂鸣器l5。第五电阻r35的第一端分别与第一直流电源3v3和蜂鸣器l 1的正极 相连,第五电阻r 35的第二端分别与第六电阻r 36的第一端和蜂鸣器l5的负极-相连。第六电阻r36的第二端与第二三极管u6的集电极相连,第二三极管u6的基极通过第七电阻r37与微控制器的第四io引脚buz(即pc13引脚)相连;第二三极管u6的射极接地。生成输出电路用于输出各种类型的提示音,例如:成功检测到芯片的提示音、烧录成功的提示音和烧录失败的提示音等。

25.进一步的,第一直流电源3v3的输出电压为3.3v。

26.在一个或多个可能的实施例中,参见图5所示,芯片烧录电路还包括:

27.指示灯电路。

28.其中,指示灯电路包括:第一发光二极管l1、第二发光二极管l2、第三发光二极管l3、第四发光二极管l4、第八电阻r5、第九电阻r6、第十电阻r7和第十一电阻r8。第一发光二级管l1的阳极与第二发光二极管l2、第三发光二极管l3和第四发光二极管l4的阳极相连;第一发光二极管l1的阴极通过第八电阻r5接地,第二发光二极管l2的阴极通过第九电阻r6与微控制器的第五io引脚led2(即pa1引脚)相连,第三发光二极管l3的阴极通过第十电阻r7与微控制器的第六io引脚led3(即pa0引脚)相连,第四发光二极管l4的阴极通过第十一电阻r8与微控制器u3的第七io引脚led1(即pa4引脚)相连。指示灯电路用于发出各种类型的提示光,例如:烧录过程中,第一发光二极管l1发出红光;烧录器处于忙碌状态时,第二发光二极管l2发出红光;烧录成功时,第三发光二极管l3发出蓝光;烧录失败时,第四发光二极管l4发出红光。

29.进一步的,微控制器的型号为apm32f103xc,该微控制器是基于32位内核,内置2个can,兼容2.0a和2.0b(主动)规范,通信速率最高可达1mbit/s,可同时保证通信可靠性同时提升实时性;支持usb和can接口同时独立工作。

30.本技术实施例提供的烧录器除包括上述的芯片烧录电路之外,还可以包括:用于容纳各个部件的壳体、显示屏和输入装置(例如:键盘、鼠标或触摸屏)等。

31.以上所述的实施方式,并不构成对该技术方案保护范围的限定。任何在上述实施方式的精神和原则之内所作的修改、等同替换和改进等,均应包含在该技术方案的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。