转译器件、包括转译器件的测试系统和存储器系统

1.相关申请的交叉参考

2.本技术基于并要求2020年12月15日向韩国知识产权局提交的韩国专利申请no.10-2020-0175831的优先权,其公开内容通过引用整体并入本文。

技术领域

3.本公开涉及一种存储器件,更具体地,涉及一种用于转译信号类型的转译器件、包括转译器件的测试系统以及包括转译器件的存储器系统。

背景技术:

4.随着设备之间发送和接收的数据容量的增加以及对高速率数据传送的需求的增加,已经提出了各种信号调制模式。在各种信号调制模式中,脉冲幅度调制(pam)-n模式可以在单位间隔期间发送一个符号。例如,根据pam-2模式,可以在单位间隔期间发送一位,并且pam-2模式可以被称为不归零(nrz)模式。例如,根据pam-4模式,可以在单位间隔期间发送两位。如上所述,可能难以在分别发送和接收基于不同信号调制模式而调制的输入/输出信号的设备之间发送和接收信号,因此,需要用于转译不同信号模式的转译器件。

技术实现要素:

5.根据一个或多个实施例的一方面,提供了一种转译器件,包括:多个第一输入/输出(i/o)电路,被配置为基于脉冲幅度调制(pam)-m模式,通过多个引脚分别发送和接收第一信号;至少一个第二i/o电路,被配置为基于pam-n模式,通过至少一个引脚发送和接收第二信号;以及转译电路,被配置为将第一信号转译为第二信号,并将第二信号转译为第一信号,其中m和n是2或更大的不同整数。

6.根据一个或多个实施例的另一方面,提供了一种转译器件,包括:第一输入/输出(i/o)电路,被配置为基于脉冲幅度调制(pam)-m模式发送和接收第一信号;第二i/o电路,被配置为基于pam-n模式发送和接收第二信号;转译电路,被配置为将第一信号转译为第二信号并将第二信号转译为第一信号;第一端接电路,设置在第一i/o引脚与第一i/o电路之间,并被配置为提供第一端接电阻;以及第二端接电路,设置在第二i/o引脚与第二i/o电路之间,并配置为提供第二端接电阻,其中m和n是2或更大的不同整数。

7.根据一个或多个实施例的另一方面,提供了一种测试系统,包括:自动测试设备(ate),包括第一引脚和第二引脚;被测器件(dut),包括第三引脚;以及外置测试(bot)模块,被配置为连接到ate和dut。bot模块包括:多个第一输入/输出(i/o)电路,分别连接到第一引脚和第二引脚,并被配置为基于脉冲幅度调制(pam)-m模式发送和接收第一信号;第二i/o电路,连接到第三引脚,并被配置为基于pam-n模式发送和接收第二信号;以及转译电路,被配置为将第一信号转译为第二信号,并被配置为将第二信号转译为第一信号,并且m和n是2或更大的不同整数。

8.根据一个或多个实施例的另一方面,提供了一种存储器系统,包括:第一存储器芯

片,包括第一引脚和第二引脚;第二存储器芯片,包括第三引脚;以及转译器件,被配置为连接在第一存储器芯片和第二存储器芯片之间。转译器件包括:多个第一输入/输出(i/o)电路,连接到第一引脚和第二引脚,并被配置为基于脉冲幅度调制(pam)-m模式发送和接收第一信号;第二i/o电路,连接到第三引脚,并被配置为基于pam-n模式发送和接收第二信号;以及转译电路,被配置为将第一信号转译为第二信号,并被配置为将第二信号转译为第一信号,并且m和n是2或更大的不同整数。

附图说明

9.从以下结合附图的详细描述中将更清楚地理解各个实施例,在附图中:

10.图1是示出了根据实施例的系统的框图;

11.图2是示出了根据实施例的转译器件的框图;

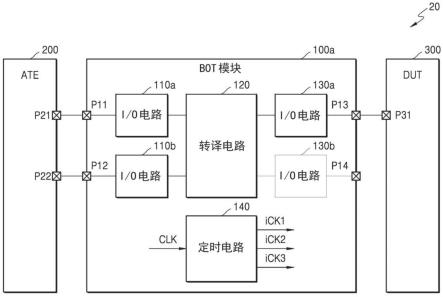

12.图3是示出了根据实施例的测试系统的框图;

13.图4a是示例性地示出了根据实施例的用于描述数据输入/输出信号的调制模式中的脉冲幅度调制(pam)-4模式的数据的曲线图;

14.图4b是示例性地示出了根据实施例的用于描述数据输入/输出信号的调制模式中的不归零(nrz)模式的数据的曲线图;

15.图5是详细示出了根据实施例的外置测试(bot)模块的框图;

16.图6是根据实施例的用于描述接收基于pam-4模式调制的数据输入信号的接收器的操作的曲线图;

17.图7是示出了根据实施例的输入/输出(i/o)电路的框图;

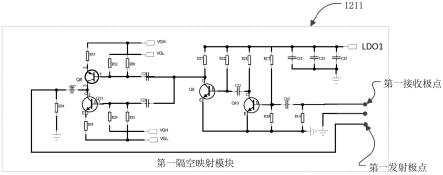

18.图8是示出了根据实施例的解码器的框图;

19.图9示例性地示出了根据实施例的将pam-4模式的数据输入信号转译成nrz模式的多个数据输出信号的操作;

20.图10示例性地示出了根据实施例的将nrz模式的数据输入信号转译成pam-4模式的多个数据输出信号的操作;

21.图11是详细示出了根据实施例的bot模块的框图;

22.图12是示出了根据实施例的选择器的框图;

23.图13是示出了根据实施例的发送器的电路图;

24.图14示例性地示出了根据实施例的将nrz模式的多个数据输入信号转译成pam-4模式的数据输出信号的操作;

25.图15示例性地示出了根据实施例的将pam-4模式的多个数据输入信号转译成nrz模式的数据输出信号的操作;

26.图16是示出了根据实施例的测试系统的框图;

27.图17和图18是示出了根据一些实施例的测试系统的框图;

28.图19a到图19c是用于描述pam-4模式的数据信号的第一摆幅间隔到第三摆幅间隔的图;

29.图20a到图20c是用于描述nrz模式的数据信号的第一摆幅间隔到第三摆幅间隔的图;

30.图21是详细示出了根据实施例的bot模块的框图;

31.图22是示出了根据实施例的串行器的框图;

32.图23示例性地示出了根据实施例的将pam-4模式的数据输入信号转译成nrz模式的数据输出信号的操作;

33.图24是详细示出了根据实施例的bot模块的框图;

34.图25是示出了根据实施例的解串器的框图;

35.图26示例性地示出了根据实施例的将nrz模式的数据输入信号转译成pam-4模式的数据输出信号的操作;

36.图27是示出了根据实施例的存储器系统的框图;

37.图28是示出了根据实施例的存储器系统的框图;

38.图29示出了根据实施例的半导体封装;以及

39.图30是示出了根据实施例的计算系统的框图。

具体实施方式

40.在下文中,将参照附图详细描述各种实施例。

41.图1是示出了根据实施例的系统10的框图。

42.参照图1,系统10可以包括转译器件100、第一设备fd和第二设备sd。第一设备fd可以发送或接收第一信号类型(即,根据第一信号调制模式调制的第一信号),第二设备sd可以发送或接收第二信号类型(即,根据第二信号调制模式调制的第二信号)。转译器件100可以设置在第一设备fd和第二设备sd之间,可以将第一信号转译为第二信号,并且可以将第二信号转译为第一信号。

43.转译器件100可以包括多个第一输入/输出(i/o)电路110a和110b、转译电路120以及多个第二i/o电路130a和130b。此外,转译器件100可以包括可连接到第一设备fd的多个i/o引脚(例如,第一引脚p11和第二引脚p12),并且第一i/o电路110a和110b可以分别连接到第一引脚p11和第二引脚p12。基于第一设备fd的i/o信号类型,可以激活第一i/o电路110a和110b中的至少一个。此外,转译器件100可以包括可连接到第二设备sd的多个i/o引脚(例如,第三引脚p13和第四引脚p14),并且第二i/o电路130a和130b可以分别连接到第三引脚p13和第四引脚p14。基于第二设备sd的i/o信号类型,可以激活第二i/o电路130a和130b中的至少一个。

44.图2是示出了根据实施例的转译器件100

′

的框图。

45.参照图2,转译器件100

′

可以包括第一接收器rx1和第二接收器rx2、转译电路120、第一发送器tx1和第二发送器tx2以及定时电路140。转译器件100

′

可以对应于图1的转译器件100的实现示例。定时电路140可以从外部时钟信号clk生成多个内部时钟信号(例如,第一内部时钟信号ick1、第二内部时钟信号ick2和第三内部时钟信号ick3)。例如,定时电路140可以包括多个分频器,因此第一内部时钟信号ick1、第二内部时钟信号ick2和第三内部时钟信号ick3的频率可以不同。然而,实施例不限于此,第一内部时钟信号ick1、第二内部时钟信号ick2和第三内部时钟信号ick3的频率中的至少两个频率可以相同。

46.第一接收器rxl和第二接收器rx2可以分别接收第一数据输入信号dq_rxl和第二数据输入信号dq_rx2,并且可以基于第一内部时钟信号ick1分别对第一数据输入信号dq_rxl和第二数据输入信号dq_rx2进行采样。在一些实施例中,可以通过一个引脚(例如,第一

引脚p11)接收数据输入信号,并且在这种情况下,可以仅激活第一接收器rx1。在一些实施例中,可以通过两个引脚(例如,第一引脚p11和第二引脚p12)接收数据输入信号,并且在这种情况下,可以激活第一接收器rx1和第二接收器rx2二者。第一接收器rx1和第二接收器rx2中的每一个可以包括多个感测放大器(例如,图7的感测放大器131a到131c)以及解码器(例如,图7的解码器132),下面将参照图7和图8描述其详细配置和操作。

47.转译电路120可以包括对准器121、数据选择器122和多路复用器(mux)123。对准器121可以基于第一内部时钟信号ick1,对准从第一接收器rx1和第二接收器rx2中的至少一个接收到的信号,从而生成对准信号s_al。数据选择器122可以从对准器121接收对准信号s_al并且可以基于第二内部时钟信号ick2从对准信号s_al生成选定信号s_sel。例如,数据选择器122可以包括串行器和解串器。多路复用器123可以从数据选择器122接收选定信号s_sel并且可以基于第三内部时钟信号ick3将选定信号s_sel多路复用以生成第一数据输出out1和第二数据输出out2。

48.第一发送器tx1和第二发送器tx2可以分别从第一数据输出out1和第二数据输出out2生成第一数据输出信号dq_tx1和第二数据输出信号dq_tx2。在一些实施例中,可以通过一个引脚(例如,第三引脚p13)发送数据输出信号,并且在这种情况下,可以仅激活第一发送器tx1。在一些实施例中,可以通过两个引脚(例如,第三引脚p13和第四引脚p14)发送数据输出信号,并且在这种情况下,可以激活第一发送器tx1和第二发送器tx2二者。例如,第一发送器tx1和第二发送器tx2中的每一个可以包括第一驱动器和第二驱动器(例如,图13的驱动器drv1和drv2),并且下面将参照图13描述其详细配置和操作。

49.图3是示出了根据实施例的测试系统20的框图。

50.参照图3,测试系统20可以包括外置测试(或外建测试)(bot)模块100a、自动测试设备(ate)200和被测器件(dut)300。bot模块100a可以包括多个第一i/o电路110a和110b、转译电路120、多个第二i/o电路130a和130b以及定时电路140。bot模块100a可以对应于图1的转译器件100和图2的转译器件100

′

中的每一个的示例,并且以上参照图1和图2给出的描述可以应用于bot模块100a,因此为了简洁起见省略了重复的描述。ate 200可以对应于图1的第一设备fd的示例,dut 300可以对应于图1的第二设备sd的示例,并且以上参照图1给出的描述可以应用于这些组件,以及为了简洁起见而省略其重复描述。

51.例如,ate 200可以包括第一引脚p21和第二引脚p22,并且第一引脚p21和第二引脚p22可以分别电连接到bot模块100a的第一引脚p11和第二引脚p12。ate 200和bot模块100a可以通过两个引脚来发送或接收i/o信号。例如,dut 300可以包括第一引脚p31,并且第一引脚p31可以电连接到bot模块100a的第三引脚p13。dut 300和bot模块100a可以通过一个引脚来发送或接收i/o信号。例如,可以不向第四引脚p14施加电信号,并且可以不激活i/o电路130b。

52.在一些实施例中,bot模块100a可以在多引脚与单个引脚之间执行信号转译。详细地,bot模块100a可以转译从第三引脚p13接收的数据输入信号以生成要提供给第一引脚p11和第二引脚p12的数据输出信号。下面将参照图5到图10描述这种转译。此外,bot模块100a可以转译从第一引脚p11和第二引脚p12接收的数据输入信号以生成要提供给第三引脚p13的数据输出信号。下面将参照图11到图15描述这种转译。

53.图4a是示例性地示出了根据实施例的用于描述数据输入/输出信号的调制模式中

的脉冲幅度调制(pam)-4模式的数据的曲线图。图4b是示例性地示出了根据实施例的用于描述数据输入/输出信号的调制模式中的不归零(nrz)模式的数据的曲线图。在图4a和图4b的曲线图中,横坐标轴可以表示时间,而纵坐标轴可以表示电压电平。

54.结合图3参照图4a,可以基于pam-4模式在dut 300和bot模块100a之间发送数据i/o信号。在这种情况下,可以生成具有第一电压电平vl1、第二电压电平vl2、第三电压电平vl3或第四电压电平vl4之一的数据i/o信号。因此,可以在单位间隔ui期间通过dut300和bot模块100a之间的数据i/o信号发送两位(例如,“11”、“10”、“01”和“00”之一)。例如,位“11”可以对应于第一电压电平vl1,位“10”可以对应于第二电压电平vl2,位“01”可以对应于第三电压电平vl3,并且位“00”可以对应于第四电压电平vl4。也就是说,可以在单位间隔ui期间生成具有第一电压电平vl1到第四电压电平vl4之一的符号,并且每个符号可以对应于两位。

55.可以基于第一参考电压vref1、第二参考电压vref2或第三参考电压vref3对基于pam-4模式发送的数据i/o信号进行采样。例如,当数据i/o信号的电压电平高于第一参考电压vref1时,可以将数据i/o信号解码为位“11”。当数据i/o信号的电压电平低于第一参考电压vref1且高于第二参考电压vref2时,可以将数据i/o信号解码为位“10”。当数据i/o信号的电压电平低于第二参考电压vref2且高于第三参考电压vref3时,可以将数据i/o信号解码为位“01”。当数据i/o信号的电压电平低于第三参考电压vref3时,可以将数据i/o信号解码为位“00”。例如,在dut 300基于pam-4模式向bot模块100a发送数据输入信号的情况下,第二i/o电路130a可以基于pam-4模式将数据输入信号的电压电平与第一参考电压vref1到第三参考电压vref3中的每一个进行比较,以获得与数据输入信号相对应的两位。

56.结合图3参照图4b,可以基于nrz模式(即,pam-2模式)在ate 200与bot模块100a之间发送数据i/o信号。在这种情况下,可以生成具有第一电压电平vl1和第四电压电平vl4之一的数据i/o信号。在一些实施例中,基于nrz模式的第一电压电平vl1可以对应于基于pam-4模式的第一电压电平vl1,并且基于nrz模式的第四电压电平vl4可以对应于基于pam-4模式的第四电压电平vl4。因此,可以在单位间隔ui期间通过dut 300和bot模块100a之间的数据i/o信号发送一位(例如,“1”和“0”之一)。例如,位“1”可以对应于第一电压电平vl1,而位“0”可以对应于第四电压电平vl4。也就是说,可以在单位间隔ui期间生成具有第一电压电平vl1和第四电压电平vl4之一的符号,并且每个符号可以对应于一位。

57.可以基于第二参考电压vref2对基于nrz模式发送的数据i/o信号进行采样。在一些实施例中,基于nrz模式的第二参考电压vref2可以对应于图4a的第二参考电压vref2。例如,当数据i/o信号dq的电压电平高于第二参考电压vref2时,可以将数据i/o信号dq解码为位“1”。当数据i/o信号dq的电压电平低于第二参考电压vref2时,可以将数据i/o信号dq解码为位“0”。例如,在ate 200基于nrz模式向bot模块100a发送数据输入信号的情况下,第一i/o电路110a可以基于nrz模式将数据输入信号的电压电平与第二参考电压vref2进行比较,以获得与数据输入信号相对应的一位。

58.在图4b中,示出了用于在nrz模式下对数据i/o信号进行采样的参考电压是第二参考电压vref2,但是实施例不限于此。例如,各种电压(例如,图4a的第一参考电压vref1或第三参考电压vref3)可以用作用于在nrz模式下对数据i/o信号进行采样的参考电压。

59.在图4a和图4b中,为了便于描述,已经描述了pam-4模式和nrz模式,但是实施例不

限于此。在一些实施例中,在基于pam-m模式在ate 200和bot模块100a之间发送数据i/o信号的情况下,可以生成具有第一电压电平到第m电压电平之一的数据i/o信号。这里,m可以是2或更大的正整数。在这种情况下,可以基于第一参考电压到第(m-1)参考电压对基于pam-m模式发送的数据i/o信号进行采样。例如,m可以是8,并且可以基于pam-8模式在ate 200和bot模块100a之间发送数据i/o信号。在这种情况下,可以在单位间隔ui期间通过ate 200和bot模块100a之间的数据i/o信号发送三位。

60.在一些实施例中,在基于pam-n模式在dut 300和bot模块100a之间发送数据i/o信号的情况下,可以生成具有第一电压电平到第n电压电平之一的数据i/o信号。这里,n可以是2或更大的正整数并与m不同。在这种情况下,可以基于第一参考电压到第(n-1)参考电压对基于pam-n模式发送的数据i/o信号进行采样。例如,n可以是16,并且可以基于pam-16模式在dut 300和bot模块100a之间发送数据i/o信号。在这种情况下,在单位间隔ui期间可以在dut 300和bot模块100a之间发送四位。

61.图5是详细示出了根据实施例的bot模块100a的框图。

62.结合图3参照图5,例如,bot模块100a可以通过第三引脚p13接收数据输入信号dq_rx并且可以通过第一引脚p11和第二引脚p12输出第一数据输出信号dq_tx1和第二数据输出信号dq_tx2。第二i/o电路130a可以包括接收器131和解码器132。接收器131可以基于第一内部时钟信号ick1对数据输入信号dq_rx进行采样,并且解码器132可以对经采样的数据输入信号进行解码以生成最高有效位msb和最低有效位lsb。

63.转译电路120a可以包括对准器121、数据选择器122以及第一多路复用器(mux)123a和第二多路复用器(mux)123b。对准器121可以基于第一内部时钟信号ick1从最高有效位msb和最低有效位lsb生成对准信号s_al。数据选择器122可以基于第二内部时钟信号ick2从对准信号s_al生成第一选定信号s_sel1和第二选定信号s_sel2。第一多路复用器123a和第二多路复用器123b可以分别从第一选定信号s_sel1和第二选定信号s_sel2生成第一数据输出out1和第二数据输出out2。

64.第一发送器tx1和第二发送器tx2可以分别从第一数据输出out1和第二数据输出out2生成第一数据输出信号dq_tx1和第二数据输出信号dq_tx2。例如,第一i/o电路110a和110b可以分别包括第一发送器tx1和第二发送器tx2。

65.图6是根据实施例的用于描述接收基于pam-4模式调制的数据输入信号dq_rx的接收器131的操作的曲线图。

66.结合图5参照图6,第一内部时钟信号ick1可以包括具有不同相位的多个第一内部时钟信号ick1[0]到ick1[3]。接收器131可以基于具有第一相位的第一内部时钟信号ick1[0]在第一时间t0处对数据输入信号dq_rx进行采样,基于具有第二相位的第一内部时钟信号ick1[1]在第二时间t1处对数据输入信号dq_rx进行采样,基于具有第三相位的第一内部时钟信号ick1[2]在第三时间t2处对数据输入信号dq_rx进行采样,并基于具有第四相位的第一内部时钟信号ick1[3]在第四时间t3处对数据输入信号dq_rx进行采样。例如,外部时钟信号clk的频率可以是第一频率f(例如,2.5ghz),并且第一内部时钟信号ick1的频率可以是第二频率f/4(例如,0.625ghz),其是通过将第一频率f除以4而生成的。

[0067]

图7是示出了根据实施例的第二i/o电路130a的框图。

[0068]

参照图7,第二i/o电路130a可以包括第一感测放大器131a、第二感测放大器131b、

第三感测放大器131c和解码器132。第一感测放大器131a到第三感测放大器131c可以包括在图5的接收器131中。第一感测放大器131a到第三感测放大器131c中的每一个可以接收数据输入信号dq_rx并且可以基于第一内部时钟信号ick1进行操作。

[0069]

第一感测放大器131a可以将数据输入信号dq_rx的电压电平与第一参考电压vref1进行比较以输出第一比较结果d_h。第二感测放大器131b可以将数据输入信号dq_rx的电压电平与第二参考电压vref2进行比较以输出第二比较结果d_m。第三感测放大器131c可以将数据输入信号dq_rx的电压电平与第三参考电压vref3进行比较以输出第三比较结果d_l。例如,当数据输入信号dq_rx的电压电平高于第一参考电压vref1时,第一感测放大器131a可以输出“1”作为第一比较结果d_h。当数据输入信号dq_rx的电压电平低于第一参考电压vref1时,第一感测放大器131a可以输出“0”作为第一比较结果d_h。

[0070]

第一感测放大器131a到第三感测放大器131c可以分别基于第一比较使能信号en1、第二比较使能信号en2和第三比较使能信号en3输出第一比较结果d_h、第二比较结果d_m和第三比较结果d_l。例如,响应于第一比较使能信号en1具有使能状态(例如,高电平),第一感测放大器131a可以将数据输入信号dq_rx的电压电平与第一参考电压vref1进行比较以输出第一比较结果d_h。响应于第一比较使能信号en1具有禁用状态(例如,低电平),第一感测放大器131a可以输出预定值(例如,“0”)作为第一比较结果d_h。同样,第二感测放大器131b和第三感测放大器131c可以分别基于第二比较使能信号en2和第三比较使能信号en3输出第二比较结果d_m和第三比较结果d_l。

[0071]

例如,在pam-4模式中,第一比较使能信号en1到第三比较使能信号en3可以在使能状态下生成。在这种情况下,第一感测放大器131a到第三感测放大器131c可以将数据输入信号dq_rx的电压电平与第一参考电压vref1到第三参考电压vref3进行比较以输出第一比较结果d_h、第二比较结果d_m和第三比较结果d_l。例如,在nrz模式下,第一比较使能信号en1和第三比较使能信号en3可以在禁用状态下生成,而第二比较使能信号en2可以在使能状态下生成。在这种情况下,第一感测放大器131a和第三感测放大器131c可以输出具有预定值(例如,“0”)的第一比较结果d_h和第三比较结果d_l,而第二感测放大器131b可以将数据输入信号dq_rx的电压电平与第二参考电压vref2进行比较,以输出第二比较结果d_m。

[0072]

解码器132可以基于解码规则对第一比较结果d_h、第二比较结果d_m和第三比较结果d_l执行解码以生成最高有效位msb和最低有效位lsb。解码规则可以预先确定。解码器132可以被称为pam-4解码器。例如,在pam-4模式下基于第一比较结果d_h、第二比较结果d_m和第三比较结果d_l生成的最高有效位msb和最低有效位lsb都可以具有有效值。例如,在nrz模式下基于第一比较结果d_h、第二比较结果d_m和第三比较结果d_l生成的最高有效位msb可以具有有效值,而最低有效位lsb可以具有无效值。也就是说,在pam-4模式下,可以并行输出两个有效位作为最高有效位msb和最低有效位lsb,而在nrz模式下,可以在第一时刻输出两个有效位中的一位作为最高有效位msb,并可以在第二时刻输出另一位作为最高有效位msb。

[0073]

如图7所示,三个感测放大器131a到131c可以用于在pam-4模式下从数据输入信号dq_rx获得两位(即,最高有效位msb和最低有效位lsb)。然而,实施例不限于此,(n-1)个感测放大器(即,第一感测放大器到第(n-1)感测放大器)可以用于在pam-n模式下从数据输入信号dq_rx获得n位。在这种情况下,在pam-n模式下,第一感测放大器到第(n-1)感测放大器

可以分别将数据输入信号dq_rx的电压电平与第一参考电压到第(n-1)参考电压进行比较以输出第一比较结果到第(n-1)比较结果,而在nrz模式下,第一感测放大器到第(n-1)感测放大器可以将数据输入信号dq_rx的电压电平与第一参考电压到第(n-1)参考电压中的某个参考电压(例如,具有中间电平的参考电压)进行比较,以输出第一比较结果到第(n-1)比较结果。在nrz模式下,第一感测放大器到第(n-1)感测放大器可以输出除了与第一参考电压到第(n-1)参考电压中的某个参考电压相对应的比较结果以外的每个比较结果,作为预定值(例如,“0”)。解码器132可以基于(n-1)个比较结果执行解码以输出n位。

[0074]

图8是示出了根据实施例的解码器132的框图。

[0075]

参照图8,解码器132可以包括第一反相器1321、第二反相器1322和第三反相器1323以及第一nand门1324和第二nand门1325。第一反相器1321可以将第二比较结果d_m反相,并且第二反相器1322可以将第一反相器1321的输出反相,从而生成最高有效位msb。第一nand门1324可以对第三比较结果d_l和第二反相比较结果d_mb执行nand运算,并且第三反相器1323可以将第一比较结果d_h反相。第二nand门1325可以对第一nand门1324的输出和第三反相器1323的输出执行nand操作以生成最低有效位lsb。

[0076]

在一些实施例中,第一感测放大器131a可以基于多个4相时钟信号(即,分别具有不同相位的多个第一内部时钟信号ick[0]到ick[3])对数据输入信号dq_rx进行采样,以生成第一比较结果d_h《3:0》。同样地,第二感测放大器131b可以基于多个4相时钟信号(即,分别具有不同相位的第一内部时钟信号ick[0]到ick[3])对数据输入信号dq_rx进行采样,以生成第二比较结果d_m《3:0》。此外,第三感测放大器131c可以基于多个4相时钟信号(即,分别具有不同相位的第一内部时钟信号ick[0]到ick[3])对数据输入信号dq_rx进行采样,以生成第三比较结果d_l《3:0》。

[0077]

因此,解码器132可以用四个解码器(即,第一解码器、第二解码器、第三解码器和第四解码器)来实现。例如,第一解码器可以解码第一比较结果d_h[0]到第三比较结果d_l[0],第二解码器可以解码第一比较结果d_h[1]到第三比较结果d_l[1],第三解码器可以解码第一比较结果d_h[2]到第三比较结果d_l[2],并且第四解码器可以解码第一比较结果d_h[3]到第三比较结果d_l[3]。因此,第一解码器到第四解码器可以生成msb《3:0》和lsb《3:0》。

[0078]

图9示例性地示出了根据实施例的将基于pam-4模式的数据输入信号dq_rx转译为基于nrz模式的多个数据输出信号dq_tx1和dq_tx2的操作。

[0079]

结合图5和图6参照图9,例如,基于pam-4模式的数据输入信号dq_rx的数据传送速率可以对应于约5gbps。基于pam-4模式的数据输入信号dq_rx中的每个符号可以包括两位(即,最高有效位和最低有效位),因此,数据输入信号dq_rx的波特率可以对应于约2.5gbaud/s。在这种情况下,数据输入信号dq_rx的符号持续时间或符号间隔可以是t3(例如,400ps)。

[0080]

第二i/o电路130a可以基于多个第一内部时钟信号ick1[0]到ick1[3]对数据输入信号dq_rx执行感测放大操作dinsa,以生成最高有效位m0到m3和最低有效位l0到l3。在这种情况下,第一内部时钟信号ick1[0]到ick1[3]中的每一个的频率可以为约0.625ghz且其切换持续时间或其切换周期可以为约1.6ns,因此,第二i/o电路130a的采样持续时间或采样周期可以为约1.6ns。基于第二i/o电路130a的采样周期,最高有效位m0到m3和最低有效

位l0到l3中的每一个可以在t1(例如,1.6ns)期间保持信号电平。

[0081]

对准器121可以基于第一内部时钟信号ick1来对准最高有效位m0到m3和最低有效位l0到l3以生成对准信号s_al。在这种情况下,对准信号s_al可以在t1(例如,1.6ns)期间保持信号电平。基于第二内部时钟信号ick2,数据选择器122可以向第一多路复用器123a提供最高有效位m0到m3作为对准信号s_al中的第一选定信号s_sel1,并且可以向第二多路复用器123b提供最低有效位l0到l3作为对准信号s_al中的第二选定信号s_sel2。

[0082]

第一多路复用器123a可以基于第三内部时钟信号ick3对第一选定信号s_sel1执行4:1多路复用,以生成第一数据输出out1。第二多路复用器123b可以基于第三内部时钟信号ick3对第二选定信号s_sel2执行4:1多路复用,以生成第二数据输出out2。第一发送器tx1可以从第一数据输出out1生成第一数据输出信号dq_tx1。第二发送器tx2可以从第二数据输出out2生成第二数据输出信号dq_tx2。

[0083]

第一数据输出信号dq_tx1可以顺序地输出最高有效位m0到m3,并且每一位可以在t3(例如,400ps)期间保持信号电平。第二数据输出信号dq_tx2可以顺序地输出最低有效位l0到l3,并且每一位可以在t3(例如,400ps)期间保持信号电平。如上所述,第一数据输出信号dq_tx1和第二数据输出信号dq_tx2中的每一个的数据传送速率可以为约2.5gbps,并且第一数据输出信号dq_tx1和第二数据输出信号dq_tx2可以被并行传送,因此,总数据传送速率可以对应于约5gbps。因此,基于pam-4模式的数据输出信号dq_rx的传送速率和基于nrz模式的第一数据输出信号dq_tx1和第二数据输出信号dq_tx2中的每一个的传送速率可以保持恒定。

[0084]

图10示例性地示出了根据实施例的将基于nrz模式的数据输入信号dq_rx转译为基于pam-4模式的多个数据输出信号dq_tx1和dq_tx2的操作。

[0085]

结合图5和图6参照图10,例如,基于nrz模式的数据输入信号dq_rx的数据传送速率可以对应于约10gbps。例如,数据输入信号dq_rx中的位间隔可以是t5(例如,100ps)。第二i/o电路130a可以基于多个第一内部时钟信号ick1[0]到ick1[3]对数据输入信号dq_rx执行感测放大操作dinsa,以生成多个位m0到m7以及l0到l7。例如,第一内部时钟信号ick1[0]到ick1[3]中的每一个的频率可以为约2.5ghz且其切换持续时间或切换周期可以为约400ps,因此,第二i/o电路130a的采样周期可以为约400ps。基于第二i/o电路130a的采样周期,多个位m0到m7和l0到l7中的每一个可以在t3(例如,400ps)期间保持信号电平。

[0086]

对准器121可以基于第一内部时钟信号ick1来对准多个位m0到m7和l0到l7,以生成对准信号s_al。在这种情况下,对准信号s_al可以在t3(例如,400ps)期间保持信号电平。基于第二内部时钟信号ick2,数据选择器122可以向第一多路复用器123a提供偶数位m0、m2、m4、m6、l0、l2、l4和l6作为对准信号s_al中的第一选定信号s_sel1,并且可以向第二多路复用器123b提供奇数位m1、m3、m5、m7、l1、l3、l5和l7作为对准信号s_al中的第二选定信号s_sel2。

[0087]

第一多路复用器123a可以基于第三内部时钟信号ick3对第一选定信号s_sel1执行4:1多路复用以生成第一数据输出out1。第二多路复用器123b可以基于第三内部时钟信号ick3对第二选定信号s_sel2执行4:1多路复用以生成第二数据输出out2。第一发送器tx1可以从第一数据输出out1生成第一数据输出信号dq_tx1。第二发送器tx2可以从第二数据输出out2生成第二数据输出信号dq_tx2。

[0088]

第一数据输出信号dq_tx1可以顺序地输出与偶数位m0、m2、m4、m6、l0、l2、l4和l6相对应的偶数符号so、s2、s4和s6,并且其符号持续时间可以对应于t3(例如,400ps)。第二数据输出信号dq_tx2可以顺序地输出与奇数位m1、m3、m5、m7、l1、l3、l5和l7相对应的奇数符号s1、s3、s5和s7,并且其符号持续时间可以对应于t3。如上所述,第一数据输出信号dq_tx1和第二数据输出信号dq_tx2中的每一个的波特率可以为约2.5gbaud/s,并且第一数据输出信号dq_tx1和第二数据输出信号dq_tx2可以被并行传送,因此,总数据传送速率可以对应于约10gbps。因此,基于nrz模式的数据输出信号dq_rx的传送速率和基于pam-4模式的第一数据输出信号dq_tx1和第二数据输出信号dq_tx2中的每一个的传送速率可以保持恒定。

[0089]

图11是详细示出了根据实施例的bot模块100b的框图。

[0090]

结合图3参照图11,例如,bot模块100b可以通过第一引脚p11和第二引脚p12接收第一数据输入信号dq_rx1和第二数据输入信号dq_rx2,并且可以通过第三引脚p13输出数据输出信号dq_tx。第一i/o电路110a可以包括接收器111a和解码器112a,并且第一i/o电路110b可以包括接收器111b和解码器112b。接收器111a和111b可以基于第一内部时钟信号ick1分别对第一数据输入信号dq_rx1和第二数据输入信号dq_rx2进行采样,并且解码器112a和112b可以对经采样的第一数据输入信号和第二数据输入信号进行解码,以分别生成最高有效位msb和最低有效位lsb。

[0091]

转译电路120b可以包括对准器121、数据选择器122和多路复用器(mux)123。对准器121可以基于第一内部时钟信号ick1从最高有效位msb和最低有效位lsb生成对准信号s_al。数据选择器122可以基于第二内部时钟信号ick2从对准信号s_al生成选定信号s_sel。多路复用器123可以从选定信号s_sel生成数据输出out。发送器tx可以从数据输出out生成数据输出信号dq_tx。例如,发送器tx可以包括在第二i/o电路130a中。

[0092]

图12是示出了根据实施例的选择器150的框图。

[0093]

结合图11参照图12,在一些实施例中,选择器150可以设置在多个解码器112a和112b与对准器121之间。(注意,选择器150未在图11中示出)。选择器150可以从解码器112a接收第一最高有效位dq1_msb和第一最低有效位dq1_lsb并且可以从解码器112b接收第二最高有效位dq2_msb和第二最低有效位dq2_lsb。第一最高有效位dq1_msb和第一最低有效位dq1_lsb可以从第一数据输入信号dq_rx1生成,并且第二最高有效位dq2_msb和第二最低有效位dq2_lsb可以从第二数据输入信号dq_rx2生成。选择器150可以从第一最高有效位dq1_msb和第二最高有效位dq2_msb以及第一最低有效位dq1_lsb和第二最低有效位dq2_lsb生成最高有效位msb和最低有效位lsb,并且可以将生成的最高有效位msb和最低有效位lsb提供给对准器121。

[0094]

详细地,选择器150可以包括第一多路复用器151、第二多路复用器152、第三多路复用器153、第四多路复用器154、第五多路复用器155、第六多路复用器156、第七多路复用器157和第八多路复用器158。第一多路复用器151到第四多路复用器154可以基于接地信号vss输出第一最高有效位dq1_msb《0》到dq1_msb《3》作为最高有效位msb《0》到msb《3》。第五多路复用器155到第八多路复用器158可以输出第一最低有效位dq1_lsb《0》到dq1_lsb《3》或第二最高有效位dq2_msb《0》或dq2_msb《3》作为最低有效位lsb《0》到lsb《3》。因此,最高有效位msb可以包括最高有效位msb《0》到msb《3》,并且最低有效位lsb可以包括最低有效位

lsb《0》到lsb《3》。

[0095]

图13是示出了根据实施例的发送器tx的电路图。

[0096]

参照图13,发送器tx可以包括第一驱动器drv1和第二驱动器drv2。第一驱动器drv1可以包括第一p型(pmos)晶体管pm1、第二p型(pmos)晶体管pm2、第三p型(pmos)晶体管pm3和第四p型(pmos)晶体管pm4以及第一n型(nmos)晶体管nm1、第二n型(nmos)晶体管nm2、第三n型(nmos)晶体管nm3和第四n型(nmos)晶体管nm4。当第二位bt1为“0”时,第一pmos晶体管pm1到第四pmos晶体管pm4可以导通,并且可以基于源电压vdd将第一节点n1的电压上拉。在这种情况下,第一nmos晶体管nm1到第四nmos晶体管nm4可以关断。当第二位bt1为“1”时,第一nmos晶体管nm1到第四nmos晶体管nm4可以导通,并且可以基于接地电压vss将第一节点n1的电压下拉。在这种情况下,第一pmos晶体管pm1到第四pmos晶体管pm4可以关断。

[0097]

第二驱动器drv2可以包括第五pmos晶体管pm5和第六pmos晶体管pm6以及第五nmos晶体管nm5和第六nmos晶体管nm6。当第一位bt0为“0”时,第五pmos pm5和第六pmos pm6可以导通,并且可以基于源电压vdd将第一节点n1的电压上拉。在这种情况下,第五nmos nm5和第六nmos nm6可以关断。当第一位bt0为“1”时,第五nmos nm5和第六nmos nm6可以导通,并且可以基于接地电压vss将第一节点n1的电压下拉。在这种情况下,第五pmos pm5和第六pmos pm6可以关断。

[0098]

如图13所示,第一驱动器drv1可以包括比第二驱动器drv2更多的用于上拉和下拉的晶体管,因此,第一驱动器drv1对第一节点n1的上拉电平和下拉电平可以大于第二驱动器drv2对第一节点n1的上拉电平和下拉电平。因此,第一节点n1的电压可以基于在pam-4模式下生成的第一位bt0和第二位bt1而具有第一电压电平vl1到第四电压电平vl4之一,并且可以生成具有第一电压电平vl1到第四电压电平vl4之一的数据输出信号dq_tx。此外,第一节点n1的电压可以基于在nrz模式下生成的第一位bt0和第二位bt1而具有第一电压电平vl1和第四电压电平vl4之一,并且可以生成具有第一电压电平vl1和第四电压电平vl4之一的数据输出信号dq_tx。

[0099]

图14示例性地示出了根据实施例的将基于nrz模式的多个数据输入信号dq_rx1和dq_rx2转译为基于pam-4模式的数据输出信号dq_tx的操作。

[0100]

结合图11参照图14,nrz模式的第一数据输入信号dq_rx1可以包括奇数位d1到d15,并且nrz模式的第二数据输入信号dq_rx2可以包括偶数位d2到d14。例如,在第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中,位间隔可以对应于t3(例如,400ps)。第一i/o电路110a可以基于具有例如约0.625ghz的频率的第一内部时钟信号ick1对第一数据输入信号dq_rx1进行采样,以输出每个位间隔为t1(例如,1.6ns)的奇数位。第一i/o电路110b可以基于具有例如约0.625ghz的频率的第一内部时钟信号ick1对第二数据输入信号dq_rx2进行采样,以输出每个位间隔为t1的偶数位。

[0101]

对准器121可以接收在第一i/o电路110a中生成的奇数位作为最高有效位msb,接收在第一i/o电路110b中生成的偶数位作为最低有效位lsb,并且基于第一内部时钟信号ick1对准最高有效位msb和最低有效位lsb,以生成对准信号s_al。数据选择器122可以基于第二内部时钟信号ick2将对准信号s_al作为选定信号s_sel提供给多路复用器123。多路复用器123可以基于第三内部时钟信号ick3对选定信号s_sel执行4:1多路复用以生成数据输出out。例如,第三内部时钟信号ick3的频率可以高于第一内部时钟信号ick1和第二内部时

钟信号ick2中的每一个的频率。例如,第三内部时钟信号ick3的频率可以对应于第一内部时钟信号ick1的频率的两倍。

[0102]

发送器tx可以从数据输出out生成数据输出信号dq_tx。数据输出信号dq_tx中的符号持续时间可以对应于t3(例如,400ps)。第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中的每一个的数据传送速率可以为约2.5gbps,并且第一数据输入信号dq_rx1和第二数据输入信号dq_rx2可以并行输入,总数据传送速率可以对应于约5gbps。在这种情况下,数据输出信号dq_tx的数据传送速率可以为约5gbps,并且第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中的每一个的数据传送速率可以与数据输出信号dq_tx的数据传送速率相同。

[0103]

图15示例性地示出了根据实施例的将基于pam-4模式的多个数据输入信号dq_rx1和dq_rx2转译为基于nrz模式的数据输出信号dq_tx的操作。

[0104]

结合图11参照图15,例如,pam-4模式的第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中的每一个的数据传送速率可以对应于约5gbps,并且总数据输入速率可以为约10gbps。例如,第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中的每一个的符号持续时间或符号间隔可以是t3(例如,400ps)。

[0105]

第一i/o电路110a和110b可以分别基于分别具有第一相位到第四相位的第一内部时钟信号ick1[0]到ick1[3]对第一数据输入信号dq_rx1和第二数据输入信号dq_rx2执行感测放大操作dinsa,从而生成最高有效位m0到m7和最低有效位l0到l7。此外,第一内部时钟信号ick1[0]到ick1[3]中的每一个的频率可以为约0.625ghz并且其切换持续时间可以为约1.6ns,因此,第一i/o电路110a和110b中的每一个的采样周期可以为约1.6ns。基于第一i/o电路110a和110b中的每一个的采样周期,最高有效位m0到m7和最低有效位l0到l7中的每一个可以在t1(例如,1.6ns)期间保持信号电平。

[0106]

对准器121可以基于第一内部时钟信号ick1来对准最高有效位m0到m7和最低有效位l0到l7,以生成对准信号s_al。在这种情况下,对准信号s_al可以在t1(例如,1.6ns)期间保持信号电平。数据选择器122可以基于第二内部时钟信号ick2对对准信号s_al执行4:1串行化(即,串行),以生成选定信号s_sel。在选定信号s_sel中,每一位可以在t3期间保持信号电平。

[0107]

多路复用器123可以基于第三内部时钟信号ick3对选定信号s_sel执行4:1多路复用以生成数据输出out。发送器tx可以从数据输出out生成nrz模式的数据输出信号dq_tx。在数据输出信号dq_tx中,每一位可以在t5(例如,100ps)期间保持信号电平。数据输出信号dq_tx的数据传送速率可以是约10gbps。因此,pam-4模式的第一数据输入信号dq_rx1和第二数据输入信号dq_rx2中的每一个的数据传送速率与nrz模式的数据输出信号dq_tx的数据传送速率可以保持相等。

[0108]

图16是示出了根据实施例的测试系统20a的框图。

[0109]

参照图16,测试系统20a可以包括自动测试设备(ate)200a、外置测试(bot)模块100c和被测器件(dut)300a。测试系统20a可以对应于图3的测试系统20的修改示例。在图3中,ate 200和bot模块100a可以通过两个引脚发送或接收i/o信号。另一方面,根据图16所示的实施例,ate 200a和bot模块100c可以通过一个引脚发送或接收i/o信号。此外,在图3中,dut 300和bot模块100a可以通过一个引脚发送或接收i/o信号。另一方面,根据图16所

示的实施例,dut 300a和bot模块100c可以通过两个引脚发送或接收i/o信号。以上参照图3到图15描述的细节可以应用于图16所示的实施例,为简明起见,省略了重复的描述。

[0110]

图17是示出了根据实施例的测试系统30的框图。

[0111]

参照图17,测试系统30可以包括自动测试设备(ate)200a、外置测试(bot)模块400和被测器件(dut)300。例如,ate 200a和bot模块400可以通过一个引脚发送或接收i/o信号,dut 300和bot模块400可以通过一个引脚发送或接收i/o信号。以上参照图3到图16描述的细节可以应用于图17所示的实施例,为简明起见,省略了重复的描述。例如,在如图3所示的配置中,设置了多个第一i/o电路110a和110b,并且在这种配置中,可以对应于多个第一i/o电路110a和110b分别设置多个第一端接电路160。

[0112]

bot模块400可以包括第一i/o电路110、转译电路120、第二i/o电路130、定时电路140以及第一端接电路160和第二端接电路170。第一端接电路160可以包括多个可变电阻器(例如,第一电阻器r1和第二电阻器r2),并且第二端接电路170可以包括多个可变电阻器(例如,第三电阻器r3和第四电阻器r4)。第一端接电路160可以基于ate 200a的端接类型提供第一端接电阻。第二端接电路170可以基于dut 300的端接类型提供第二端接电阻。尽管图17示出了一个第一端接电路160和一个第二端接电路170,但是实施例不限于此。例如,在如图3所示的配置中,设置了多个第一i/o电路110a和110b,可以对应于多个第一i/o电路110a和110b分别设置多个第一端接电路160。类似地,在设置了多个第二i/o电路130a和130b的配置中,可以对应于多个第二i/o电路130a和130b分别设置多个第二端接电路170。

[0113]

更详细地,可以基于ate 200a的发送器(例如,驱动器的类型)来确定第一端接电路160的端接类型,并且可以基于dut 300的发送器(例如,驱动器的类型)来确定第二端接电路170的端接类型。第一端接电路160的端接类型可以基于中心抽头端接(ctt)类型、伪开漏(pod)类型或低电压摆幅端接逻辑(lvstl)类型来确定。同样地,第二端接电路170的端接类型可以基于ctt类型、pod类型或lvstl类型来确定。根据一些实施例,第一端接电路160的端接类型可以不同于第二端接电路170的端接类型。此外,根据一些实施例,第一端接电路160的端接类型可以与第二端接电路170的端接类型相同。

[0114]

例如,第一端接电路160的端接类型可以基于ctt类型来确定。第一电阻器r1可以连接到源电压vdd端,第二电阻器r2可以连接到接地电压vss端,并且第一引脚p11可以连接在第一电阻器r1和第二电阻器r2之间。此外,例如,第二端接电路170的端接类型可以基于ctt类型来确定。第三电阻器r3可以连接到源电压vdd端,第四电阻器r4可以连接到接地电压vss端,并且第三引脚p13可以连接在第三电阻器r3和第四电阻器r4之间。

[0115]

图18是示出了根据实施例的测试系统30a的框图。

[0116]

参照图18,测试系统30a可以包括自动测试设备(ate)200a、外置测试(bot)模块400a和被测器件(dut)300。根据图18的实施例的测试系统30a可以对应于图17的测试系统30的修改示例,并且以上参照图17描述的细节可以应用于图18所示的实施例。bot模块400a的第一端接电路160a和第二端接电路170a可以被实现为不同于bot模块400的第一端接电路160和第二端接电路170。

[0117]

例如,第一端接电路160a的端接类型可以基于pod类型来确定。第一电阻器r1可以连接在源电压vdd端和第一引脚p11之间。此外,例如,第二端接电路170a的端接类型可以基于lvstl类型来确定。第四电阻器r4可以连接在接地电压vss端和第三引脚p13之间。根据一

些实施例,第四电阻器r4可以连接到接地电压vss端,并因此,可以被称为接地类型。

[0118]

图19a到图19c是用于描述pam-4模式的数据信号的第一摆幅间隔到第三摆幅间隔的图。

[0119]

参照图18和图19a,例如,通过第三引脚p13接收的数据输入信号可以在接地电压vss与源电压或电源电压vdd的1/2(即,vdd/2)之间具有第一摆幅间隔。例如,与数据输入信号的最低电平相对应的第一电平v1a可以对应于接地电压vss,并且与数据输入信号的最高电平相对应的第四电平v4a可以对应于源电压vdd的1/2。例如,与数据输入信号的中间电平相对应的第二电平v2a和第三电平v3a可以分别对应于源电压vdd的1/6和1/3。如上所述,数据输入信号可以在接地电压vss与源电压vdd的1/2之间以第一摆幅间隔在第一电平v1a到第四电平v4a之一处摆动。多个参考电平vaa到vca可以用于区分第一电平v1a到第四电平v4a。

[0120]

参照图17和图19b,例如,通过第一引脚p11接收的数据输入信号可以在源电压vdd的1/2(即,vdd/2)与源电压vdd之间具有第二摆幅间隔。例如,与数据输入信号的最低电平相对应的第一电平v1b可以对应于源电压vdd的1/2,并且与数据输入信号的最高电平相对应的第四电平v4b可以对应于源电压vdd。与数据输入信号的中间电平相对应的第二电平v2b和第三电平v3b可以分别对应于源电压vdd的2/3和5/6。如上所述,数据输入信号可以在源电压vdd的1/2(即,vdd/2)与源电压vdd之间以第二摆幅间隔在第一电平v1b到第四电平v4b之一处摆动。多个参考电平vab到vcb可以用于区分第一电平v1b到第四电平v4b。

[0121]

参照图17和图19c,例如,通过第一引脚p11接收的数据输入信号或通过第三引脚p13接收的数据输入信号可以在源电压vdd的1/4(即,vdd/4)与源电压vdd的3/4(即,3vdd/4)之间具有第三摆幅间隔。例如,与数据输入信号的最低电平相对应的第一电平v1c可以对应于源电压vdd,并且与数据输入信号的最高电平相对应的第四电平v4c可以对应于源电压vdd的3/4。例如,与数据输入信号的中间电平相对应的第二电平v2c和第三电平v3c可以分别对应于源电压vdd的5/12和7/12。如上所述,数据输入信号可以在源电压vdd的1/4与源电压vdd的3/4之间以第三摆幅间隔在第一电平v1c到第四电平v4c之一处摆动。多个参考电平vac到vcc可以用于区分第一电平v1c到第四电平v4c。

[0122]

图20a到图20c是用于描述nrz模式的数据信号的第一摆幅间隔到第三摆幅间隔的图。

[0123]

参照图18和图20a,例如,通过第三引脚p13接收的数据输入信号可以在接地电压vss与源电压vdd的1/2(即,vdd/2)之间以第一摆幅间隔摆动。参照图18和图20b,例如,通过第一引脚p11接收的数据输入信号可以在源电压vdd的1/2与源电压vdd之间以第二摆幅间隔摆动。参照图17和图20c,例如,通过第一引脚p11接收的数据输入信号或通过第三引脚p13接收的数据输入信号可以在源电压vdd的1/4与源电压vdd的3/4之间以第三摆幅间隔摆动。

[0124]

图21是详细示出了根据实施例的bot模块400a的框图。

[0125]

参照图21,bot模块400a可以包括第二i/o电路130、转译电路120c和发送器tx。第二i/o电路130可以接收pam-4的数据输入信号dq_rx并且可以从数据输入信号dq_rx生成最高有效位msb和最低有效位lsb。例如,数据输入信号dq_rx的符号持续时间可以对应于t3(例如,400ps)。以上参照图5到图8描述的细节可以应用于第二i/o电路130。

[0126]

转译电路120c可以包括对准器121、串行器122a和多路复用器(mux)123。对准器121可以基于第一内部时钟信号ick1对准最高有效位msb和最低有效位lsb,以生成对准信号s_al。串行器122a可以基于第二内部时钟信号ick2将对准信号s_al串行化,以生成串行化信号s_se。多路复用器123可以基于第三内部时钟信号ick3对串行化信号s_se执行多路复用,以生成数据输出out。

[0127]

发送器tx可以从数据输出out生成数据输出信号dq_tx。数据输出信号dq_tx可以包括顺序输出的多个位,且其位持续时间可以是t4(例如,200ps)。例如,数据输入信号dq_rx的符号s0可以对应于数据输出信号dq_tx的位m0和l0。数据输入信号dq_rx的符号持续时间可以对应于数据输出信号dq_tx的位持续时间的两倍,因此,数据传送速率可以保持恒定。

[0128]

图22是示出了根据实施例的串行器122a的框图。

[0129]

参照图22,串行器122a可以包括第一多路复用器1221、第二多路复用器1222、第三多路复用器1223和第四多路复用器1224,并且第一多路复用器1221到第四多路复用器1224中的每一个可以基于第二内部时钟信号ick2执行2:1多路复用操作。详细地,第一多路复用器1221可以在第二内部时钟信号ick2的使能间隔中输出第一输入信号pma-4_m2,并且可以在第二内部时钟信号ick2的禁用间隔中输出第二输入信号pma-4_m0,从而输出串行化的nrz信号nrz《0》。第二多路复用器1222可以在第二内部时钟信号ick2的使能间隔中输出第一输入信号pma-4_l2,并且可以在第二内部时钟信号ick2的禁用间隔中输出第二输入信号pma-4_l0,从而输出串行化的nrz信号nrz《1》。第三多路复用器1223可以在第二内部时钟信号ick2的使能间隔中输出第一输入信号pma-4_m3,并且可以在第二内部时钟信号ick2的禁用间隔中输出第二输入信号pma-4_m1,从而输出串行化的nrz信号nrz《2》。第四多路复用器1224可以在第二内部时钟信号ick2的使能间隔中输出第一输入信号pma-4_l3,并且可以在第二内部时钟信号ick2的禁用间隔中输出第二输入信号pma-4_l1,从而输出串行化的nrz信号nrz《3》。

[0130]

图23示例性地示出了根据实施例的将pam-4模式的数据输入信号dq_rx转译成nrz模式的数据输出信号dq_tx的操作。

[0131]

参照图21和图23,例如,pam-4模式的数据输入信号dq_rx的数据传送速率可以对应于约5gbps。例如,数据输入信号dq_rx的符号持续时间或符号间隔可以是t3(例如,400ps)。第二i/o电路130可以基于第一内部时钟信号ick1[0]到ick1[3]对数据输入信号dq_rx执行感测放大操作dinsa,从而生成最高有效位m0到m3和最低有效位l0到l3。在这种情况下,第一内部时钟信号ick1[0]到ick1[3]中的每一个的频率可以是约0.625ghz并且其切换持续时间可以是约1.6ns,因此,第二i/o电路130的采样周期可以是约1.6ns。基于第二i/o电路130的采样周期,最高有效位m0到m3和最低有效位l0到l3中的每一个可以在t1(例如,1.6ns)期间保持信号电平。

[0132]

对准器121可以基于第一内部时钟信号ick1来对准最高有效位m0到m3和最低有效位l0到l3,以生成对准信号s_al。在这种情况下,对准信号s_al可以在t1(例如,1.6ns)期间保持信号电平。串行器122a可以基于第二内部时钟信号ick2对对准信号s_al执行2:1串行化,以生成串行化信号s_se。例如,第二内部时钟信号ick2的频率可以对应于第一内部时钟信号ick1的频率的两倍。例如,第二内部时钟信号ick2的频率可以是约1.25ghz。在选定信

号s_se中,每个位可以在t2(例如,800ps)期间保持信号电平。

[0133]

多路复用器123可以基于第三内部时钟信号ick3对选定信号s_se执行4:1多路复用,以生成数据输出out。例如,第三内部时钟信号ick3的频率可以高于第一内部时钟信号ick1和第二内部时钟信号ick2的频率。例如,第三内部时钟信号ick3的频率可以为约2.5ghz。发送器tx1可以从数据输出out生成数据输出信号dq_tx。数据输出信号dq_tx可以顺序地输出多个位m0到l3,并且每个位可以在t4(例如,200ps)期间保持信号电平。如上所述,数据输出信号dq_tx的数据传送速率可以是约5gbps,并且数据输入信号dq_rx的数据传送速率可以保持恒定。

[0134]

图24是详细示出了根据实施例的bot模块400b的框图。

[0135]

参照图24,bot模块400b可以包括接收器rx、转译电路120d和发送器tx。接收器rx可以接收nrz模式的数据输入信号dq_rx并且可以基于第一内部时钟信号ick1对数据输入信号dq_rx进行采样。例如,数据输入信号dq_rx可以包括顺序输出的多个位,且其位持续时间可以是t4(例如,200ps)。

[0136]

转译电路120d可以包括对准器121、解串器122b和多路复用器(mux)123。对准器121可以基于第一内部时钟信号ick1从接收器rx的输出生成对准信号s_al。解串器122b可以基于第二内部时钟信号ick2从对准信号s_al生成解串信号s_de。多路复用器123可以从解串信号s_de生成数据输出out。

[0137]

发送器tx可以从数据输出out生成数据输出信号dq_tx。数据输出信号dq_tx可以包括顺序输出的多个符号,且其符号持续时间可以是t3(例如,400ps)。因此,数据输入信号dq_rx的数据传送速率可以与数据输出信号dq_tx的数据传送速率相同。

[0138]

图25是示出了根据实施例的解串器122b的框图。

[0139]

参照图25,解串器122b可以包括多个触发器ff11到ff43,并且多个触发器ff11到ff43可以基于第二内部时钟信号ick2和第二反相内部时钟信号ickb2进行操作。对准信号s_al可以包括nrz信号nrz《3:0》。在这种情况下,对准信号s_al的位持续时间可以是t2(例如,800ps)。

[0140]

触发器f11可以基于第二内部时钟信号ick2接收nrz《0》,触发器f12可以基于第二反相内部时钟信号ickb2接收触发器f11的输出,以生成pam-4_m0。触发器f13可以基于第二反相内部时钟信号ickb2接收nrz《0》,以生成pam-4_m2。触发器f11到f13的描述可以应用于触发器f21到f43。如上所述,解串器122b可以对对准信号s_al执行1:2解串以生成解串信号s_de。在这种情况下,解串信号s_de的位持续时间或位周期可以是t1(例如,1.6ns)。

[0141]

图26示例性地示出了根据实施例的将nrz模式的数据输入信号dq_rx转译成pam-4模式的数据输出信号dq_tx的操作。

[0142]

参照图24到图26,nrz模式的数据输入信号dq_rx可以包括多个位d0到d7。例如,数据输入信号dq_rx中的位间隔可以对应于t2(例如,800ps)。对准器121可以基于第一内部时钟信号ick1对准由接收器rx生成的位,以生成对准信号s_al。解串器122b可以基于第二内部时钟信号ick2对对准信号s_al执行1:2解串,以生成解串信号s_de。解串信号s_de中的位持续时间可以是t1(例如,1.6ns)。多路复用器123可以基于第三内部时钟信号ick3对解串信号s_de执行4:1多路复用,以生成数据输出out。

[0143]

发送器tx可以从数据输出out生成数据输出信号dq_tx。数据输出信号dq_tx中的

符号持续时间可以对应于t3(例如,400ps)。数据输入信号dq_rx的数据传送速率可以是约5gbps,并且数据输出信号dq_tx的数据传送速率可以是约5gbps。如上所述,数据输入信号dq_rx的数据传送速率可以与数据输出信号dq_tx的数据传送速率相同。

[0144]

图27是示出了根据实施例的存储器系统40的框图。

[0145]

参照图27,存储器系统40可以包括转译器件100、第一存储器芯片500和第二存储器芯片600。转译器件100可以包括多个第一i/o电路110a和110b、转译电路120以及多个第二i/o电路130a和130b,并且以上参照图1到图26描述的细节可以应用于图27所示的实施例。第一存储器芯片500可以包括第一i/o引脚p51和第二i/o引脚p52,并且第一i/o引脚p51和第二i/o引脚p52可以分别对应于转译器件100的第一引脚p11和第二引脚p12。根据一些实施例,可以激活第一i/o引脚p51和第二i/o引脚p52中的至少一个。第二存储器芯片600可以包括第一i/o引脚p61和第二i/o引脚p62,并且第一i/o引脚p61和第二i/o引脚p62可以分别对应于转译器件100的第三引脚p13和第四引脚p14。根据一些实施例,可以激活第一i/o引脚p61和第二i/o引脚p62中的至少一个。

[0146]

图28是示出了根据实施例的存储器系统40a的框图。

[0147]

参照图28,存储器系统40a可以包括转译器件100”、第一存储器芯片500a和第二存储器芯片600a。转译器件100”可以包括第一i/o电路110、转译电路120、第二i/o电路130、定时电路140以及第一端接电路160和第二端接电路170,并且以上参照图1到图26描述的细节可以应用于图28所示的实施例。第一存储器芯片500a可以包括第一i/o引脚p51,并且第一i/o引脚p51可以连接到转译器件100”的第一引脚p11。第二存储器芯片600a可以包括第一i/o引脚p61,并且第一i/o引脚p61可以连接到转译器件100”的第三引脚p13。

[0148]

图29示出了根据实施例的半导体封装1000。

[0149]

参照图29,半导体封装1000可以包括堆叠型存储器设备1100、片上系统(soc)1200、中介层1300和封装基板1400。堆叠型存储器设备1100可以包括缓冲管芯1110、多个核管芯1120、1130和1150以及转译器件1140。堆叠型存储器设备1100可以对应于以上参照图26和图27描述的存储器系统40和40a。例如,核管芯1130和1150可以具有不同的信号类型,并且转译器件1140可以在核管芯1130和1150之间转译信号类型。注意的是,图29示出了核管芯1130和核管芯1150之间的转译器件1140。然而,这仅是示例,并且在一些实施例中,转译器件1140可以根据不同核管芯的信号类型设置在其他核管芯之间。例如,在一些实施例中,转译器件1140可以设置在核管芯1130和核管芯1120之间。以上参照图1到图28描述的细节可以应用于图29所示的实施例。

[0150]

核管芯1120、1130和1150中的每一个可以包括用于存储数据的多个存储单元。缓冲管芯1110可以包括物理层1111和直接存取区(dab)1112。物理层1111可以通过中介层1300电连接到soc 1200的物理层1210。堆叠型存储器设备1100可以通过物理层1111从soc 1200接收信号,或者可以将信号发送到soc 1200。

[0151]

直接存取区1112可以提供使得能够在不通过soc 1200的情况下测试堆叠型存储器设备1100的存取路径。直接存取区1112可以包括:导电连接器(例如,端口或引脚),其可以直接与外部测试设备通信。通过直接存取区1112接收到的测试信号可以通过多个硅通孔(tsv)1101发送到核管芯1120、1130和1150以及转译器件1140。从核管芯1120、1130和1150读取的数据可以被发送到转译器件1140、tsv 1101和直接存取区1112,以测试核管芯1120、

1130和1150。因此,可以对核管芯1120、1130和1150执行直接存取测试。

[0152]

缓冲管芯1110、核管芯1120、1130和1150以及转译器件1140可以通过tsv 1101和多个凸块1102彼此电连接。缓冲管芯1110可以从soc 1200接收通过为每个通道分配的凸块1102提供给每个通道的信号,或者可以通过凸块1102向soc 1200发送信号。例如,凸块1102可以是微凸块。

[0153]

soc 1200可以通过使用堆叠型存储器设备1100执行半导体封装1000所支持的应用。例如,soc 1200可以包括中央处理单元(cpu)、应用处理器(ap)、图形处理单元(gpu)、神经处理单元(npu)、张量处理单元(tpu)、视觉处理单元(vpu)、图像信号处理器(isp)、数字信号处理器(dsp)中的至少一个,并且可以执行某些算术运算。

[0154]

soc 1200可以控制堆叠型存储器设备1100的整体操作。soc 1200可以包括物理层1210。物理层1210可以包括用于向堆叠型存储器设备1100的物理层1111发送信号或从物理层1111接收信号的接口电路。soc 1200可以通过物理层1210向物理层1111提供各种信号。提供给物理层1111的信号可以通过物理层1111的接口电路和tsv 1101而传送到核管芯1120、1130和1150以及转译器件1140。

[0155]

中介层1300可以将堆叠型存储器设备1100连接到soc 1200。中介层1300可以将堆叠型存储器设备1100的物理层1111连接到soc 1200的物理层1210并且可以提供由导电材料形成的物理路径。因此,堆叠型存储器设备1100和soc 1200可以堆叠在中介层1300上并且可以在其间发送和接收信号。

[0156]

凸块1103可以附着在封装基板1400的上部,并且焊球1104可以附着在封装基板1400的下部。例如,凸块1103可以是倒装芯片凸块。中介层1300可以通过凸块1103堆叠在封装基板1400上。半导体封装1000可以通过焊球1104向外部封装或半导体设备发送信号或从外部封装或半导体设备接收信号。例如,封装基板1400可以是印刷电路板(pcb)。

[0157]

图30是示出了根据实施例的计算系统2000的框图。计算系统2000可以用一个电子设备实现,或者可以分布到或实现在两个或更多个电子设备上。例如,计算系统2000可以用各种电子设备中的至少一种来实现,例如台式计算机、膝上计算机、平板计算机、智能手机、自动驾驶车辆、数码相机、可穿戴设备、医疗保健设备、服务器系统、数据中心、无人机、掌上游戏机、物联网(iot)设备、图形加速器和人工智能(ai)加速器。

[0158]

参照图30,计算系统2000可以包括主机2100、加速器子系统2200和互连2300。主机2100可以控制加速器子系统2200的整体操作,并且加速器子系统2200可以基于主机2100的控制来操作。主机2100可以通过互连2300连接到加速器子系统2200。可以通过互连2300在主机2100和加速器子系统2200之间发送和接收各种信号和数据。

[0159]

主机2100可以包括主机处理器2110、主机存储器控制器2120、主机存储器2130和接口电路2140。主机处理器2110可以控制计算系统2000的整体操作。主机处理器2110可以通过主机存储器控制器2120控制主机存储器2130。主机处理器2110可以通过互连2300控制与其连接的加速器子系统2200。例如,主机处理器2110可以向加速器子系统2200发送指令以将操作分配给加速器子系统2200。

[0160]

主机处理器2110可以是通用处理器或主处理器,执行与各种操作相关联的通用算术运算。例如,主机处理器2110可以是中央处理单元(cpu)或应用处理器(ap)。

[0161]

主机存储器2130可以是计算系统2000的主存储器。主机存储器2130可以存储通过

主机处理器2110处理获得的数据,或者可以存储从加速器子系统2200接收的数据。例如,主机存储器2130可以实现为动态随机存取存储器(dram)。然而,实施例不限于此,并且主机存储器2130可以包括以下项中的至少一个:诸如静态随机存取存储器(sram)等易失性存储器、和诸如闪存、相变随机存取存储器(pram)、电阻随机存取存储器(rram)和磁性随机存取存储器(mram)等非易失性存储器。

[0162]

接口电路2140可以被配置为使得主机2100能够与加速器子系统2200进行通信。主机处理器2110可以通过接口电路2140向加速器子系统2200发送控制信号和数据,并且可以从加速器子系统2200接收信号和数据。在一些实施例中,主机处理器2110、主机存储器控制器2120和接口电路2140可以实现为一个芯片。

[0163]

加速器子系统2200可以基于主机2100的控制执行特定功能。例如,加速器子系统2200可以基于主机2100的控制执行适合特定应用的算术运算。加速器子系统2200可以与主机2100物理连接或电连接,或者可以实现为诸如模块、卡、封装、芯片和设备等各种类型,以便无线地或有线地连接到主机2100。例如,加速器子系统2200可以实现为图形卡或加速器卡。例如,加速器子系统2200可以基于现场可编程门阵列(fpga)或专用集成电路(asic)来实现。

[0164]

在一些实施例中,加速器子系统2200可以基于各种封装技术之一来实现。例如,加速器子系统2200可以用诸如球栅阵列(bga)、多芯片封装(mcp)、封装上系统(sop)、封装内系统(sip)、封装上封装(pop)、芯片级封装(csp)、晶片级封装(wlp)或面板级封装(plp)等封装技术来实现。在一些实施例中,加速器子系统2200的一些或所有元件可以通过铜对铜接合而彼此连接。在一些实施例中,加速器子系统2200的一些或所有元件可以通过诸如硅中介层、有机中介层、玻璃中介层或有源中介层等中介层而彼此连接。在一些实施例中,加速器子系统2200的一些或所有元件可以基于tsv而堆叠。在一些实施例中,加速器子系统2200的一些或所有元件可以通过高速连接路径(例如,硅桥)彼此连接。

[0165]

加速器子系统2200可以包括专用处理器2210、本地存储器控制器2220、本地存储器2230和主机接口电路2240。专用处理器2210可以基于主机处理器2110的控制进行操作。例如,专用处理器2210可以响应于主机处理器2110的指令通过本地存储器控制器2220从本地存储器2230读取数据。专用处理器2210可以基于读取的数据执行算术运算以处理数据。专用处理器2210可以将处理后的数据传送到主机处理器2110,或者可以将处理后的数据写入本地存储器2230。

[0166]

专用处理器2210可以基于本地存储器2230中存储的值来执行适合特定应用的算术运算。例如,专用处理器2210可以执行适合于诸如人工智能(ai)(例如,专用处理器2210可以是ai引擎)之类的应用的算术运算、流分析、视频转码、数据索引、数据编码/解码和数据加密。因此,专用处理器2210可以处理各种类型的数据,例如图像数据、语音数据、运动数据、生物数据和键值。例如,专用处理器2210可以包括gpu、npu、tpu、vpu、isp和dsp中的至少一种。

[0167]

专用处理器2210可以包括一个处理器核,或者可以包括多个处理器核,例如双核、四核和六核。在一些实施例中,例如在涉及适合于并行处理的算术运算的配置中,专用处理器2210可以包括比主机处理器2110更多的核。例如,专用处理器2210可以包括1000个或更多个核。

[0168]

本地存储器控制器2220可以控制本地存储器2230的整体操作。在一些实施例中,本地存储器控制器2220可以执行纠错码(ecc)编码和ecc解码,基于循环冗余校验(crc)执行数据验证,或执行数据加密和数据解密。

[0169]

本地存储器2230可以被专用处理器2210用作专用存储器。本地存储器2230可以实现为dram,但是实施例不限于此。例如,本地存储器2230可以包括诸如sram等易失性存储器和诸如闪存、pram、rram和mram等非易失性存储器中的至少一个。在一些实施例中,本地存储器2230可以与专用处理器2210一起安装在一个基板上,或者可以实现为诸如管芯、芯片、封装、模块、卡和设备等各种类型,以便基于单独的连接器连接到专用处理器2210。本地存储器2230可以对应于以上参照图27到图29描述的存储器系统40和40a或堆叠型存储器设备1100。

[0170]

在一些实施例中,本地存储器2230可以包括用于执行一些算术运算的逻辑电路。逻辑电路可以对从本地存储器2230读取的数据或要写入本地存储器2230的数据执行线性运算、比较运算、压缩运算、数据转译运算和算术运算。因此,可以减小通过逻辑电路的处理而得到的数据的大小。当数据大小减小时,可以提高本地存储器2230和本地存储器控制器2220之间的带宽效率。

[0171]

主机接口电路2240可以被配置为使得加速器子系统2200能够与主机2100执行通信。加速器子系统2200可以通过主机接口电路2240向主机2100发送信号和数据并且可以从主机2100接收控制信号和数据。在一些实施例中,专用处理器2210、本地存储器控制器2220和主机接口电路2240可以实现为一个芯片。

[0172]

互连2300可以提供主机2100和加速器子系统2200之间的数据传送路径并且可以充当数据总线或数据链路。数据传送路径可以通过有线或无线方式形成。接口电路2140和主机接口电路2240可以基于预定协议通过互连2300彼此通信。例如,接口电路2140和2240可以基于以下各种标准执行通信:例如高级技术附件(ata)、串行ata(sata)、外部sata(e-sata)、小型计算机小型接口(scsi)、串行附加scsi(sas)、外围组件互连(pci)、pci express(pcie)、nvm express(nvme)、高级可扩展接口(axi)、arm微控制器总线架构(amba)、ieee 1394、通用串行总线(usb)、安全数字(sd)卡、多媒体卡(mmc)、嵌入式多媒体卡(emmc)、通用闪存(ufs)、紧凑型闪存(cf)和gen-z。备选地,接口电路2140和2240可以基于设备之间的通信链路执行通信,例如开放相干加速器处理器接口(capi)、加速器的高速缓存相干互连(ccix)、计算快速链路(cxl)和nvlink。备选地,接口电路2140和2240可以基于无线通信技术执行通信,例如长期演进(lte)、第五代(5g)、lte机器(lte-m)、窄带物联网(nb-iot)、低功耗广域网(lpwan)、蓝牙、近场通信(nfc)、zigbee、z-wave或无线局域网(wlan)。

[0173]

在一些实施例中,加速器子系统2200还可以包括用于感测图像数据、语音数据、运动数据、生物数据和外围环境信息的传感器。在一些实施例中,当加速器子系统2200中包括传感器时,传感器可以基于上述封装技术连接到其他元件(例如,专用处理器2210和本地存储器2230)。加速器子系统2200可以基于特定算术运算来处理由传感器感测的数据。

[0174]

在图30中,示出了专用处理器2210通过一个本地存储器控制器2220使用一个本地存储器2230,但实施例不限于此。例如,专用处理器2210可以通过一个本地存储器控制器2220使用多个本地存储器。作为另一示例,专用处理器2210可以通过多个本地存储器控制

器中的每一个使用与专用处理器2210相对应的本地存储器。

[0175]

虽然以上已经具体地示出和描述了各种实施例,但是将理解,在不脱离所附权利要求的精神和范围的情况下,可以在形式和细节上进行各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。