1.本发明涉及一种闪烁减轻像素阵列基板和一种用于制造闪烁减轻像素阵列基板的方法。

背景技术:

2.安装在机动车辆上的相机包括具有像素阵列的图像传感器。像素阵列包括被配置用于强光检测的第一组像素和被配置用于弱光检测的第二组像素。由此类相机捕获的图像和视频常常包括由机动车辆的日间行车灯造成的闪烁伪影。日间行车灯的光生成元件是发光二极管,其以近似一百赫兹的频率闪烁。

3.除了闪烁伪影之外,机动车辆相机常见的第二图像伪影被称为花瓣光斑。第一组像素和第二组像素中的每一组都以二维周期性阵列布置,像素间距在入射到其上的光的波长的两倍到三倍之间。许多图像传感器包括微透镜阵列,其由多个微透镜形成,每个微透镜与相应的像素对准,在像素阵列上方具有二维周期性表面高度。图像传感器的像素阵列和其上的微透镜阵列的周期性导致图像传感器类似于反射式二维衍射光栅。入射在图像传感器上的光的部分朝着相机的成像透镜衍射。相机的不同元件(例如,盖玻璃、ir截止滤光片、成像透镜的表面)将这种衍射光反射回图像传感器,这产生花瓣光斑。

技术实现要素:

4.本文公开的实施例通过对于第一组像素中的每个像素将位于像素的光电二极管上方的金属膜与填充包围像素的沟槽的金属集成来减轻闪烁伪影和花瓣光斑。

5.本发明提供了一种闪烁减轻像素阵列基板和一种用于制造闪烁减轻像素阵列基板的方法。

6.在第一方面,一种闪烁减轻像素阵列基板包括半导体基板和金属层。半导体基板包括小光电二极管区域。半导体基板的后表面在与小光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中形成包围小光电二极管区域的沟槽。金属层覆盖第一后表面区域,至少部分地填充沟槽,并在该横截面平面中包围小光电二极管区域。

7.在一些实施例中,所述第一后表面区域上方的所述金属层的厚度在0.1微米和0.3微米之间。

8.在一些实施例中,所述像素阵列基板还包括粘合层,所述粘合层覆盖所述第一后表面区域并延伸到(i)所述金属层和所述后表面的内侧壁区域之间以及(ii)所述金属层和所述后表面的外侧壁区域之间的沟槽中。

9.在一些实施例中,所述第一后表面区域上方的所述粘合层的厚度在二十纳米和五十纳米之间。

10.在一些实施例中,所述半导体基板还包括形成二乘二阵列的四个大光电二极管区域,所述小光电二极管区域位于所述二乘二阵列的中心。

11.在一些实施例中,所述半导体基板的所述后表面包括四个共面的表面区域,每个

表面区域位于所述四个大光电二极管区域中相应一个的上方,所述小光电二极管区域上方的所述金属层的顶表面与(i)所述四个共面的表面区域、(ii)在所述四个共面的表面区域中的每一个上形成的钝化层以及(iii)在所述四个共面的表面区域中的每一个上形成的蚀刻停止层之一共面。

12.在一些实施例中,所述四个大光电二极管区域包括第一大光电二极管区域、第二大光电二极管区域、第三大光电二极管区域和第四大光电二极管区域,所述半导体基板还包括附加的小光电二极管区域,所述半导体基板还包括第五大光电二极管区域和第六大光电二极管区域,所述第五大光电二极管区域和所述第六大光电二极管区域与所述第三大光电二极管区域和所述第四大光电二极管区域形成附加的二乘二阵列,所述附加的小光电二极管区域位于所述附加的二乘二阵列的中心。

13.在一些实施例中,所述半导体基板具有(i)在所述第一后表面区域和与所述后表面相对的平坦前表面之间的第一厚度,以及(ii)在所述平坦前表面和所述四个大光电二极管区域之一上方的第二后表面区域之间的超过所述第一厚度的第二厚度。

14.在一些实施例中,所述像素阵列基板还包括钝化层,所述钝化层位于所述金属层和所述半导体基板之间并且覆盖所述第一后表面区域和所述四个大光电二极管区域中的每个大光电二极管区域上方的所述后表面。

15.在一些实施例中,所述像素阵列基板还包括位于所述金属层和所述钝化层之间的蚀刻停止层。

16.在一些实施例中,所述蚀刻停止层覆盖所述四个大光电二极管区域中的每一个上方的所述钝化层,所述小光电二极管区域上方的所述金属层的顶表面与位于所述四个大光电二极管区域中的每一个上方的所述蚀刻停止层的顶表面共面。

17.在一些实施例中,所述像素阵列基板还包括位于所述第一后表面区域和所述四个大光电二极管区域中的每一个上方的缓冲层,所述金属层位于所述第一后表面区域与所述缓冲层之间。

18.在一些实施例中,所述缓冲层在所述小光电二极管区域上方具有第一厚度,并且在所述四个大光电二极管区域中的每一个上方具有超过所述第一厚度的第二厚度。

19.在一些实施例中,所述像素阵列基板还包括:在所述缓冲层上的金属网格,所述金属网格与所述沟槽对准,并且在所述小光电二极管区域上方形成孔。

20.在第二方面,一种用于制造闪烁减轻像素阵列基板的方法包括在半导体基板的后表面上形成在与小光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中包围半导体基板的小光电二极管区域的沟槽。该方法还包括在第一后表面区域上和在沟槽中形成金属层。

21.在一些实施例中,所述方法还包括,在形成所述金属层之前,在(i)所述第一后表面区域和(ii)限定出所述沟槽的所述后表面的内侧壁区域、外侧壁区域和底部区域上沉积粘合层、钝化层和蚀刻停止层中的至少一个。

22.在一些实施例中,所述方法还包括:在所述金属层上和在与所述小光电二极管区域相邻的大光电二极管区域上方沉积缓冲层。

23.在一些实施例中,沉积所述缓冲层包括将所述金属层嵌入所述缓冲层中。

24.在一些实施例中,所述半导体基板具有(i)在所述第一后表面区域和与所述后表

面相对的平坦前表面之间的第一厚度和(ii)在所述平坦前表面和与所述小光电二极管区域相邻的大光电二极管区域上方的第二后表面区域之间的超过所述第一厚度的第二厚度,形成所述金属层包括:在所述第一后表面区域和所述第二后表面区域上以及在所述沟槽中沉积初始金属层;以及通过平坦化所述金属层来移除位于所述第二后表面区域上方的所述初始金属层的区域。

25.在一些实施例中,形成所述金属层包括:在所述第一后表面区域、在与所述小光电二极管区域相邻的大光电二极管区域上方的第二后表面区域上以及在所述沟槽中沉积初始金属层;以及通过经由光掩模曝光所述金属层并蚀刻经曝光的金属层来移除位于所述第二后表面区域上方的所述初始金属层的区域。

附图说明

26.图1是车辆的示意图,安装在车辆上的相机包括图像传感器。

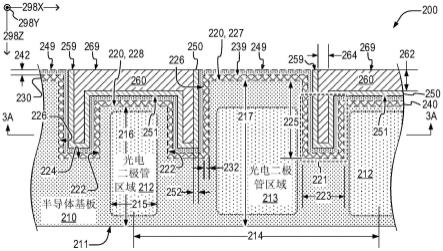

27.图2和3分别是实施例中图1的相机的闪烁减轻像素阵列基板的示意图。

28.图4是实施例中的像素阵列基板的示意图,其是图2的像素阵列基板的示例。

29.图5是图4的闪烁减轻像素阵列基板的第一实施例的示意图。

30.图6是图4的闪烁减轻像素阵列基板的第二实施例的示意图。

31.图7是实施例中在其上形成金属层之前图2的像素阵列基板的前体的横截面示意图。

32.图8是第一图像传感器的示意性横截面视图,其是图1的图像传感器的示例。

33.图9是第二图像传感器的示意性横截面视图,其是图1的图像传感器的示例。

34.图10是图示实施例中用于制造闪烁减轻像素阵列基板的方法的流程图。

具体实施方式

35.在整个说明书中对“一个示例”或“一个实施例”的引用是指结合该示例描述的特定特征、结构或特点包括在本发明的至少一个示例中。因此,在整个说明书中各处出现的短语“在一个示例中”或“在一个实施例中”不一定都是指同一个示例。此外,在一个或多个示例中,可以以任何合适的方式组合特定的特征、结构或特点。

36.为了便于描述,在本文中可以使用空间相对术语,诸如“在...之下”、“在...下方”、“下”、“在...下面”、“在...上方”、“上”等,以描述一个元件或特征与另一个(多个)元件或特征的关系,如图所示。将理解的是,除了附图中描绘的朝向之外,空间相对术语还意图涵盖设备在使用或操作中的不同朝向。例如,如果附图中的设备被翻转,那么被描述为在其他元件或特征“下方”或“之下”或“下面”的元件将被定向为在其他元件或特征“上方”。因此,术语“在...下方”和“在...下面”可以涵盖上方和下方两个朝向。可以以其他方式将设备定向(旋转九十度或以其他朝向),并相应地解释本文中使用的空间相对描述语。此外,还将理解的是,当一个层被称为在两个层“之间”时,它可以是这两个层之间的唯一层,或者也可以存在一个或多个中间层。

37.术语半导体基板可以是指使用诸如硅、硅-锗、锗、砷化镓及其组合之类的半导体形成的基板。术语半导体基板也可以是指由一种或多种半导体形成的基板,该基板经历了在基板中形成区域和/或结的先前工艺步骤。半导体基板还可以包括各种特征,诸如掺杂和

未掺杂的半导体、硅的外延层以及在基板上形成的其他半导体结构。

38.在整个说明书中,使用了几个技术术语。这些术语应具有其所属领域中的普通含义,除非在本文专门定义或者它们的使用上下文明确地暗示为其他。应当注意的是,在本文档中,元素名称和符号可以互换使用(例如,si与硅);但是,两者具有完全相同的含义。

39.图1是安装在车辆192上的相机190的示意图。相机190包括图像传感器194,其包括像素阵列基板100。图1是图像传感器194和像素阵列基板100的示例使用场景,它们中的每一个都可以在不脱离本发明范围的情况下用在其他高动态范围成像应用中。像素阵列基板100包括像素阵列112a。像素阵列基板100可以是芯片级封装或板上芯片封装的一部分。

40.图2和3分别是闪烁减轻像素阵列基板200的横截面示意图,闪烁减轻像素阵列基板200在下文中也称为像素阵列基板200。图2中所示的横截面平行于由正交轴298x和298z形成的平面,下文中称为x-z平面,正交轴298x和298z各自正交于轴298y。在本文中,x-y平面由正交轴298x和298y形成,并且平行于x-y平面的平面被称为横向平面。除非另有说明,否则本文中对象的高度是指对象沿着轴298z的范围。在本文中,对轴x、y或z的引用分别是指轴298x、298y和298z。而且,在本文中,水平平面平行于x-y平面,宽度是指对象沿着y轴的范围,并且竖直是指沿着z轴的方向。图3的横截面视图位于图2中表示的横截面平面3a中。

41.像素阵列基板200是图像传感器194的像素阵列基板100的示例并且包括半导体基板210和金属层260。半导体基板210的构成元素可以包括硅和锗中的至少一种。半导体基板210包括前表面211、后表面220和小光电二极管区域212。后表面220包括内侧壁表面区域222、外侧壁表面区域226和底表面区域224,它们形成包围小光电二极管区域212的沟槽221。在实施例中,表面区域228形成沟槽221的底表面的一部分,使得沟槽221的一部分在光电二极管区域212上方,即,在表面区域228上方。图2表示小光电二极管区域212上方的后表面220的表面区域228。在平行于后表面区域228的横截面平面3a中,沟槽221包围小光电二极管区域212并将小光电二极管区域212与相邻的大光电二极管区域213隔离。在实施例中,像素阵列基板200包括钝化层230、蚀刻停止层240和粘合层250中的至少一个。在实施例中,粘合层250用作扩散阻挡层。在实施例中,像素阵列基板缺少粘合层250。

42.金属层260沉积在小光电二极管区域212上并且至少部分地填充沟槽221以减少由小光电二极管区域212接收的光量。金属层260的一部分在半导体基板210中形成。沟槽221中的金属层260的部分减少串扰,而表面区域228上方的金属层的部分减少到达小光电二极管区域212的入射光的光强度,从而防止小光电二极管区域212在集成期间饱和,并减少闪烁伪影。常规的像素阵列基板采用分离的结构来解决串扰和闪烁伪影,而像素阵列基板200包括一个结构

–

金属层260

–

其执行这两种功能,从而简化与形成像素阵列基板200相关联的制造工艺。

43.在实施例中,构成金属层260的材料包括钨和铝中的至少一种,这两种材料都非常适合于集成电路制造工艺并适合于将光衰减到大约本文公开的金属层260的厚度处所期望的。钨和铝在可见光和近ir波长处具有吸收性,因此通过吸收入射在其上的衍射光来减少花瓣光斑伪影。

44.在表面区域228上方,金属层260具有厚度262,在实施例中,该厚度介于0.1微米的最小厚度和0.3微米的最大厚度之间。在沟槽221中,金属层260具有宽度264,在实施例中,该宽度在20纳米的最小宽度和100纳米的最大宽度之间,基于与小光电二极管区域212相关

联的期望光敏度或量子效率(qe)来配置。

45.粘合层250可以设置在金属层260和后表面220之间以提供金属层260和下面的材料层之间的粘合并防止金属离子扩散到半导体基板210中。粘合层250覆盖表面区域228(例如,小光电二极管区域的曝光区块)并延伸到(i)金属层260与内侧壁表面区域222之间以及(ii)金属层260与外侧壁表面区域226之间的沟槽221中。在实施例中,粘合层250从沟槽221的第一侧跨过相应小光电二极管区域212上方的表面区域228延伸到沟槽221的与第一侧相对的第二侧。在实施例中,粘合层250不覆盖大光电二极管区域213上方的表面区域。在实施例中,形成粘合层250的材料包括钛和氮化钛中的至少一种。粘合层250具有厚度252。在实施例中,厚度252在二十纳米和五十纳米之间。厚度252可以在竖直和/或水平方向上。

46.钝化层230覆盖后表面区域228并且位于金属层260和半导体基板210之间。在实施例中,钝化层230邻接后表面220。在实施例中,附加材料层位于钝化层和后表面220之间。附加层可以比钝化层230薄,并且可以由氧化物形成。

47.钝化层230可以共形地覆盖沟槽221的表面区域222、224和226。钝化层230可以由高κ材料形成,高κ材料例如为介电常数κ大于或等于氮化硅的介电常数(κ≥7)的材料。钝化层230可以具有固定的负电荷,从而在其与半导体基板210的表面界面处产生空穴累积层。在实施例中,形成钝化层230的示例材料包括氧化铝(al2o3)、氧化铪(hfo2)及其组合。钝化层230具有厚度232,在实施例中,该厚度在十埃的最小厚度和五百埃的最大厚度之间。当厚度232小于最小厚度时,钝化层230不再用作有效的钝化层,因为材料层包含的固定的负电荷的量与其厚度相关。当厚度232超过最大厚度时,过多的厚度不会改善钝化层230的功能,因此不必要地增加了像素阵列基板200的整体厚度。

48.蚀刻停止层240位于金属层260和钝化层230之间。在实施例中,蚀刻停止层240由氧化物材料或氮氧化物材料形成。蚀刻停止层240具有厚度242,在实施例中,该厚度242在五十纳米和三百纳米之间。

49.在实施例中,半导体基板210包括光电二极管区域212的二维阵列,其中该二维阵列的行和列的相应方向限定出轴298y和298x的相应方向。相邻的光电二极管区域212在x和y方向中的每一个上以像素间距214隔开。在实施例中,每个光电二极管区域212是在半导体基板210中形成的小像素阵列的相应像素的一部分。

50.图2表示相邻光电二极管区域212之间的后表面220的表面区域227。半导体基板210在前表面211和表面区域228之间具有第一厚度216,并且在前表面211和表面区域227之间具有第二厚度217。在实施例中,第一厚度216小于或等于第二厚度217。例如,厚度217可以以层230、240、250和260的相应厚度232、242、252和262的总和超过厚度216。在实施例中,厚度262等于厚度217与厚度216之间的差。

51.钝化层230、蚀刻停止层240和粘合层250以及金属层260具有相应的顶表面239、249、259和269。在像素阵列基板200的实施例中,当第一厚度216小于第二厚度217时,金属层260的顶表面269(上表面)与顶表面239、249和259中的至少一个共面,如图2中所示。在实施例中,金属层260的顶表面269与蚀刻停止层240的顶表面249共面。粘合层250具有底表面251。在像素阵列基板200的实施例中,当第一厚度216等于第二厚度217时,光电二极管区域212上方的底表面251的部分与顶表面239和249中的至少一个共面。

52.在实施例中,半导体基板210包括多个大光电二极管区域213,图2和3中的每一个

中示出了其中之一。每个大光电二极管区域213位于相应的一对相邻的小光电二极管区域212之间。重申一下,每个小光电二极管区域212被布置为被相邻的大光电二极管区域213包围。多个小光电二极管区域212和大光电二极管区域213形成二维阵列。在实施例中,每个小光电二极管区域212和相邻的大光电二极管区域213是在半导体基板210中形成的大像素阵列的相应像素的一部分,其中大像素阵列与包括光电二极管区域212的二维阵列的小像素阵列交错。在实施例中,每个小光电二极管区域212具有比每个大光电二极管区域213更小的满阱容量。在实施例中,大光电二极管区域213被图3的横截面平面中的深沟槽隔离结构包围。

53.沟槽221分别在水平和竖直方向上具有宽度223和深度225。宽度223可以在0.10微米和0.25微米之间。深度225相对于后表面区域227。在实施例中,厚度217以0.5微米和2.0微米之间超过深度225以确保足够的电隔离。在实施例中,沟槽221用作半导体基板210中的深沟槽隔离结构。

54.图4是像素阵列基板400的横截面示意图,像素阵列基板400是像素阵列基板200的示例。图4的横截面视图位于图2中所示的横截面平面3a中。图4表示横截面2a,其是图2的横截面平面的示例。像素阵列基板400包括多个小光电二极管区域412和多个大光电二极管区域413,它们分别是小光电二极管区域212和多个大光电二极管区域213的示例。每个小光电二极管区域位于大光电二极管区域413的相应二乘二阵列的中心。例如,小光电二极管区域412(1)位于大光电二极管区域413(1

–

4)的二乘二阵列的中心,而小光电二极管区域412(2)位于大光电二极管区域413(3

–

6)的二乘二阵列的中心。

55.在实施例中,大光电二极管区域413中的每一个都定位为与小光电二极管区域412相邻并且包围相应的小光电二极管区域412。例如,小光电二极管区域412(2)被大光电二极管区域413(3)、413(4)、413(5)和413(6)包围。每个小光电二极管区域412通过深沟槽隔离结构与和其相邻的大光电二极管区域413电和光隔离,其中深沟槽隔离结构包括钝化层230、蚀刻停止层240、粘合层250和金属层260。

56.在实施例中,每个小光电二极管区域412是在半导体基板410中形成的小像素阵列416a的相应像素的一部分,并且每个大光电二极管区域413是在半导体基板410中形成的大像素阵列417a的相应像素的一部分。像素阵列基板400是像素阵列基板100的示例,使得在实施例中,像素阵列112a包括小像素阵列416a和大像素阵列417a。半导体基板410是半导体基板210的示例。

57.图5是闪烁减轻像素阵列基板500的横截面示意图,闪烁减轻像素阵列基板500是像素阵列基板400的示例。像素阵列基板500包括具有厚度516和517的半导体基板510。半导体基板510以及厚度516和517分别是图2的半导体基板210以及像素阵列基板200的厚度216和217的示例。厚度517超过厚度516。半导体基板510包括多个小光电二极管区域512和包围每个小光电二极管区域512的多个大光电二极管区域513,它们分别是小光电二极管区域212和大光电二极管区域213的示例。半导体基板510具有后表面520,后表面520是后表面220的示例,因此包括表面区域522、524和526,它们分别是表面区域222、224和226的示例。表面区域522、524和526限定出沟槽521,沟槽521是沟槽221的示例。后表面520还包括后表面220的其他表面区域(诸如表面区域227和228)的类似物。

58.在实施例中,像素阵列基板500包括在每个小光电二极管区域512和每个大光电二

极管区域513上方的缓冲层570。缓冲层570具有均匀的厚度572并且可以由氧化物形成。在实施例中,厚度572在0.1微米和0.3微米之间。

59.在实施例中,像素阵列基板500包括多个深沟槽隔离结构,这些深沟槽隔离结构形成在相应沟槽521中,彼此互连并以包围每个小光电二极管区域512和每个大光电二极管区域513的网格形式形成,在它们之间提供隔离。

60.在实施例中,像素阵列基板500包括钝化层530、蚀刻停止层540和粘合层550中的至少一个,它们是钝化层230、蚀刻停止层240和粘合层250的相应示例。每个深沟槽隔离结构包括钝化层530、蚀刻停止层540和粘合层550,以及沉积的金属层560。层530、540、550、560具有相应的厚度532、542、552和562,它们是厚度232、242、252和262的相应示例。厚度517以相应厚度532、542、552和562的总和超过厚度516。

61.在实施例中,像素阵列基板500包括在缓冲层570的顶表面579上的金属网格580。金属网格580包括以网格形式互连的多个金属片段582,使得每个金属片段582在相应的深沟槽隔离结构上方对准并且包围光电二极管区域212、213,限定出光电二极管区域212、213上方的孔。金属网格580可以吸收和/或反射入射光,使得例如通过微透镜引导到光电二极管区域212或213的入射光停留在相应的光电二极管区域212或213内,从而减少相邻光电二极管区域212、213之间的光学串扰。金属网格580可以由金属(诸如钨)形成。在实施例中,金属网格580可以由电介质和金属材料的堆叠形成。在实施例中,像素阵列基板包括在金属网格580上方的层中的多个微透镜。

62.在方向298z上,每个金属片段582具有厚度584,在实施例中,该厚度超过自由空间电磁波长λ0处的强度穿透深度δ,δ=λ0/(πni),其中ni是金属片段582在波长λ0处的折射率的虚部。波长λ0可以在0.4微米和1.0微米之间。在实施例中,厚度584在75和125纳米之间。

63.图6是闪烁减轻像素阵列基板600的截面示意图,闪烁减轻像素阵列基板600是像素阵列基板400的示例。在实施例中,像素阵列基板包括在每个小光电二极管区域612和每个大光电二极管区域613上方的缓冲层670。半导体基板610具有后表面620,后表面620是后表面220的示例,并且因此包括表面区域622、624和626,它们分别是表面区域222、224和226的示例并且形成沟槽621,沟槽621是沟槽221的示例。后表面620还包括后表面220的其他表面区域(诸如表面区域227和228)的类似物。

64.像素阵列基板600包括半导体基板610和金属层660,它们分别是图2的像素阵列基板200的半导体基板210和金属层260的示例。半导体基板610包括多个小光电二极管区域612和多个大光电二极管区域613,它们分别是小光电二极管区域212和大光电二极管区域213的示例。如图6中所示,金属层660在半导体基板610的后表面620上方形成并且完全覆盖小光电二极管区域612的曝光区块。金属层660嵌入缓冲层670中。金属层660可以具有在0.1微米至0.3微米之间的材料厚度,这取决于所选择的材料和所需的透光量。

65.半导体基板610具有厚度616和617,它们分别是图2的像素阵列基板200的厚度216和217的示例。在实施例中,厚度617等于厚度616。在实施例中,像素阵列基板600包括钝化层630、蚀刻停止层640和粘合层650中的至少一个,它们分别是钝化层230、蚀刻停止层240和粘合层250的示例。

66.半导体基板610包括形成在其中的多个深沟槽隔离结构,其中多个深沟槽隔离结构彼此互连并以包围每个小光电二极管区域612的网格形式形成,从而在每个小光电二极

管区域612与相邻的大光电二极管区域613之间提供隔离。每个深沟槽隔离结构包括分别沉积有钝化层630、蚀刻停止层640和粘合层650以及金属层660的沟槽621。

67.钝化层630和蚀刻停止层640具有相应的顶表面639和649,它们分别是顶表面239和249的示例。粘合层650具有底表面651,其是粘合层250的底表面251的示例。当像素阵列基板600包括蚀刻停止层640时,底表面651可以与顶表面649共面。当像素阵列基板600包括钝化层630并且不包括蚀刻停止层640时,底表面651可以与顶表面639共面。粘合层650覆盖位于小光电二极管区域612上方的表面区域(例如,曝光区块),而不覆盖大光电二极管区域613上方的表面区域(例如,曝光区块)。

68.在实施例中,像素阵列基板600包括形成在缓冲层670上的金属网格580。金属网格580的每个金属片段582与相应的沟槽621对准,并且被构造为在小光电二极管区域612和/或大光电二极管区域613上方限定出孔或开口。在实施例中,每个金属片段582与包围相应小光电二极管区域612的相应沟槽621对准。在实施例中,钝化层630、蚀刻停止层640和粘合层650以及金属层660在沟槽621中形成深沟槽隔离结构。

69.缓冲层670具有在光电二极管区域612上方的厚度672和在光电二极管区域613上方的厚度673。厚度673超过厚度672。在实施例中,厚度672在0.1微米和0.3微米之间。缓冲层670可以由氧化物材料形成。

70.图7是像素阵列基板700的横截面示意图,像素阵列基板700是在其上形成金属层260之前的像素阵列基板200的前体。像素阵列基板700包括半导体基板210和层230、240中的至少一个、以及粘合层750。粘合层750是在光电二极管区域212和213上方的粘合层250的示例。像素阵列基板700还包括在多个光电二极管区域212和213中的每一个上方的金属层760。在实施例中,金属层760被沉积到位于小光电二极管区域612上方的沟槽621的区域中。在实施例中,金属层760被平坦化以产生金属层560。在实施例中,蚀刻金属层760以产生金属层660。

71.图8是图像传感器894的示意性横截面图,图像传感器894是图1的相机190的图像传感器194的示例。图像传感器894包括像素阵列基板200、缓冲层570、滤色器阵列880、金属网格580和微透镜阵列885。金属网格580在缓冲层570的顶表面579上并且嵌入到滤色器阵列880中。

72.微透镜阵列885包括(i)多个微透镜886,每个微透镜886与相应的光电二极管区域212对准以将光引导到其上,以及(ii)多个微透镜887,每个微透镜887与相应的光电二极管区域213对准以将光引导到其上。在实施例中,微透镜887比微透镜886更厚。滤色器阵列880位于微透镜阵列885和后表面220之间,并且包括多个滤色器881。每个滤色器881设置在金属网格580上并进入由金属网格580限定出的孔中。每个滤色器881与相应的光电二极管区域212或213对准,用于对透射通过与其对准的微透镜886或微透镜887的光进行光谱过滤。

73.因而,到达小光电二极管区域212的入射光已经透射穿过第一后表面区域上的相应金属层260,而到达大光电二极管区域213的入射光不穿过金属层260。照此,被引导到小光电二极管区域212的入射光的强度被衰减以获得期望的量子效率并减少小光电二极管区域212和相邻的大光电二极管部分213之间的串扰,而不影响被引导到大光电二极管区域213的入射光的光强度。

74.图9是图像传感器994的示意性横截面视图,图像传感器994是图1的相机190的图

像传感器194的示例。图像传感器994包括其上具有滤色器阵列880和微透镜阵列885的像素阵列基板900。每个滤色器881与相应的光电二极管区域612或613对准,用于对透射通过与其对准的微透镜886或微透镜887的光进行光谱过滤。每个微透镜886与相应的光电二极管区域612对准以将光引导到其上。每个微透镜887与相应的光电二极管区域613对准以将光引导到其上。

75.图10是图示用于制造闪烁减轻像素阵列基板的方法1000的流程图。方法1000包括步骤1040。在实施例中,方法1000还包括步骤1010、1020、1030和1050中的至少一个。

76.步骤1010包括从位于在半导体基板中形成的小光电二极管区域上方的半导体基板的后表面开始减小半导体基板的一个区段的厚度。在实施例中,步骤1010和后续步骤应用于半导体基板的与在半导体基板中形成的多个小光电二极管区域中的相应一个对应的附加区段。

77.在步骤1010的示例中,图5的半导体基板510的前体基板具有均匀的厚度517,因此没有任何沟槽并且没有表面区域522、524和526。在实施例中,这个前体基板是例如在可以包括形成多个大和小光电二极管区域、晶体管栅极以及相关联的源极和漏极的前端工艺之后半制造的。这个前体基板被掩蔽和蚀刻,使得其包括小光电二极管区域512的区域具有小于厚度517的厚度516。

78.步骤1020包括在半导体基板的后表面上形成在与小光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中包围小光电二极管区域的沟槽。在步骤1020的第一示例中,在图2的半导体基板210的后表面220上形成沟槽221。在步骤1020的第二示例中,图3的沟槽314(1)、314(2)、315(1)和315(2)在后表面220上形成。

79.在实施例中,步骤1020包括步骤1022,其包括蚀刻后表面以产生限定出沟槽的后表面的内侧壁区域、外侧壁区域和底部区域。在步骤1022的示例中,蚀刻半导体基板210的后表面220以产生限定出沟槽221的后表面220的内侧壁表面区域222、外侧壁表面区域226和底表面区域224。步骤1022还可以包括蚀刻后表面以在小光电二极管区域上方产生表面区域(诸如表面区域228)。

80.步骤1030包括在(i)第一后表面区域和(ii)限定出沟槽的后表面的内侧壁区域、外侧壁区域和底部区域上沉积粘合层、钝化层和蚀刻停止层中的至少一个。步骤1030还可以包括在小光电二极管区域上方的表面区域上沉积粘合层、钝化层和蚀刻停止层中的至少一个。在步骤1030的示例中,钝化层230、蚀刻停止层240和粘合层250中的至少一个沉积在后表面220上。在1030的示例中,粘合层250的沉积在蚀刻停止层240的沉积之后,蚀刻停止层240的沉积在钝化层230的沉积之后。

81.步骤1040包括在第一后表面区域上和在沟槽中形成金属层。在实施例中,形成在第一后表面区域上的金属层与沉积在相邻的大光电二极管区域上方的后表面上的蚀刻停止层的顶表面共面。在步骤1040的示例中,金属层260形成在后表面区域228上和沟槽221中。在实施例中,金属层260的顶表面269与蚀刻停止层240的顶表面249共面。

82.步骤1040可以包括步骤1042。步骤1042包括在第一后表面区域、与小光电二极管区域相邻的大光电二极管区域上方的第二后表面区域上以及在沟槽中沉积初始金属层。在步骤1042的示例中,金属层760沉积在图7的像素阵列基板700的后表面区域227和228上以及沟槽221中。

83.当方法1000产生像素阵列基板500时,步骤1040可以包括步骤1044。当半导体基板具有(i)在第一后表面区域和与该后表面相对的平坦前表面之间的第一厚度以及(ii)在平坦前表面和第二后表面区域之间的超过第一厚度的第二厚度时,步骤1040可以包括步骤1044。这种半导体基板的示例是当厚度217超过厚度216时的半导体基板210,如图5中的半导体基板510。

84.步骤1044包括通过平坦化金属层来移除位于第二后表面区域上的初始金属层的区域。在实施例中,平坦化是经由蚀刻或化学机械抛光(cmp)工艺实现的。平坦化工艺在蚀刻停止层处自行停止。照此,在每个大光电二极管区域上方的第二后表面区域上的金属层760的部分被移除,而在每个小光电二极管区域上方的第一后表面区域上的金属层760的部分被留下,其中金属层760的剩余部分覆盖每个小光电二极管区域的曝光区域。在步骤1044的示例中,位于大光电二极管区域213上方的金属层760的部分通过平坦化金属层760而被移除,而位于小光电二极管区域212上方的金属层760的部分保留。步骤1044还可以包括移除大光电二极管区域上方的粘合层的部分。例如,步骤1044可以包括移除大光电二极管区域213上方的粘合层750的部分以产生至少一个粘合层250。

85.当半导体基板具有均匀厚度时,例如,当厚度216和217相等时,如图6中的半导体基板610,步骤1040可以包括步骤1047。因而,在实施例中,方法1000包括步骤1047而不包括步骤1010。步骤1047包括通过经由光掩模使金属层曝光并蚀刻经曝光的金属层来移除位于第二后表面区域上方的初始金属层的区域。在步骤1047的示例中,通过经由图案化的光掩模使金属层760曝光然后相应地蚀刻金属层760来移除位于后表面区域227上方的金属层760的区域。

86.步骤1050包括在金属层上和在与小光电二极管区域相邻的大光电二极管区域上方沉积缓冲层。在步骤1050的第一示例中,缓冲层570沉积在图5中的金属层560上和大光电二极管区域513上方。在步骤1050的第二示例中,缓冲层670沉积在图6中的金属层660上和大光电二极管区域613上方,这导致金属层660嵌入缓冲层670中。

87.在实施例中,在步骤1050之后,方法1000包括金属沉积、图案化和蚀刻以形成多个互连金属片段的步骤,从而在封住相应的大和小光电二极管区域的曝光区域的缓冲层上形成金属网格。之后可以在金属片段之间沉积滤色器材料以形成用于大和小光电二极管区域中的每一个的多个滤色器。可以在形成滤色器之后执行用于形成微透镜阵列的工艺。

88.特征的组合

89.上面描述的特征以及下面要求保护的那些特征可以在不脱离本发明的范围的情况下以各种方式组合。以下列举的示例说明了一些可能的、非限制性的组合。

90.(a1)一种闪烁减轻像素阵列基板,包括半导体基板和金属层。半导体基板包括小光电二极管区域。半导体基板的后表面形成在与小光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中包围小光电二极管区域的沟槽。金属层覆盖第一后表面区域,至少部分地填充沟槽,并在该横截面平面中包围小光电二极管区域。

91.(a2)在像素阵列基板(a1)的实施例中,第一后表面区域上方的金属层的厚度在0.1微米和0.3微米之间。

92.(a3)在像素阵列基板(a1)和(a2)中的任一项的实施例中,形成金属层的材料包括钨和铝中的至少一种。

93.(a4)像素阵列基板(a1)

–

(a3)中的任何一项的实施例,还包括粘合层,该粘合层覆盖第一后表面区域并延伸到(i)金属层和后表面的内侧壁区域之间以及(ii)金属层和后表面的外侧壁区域之间的沟槽中。

94.(a5)在像素阵列基板(a4)的实施例中,第一后表面区域上方的粘合层的厚度在二十纳米和五十纳米之间。

95.(a6)在像素阵列基板(a1)

–

(a5)中的任何一项的实施例中,半导体基板还包括形成二乘二阵列的四个大光电二极管区域。小光电二极管区域位于该二乘二阵列的中心。

96.(a7)在像素阵列基板(a6)的实施例中,四个大光电二极管区域包括第一、第二、第三和第四大光电二极管区域,半导体基板还包括附加的小光电二极管区域,半导体基板还包括第五大光电二极管区域和第六大光电二极管区域,它们与第三大光电二极管区域和第四大光电二极管区域形成附加的二乘二阵列。附加的小光电二极管区域位于附加的二乘二阵列的中心。

97.(a8)在像素阵列基板(a6)和(a7)的实施例中,半导体基板具有(i)在第一后表面区域和与后表面相对的平坦前表面之间的第一厚度,以及(ii)在平坦前表面和四个大光电二极管区域之一上方的第二后表面区域之间的超过第一厚度的第二厚度。

98.(a9)在像素阵列基板(a6)

–

(a8)中的任何一项的实施例中,半导体基板的后表面包括四个共面的表面区域,每个表面区域位于四个大光电二极管区域中相应一个的上方。小光电二极管区域上方的金属层的顶表面与(i)四个共面的表面区域、(ii)在四个共面的表面区域中的每一个上形成的钝化层以及(iii)在四个共面的表面区域中的每一个上形成的蚀刻停止层之一共面。

99.(a10)像素阵列基板(a6)

–

(a9)中的任何一项的实施例,还包括钝化层,该钝化层位于金属层和半导体基板之间并且覆盖第一后表面区域和四个大光电二极管区域中的每个大光电二极管区域上方的后表面。

100.(a11)像素阵列基板(a10)的实施例,还包括在金属层和钝化层之间的蚀刻停止层。蚀刻停止层可以覆盖四个大光电二极管区域中的每一个上方的钝化层。小光电二极管区域上方的金属层的顶表面可以与位于四个大光电二极管区域中的每一个上方的蚀刻停止层的顶表面共面。

101.(a12)像素阵列基板(a11)的实施例,还包括位于第一后表面区域和四个大光电二极管区域中的每一个上方的缓冲层。金属层位于第一后表面区域与缓冲层之间。

102.(a13)在像素阵列基板(a12)的实施例中,缓冲层具有(i)在小光电二极管区域上方的第一厚度,以及(ii)在四个大光电二极管区域中的每一个上方的超过第一厚度的第二厚度。

103.(a14)在像素阵列基板(a12)的实施例中,缓冲层具有(i)在小光电二极管区域上方的第一厚度,以及(ii)在四个大光电二极管区域中的每一个上方的等于第一厚度的第二厚度。

104.(a15)像素阵列基板(a12)

–

(a14)中的任何一项的实施例,还包括在缓冲层上的金属网格,该金属网格与沟槽对准,并且在小光电二极管区域上方形成孔。

105.(b1)一种用于制造闪烁减轻像素阵列基板的方法,包括(i)在与小光电二极管区域上方的后表面的第一后表面区域平行的横截面平面中包围半导体基板的小光电二极管

区域的沟槽中和(ii)第一后表面区域上形成金属层。

106.(b2)在方法(b1)的实施例中,形成沟槽包括蚀刻后表面以产生限定出沟槽的后表面的内侧壁区域、外侧壁区域和底部区域。

107.(b3)方法(b1)和(b2)中的任一项的实施例,还包括,在形成金属层之前,在(i)第一后表面区域和(ii)限定出沟槽的后表面的内侧壁区域、外侧壁区域和底部区域上沉积粘合层、钝化层和蚀刻停止层中的至少一个。

108.(b4)方法(b1)

–

(b3)中的任何一项的实施例,还包括在金属层上和在与小光电二极管区域相邻的大光电二极管区域上方沉积缓冲层。沉积缓冲层可以包括将金属层嵌入缓冲层中。

109.(b5)在方法(b1)

–

(b4)中的任何一项的实施例中,半导体基板具有(i)在第一后表面区域和与该后表面相对的平坦前表面之间的第一厚度和(ii)在平坦前表面和与小光电二极管区域相邻的大光电二极管区域上方的第二后表面区域之间的超过第一厚度的第二厚度。在此类实施例中,形成金属层可以包括在第一和第二后表面区域上以及在沟槽中沉积初始金属层;并且通过平坦化金属层来移除位于第二后表面区域上方的初始金属层的区域。

110.(b6)在方法(b1)

–

(b4)中的任何一项的实施例中,形成金属层包括:在第一后表面区域、在与小光电二极管区域相邻的大光电二极管区域上方的第二后表面区域上以及在沟槽中沉积初始金属层;并且通过经由光掩模曝光金属层并蚀刻经曝光的金属层来移除位于第二后表面区域上方的初始金属层的区域。

111.(b7)方法(b1)

–

(b6)中的任何一项的实施例,还包括形成沟槽。

112.(b8)在方法(b7)的实施例中,形成沟槽包括蚀刻后表面以产生限定出沟槽的后表面的内侧壁区域、外侧壁区域和底部区域。

113.在不脱离本实施例的范围的情况下,可以在以上方法和系统中进行改变。因此应当注意的是,以上描述中包含或附图中所示的内容应当被解释为说明性的,而不是限制性的。在本文中,并且除非另外指出,否则短语“在实施例中”等同于短语“在某些实施例中”,并且并不是指所有实施例。以下权利要求书旨在覆盖本文描述的所有一般和具体特征,以及本方法和系统的范围的所有陈述,就语言而言,可以认为其介于两者之间。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。