1.本发明涉及半导体电路技术,特别是涉及一种运算放大器及带隙基准源电路。

背景技术:

2.现有传统带隙基准源电路如图1、图2所示,图1电路结构产生的基准电压为图2电路结构产生的基准电压为调整r2与r1的比例,可以产生任意值的基准电压;其中,图1电路结构和图2结构中的δv

be

=v

t

*ln(n),为正温度系数,v

t

为热电势,n为三极管q1与q0的比例常数,通常取8或者24等,在版图实现时更好的进行匹配,v

be

为三极管q0的基极与发射极的电压差值,为负温度系数。

3.图1电路结构产生的零温度系数基准电压为固定值约1.25v,可以产生正温度系数电压和正温度系数电流,在实际应用中可能会涉及低电源电压,如电源电压小于1.3v的应用,该电路结构无法满足,同时该电路结构只能产生正温度系数的电流,无法满足零温度系数电流的应用需求;图2电路结构产生的零温度系数基准电压可以为任意值(通过调整r2与r1的比例实现),可以产生无温度系数的电流,但该结构无法产生正温度系数的电压,如在一些应用中需要正温度系数的电压对温度进行检测,该结构无法满足,同时该结构存在多个电压稳定工作点,启动电路设计更有挑战。

技术实现要素:

4.本发明要解决的技术问题是提供一种运算放大器,为三端输入、两端输出的电路结构。

5.为解决上述技术问题,本发明提供的一种运算放大器,其包括第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5及第六nmos管mn6;

6.第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5及第六pmos管mp6的源端同接工作电压源vcc;

7.第一nmos管mn1、第二nmos管mn2及第三nmos管mn3的源端同接地gnd;

8.第四nmos管mn4、第五nmos管mn5及第六nmos管mn6的源端同接地gnd;

9.第一pmos管mp1的漏端接第六nmos管mn6的漏端,并作为正温度系数运放输出端vout_p;

10.第一pmos管mp1的栅端接第二pmos管mp2的栅端、漏端及第一nmos管mn1漏端;

11.第一nmos管mn1漏端作为正温度系数电流正向输入端inp_p;

12.第四pmos管mp4的漏端接第四nmos管mn4的漏端,并作为负温度系数运放输出端vout_n;

13.第四pmos管mp4的栅端接第三pmos管mp3的栅端、漏端及第三nmos管mn3漏端;

14.第三nmos管mn3漏端作为负温度系数电流正向输入端inp_n;

15.第六pmos管mp6的漏端接第五nmos管mn5的漏端及第四nmos管mn4、第五nmos管mn5和第六nmos管mn6的栅端;

16.第六pmos管mp6的栅端接第五pmos管mp5的栅端、漏端及第二nmos管mn2漏端;

17.第二nmos管mn2漏端作为负向输入端inn。

18.较佳的,所述运算放大器还包括第七nmos管mn7及第八nmos管mn8;

19.第七nmos管mn7的漏端、栅端及第八nmos管mn8的栅端短接,用于接偏置电流ibias;

20.第七nmos管mn7及第八nmos管mn8的源端接地gnd;

21.第一nmos管mn1、第二nmos管mn2及第三nmos管mn3的源端同接第八nmos管mn8的漏端,经第八nmos管mn8接地gnd。

22.为解决上述技术问题,本发明提供的另一种运算放大器,其包括第一pmos管mp1、第二pmos管mp2、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10、第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15及第十六nmos管mn16;

23.第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15及第十六nmos管mn16的源端同接地gnd;

24.第一pmos管mp1、第二pmos管mp2、第七pmos管mp7的源端同接工作电压源vcc;

25.第一pmos管mp1的漏端接第十五nmos管mn15的漏端,并作为正温度系数运放输出端vout_p;

26.第七pmos管mp7的漏端接第十六nmos管mn16的漏端,并作为负温度系数运放输出端vout_n;

27.第二pmos管mp2的栅端、漏端及第一pmos管mp1栅端、第七pmos管mp7栅端同接第十四nmos管mn14的漏端;

28.第八pmos管mp8、第九pmos管mp9及第十pmos管mp10的源端接偏置电流ibias;

29.第八pmos管mp8的漏端接第十三nmos管mn13的漏端、栅端及第十五nmos管mn15的栅端;

30.第八pmos管mp8的栅端作为正温度系数电流正向输入端inp_p;

31.第九pmos管mp9的漏端接第十一nmos管mn11的漏端、栅端及第十六nmos管mn16的栅端;

32.第九pmos管mp9的栅端作为负温度系数电流正向输入端inp_n;

33.第十pmos管mp10的漏端接第十二nmos管mn12的漏端、栅端及第十四nmos管mn14的栅端;

34.第十pmos管mp10的栅端作为负向输入端inn。

35.本发明还提供了一种包括所述运算放大器的带隙基准源电路,其还包括正温度系数电流产生电路、负温度系数电流产生电路及基准电压产生电路;

36.所述正温度系数电流产生电路包括第十一pmos管mp11、第十二pmos管mp12、第一pnp三极管q1、第零pnp三极管q0及第零电阻r0;

37.所述负温度系数电流产生电路包括第十三pmos管mp13及第一电阻r1;

38.所述基准电压产生电路包括第十四pmos管mp14、第十五pmos管mp15及第二电阻

r2;

39.第十一pmos管mp11、第十二pmos管mp12、第十三pmos管mp13、第十四pmos管mp14及第十五pmos管mp15的源端接工作电源正;

40.第十一pmos管mp11、第十二pmos管mp12、第十四pmos管mp14的栅端均接正温度系数运放输出端vout_p;

41.第十三pmos管mp13、第十五pmos管mp15的栅端均接所述运算放大器的负温度系数运放输出端vout_n;

42.第十一pmos管mp11的漏端接所述运算放大器的正温度系数电流正向输入端inp_p;

43.第十二pmos管mp12的漏端接所述运算放大器的负向输入端inn;

44.第一pnp三极管q1的发射极经第零电阻r0接所述运算放大器的正温度系数电流正向输入端inp_p;

45.第零pnp三极管q0的发射极接所述运算放大器的负向输入端inn;

46.第一pnp三极管q1、第零pnp三极管q0的基极短接,集电极均接地;

47.第十三pmos管mp13的漏端接所述运算放大器的负温度系数电流正向输入端inp_n;

48.第一电阻r1串接在第十三pmos管mp13的漏端同地之间;

49.第十四pmos管mp14、第十五pmos管mp15的漏端短接后经第二电阻r2接地,并且短接端作为一零温度系数基准电压vref输出端。

50.较佳的,所述第二电阻r2是由多个电阻串联构成;

51.多个电阻串联的串接点用于输出大小不同的零温度系数基准电压vref1,vref2。

52.较佳的,所述基准电压产生电路还包括第十六pmos管mp16及第三电阻r3;

53.第十六pmos管mp16的源端接工作电源正,栅端接正温度系数运放输出端vout_p,漏端经第三电阻r3接地并作为正温度系数电压vptc输出端。

54.较佳的,所述基准电压产生电路还包括第十七pmos管mp17及第五电阻r5;

55.第十七pmos管mp17栅端接所述运算放大器的负温度系数运放输出端vout_n,源端接工作电源正,漏端经第五电阻r5接地并作为负温度系数电压vntc输出端。

56.较佳的,所述带隙基准源电路还包括基准电流产生电路;

57.所述基准电流产生电路包括第十八pmos管mp18及第十九pmos管mp19;

58.第十八pmos管mp18、第十九pmos管mp19的源端接工作电源正;

59.第十八pmos管mp18的栅端接正温度系数运放输出端vout_p;

60.第十九pmos管mp19的栅端接负温度系数运放输出端vout_n;

61.第十八pmos管mp18、第十九pmos管mp19的漏端均接零温度系数电流irefztc输出端。

62.较佳的,所述基准电流产生电路还包括第二十pmos管mp20;

63.第二十pmos管mp20的源端接工作电源正,栅端接正温度系数运放输出端vout_p,漏端接正温度系数电流irefptc输出端。

64.较佳的,所述基准电流产生电路还包括第二一pmos管mp21;

65.第二一pmos管mp21的源端接工作电源正,栅端接负温度系数运放输出端vout_n,

漏端接负温度系数电流irefntc输出端。

66.本发明的运算放大器,为三端输入、两端输出的电路结构,具有负向输入端inn、正温度系数电流正向输入端inp_p、负温度系数电流正向输入端vout_p、正温度系数运放输出端vout_p、负温度系数运放输出端vout_n。

67.本发明的带隙基准源电路,在现有带隙基准电路的理论基础上,通过采用新的电路结构的运算放大器,同时配合正温度系数电流产生电路、负温度系数电流产生电路、基准电压产生电路和基准电流产生电路,能提供任意值的零温度系数(ztc:zero temperature coefficient)电压、正温度系数(ptc:positive temperature coefficient)电压和负温度系数(ntc:negative temperature coefficient)电压,同时可以产生正温度系数电流、负温度系数电流和零温度系数电流,可以节省面积。

附图说明

68.为了更清楚地说明本发明的技术方案,下面对本发明所需要使用的附图作简单的介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

69.图1是现有一种带隙基准源电路;

70.图2是现有另一种带隙基准源电路;

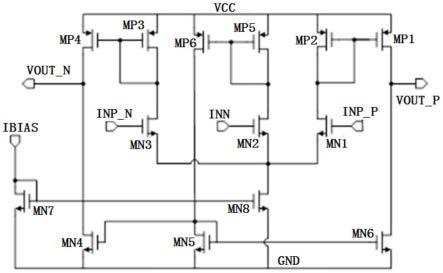

71.图3是本发明的一种运算放大器;

72.图4是本发明的另一种运算放大器;

73.图5是本发明的带隙基准源电路一实施例电路图;

74.图6是本发明的带隙基准源电路一实施例的输出电压仿真结果;

75.图7是本发明的带隙基准源电路一实施例的输出电流仿真结果。

具体实施方式

76.下面将结合附图,对本发明中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

77.实施例一

78.如图3所示,运算放大器包括第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5、第六pmos管mp6、第一nmos管mn1、第二nmos管mn2、第三nmos管mn3、第四nmos管mn4、第五nmos管mn5及第六nmos管mn6;

79.第一pmos管mp1、第二pmos管mp2、第三pmos管mp3、第四pmos管mp4、第五pmos管mp5及第六pmos管mp6的源端同接工作电压源vcc;

80.第一nmos管mn1、第二nmos管mn2及第三nmos管mn3的源端同接地gnd;

81.第四nmos管mn4、第五nmos管mn5及第六nmos管mn6的源端同接地gnd;

82.第一pmos管mp1的漏端接第六nmos管mn6的漏端,并作为正温度系数运放输出端vout_p;

83.第一pmos管mp1的栅端接第二pmos管mp2的栅端、漏端及第一nmos管mn1漏端;

84.第一nmos管mn1漏端作为正温度系数电流正向输入端inp_p;

85.第四pmos管mp4的漏端接第四nmos管mn4的漏端,并作为负温度系数运放输出端vout_n;

86.第四pmos管mp4的栅端接第三pmos管mp3的栅端、漏端及第三nmos管mn3漏端;

87.第三nmos管mn3漏端作为负温度系数电流正向输入端inp_n;

88.第六pmos管mp6的漏端接第五nmos管mn5的漏端及第四nmos管mn4、第五nmos管mn5和第六nmos管mn6的栅端;

89.第六pmos管mp6的栅端接第五pmos管mp5的栅端、漏端及第二nmos管mn2漏端;

90.第二nmos管mn2漏端作为负向输入端inn。

91.较佳的,所述运算放大器还包括第七nmos管mn7及第八nmos管mn8;

92.第七nmos管mn7的漏端、栅端及第八nmos管mn8的栅端短接,用于接偏置电流ibias;

93.第七nmos管mn7及第八nmos管mn8的源端接地gnd;

94.第一nmos管mn1、第二nmos管mn2及第三nmos管mn3的源端同接第八nmos管mn8的漏端,经第八nmos管mn8接地gnd。

95.实施例一的运算放大器,为三端输入、两端输出的电路结构,具有负向输入端inn、正温度系数电流正向输入端inp_p、负温度系数电流正向输入端vout_p、正温度系数运放输出端vout_p、负温度系数运放输出端vout_n。

96.实施例二

97.如图4所示,运算放大器包括第一pmos管mp1、第二pmos管mp2、第七pmos管mp7、第八pmos管mp8、第九pmos管mp9、第十pmos管mp10、第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15及第十六nmos管mn16;

98.第十一nmos管mn11、第十二nmos管mn12、第十三nmos管mn13、第十四nmos管mn14、第十五nmos管mn15及第十六nmos管mn16的源端同接地gnd;

99.第一pmos管mp1、第二pmos管mp2、第七pmos管mp7的源端同接工作电压源vcc;

100.第一pmos管mp1的漏端接第十五nmos管mn15的漏端,并作为正温度系数运放输出端vout_p;

101.第七pmos管mp7的漏端接第十六nmos管mn16的漏端,并作为负温度系数运放输出端vout_n;

102.第二pmos管mp2的栅端、漏端及第一pmos管mp1栅端、第七pmos管mp7栅端同接第十四nmos管mn14的漏端;

103.第八pmos管mp8、第九pmos管mp9及第十pmos管mp10的源端接偏置电流ibias;

104.第八pmos管mp8的漏端接第十三nmos管mn13的漏端、栅端及第十五nmos管mn15的栅端;

105.第八pmos管mp8的栅端作为正温度系数电流正向输入端inp_p;

106.第九pmos管mp9的漏端接第十一nmos管mn11的漏端、栅端及第十六nmos管mn16的栅端;

107.第九pmos管mp9的栅端作为负温度系数电流正向输入端inp_n;

108.第十pmos管mp10的漏端接第十二nmos管mn12的漏端、栅端及第十四nmos管mn14的

栅端;

109.第十pmos管mp10的栅端作为负向输入端inn。

110.实施例二的运算放大器,为三端输入、两端输出的电路结构,具有负向输入端inn、正温度系数电流正向输入端inp_p、负温度系数电流正向输入端vout_p、正温度系数运放输出端vout_p、负温度系数运放输出端vout_n。

111.实施例三

112.如图5所示,一种包括实施例一或实施例二的运算放大器的带隙基准源电路,其还包括正温度系数电流产生电路、负温度系数电流产生电路及基准电压产生电路;

113.所述正温度系数电流产生电路包括第十一pmos管mp11、第十二pmos管mp12、第一pnp三极管q1、第零pnp三极管q0及第零电阻r0;

114.所述负温度系数电流产生电路包括第十三pmos管mp13及第一电阻r1;

115.所述基准电压产生电路包括第十四pmos管mp14、第十五pmos管mp15及第二电阻r2;

116.第十一pmos管mp11、第十二pmos管mp12、第十三pmos管mp13、第十四pmos管mp14及第十五pmos管mp15的源端接工作电源正;

117.第十一pmos管mp11、第十二pmos管mp12、第十四pmos管mp14的栅端均接正温度系数运放输出端vout_p;

118.第十三pmos管mp13、第十五pmos管mp15的栅端均接所述运算放大器的负温度系数运放输出端vout_n;

119.第十一pmos管mp11的漏端接所述运算放大器的正温度系数电流正向输入端inp_p;

120.第十二pmos管mp12的漏端接所述运算放大器的负向输入端inn;

121.第一pnp三极管q1的发射极经第零电阻r0接所述运算放大器的正温度系数电流正向输入端inp_p;

122.第零pnp三极管q0的发射极接所述运算放大器的负向输入端inn;

123.第一pnp三极管q1、第零pnp三极管q0的基极短接,集电极均接地;

124.第十三pmos管mp13的漏端接所述运算放大器的负温度系数电流正向输入端inp_n;

125.第一电阻r1串接在第十三pmos管mp13的漏端同地之间;

126.第十四pmos管mp14、第十五pmos管mp15的漏端短接后经第二电阻r2接地,并且短接端作为一零温度系数基准电压vref输出端。

127.较佳的,所述第二电阻r2是由多个电阻串联构成;

128.多个电阻串联的串接点用于输出大小不同的零温度系数基准电压vref1,vref2。

129.正温度系数电流产生电路:其中δv

be

=v

t

*ln(n),为正温度系数,v

t

为热电势,n为第一pnp三极管q1与第零pnp三极管q0的比例常数,通常取8或者24等,在版图实现时更好的进行匹配。

130.负温度系数电流产生电路:其中v

be

为第零pnp三极管q0的基极与发射极的电压差值,为负温度系数;

131.基准电压产生电路:调整第二电阻r2的值可以实现任意值的零温度系数基准电压输出。

132.较佳的,所述基准电压产生电路还包括第十六pmos管mp16及第三电阻r3;

133.第十六pmos管mp16的源端接工作电源正,栅端接正温度系数运放输出端voutp,漏端经第三电阻r3接地并作为正温度系数电压vptc输出端。

134.调整第三电阻r3的值可以实现任意中心值(室温下)的正温度系数电压输出。

135.较佳的,所述基准电压产生电路还包括第十七pmos管mp17及第五电阻r5;

136.第十七pmos管mp17栅端接所述运算放大器的负温度系数运放输出端vout_n,源端接工作电源正,漏端经第五电阻r5接地并作为负温度系数电压vntc输出端。

137.调整第五电阻r5的值可以实现任意中心值(室温下)的负温度系数电压输出。

138.实施例四

139.基于实施例三,所述带隙基准源电路还包括基准电流产生电路;

140.所述基准电流产生电路包括第十八pmos管mp18及第十九pmos管mp19;

141.第十八pmos管mp18、第十九pmos管mp19的源端接工作电源正;

142.第十八pmos管mp18的栅端接正温度系数运放输出端vout_p;

143.第十九pmos管mp19的栅端接负温度系数运放输出端vout_n;

144.第十八pmos管mp18、第十九pmos管mp19的漏端均接零温度系数电流irefztc输出端。

145.基准电流产生电路:irefztc=k1*i0 k2*i1,其中k1和k2为常数,选择合适的值可以实现零温度系数电流输出。i0为正温度系数电流产生电路产生的电流,i1为负温度系数电流产生电路产生的电流。

146.较佳的,所述基准电流产生电路还包括第二十pmos管mp20;

147.第二十pmos管mp20的源端接工作电源正,栅端接正温度系数运放输出端vout_p,漏端接正温度系数电流irefptc输出端。irefptc=k3*i0,其中k3为常数。

148.较佳的,所述基准电流产生电路还包括第二一pmos管mp21;

149.第二一pmos管mp21的源端接工作电源正,栅端接负温度系数运放输出端vout_n,漏端接负温度系数电流irefntc输出端。irefntc=k4*i1,其中k4为常数。

150.实施例三的带隙基准源电路,在现有带隙基准电路的理论基础上,通过采用新的电路结构的运算放大器,同时配合正温度系数电流产生电路、负温度系数电流产生电路、基准电压产生电路和基准电流产生电路,能提供任意值的零温度系数(ztc:zero temperature coefficient)电压、正温度系数(ptc:positive temperature coefficient)电压和负温度系数(ntc:negative temperature coefficient)电压,同时可以产生正温度系数电流、负温度系数电流和零温度系数电流,可以节省面积。实施例三的带隙基准源电路,其输出电压和电流仿真结果见图6和图7。

151.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精

神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。