具有噪声消除的分数n锁相环pll

1.相关申请的交叉引用

2.本技术要求于2020年12月3日提交的美国临时专利申请第63/120,852号的优先权,该申请的公开内容以引用方式并入。

技术领域

3.本发明主要涉及一种分数n锁相环(pll)电路,并且尤其涉及分数npll电路操作过程中的噪声消除。

背景技术:

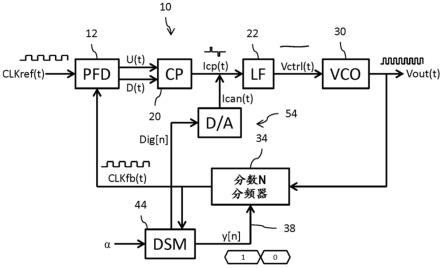

4.参见图1,图中示出分数n锁相环(pll)电路10的框图。相位频率检测器(pfd)电路12具有用于接收参考时钟信号clkref(t)的第一输入端和用于接收反馈时钟信号clkfb(t)的第二输入端。pfd电路12测量在参考时钟信号clkref(t)与反馈时钟信号clkfb(t)的相似沿(即上升沿或下降沿)之间的差。在pfd电路12检测到参考时钟信号clkref(t)和反馈时钟信号clkfb(t)的相似沿对准的情况下,脉冲产生上信号u(t)并且脉冲产生下信号d(t)(两个脉冲是同步的并且具有相同的持续时间)。如果pfd电路12检测到参考时钟信号clkref(t)的沿超前于反馈时钟信号clkfb(t)的相似沿,则脉冲产生第一持续时间的上信号u(t),并且脉冲产生第二持续时间(小于第一持续时间)的下信号d(t),其中,第一持续时间的长度取决于相似沿之间的相位误差。相反地,如果反馈时钟信号clkfb(t)的沿超前于参考时钟信号clkref(t)的相似沿,则pfd电路12脉冲产生第三持续时间的下信号d(t),并且脉冲产生第四持续时间(小于第三持续时间)上信号u(t),其中,第三持续时间的长度取决于相似沿之间的相位误差。

5.图2示出pfd电路12的实施例框图。pfd电路12还包括第一d型触发器(ff)电路14,ff电路14具有用于接收逻辑高电压(vdd)的数据输入端(d)和用于接收参考时钟信号clkref(t)的时钟输入端(clk)。ff电路14的输出端(q)生成上信号u(t)。pfd电路12还包括第二d型触发器(ff)电路16,ff电路16具有用于接收逻辑高电压(vdd)的数据输入端(d)和用于接收反馈时钟信号clkfb(t)的时钟输入端(clk)。ff电路16的输出端(q)生成下信号d(t)。逻辑与门18具有用于接收上信号u(t)的第一输入端和用于接收下信号d(t)的第二输入端。门18对这些信号进行逻辑与,以生成复位信号,该复位信号施加至第一ff电路14和第二ff电路16的复位输入端。

6.图2进一步示出针对以下操作情况中上信号u(t)和下信号d(t)的波形:a)将参考时钟信号clkref(t)和反馈时钟信号clkfb(t)的相似沿对准;b)参考时钟信号clkref(t)的沿超前于反馈时钟信号clkfb(t)的相似沿;以及c)反馈时钟信号clkfb(t)的沿超前于参考时钟信号clkref(t)的相似沿。在情况a)、b)和c)中,上信号u(t)和下信号d(t)的较小脉冲宽度由与门18的操作时延(td)控制,以使第一ff电路14和第二ff电路16复位。这是上信号u(t)和下信号d(t)的最小脉冲宽度。在情况b)和c)中,上信号u(t)和下信号d(t)的较长脉冲宽度分别被控制为最小脉冲宽度(td)加上参考时钟信号clkref(t)和反馈时钟信号clkfb

(t)的相似沿之间的时间差(即相位差-pd)之和的函数。

7.再次参见图1,响应上信号u(t)和下信号d(t)的脉冲持续时间(即宽度),电荷泵(cp)电路20生成输出电流icp(t)。cp电路20包括电流源(路径)电路(未明确示出,参见图4),用于响应上信号u(t)而操作,以向电荷泵输出电流icp(t)提供源电流贡献。cp电路20还包括电流吸收器(路径)电路(未明确示出,参见图4),用于响应下信号d(t)而操作,以向电荷泵输出电流icp(t)提供吸收电流贡献。输出电流icp(t)是源电流贡献与吸收电流贡献之间的差值。当上信号和下信号具有相同的脉冲时,如上文描述的情况a),输出电流icp(t)为零,因为由上信号u(t)和下信号d(t)的脉冲引起的源电流贡献和吸收电流贡献被抵消。在上信号u(t)脉冲持续时间比下信号d(t)脉冲持续时间长的情况下,如上文描述的情况b),输出电流icp(t)包括持续时间为上信号u(t)和下信号d(t)的脉冲宽度差的瞬时源电流。相反地,在下信号d(t)脉冲持续时间比上信号u(t)脉冲持续时间长的情况下,如上文描述的情况c),输出电流icp(t)包括持续时间为上信号u(t)和下信号d(t)的脉冲宽度差的瞬时吸收电流。

8.环路滤波器(lf)电路22对来自电荷泵电路20的输出电流icp(t)进行滤波,以生成控制电压vctrl(t)。在一个实施例中,lf电路22被实现为模拟积分电路,并且因此,控制电压vctrl(t)通过对源电流和吸收电流进行积分来生成。因此,控制电压vctrl(t)将响应输出电流icp(t)的每次瞬时增加而递增地升高,并且响应输出电流icp(t)的每次瞬时减少而递增地降低。

9.压控振荡器(vco)电路30生成频率由控制电压vctrl(t)的电平控制的振荡输出信号vout(t)。因输出电流icp(t)瞬时增加而引起的控制电压vctrl(t)电平的升高导致振荡输出信号vout(t)的频率相应地升高。相反地,因输出电流icp(t)瞬时减少而引起的控制电压vctrl(t)电平的降低导致振荡输出信号vout(t)的频率相应地降低。

10.可编程分频器电路34对振荡输出信号vout(t)进行分频以生成反馈时钟信号clkfb(t)。可编程分频器电路34实现振荡输出信号vout(t)的频率与反馈时钟信号clkfb(t)的频率之间的分数分频比。该分数分频比等于n y[n],其中,y[n]是由一个或多个位表示的整数。可编程分频器电路34操作为在每个时间段用振荡输出信号vout(t)除以n y[n]。例如,在y[n]是单个位的情况下,可编程分频器电路34操作为用振荡输出信号vout(t)除以n 1(对于该单个位的每个逻辑1整数值),并且用振荡输出信号vout(t)除以n(对于该单个位的每个逻辑0整数值)。

[0011]

数字信号38的y[n]整数值例如可以由分数δ-σ调制器(dsm)电路44生成。分数δ-σ调制器(dsm)电路44接收反馈时钟信号clkfb(t)和控制信号α,控制信号α指定0至1之间的分数值。响应该输入,dsm电路44生成y[n]的整数,并且控制序列中每个时间段的长度。可编程分频器电路34通过在每个时间段执行n y[n]分频来响应整数。在这种情况下,avg(y[n])=α,其中,“avg”是平均函数。结果,振荡输出信号vout(t)的频率f

pll

平均等于(n α)*f

clk

,其中,f

clk

是参考时钟信号clkref(t)的频率。

[0012]

与图1的pll电路10相关的问题在于,来自dsm电路44的量化噪声被注入可编程分频器电路34,并且在由lf电路22集成之前通过pfd电路12和cp电路20。对于该噪声问题的常规解决方案是减小pll电路10的带宽(bw),从而滤除噪声。这对于某些电路应用中的pll电路设计者来说是可接受的折衷。然而,在需要高带宽pll电路的情况下,必须替代地使用噪

声消除技术。

[0013]

因此,本领域中存在改进噪声消除技术的需求。

技术实现要素:

[0014]

一种锁相环(pll)电路,包括生成反馈时钟信号的分数n分频器。一种用于pll电路的噪声消除电路,包括:同步电路,同步电路接收pll电路的压控时钟信号和反馈时钟信号,并且被配置为生成第一同步反馈时钟信号和第二同步反馈时钟信号,其中,第二同步反馈时钟信号延迟压控时钟信号的整数个周期;第一相位频率检测器电路,第一相位频率检测器电路接收第一同步反馈时钟信号和第二同步反馈时钟信号,并且被配置为生成第一上控制信号和第一下控制信号,其中,第一上控制信号的脉冲宽度与第一下控制信号的脉冲宽度相差整数个周期;逻辑电路,逻辑电路被配置为响应第一上控制信号、第一下控制信号和指示噪声消除校正幅度的数字码信号,生成上数字控制信号和下数字控制信号;以及电流数模转换器电路,电流数模转换器电路接收上数字控制信号和下数字控制信号,并且包括:电流源电路,电流源电路响应上数字控制信号而操作,以向pll电路提供噪声消除源电流;以及电流吸收电路,电流吸收电路响应下数字控制信号而操作,以向pll电路提供噪声消除吸收电流。

[0015]

一种锁相环(pll)电路,包括:分数n分频器,生成反馈时钟信号;第一相位频率检测器,第一相位频率检测器被配置为将反馈时钟信号与参考时钟信号进行比较,并且生成第一上控制信号和第一下控制信号;以及电荷泵电路,电荷泵电路由第一上控制信号和第一下控制信号控制,以生成电荷泵输出电流。一种用于pll电路的噪声消除电路,包括:同步电路,同步电路接收pll电路的压控时钟信号和反馈时钟信号,并且被配置为生成第一同步反馈时钟信号和第二同步反馈时钟信号,其中,第二同步反馈时钟信号延迟压控时钟信号的整数个周期;第二相位频率检测器电路,第二相位频率检测器电路接收第一同步反馈时钟信号和第二同步反馈时钟信号,并且被配置为生成第二上控制信号和第二下控制信号,其中,第二上控制信号的脉冲宽度与第二下控制信号的脉冲宽度相差整数个周期;以及电流数模转换器电路,电流数模转换器电路响应第二上控制信号而被控制,以将噪声消除源电流施加至电荷泵输出电流,并且响应第二下控制信号而被控制,以将噪声消除吸收电流施加至电荷泵输出电流。

[0016]

在一个实施例中,提出了一种用于锁相环(pll)电路的噪声消除电路的方法,该pll电路包括分数n分频器,用于接收pll电路的压控时钟信号并生成pll电路的反馈时钟信号。该方法包括:从pll电路的压控时钟信号和反馈时钟信号生成第一同步反馈时钟信号和第二同步反馈时钟信号,第二同步反馈时钟信号从第一同步反馈时钟信号延迟压控时钟信号的整数个周期;处理第一同步反馈时钟信号和第二同步反馈时钟信号以生成第一上控制信号和第一下控制信号,其中,第一上控制信号的脉冲宽度与第一下控制信号的脉冲宽度相差整数个周期;生成指示噪声消除校正幅度的数字码信号;向pll电路施加噪声消除源电流,其中,噪声消除源电流的幅度取决于数字码信号和从第一上控制信号和第一下控制信号导出的上数字控制信号;以及向pll电路施加噪声消除吸收电流,其中,噪声消除吸收电流的幅度取决于数字码信号以及从第一上控制信号与第一下控制信号导出的下数字控制信号。

[0017]

在一个实施例中,该方法包括:将反馈时钟信号与压控时钟信号同步,以生成第一同步反馈时钟信号和第二同步反馈时钟信号,第二同步反馈时钟信号从第一同步反馈时钟信号延迟压控时钟信号的整数个周期;对第一同步反馈时钟信号和第二同步反馈时钟信号进行相位比较,以生成上控制信号和下控制信号,其中,上控制信号的脉冲宽度与下控制信号的脉冲宽度相差整数个周期;以及响应于上控制信号,向pll电路施加噪声消除源电流;以及响应于下控制信号,向pll电路施加噪声消除吸收电流。

附图说明

[0018]

为了更好地理解实施例,现在将仅通过示例的方式参考附图,其中:

[0019]

图1是分数n分频锁相环(pll)电路的框图;

[0020]

图2是用于图1的pll电路的pfd电路的框图;

[0021]

图3是实现量化噪声消除技术的分数n分频pll电路的框图;

[0022]

图4是实现另一量化噪声消除技术的分数n分频pll电路的框图;

[0023]

图5是用于图4的pll电路的sync电路的框图;

[0024]

图6是用于图4的pll电路的副本pfd电路的框图;

[0025]

图7是逻辑电路的框图;

[0026]

图8a至8b、9a至9d和10a至10d是说明图7的逻辑电路操作的时序图;并且

[0027]

图11a至11c是用于图4的pll电路的电荷泵和电流数模(d/c)转换器电路的操作时序图。

具体实施方式

[0028]

图3示出实现量化噪声消除技术的分数n锁相环(pll)电路50的框图。图1和图3中相似的附图标记表示相同或相似的部件、电路、部分、信号等,并且为了简洁起见,本文省略了重复讨论。参见以上讨论。pll电路50与pll电路10的不同之处在于增加了量化噪声消除电路54。量化噪声消除电路54包括数模(d/a)转换器电路,d/a转换器电路具有输入端,用于接收由dsm电路44输出的数字码信号dig[n]。该数字码信号dig[n]由d/a转换器电路转换以生成模拟噪声消除电流ican(t),该电流被施加至来自电荷泵电路20的输出电流icp(t)。实际上,该噪声消除电流ican(t)对应于sdm量化噪声并且从输出电流icp(t)中减掉。因此,噪声消除电流ican(t)是在任一情况下作为源电流或吸收电流施加固定持续时间的可变电流,并且噪声消除电流ican(t)是将消除输出电流icp(t)中存在的量化噪声的电荷等效物。在该实施方式中,应当认识到噪声消除的准确度高度依赖于d/a电路的实施方式。

[0029]

由于dsm电路44生成的量化噪声,由电荷泵电路20生成的输出电流icp(t)中的电荷噪声由下式给出:

[0030][0031]

其中:icp是电荷泵电流;tvco是振荡输出信号vout(t)的周期。q[n]取决于振荡输出信号vout(t)的周期(或其某些函数)是因为分频器34将基于y[n]的值从其输出(即反馈时钟信号clkfb(t))加上或减去输入的许多时钟周期。

[0032]

为了消除这种噪声,d/a转换器电路生成噪声消除电流ican(t)。这里的想法是在最短的可能时间段内消除噪声。由于pll系统中可用的最小且最准确的时间对应于tvco,因

此,该周期用于生成噪声消除的接通(on)时间。考虑到时滞,直接使用tvco可能是不可行的,因此,将tvco的整数倍替代地用于噪声消除电流ican(t)。结果,d/a转换器电路的dc和瞬态切换行为必须与cp电路20的dc和瞬态切换行为紧密匹配。这是困难的,因为存在多个导致瞬态行为差异的失配源:sdm量化噪声通过pfd电路和cp电路,而消除电荷仅通过d/a转换器电路;响应于相位误差,cp电路的电流源和电流吸收器路径被接通(on)为不同的宽度,并且电流源路径和电流吸收器路径两者的接通有效地消除了因切换而导致的用于vco控制的电荷注入;并且来自d/a转换器电路的噪声消除电流ican(t)通常仅被施加至源电流路径和吸收电流路径中的一个电流路径。由于这些失配,噪声消除的总体效果有限,并且可能导致pll时钟抖动增加。

[0033]

为了减小d/a转换器电路中的切换的影响,可以增加施加抵消电流ican(t)的接通时间。有帮助的是通过逻辑电路装置实现路径匹配,以确保当施加消除量化噪声的消除电流ican(t)时,d/a转换器电路在精确地期望固定持续时间内接通。由于这种消除技术涉及电荷的消除,为了保持d/a转换器电路中的相同分辨率,需要在电流接通时间增加的情况下减小与最低有效位(lsb)相关的电流。这对用于低电流支持的d/a转换器电路的设计起到了约束作用。此外,为了解决并且减少抖动,注入用于提供噪声消除的消除电流ican(t)的持续时间应当与通过cp电路20将部分(量化)噪声注入lf电路中的持续时间相同。然而,增加电流接通时间将增加注入时间量,进而增加抖动。量化噪声消除电路54中的延迟匹配也是一个挑战,因为其在工艺、电压和温度(pvt)变化上并不稳健。

[0034]

现在参考图4,图中示出实现另一量化噪声消除技术的分数n锁相环(pll)电路110的框图。pll电路110与pll电路10和50的不同之处在于使用了量化噪声消除电路112。图1、图3和图4中相似的附图标记表示相同或相似的部件、电路、部分、信号等,并且为了简洁起见,本文省略了重复讨论。参见以上讨论。

[0035]

量化噪声消除电路112包括同步(sync)电路120,同步(sync)电路120具有用于接收反馈时钟信号clkfb(t)的第一输入端和从vco电路30接收振荡输出信号vout(t)或其衍生物的第二输入端。sync电路120生成等同于反馈时钟信号clkfb(t)的同步反馈信号(clkfb_sync)122,反馈时钟信号clkfb(t)的沿与振荡输出信号vout(t)的相似沿同步。sync电路120还生成延迟同步反馈信号(clkfb_sync_dly)124,该延迟同步反馈信号等同于延迟了振荡输出信号vout(t)期望数目的时钟周期后的同步反馈信号clkfb_sync。在所示的该具体示例中,延迟了一个时钟周期。

[0036]

图5示出sync电路120的实施例框图。sync电路120包括第一d型触发器(ff)电路126,ff电路126具有用于接收反馈时钟信号clkfb(t)的数据(d)输入端和用于接收振荡输出信号vout(t)的时钟(clk)输入端。ff电路126的输出端(q)生成同步反馈信号clkfb_sync,该信号被施加至第二d型触发器(ff)电路128的数据(d)输入端。ff电路128的时钟(clk)输入端接收振荡输出信号vout(t)。ff电路128的输出端(q)生成延迟同步反馈信号(clkfb_sync_dly)124。

[0037]

应当注意的是,图5的电路被实现为使得延迟同步反馈信号(clkfb_sync_dly)124相对于同步反馈信号clkfb_sync延迟振荡输出信号vout(t)的一个时钟周期。这仅仅是示例。在需要增加消除电流ican(t)的接通时间的情况下,图5的电路可以根据需要用串联的附加ff电路128来实现,以提供噪声消除电流ican(t)所需的整数倍的tvco。

[0038]

再次参见图4,量化噪声消除电路112还包括电路副本相位频率检测器(pfd)电路130。“电路副本”的意思是用于pfd电路130的电路装置是用于pfd电路12的电路装置的复制(比较图2和图6以及相同电路架构的使用)。

[0039]

现在同样参见图6,副本pfd电路130具有用于接收同步反馈信号(clkfb_sync)122的第一输入端和用于接收延迟同步反馈信号(clkfb_sync_dly)124的第二输入端。同步反馈信号(clkfb_sync)122被施加至第一d型触发器(ff)电路134的时钟(clk)输入端,第一d型触发器电路134还具有用于接收逻辑高电压(vdd)的数据(d)输入端。ff电路134的输出端(q)生成上信号urep(t)。延时同步反馈信号(clkfb_sync_dly)124被施加至第二d型触发器(ff)电路136的时钟(clk)输入端,第二d型触发器电路136还具有用于接收逻辑高电压(vdd)的数据(d)输入端。ff电路136的输出端(q)生成下信号drep(t)。逻辑与门138具有用于接收上信号urep(t)的第一输入端和用于接收下信号drep(t)的第二输入端。门138对这些信号进行逻辑与,以生成复位信号,复位信号施加至第一ff电路134和第二ff电路136的复位输入端(rst)。

[0040]

由于同步电路120的配置,同步反馈信号(clkfb_sync)122与延迟同步反馈信号(clkfb_sync_dly)124总是具有相位关系,其中,同步反馈信号(clkfb_sync)122的沿超前于延迟同步反馈信号(clkfb_sync_dly)124的相似沿;更具体地,超前振荡输出信号vout(t)的一个周期tvco(或如上所述,根据ff电路128的数目设定的整数倍)。因此,脉冲产生上信号urep(t)第一持续时间,脉冲产生下信号drep(t)第二持续时间(小于第一持续时间)。下信号drep(t)的较小脉冲宽度由与门138的操作时延(td)控制,以使第一ff电路134和第二ff电路136复位。上信号urep(t)的较大脉冲宽度被控制为最小脉冲宽度(td)加上同步反馈信号(clkfb_sync)122和延时同步反馈信号(clkfb_sync_dly)124的相似沿之间的时间差(即相位差-pdo)之和的函数。该相位差(pdo)取决于由同步电路120(的一个或多个第二触发器128)施加的延迟,该延迟等于振荡输出信号vout(t)的一个(或多个)时钟周期(cc)(即一个或多个周期tvco)。

[0041]

再次参见图4,cp电路20包括电流源(路径)电路20a,用于响应上信号u(t)的断言而操作,以向电荷泵输出电流icp(t)提供源电流贡献。cp电路20还包括电流吸收器(路径)电路20b,用于响应下信号d(t)的断言而操作,以向电荷泵输出电流icp(t)提供吸收电流贡献。输出电流icp(t)是源电流贡献与吸收电流贡献之间的差值。如前文所述,该电荷泵输出电流icp(t)受到sdm量化噪声的干扰。量化噪声消除电路112用于消除sdm量化噪声以生成基本上没有sdm量化噪声的校正(或补偿)输出电流icp(t)',施加至lf电路22的输入端。

[0042]

量化噪声消除电路112包括电流数模(d/a)转换器电路150,电流d/a转换器电路150被配置为生成噪声消除电流ican(t),施加电流ican(t)以消除存在于cp电路20的输出电流icp(t)中的量化噪声。电流d/a转换器电路150包括电流源(路径)电路150a,用于响应n位信号(up_dac《n-1:0》)142而操作,以向噪声消除电流ican(t)提供幅度可控的源电流贡献。电流源(路径)电路150a可以(例如)由n个单独电流源实现,这些电流源由n位信号(up_dac《n-1:0》)142的相应位致动。电流源(路径)电路150a中的每个电流源可以响应位的断言而生成相同幅度的电流。电流d/a转换器电路150还包括电流吸收器(路径)电路150b,用于响应n位信号(dn_dac《n-1:0》)144而操作,以向噪声消除电流ican(t)提供幅度可控的吸收电流贡献。电流吸收器(路径)电路150b可以(例如)由n个单独电流吸收器实现,这些电流吸

收器由n位信号(dn_dac《n-1:0》)142的相应位致动。电流吸收器(路径)电路150b中的每个电流吸收器可以响应位的断言而生成相同幅度的电流。

[0043]

量化噪声消除电路112还包括逻辑电路140,逻辑电路140被配置为生成被源电流数模(d/a)转换器电路150的n位信号(up_dac《n-1:0》)142,以控制电流源(路径)电路150a(的各个电流源)的操作。逻辑电路140还被配置为生成被源电流数模(d/a)转换器电路150的n位信号(dn_dac《n-1:0》)144,以控制电流吸收器(路径)电路150b(的各个电流吸收器)的操作。n位信号(up_dac《n-1:0》)142和n位信号(dn_dac《n-1:0》)144响应由副本pfd电路130输出的上信号urep(t)和下信号drep(t)以及由dsm电路44输出的具有符号位(sign)的数字码信号dig[n]而生成。在这种背景下,响应,数字码信号dig[n]提供关于噪声消除电流幅度的信息,符号位提供关于极性的信息(例如执行电流输入或执行电流吸收)。

[0044]

现在参考图7,图中示出逻辑电路140的框图。逻辑电路140包括n=n个子电路140《i》,其中,每个子电路操作为将数字码信号dig[n]的一个位转换为up_dac信号142的对应位和dn_dac信号144的对应位。每个子电路内的逻辑是相同的。第一逻辑与门160具有用于接收数字码信号dig[n]的第i位的第一输入端和用于接收副本pfd电路130输出的下信号drep(t)的第二输入端。第二逻辑与门162具有用于接收数字码信号dig[n]逻辑倒置的第i位的第一输入端和用于接收副本pfd电路130输出的上信号urep(t)的第二输入端。由与门160和162输出的信号由逻辑或门164处理以生成dac_cont《i》信号的第i位。由门160、162和164提供的逻辑生成dac_cont《i》信号,以在数字码信号dig《i》的第i位的逻辑是逻辑低(图8a)时,即未断言数字码信号dig的位时具有与上信号urep(t)相等的脉冲。相反地,当数字码信号dig《i》的第i位的逻辑是逻辑高(图8b)时,即断言了数字码信号dig的位时,dac_cont《i》信号具有与下信号drep(t)相等的脉冲。

[0045]

第三逻辑与门166具有用于接收dac_cont《i》信号的第i位的第一输入端和用于接收逻辑倒置符号位的第二输入端。第四逻辑与门168具有用于接收由副本pfd电路130输出的上信号urep(t)的第一输入端和用于接收符号位的第二输入端。由与门166和168输出的信号由逻辑或门170处理,以生成up_dac信号142的第i位。由门166、168和170提供的逻辑生成up_dac《i》信号142,以在数字码信号dig《i》的第i位的是逻辑低(即未断言,参见图9a和9c)时具有与上信号urep(t)相等的脉冲,无论符号位的逻辑状态如何。相反地,当数字码信号dig《i》的第i位是逻辑高(即已断言)时,由门166、168和170提供的逻辑生成up_dac《i》信号142,以在符号位被断言(逻辑1)时具有与上信号urep(t)相等的脉冲,如图9b所示,或者在符号位未被断言时(逻辑0)具有与下信号drep(t)相等的脉冲,如图9d所示。

[0046]

第五逻辑与门172具有用于接收dac_cont《i》信号的第i位的第一输入端和用于接收符号位的第二输入端。第六逻辑与门174具有用于接收由副本pfd电路130输出的上信号urep(t)的第一输入端和用于接收逻辑倒置符号位的第二输入端。由与门172和174输出的信号由逻辑或门176处理以生成dn_dac信号144的第i位。由门172、174和176提供的逻辑生成dn_dac《i》信号144,以在数字码信号dig《i》的第i位的是逻辑低(即未断言,参见图10a和10c)时具有与上信号urep(t)相等的脉冲,无论符号位的逻辑状态如何。相反地,当数字码信号dig《i》的第i位是逻辑高(即已断言)时,由门172、174和176提供的逻辑生成dn_dac《i》信号144,以在符号位未被断言(逻辑0)时具有与上信号urep(t)相等的脉冲,如图10b所示,

或者在符号位被断言时(逻辑1)具有与下信号drep(t)相等的脉冲,如图10d所示。

[0047]

现在参考图11a,图11a中示出在参考时钟信号clkref(t)和反馈时钟信号clkfb(t)的相似沿对准的情况a)中,cp电路20和电流d/a转换器电路150的操作时序图。如上所述,在这种情况下,pfd电路12将生成具有相同脉冲(标记为200)的上信号u(t)和下信号d(t),脉冲的宽度(较小)由与门18的操作时延(td)控制,以使第一ff电路14和第二ff电路16复位。结果,源电流i(20a)和吸收电流i(20b)相同,并且由于源电流贡献与吸收电流贡献抵消,输出电流icp(t)为零。

[0048]

由于上信号u(t)和下信号d(t)之间的相位差,待由d/a转换器电路150消除的噪声以上信号u(t)和下信号d(t)的脉冲宽度差的形式出现。在该情况a)中,由于参考时钟信号clkref(t)和反馈时钟信号clkfb(t)对准,上信号u(t)和下信号d(t)具有相同宽度(标记为200)。在这种情况下由dsm电路44生成的数字码信号dig[n]将不具有断言位,在图11a中记为“未断言”,并且符号位的值无关紧要。对此,应当注意的是,dsm电路44输出与成比例的数字码信号dig[n],并且当该式等于0时,码也是0并且码的任何位都未断言。通过逻辑电路140对电流d/a转换器电路150进行控制,使得对于等于最小脉冲宽度(td)加上由副本pfd电路130输出的向上信号urep(t)提供的相位差(pdo)之和的相同脉冲宽度(标记为206),所有电流源(路径)电路150a(的各个电流源)和所有电流吸收器(路径)电路150b(的各个电流吸收器)响应码的任何位均未被断言而致动(参见图8a、9a、9c、10a和10c)。结果,分别用于致动电流源和电流吸收器的源电流i(150a)和吸收电流i(150b)是相同的,并且由于源电流贡献与吸收电流贡献的偏移为零,输出电流ican(t)为零。

[0049]

现在参考图11b,图中示出在参考时钟信号clkref(t)的沿超前于反馈时钟信号clkfb(t)的相似沿的情况b)中,cp电路20和电流d/a转换器电路150的操作时序图。如上所述,在这种情况下,pfd电路12将生成下信号d(t)(如标记210所示),下信号d(t)的宽度(较小)由与门18的操作时延(td)控制,以使得第一ff电路14和第二ff电路16复位并且生成上信号u(t),上信号u(t)的宽度(较大)被控制为最小脉冲宽度(td)加上参考时钟信号clkref(t)与反馈时钟信号clkfb(t)的相似沿之间的时间差(即相位差-pd)之和的函数。结果,源电流i(20a)和吸收电流i(20b)不相同,并且输出电流icp(t)包括源电流贡献(即电流输入脉冲)。

[0050]

由于上信号u(t)和下信号d(t)之间的相位差,待由d/a转换器电路150消除的噪声以上信号u(t)和下信号d(t)的脉冲宽度差的形式出现。在该情况b)中,参考时钟信号clkref(t)的沿超前于反馈时钟信号clkfb(t)的相似沿,上信号u(t)具有比下信号d(t)更大的宽度。在这种情况下,补偿操作是致动比源电流i(150a)更多的吸收电流i(150b),从而补偿吸收电流i(20b)的较短致动。由dsm电路44生成的数字码信号dig[n]将具有一定数目的断言位(该数目为1-n)以及指示补偿是电流吸收操作的符号位(即符号位是逻辑0)。对此,应当注意的是,dsm电路44输出与成比例的数字码信号dig[n],并且当该式为非零时,码也为非零,并且码的至少一些位(与非零值成正比)被断言,并且符号位被设置为与非零值的符号相对应。因此,数字码信号dig[n]中的断言位的数目取决于上信号u(t)和下信号d(t)之间的相位差的幅度。通过逻辑电路140对电流d/a转换器电路150进行控制。对于数字码信号dig[n]未断言的位(在图11b中记为“未断言”)而言,相应电流源(路径)

电路150a(的各个电流源)和相应电流吸收器(路径)电路150b(的各个电流吸收器)被致动为相同的脉冲宽度(标记为216),该脉冲宽度等于最小脉冲宽度(td)加上由副本pfd电路130输出的上信号urep(t)提供的相位差(pdo)的和(见图8a、9a、9c、10a和10c)。结果,由于源电流贡献和吸收电流贡献抵消,这些电流源/吸收器路径的源电流i(150a)和吸收电流i(150b)相同,并且来自这些电流源/吸收电路的输出电流ican(t)的贡献为零。相反,对于数字码信号dig[n]位已经断言(在图11b中记为“断言”)的情况,致动相应的电流源(路径)电路150a(的各个电流源)为相同的脉冲宽度(标记为216u),该脉冲宽度等于由副本pfd电路130输出的下信号drep(t)提供的最小脉冲宽度(td)(见图8b和9d),并且致动相应的电流吸收器(路径)电路150b(的各个电流吸收器)为相同的脉冲宽度(标记为216d),该脉冲宽度等于最小脉冲宽度(td)加上由副本pfd电路130输出的上信号urep(t)提供的相位差(pdo)的和(见图8b和10b)。结果,这些电流源/吸收器路径的源电流i(150a)和吸收电流i(150b)不同,并且来自这些电流源/吸收器电路的输出电流ican(t)的贡献是用于补偿吸收电流i(20b)的较短致动的吸收电流脉冲。

[0051]

现在参考图11c,图中示出在反馈时钟信号clkfb(t)的沿超前于参考时钟信号clkref(t)的相似沿的情况c)中,cp电路20和电流d/a转换器电路150的操作时序图。如上所述,在这种情况下,pfd电路12将生成上信号u(t)(如标记220所示),上信号u(t)的宽度(较小)由与门18的操作时延(td)控制,以使得第一ff14和第二ff电路16复位并且生成下信号d(t),下信号d(t)的宽度(较大)被控制为最小脉冲宽度(td)加上参考时钟信号clkref(t)与反馈时钟信号clkfb(t)的相似沿之间的时间差(即相位差-pd)之和的函数。结果,源电流i(20a)和吸收电流i(20b)不相同,并且输出电流icp(t)包括吸收电流贡献(即电流吸收脉冲)。

[0052]

由于上信号u(t)和下信号d(t)之间的相位差,待由d/a转换器电路150消除的噪声以上信号u(t)和下信号d(t)的脉冲宽度差的形式出现。在该情况c)中,反馈时钟信号clkfb(t)的沿超前于参考时钟信号clkref(t)的相似沿,下信号d(t)具有比上信号u(t)更大的宽度。在这种情况下,补偿操作是致动比吸收电流i(150b)更多的源电流i(150a),从而补偿源电流i(20a)的较短致动。由dsm电路44生成的数字码信号dig[n]将具有一定数目的断言位(该数目为1-n)以及指示补偿是电流输入操作的符号位(即符号位是逻辑1)。对此,应当注意的是,dsm电路44输出与成比例的数字码信号dig[n],并且当该式为非零时,码也为非零,并且码的至少一些位(与非零值成正比)被断言,并且符号位被设置为与非零值的符号相对应。因此,数字码信号dig[n]中的断言位的数目取决于上信号u(t)和下信号d(t)之间的相位差的幅度。通过逻辑电路140对电流d/a转换器电路150进行控制。对于数字码信号dig[n]未断言的位(在图11c中记为“未断言”)而言,相应电流源(路径)电路150a(的各个电流源)和相应电流吸收器(路径)电路150b(的各个电流吸收器)被致动为相同的脉冲宽度(标记为226),该脉冲宽度等于最小脉冲宽度(td)加上由副本pfd电路130输出的上信号urep(t)提供的相位差(pdo)的和(见图8a、9a、9c、10a和10c)。结果,这些电流源/吸收器路径的源电流i(150a)和吸收电流i(150b)相同,并且由于源电流贡献与吸收电流贡献抵消,来自这些电流源/吸收器电路的输出电流ican(t)的贡献为零。相反,对于数字码信号dig[n]位已经断言(在图11c中记为“断言”)的情况,致动相应的电流吸收器(路径)电路150b(的各个电流吸收器)为相同的脉冲宽度(标记为226d),该脉冲宽度等于由副本

pfd电路130输出的下信号drep(t)提供的最小脉冲宽度(td)(见图8b和10d),并且致动相应的电流源(路径)电路150a(的各个电流源)为相同的脉冲宽度(标记为226u),该脉冲宽度等于最小脉冲宽度(td)加上由副本pfd电路130输出的上信号urep(t)提供的相位差(pdo)的和(见图8b和9b)。结果,这些电流源/吸收器路径的源电流i(150a)和吸收电流i(150b)不同,并且来自这些电流源/吸收器电路的输出电流ican(t)的贡献是用于补偿源电流i(20a)的较短致动的源电流脉冲。

[0053]

虽然附图和以上描述中已经详细说明并描述了本发明,但这些说明和描述应视为说明性或示例性的,而非限制性的;本发明不限于所公开的实施例。在实践所要求保护的发明的过程中,通过学习附图、公开内容及所附权利要求,本领域技术人员对于所公开实施例的其它变型是可以理解并实现的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。