1.本发明涉及soi(silicon on insulator,绝缘体上硅)基板等在绝缘膜上具有半导体单晶层的半导体基板的制造方法及半导体基板。

背景技术:

2.作为半导体元件用的半导体基板之一,有在作为绝缘膜的氧化硅膜之上形成有硅层(以下,有时称为soi层)的soi(silicon on insulator,绝缘体上硅)基板。在该soi基板中,由于作为器件制作区域的基板表层部的soi层通过埋入式氧化膜层(box层)而与基板内部电分离,因此具有寄生电容小,抗放射性能力高等特征。因此,期待高速、低功耗动作、防止软错误等效果,而有望成为高性能半导体元件用的基板。

3.作为制造该soi基板的代表性方法,可举出晶圆贴合法、simox法。晶圆贴合法例如在两片单晶硅基板(硅晶圆)中的一个的表面形成热氧化膜后,经由该形成的热氧化膜使两片晶圆贴紧,通过实施结合热处理而提高结合力,之后,通过镜面抛光等将其中一个晶圆(形成soi层的晶圆(以下称为结合晶圆)薄膜化,由此制造soi基板。作为该薄膜化的方法,有将结合晶圆磨削、磨光至所期望厚度的方法、或称为离子注入剥离法的方法等,该离子注入剥离法预先将氢离子或稀有气体离子的至少一种注入至结合晶圆的内部而形成离子注入层,贴合后,在离子注入层中将结合晶圆剥离。simox法将氧离子注入至单晶硅基板的内部,之后进行高温热处理(氧化膜形成热处理),使注入的氧与硅反应而形成box层,由此制造soi基板。

4.专利文献1、2记载了:通过在单晶硅基板的表面形成与单晶硅基板保持外延关系的氧化膜,并在该氧化膜上堆积外延层,而制作soi晶圆。另外,专利文献3记载了:在以离子注入剥离法进行的soi晶圆的制造方法中,可使用氮化硅膜作为埋入式绝缘膜。现有技术文献专利文献

5.专利文献1:日本专利公报第5168990号专利文献2:日本专利公报第5205840号专利文献3:国际公开第2004/010505号

技术实现要素:

(一)要解决的技术问题

6.作为soi晶圆的制造方法,如上所述有贴合法,但是由于贴合两片晶圆,因此有耗费材料成本、制造工序数较多的问题。另外,在simox法中,也有离子注入、高温热处理等制造工序数较多的问题。如果考虑形成的soi层与box层的品质、膜厚的自由度及均匀性,则在前述soi基板的制造方法中,离子注入剥离法最有前景,但是,例如为了获得厚度10nm的soi层,需要在形成了比该厚度厚的soi层之后,进行牺牲氧化处理来调整膜厚,因此工序变得复杂,无法避免高成本。

7.记载于专利文献3的作为绝缘膜的氮化硅膜与氧化硅膜相比介电常数大,因此具有以较薄的膜厚作为soi晶圆的埋入式绝缘膜发挥功能的优点。然而,在专利文献1、2中,并未公开形成氮化硅膜作为埋入式绝缘膜的内容或给出启示。在形成氮化硅膜作为埋入式绝缘膜的情况下,尚未知晓能够以简便的方法高生产率地获得soi基板的方法。

8.本发明是为了解决上述问题而完成的,其目的在于提供一种半导体基板的制造方法及半导体基板,在soi基板那样的半导体基板中,即使在将设置于单晶硅基板与半导体单晶层之间的绝缘膜设置为氮化硅膜的情况下,也能够以简便的方法高生产率且低成本地获得半导体基板,该soi基板在单晶硅基板的表面具有绝缘膜和该绝缘膜上的半导体单晶层。(二)技术方案

9.本发明为了实现上述目的而做出,提供一种半导体基板的制造方法,通过在单晶硅基板的表面依次形成绝缘膜及半导体单晶层,而制造在所述绝缘膜上具有所述半导体单晶层的半导体基板,至少包含以下工序:在含氮气气氛下对单晶硅基板进行热处理,在所述单晶硅基板的表面形成与所述单晶硅基板保持外延关系的氮化硅膜作为绝缘膜;以及在所述氮化硅膜上外延生长所述半导体单晶层。

10.根据这样的半导体基板的制造方法,能够以简便的方法高生产率且低成本地获得半导体基板。

11.此时,可以设置为将在所述含氮气气氛下进行热处理的温度设置为800℃以上的半导体基板的制造方法。

12.由此,能够更稳定可靠地在不使生产率降低的情况下形成氮化硅膜。

13.此时,可以设置为以下的半导体基板的制造方法,该方法使用外延生长装置作为所述热处理装置,在形成所述氮化硅膜之后,将所述外延生长装置内的气氛气体转换为半导体单晶层生长用气体,并进行所述外延生长。

14.由此,能够以极简便的方法更有效率、高生产率、低成本地获得高品质的半导体基板。

15.此时,可以设置为将所述半导体单晶层设置为si层、sige层、ge层、化合物半导体层中的任一个的半导体基板的制造方法。

16.由此,能够获得具有更优质的半导体单晶层的半导体基板。

17.此时,可以设置为将所述半导体单晶层设置为si层,将该si层的外延生长用气体设置为三氯硅烷的半导体基板的制造方法。

18.由此,能够以更高的生产率、低成本获得soi半导体基板。

19.此时,可以设置为将所述氮化硅膜的膜厚设置为2nm以下的半导体基板的制造方法。

20.由此,能够更稳定可靠地获得保持与基底的单晶硅基板的外延关系的氮化硅膜。

21.此时,可以设置为交替地形成多层所述氮化硅膜和所述半导体单晶层的半导体基板的制造方法。

22.由此,能够调整至合计所需的单晶硅基板与最表面的半导体单晶层间的绝缘耐压。同样地,通过交替地层叠多层,也能够形成纵型多层存储器的层叠构造、三维层叠型的集成电路等。

23.此时,可以设置为使用预先掺杂有氮或氧的单晶硅基板作为所述单晶硅基板的半

导体基板的制造方法。

24.由此,通过氮化硅膜的形成、之后的半导体结晶层的形成热历史及之后的追加热历史,从而追加形成氮化硅层本身、氮氧化硅层或氧化硅层,能够使氮化硅层的初始形成厚度变厚。

25.此时,可以设置为使用晶面方向(日语:面方位)为(111)的单晶硅基板作为所述单晶硅基板的半导体基板的制造方法。

26.晶面方向为(111)的单晶硅基板的表面构造由于与氮化硅膜(si3n4)的原子构造类似,能够适合用于形成与单晶硅基板保持外延关系的氮化硅膜,能够更稳定可靠地获得保持与基底的单晶硅基板的外延关系的氮化硅膜。

27.本发明还提供一种半导体基板,其在单晶硅基板的表面具有绝缘膜、及该绝缘膜上的半导体单晶层,所述绝缘膜是与所述单晶硅基板保持外延关系的氮化硅膜,所述半导体单晶层是外延生长层。

28.根据这样的半导体基板,能够简便且低成本地获得的具有高品质的半导体单晶层的半导体基板。

29.此时,可以设置为所述半导体单晶层是si层、sige层、ge层、化合物半导体层中的任一个的半导体基板。

30.由此,成为具有更优质的半导体单晶层的半导体基板。

31.此时,可以设置为所述氮化硅膜的膜厚为2nm以下的半导体基板。

32.由此,更稳定可靠地形成为保持与基底的单晶硅基板的外延关系的氮化硅膜。

33.此时,可以设置为交替地具有多层所述氮化硅膜和所述半导体单晶层的半导体基板。

34.由此,能够调整至合计所需的单晶硅基板与最表面的半导体单晶层间的绝缘耐压。另外,也能够形成纵型多层存储器的层叠构造、三维层叠型的集成电路等。

35.此时,可以设置为所述单晶硅基板的晶面方向为(111)的半导体基板。

36.由此,能够更稳定可靠地形成为保持与基底的单晶硅基板的外延关系的氮化硅膜。(三)有益效果

37.如上所述,根据本发明的半导体基板的制造方法,能够简便且低成本地提供具有作为绝缘膜的氮化硅膜与高品质的半导体单晶层的半导体基板。

附图说明

38.图1一并示出本发明的半导体基板的概念图与制造流程。图2示出实施例1的soi晶圆(半导体基板)的截面tem观察照片。图3示出图2的部分放大图(晶格影像)。图4示出实施例2的soi晶圆(半导体基板)的截面tem观察照片。图5示出图4的部分放大图(晶格影像)。

具体实施方式

39.以下,详细地说明本发明,但是本发明不限于此。

40.如上所述,寻求即使在将设置于单晶硅基板与半导体单晶层之间的绝缘膜设置为氮化硅膜时,也能够以简便的方法生产率高地获得半导体基板的半导体基板的制造方法及半导体基板。

41.本案发明人针对上述课题反复深入研究,结果发现当在含氮气气氛下对单晶硅基板进行热处理(热氮化)时,形成于单晶硅基板的表面的氮化硅膜会与基底的单晶硅基板保持外延关系。另外,想到如果是这样的氮化硅膜,则能够在该膜的表面外延生长半导体单晶层,从而完成了本发明。

42.即,发现一种半导体基板的制造方法,通过该方法能够简便且低成本地提供具有作为绝缘膜的氮化硅膜与高品质的半导体单晶层的半导体基板,从而完成了本发明,该半导体基板的制造方法通过在单晶硅基板的表面依次形成绝缘膜及半导体单晶层,而制造在所述绝缘膜上具有所述半导体单晶层的半导体基板,至少包含以下工序:在含氮气气氛下对单晶硅基板进行热处理,在所述单晶硅基板的表面形成与所述单晶硅基板保持外延关系的氮化硅膜作为绝缘膜;以及在所述氮化硅膜上外延生长所述半导体单晶层。

43.本案发明人还发现一种半导体基板,通过该半导体基板实现能够以低成本且简便的方法获得的具有作为绝缘膜的氮化硅膜与高品质的半导体单晶层的半导体基板,从而了完成本发明,该半导体基板在单晶硅基板的表面具有绝缘膜、及该绝缘膜上的半导体单晶层,所述绝缘膜是与所述单晶硅基板保持外延关系的氮化硅膜,所述半导体单晶层是外延生长层。

44.以下,参照附图进行说明。

45.在本发明中,“保特外延关系的氮化硅膜”是指具有可外延生长诸如单晶si层那样的半导体单晶层的程度的结晶性的氮化硅膜。

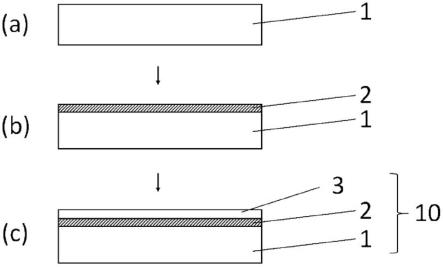

46.(半导体基板)首先,对本发明的半导体基板进行说明。在图1的(c)示出本发明的半导体基板10。本发明的半导体基板10至少在单晶硅基板1的表面具有作为绝缘膜的保持外延关系的氮化硅膜2、及该氮化硅膜2上的半导体单晶层3。

47.单晶硅基板1只要是单晶硅则没有特别限定,表面的取向、基板的电阻率、导电型(p或n)、掺杂剂的种类、直径(面积)、厚度等可以根据用途而适当选择、设定。可以是fz基板,也可以是cz基板,结晶中的氧浓度等物性也没有特别限定。

48.单晶硅基板1优选晶面方向是(111)。晶面方向为(111)的单晶硅基板的表面构造与氮化硅膜(si3n4)的原子构造类似,因此能够适用于形成与单晶硅基板保持外延关系的氮化硅膜。

49.另外,在本发明的半导体基板中,当在宽范围(例如,晶圆整个面)内设置例如2nm以下的较薄氮化硅膜时,单晶硅基板上的氮化硅膜需要具有较高的均匀性。在这种情况下,优选使用预先对单晶硅基板实施了退火处理的晶圆或预先在单晶硅基板上设置了外延硅层的晶圆作为单晶硅基板。通过退火处理或外延生长,改善了晶圆的表面平坦度,并能够形成为具有更高的均匀性的氮化硅膜2。

50.另外,通过使单晶硅基板1在晶面方向具有偏角而导入原子台阶,能够提高氮化硅膜的台阶生长速度,并改善氮化硅膜的均匀性。同样地,当在单晶硅基板整体或其表面具有高浓度掺杂物、或高浓度氧、或它们的硅析出物时,由于这些反应或变形等的影响而提高氮

化硅膜的台阶生长速度,能够形成为具有高均匀性的氮化硅膜2。

51.制造方法的详细情况在之后叙述,氮化硅膜2通过利用含氮气气氛下的热处理进行的硅的氮化而形成,是与单晶硅基板1“保持外延关系的氮化硅膜”。

52.上述的氮化硅膜2的膜厚越薄,则保持与基底的单晶硅基板1的外延的关系越稳定,因此优选将膜厚设置为2nm以下。

53.另外,氮化硅膜对高温气体的耐蚀刻特性比氧化硅膜高,因此作为后述的半导体单晶层3,能够使用三氯硅烷作为外延生长si层时的si源。在上述专利文献1、2中,使用了甲硅烷气体作为外延生长单晶si层时的原料气体,但是如本发明的半导体基板10这样将绝缘膜设置为氮化硅膜,则当在其上外延生长si层的半导体单晶层3时,能够使用比单硅烷廉价且生长速度也较高的三氯硅烷,因此能够获得量产时的成本优势。

54.半导体单晶层3是外延生长层。该半导体单晶层3在soi晶圆上作为所谓的soi层发挥功能。作为半导体单晶层3,优选设置为与基底的单晶硅基板1相同材料的si层,但是不限于si层,只要是接近单晶硅的晶格常数的半导体单晶层3,就能够外延生长。具体而言,能够举出sige层、ge层、化合物半导体层(gan层、aln层等)。如果是这些材料,则能够获得更优质的半导体单晶层。此外,半导体单晶层3的膜厚没有特别限定,能够根据所应用的器件的设计而适当设定。

55.另外,也可以交替地具有多层氮化硅膜2和半导体单晶层3。一层2nm以下的氮化硅膜2所具有的绝缘耐压能够通过交替地层叠多层氮化硅膜2和半导体单晶层3的构造,而调整至合计所需的单晶硅基板与最表面的半导体单晶层间的绝缘耐压。同样地,通过交替地层叠多层,也能够形成纵型多层存储器的层叠构造、三维层叠型的集成电路等。

56.(半导体基板的制造方法)接着,参照图1说明本发明的半导体基板的制造方法。

57.首先,如图1的(a)所示,准备用于在表面依次形成氮化硅膜2及半导体单晶层3的单晶硅基板1。

58.此时,也可以使用预先掺杂有氮或氧的单晶硅基板1。当使用这样的单晶硅基板1时,通过氮化硅膜2的形成、之后的半导体单晶层3的形成热历史及之后的追加热历史,从而追加形成氮化硅层自身、氮氧化硅层或氧化硅层,能够使氮化硅膜2的初期形成厚度变厚。

59.另外,如上所述,作为单晶硅基板,优选使用晶面方向为(111)的单晶硅基板。

60.另外,为了在宽范围(例如,晶圆整个面)内形成例如2nm以下这样的较薄氮化硅膜,形成在单晶硅基板上的氮化硅膜需要具有较高的均匀性。通过预先对单晶硅基板实施退火处理,或预先在单晶硅基板上外延生长硅层,而能够改善晶圆的表面平坦度,并改善形成在基板上的氮化硅膜的均匀性。另外,当使用使单晶硅基板的晶面方向具有偏角而导入原子台阶的晶圆、或者使用在单晶硅基板整体或其表面具有高浓度掺杂物、高浓度氧或它们的硅析出物的晶圆时,能够提高氮化硅膜的台阶生长速度,并改善氮化硅膜的均匀性。

61.接着,以如下方式在单晶硅基板1的表面上形成氮化硅膜2。首先,将准备好的单晶硅基板1投入热处理炉。然后,如图1的(b)所示,在单晶硅基板1的表面形成与单晶硅基板1“保持外延关系的氮化硅膜2”。“保持外延关系的氮化硅膜2”可通过在含氮气气氛下进行热处理而形成。具体而言,例如通过在氮气与氢气的混合气氛下进行热处理,能够获得保持外延关系的氮化硅膜2。此时,当氮气的混合比率较低时,热处理温度优选为高温(例如1100℃

以上),通过使氮气的混合比率提高,也可以设置为800℃左右的温度。由于在800℃以上的温度下,能够更稳定可靠地在不使生产率下降的情况下形成氮化硅膜,因此是优选的。热处理温度的上限没有特别限定,理论上只要不到单晶硅基板1的熔点即可,但是如果考虑生产率或对基板的热损伤等,则可以设置为1300℃左右以下。

62.另外,形成的氮化硅膜2的膜厚越薄,则越稳定可靠地保持与基底的单晶硅基板1的外延关系,因此氮化硅膜2的膜厚优选为2nm以下。氮化硅膜2的膜厚的下限只要保持了与基底的单晶硅基板1的外延关系则没有特别限定,可设置为0.3nm以上。

63.形成氮化硅膜2之后,如图1的(c)所示,使用外延生长装置,在氮化硅膜2上外延生长半导体单晶层3。作为生长的半导体单晶层3,如上所述,可举出si层、sige层、ge层、化合物半导体层(gan层、aln层等)。

64.另外,也可以交替地重复形成氮化硅膜2和半导体单晶层3,从而交替地形成多层氮化硅膜2和半导体单晶层3。一层2nm以下的氮化硅膜2所具有的绝缘耐压能够通过交替地层叠多层氮化硅膜2和半导体单晶层3的构造,而调整至合计所需的单晶硅基板1与最表面的半导体单晶层间的绝缘耐压。同样地,通过交替地层叠多层,也能够形成纵型多层存储器的层叠构造、三维层叠型的集成电路等。

65.半导体单晶层3的外延生长条件、使用的原料气体可根据生长的半导体单晶层3的种类而适宜设定、选择。由于本发明的半导体基板10具有氮化硅膜2作为绝缘膜,且与氧化硅膜相比而言氮化硅膜对高温气体的耐蚀刻特性较高,因此在外延生长如si层或sige层那样含si的半导体单晶层3时,能够使用三氯硅烷作为原料气体。而且,由于三氯硅烷比甲硅烷廉价,生长速度也快,因此在能够获得量产时的成本优势这一点上是有利的。另外,三氯硅烷是比甲硅烷更易处理的材料,安全性高,也能够降低制造设备所花费的成本。

66.如上所述,能够获得在单晶硅基板1的表面具有作为绝缘膜的与单晶硅基板1保持外延关系的氮化硅膜2、及绝缘膜上的外延生长层即半导体单晶层3的半导体基板10。如果是这样的半导体基板的制造方法,由于不会如贴合法那样需要两片晶圆,因此能够降低材料成本。另外,也可使制造步骤减少,而能够以简便的方法实现高生产率,并降低整体成本。

67.作为上述的半导体基板10的制造方法中的、用于将单晶硅基板1的表面氮化而形成氮化硅膜2的热处理装置,只要是能够在含氮气气氛下进行热处理而将单晶硅基板1的表面氮化的热处理装置,则没有特别限定。例如,可使用利用灯加热等的rtp(rapid thermal processing,快速热处理)装置、批处理式的电阻加热炉、或在基板进行外延生长的外延生长装置等。其中,优选使用外延生长装置。

68.如果使用外延生长装置,则在外延生长装置内进行用于氮化的热处理,在单晶硅基板1的表面上形成氮化硅膜2之后,通过将炉内的气氛气体转换成半导体单晶层3的外延生长用气体,从而能够进行半导体单晶层3的外延生长。由此,可在同一炉内连续地进行氮化硅膜2的生长、半导体单晶层3的外延生长,因此能够以极简便的方法高效、高生产率地制造半导体基板10。另外,由于能够以相同的装置进行氮化硅膜2的形成与半导体单晶层3的外延生长而不会引起伴随装置间的移动的污染,因此能够获得污染等级低的高品质的半导体基板10。实施例

69.以下,举出实施例而详细地说明本发明,但是并不限定本发明。

70.(实施例1)制作在硅晶圆(单晶硅基板)的表面具有与硅晶圆保持外延关系的氮化硅膜(绝缘膜)、及该氮化硅膜上的si外延生长层(半导体单晶层/soi层)的soi晶圆(半导体基板),进行了构造的评价。制造条件如下。

71.(soi晶圆的结构)si晶圆:直径200mm、晶面方向(100)、p型、10ωcm绝缘膜:氮化硅soi层:si外延生长层

72.(soi晶圆的制造条件)热处理装置:单片式外延生长装置氮化硅膜:n224slm h234slm热处理温度1190℃热处理时间300秒si(soi层):三氯硅烷10slm h234slm生长温度1070℃生长时间600秒生长速度2.4μm/min。

73.使用穿透式电子显微镜(tem),观察了所得的soi晶圆的截面。在图2中示出通过实施例1制造的soi晶圆(半导体基板)的截面tem观察照片。图3是将图2的氮化硅膜附近放大后的晶格影像。如图2所示,可知在si晶圆与soi层(si外延生长层)之间形成了1.4~1.5nm左右的氮化硅膜。另外,如图3所示,可知在si晶圆的表面上形成有与si晶圆保持外延关系的氮化硅膜(在氮化硅膜的部分观察的晶格影像)、及在该氮化硅膜上外延生长的si外延生长层。此外,对于氮化硅膜的部分,通过tem-edx进行膜中的元素分析,结果确认检测出si和n。

74.(实施例2)(soi晶圆的结构)si晶圆:直径150mm、晶面方向(111)、p型、50ωcm绝缘膜:氮化硅soi层:si外延生长层

75.(soi晶圆的制造条件)热处理装置:单片式外延生长装置氮化硅膜:n224slm h234slm热处理温度1190℃热处理时间300秒si(soi)层:三氯硅烷10slm h234slm

生长温度1130℃生长时间15秒生长速度3.8μm/min

76.使用穿透型电子显微镜(tem),观察了所得的soi晶圆的截面。在图4中示出通过实施例2制造的soi晶圆(半导体基板)的截面tem观察照片。图5是将图4的氮化硅膜附近放大后的晶格影像。如图4所示,可知在si晶圆与soi层(si外延生长层)之间形成了0.9~1.1nm左右的氮化硅膜。另外,如图5所示,可知在si晶圆的表面上形成有与si晶圆保持外延关系的氮化硅膜(在氮化硅膜的部分观察的晶格影像)、及在该氮化硅膜上外延生长的si外延生长层。此外,对于氮化硅膜的部分,通过tem-edx进行膜中的元素分析,结果确认检测出si和n。

77.如上所述,根据本发明的实施例,能够以简便且生产率高的方法获得在单晶硅基板的表面上形成有与单晶硅基板保持外延关系的氮化硅膜、及si外延生长层的高品质的soi晶圆。

78.此外,本发明不限于上述实施方式。上述实施方式是例示,凡具有与本发明的权利要求书所记载的技术思想实质上相同的结构、起到同样的作用效果的任何方案都包含在本发明的技术范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。