1.本揭露的实施例涉及一种电子装置的制造方法,尤其涉及一种封装电路的制造方法。

背景技术:

2.随着具有封装电路的电子装置的应用持续的增广,对于封装电路的制造良率质量的要求越来越高。因此,电子装置的封装电路的制造方法(包括检测方法)须持续更新与调整。

技术实现要素:

3.根据本揭露的实施例,封装电路的制造方法包括以下步骤。形成电路结构,电路结构具有多个导电接垫。形成液晶层于电路结构上。执行检测步骤,包括根据液晶层受电场所转动的结果来判断多个导电接垫的导通状况。以及,去除液晶层。

附图说明

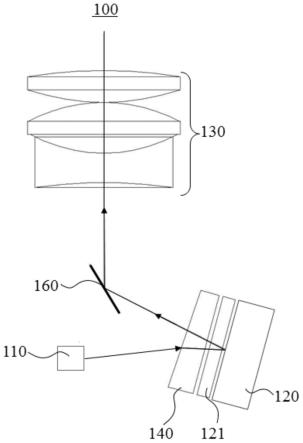

4.图1为本揭露一实施例的封装电路于检测步骤的剖面示意图;

5.图2为本揭露一实施例的裁切前的封装电路的剖面示意图;

6.图3为图2的裁切前的封装电路的剖面线a-a’的剖面示意图;

7.图4为本揭露另一实施例的封装电路于检测步骤的剖面示意图;

8.图5为本揭露另一实施例的封装电路于检测步骤的剖面示意图;

9.图6为本揭露另一实施例的封装电路于检测步骤的剖面示意图;

10.图7为本揭露另一实施例的封装电路的制造方法的流程图;

11.图8为本揭露另一实施例的电路结构的局部放大立体示意图;

12.图9为本揭露另一实施例的封装电路的制造方法的流程图;

13.图10为本揭露又一实施例的封装电路的制造方法的流程图;

14.图11为本揭露再一实施例的封装电路的制造方法的流程图。

具体实施方式

15.通过参考以下的详细描述并同时结合附图可以理解本揭露,须注意的是,为了使读者能容易了解及为了附图的简洁,本揭露中的多张附图只绘出电子装置的一部分,且附图中的特定元件并非依照实际比例绘图。此外,图中各元件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。

16.揭露通篇说明书与后附的权利要求中会使用某些词汇来指称特定元件。本领域技术人员应理解,电子设备制造商可能会以不同的名称来指称相同的元件。本文并不意在区分那些功能相同但名称不同的元件。在下文说明书与权利要求书中,“包括”、“含有”、“具有”等词为开放式词语,因此其应被解释为“含有但不限定为

…”

之意。因此,当本揭露的描

述中使用术语“包括”、“含有”和/或“具有”时,其指定了相应的特征、区域、步骤、操作和/或构件的存在,但不排除一个或多个相应的特征、区域、步骤、操作和/或构件的存在。

17.本文中所提到的方向用语,例如:“上”、“下”、“前”、“后”、“左”、“右”等,仅是参考附图的方向。因此,使用的方向用语是用来说明,而并非用来限制本揭露。在附图中,各附图示出的是特定实施例中所使用的方法、结构和/或材料的通常性特征。然而,这些附图不应被解释为界定或限制由这些实施例所涵盖的范围或性质。举例来说,为了清楚起见,各膜层、区域和/或结构的相对尺寸、厚度及位置可能缩小或放大。

18.应当理解到,当组件或膜层被称为“连接至”另一个组件或膜层时,它可以直接连接到此另一组件或膜层,或者两者之间存在有插入的组件或膜层。当组件被称为“直接连接至”另一个组件或膜层时,两者之间不存在有插入的组件或膜层。另外,当构件被称为“耦接于另一个构件(或其变体)”时,它可以直接地连接到此另一构件,通过一或多个构件间接地连接(例如电性连接)到此另一构件。

19.在本揭露中,长度与宽度的测量方式可以是采用光学显微镜测量而得,厚度则可以由电子显微镜中的剖面图像测量而得,但不以此为限。另外,任两个用来比较的数值或方向,可存在着一定的误差。

20.术语“大约”、“等于”、“相等”或“相同”、“实质上”或“大致上”一般解释为在所给定的值或范围的20%以内,或解释为在所给定的值或范围的10%、5%、3%、2%、1%或0.5%以内。

21.本揭露中所叙述的一结构(或层别、组件、基底)位于另一结构(或层别、元件、基底)之上,可以指二结构相邻且直接连接,或可指二结构相邻而非直接连接,非直接连接是指二结构之间具有至少一中介结构(或中介层别、中介组件、中介基底、中介间隔),一结构的下侧表面相邻或直接连接于中介结构的上侧表面,另一结构的上侧表面相邻或直接连接于中介结构的下侧表面,而中介结构可以是单层或多层的实体结构或非实体结构所组成,并无限制。在本揭露中,当某结构配置在其它结构“上”时,有可能是指某结构“直接”在其它结构上,或指某结构“间接”在其它结构上,即某结构和其它结构间还夹设有至少一结构。

22.本揭露说明书内的“第一”、“第二”...等在本文中可以用于描述各种元件、部件、区域、层和/或部分,但是这些元件、部件、区域、和/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。因此,下面讨论的“第一元件”、“部件”、“区域”、“层”、或“部分”是用于与“第二元件”、“部件”、“区域”、“层”、或“部分”区隔,而非用于限定顺序或特定元件、部件、区域、层和/或部分。

23.在本揭露中,厚度、长度与宽度的测量方式可采用光学显微镜测量而得,厚度则可以由电子显微镜中的剖面图像测量而得,但不以此为限。另外,任两个用来比较的数值或方向,可存在着一定的误差。若第一值等于第二值,其隐含着第一值与第二值之间可存在着约10%的误差;若第一方向垂直于第二方向,则第一方向与第二方向之间的角度可介于80度至100度之间;若第一方向平行于第二方向,则第一方向与第二方向之间的角度可介于0度至10度之间。

24.除非另外定义,在此使用的全部用语(包括技术及科学用语)具有与此篇揭露所属的一般技艺者所通常理解的相同涵义。能理解的是这些用语,例如在通常使用的字典中定义的用语,应被解读成具有一与相关技术及本揭露的背景或上下文一致的意思,而不应以

一理想化或过度正式的方式解读,除非在此特别定义。

25.须说明的是,下文中不同实施例所提供的技术方案可相互替换、组合或混合使用,以在未违反本揭露精神的情况下构成另一实施例。

26.电子装置具有本揭露实施例的封装电路可达到多种应用的效果,电子装置可包括显示装置、天线装置、感测装置、拼接装置或透明显示装置,但不以此为限。电子装置可为可卷曲、可拉伸、可弯折或可挠式电子装置。电子装置可例如包括液晶(liquid crystal)、发光二极管(light emitting diode,led)、量子点(quantum dot,qd)、荧光(fluorescence)、磷光(phosphor)或其他适合的材且其材料可任意排列组合或其他适合的显示介质,或前述的组合;发光二极管可例如包括有机发光二极管(organic light emitting diode,oled)、毫米/次毫米发光二极管(mini led)、微发光二极管(micro led)或量子点发光二极管(quantum dot,qd,可例如为qled、qdled),但不以此为限。天线装置可例如是液晶天线,但不以此为限。拼接装置可例如是显示器拼接装置或天线拼接装置,但不以此为限。需注意的是,电子装置(包括封装电路)的外型可为矩形、圆形、多边形、具有弯曲边缘的形状或其他适合的形状。下文将以封装电路说明本揭露内容,但本揭露不以此为限。

27.在本揭露中,以下所述的各种实施例可在不背离本揭露的精神与范围内做混合搭配使用,例如一实施例的部分特征可与另一实施例的部分特征组合而成为另一实施例。

28.现将详细地参考本揭露的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

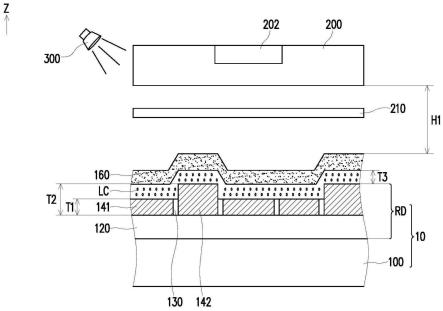

29.图1为本揭露一实施例的封装电路于检测步骤的剖面示意图。为了附图清楚及方便说明,图1省略示出了若干元件。请先参考图1,本揭露的封装电路10包括基板100及电路结构rd。电路结构rd例如包括重布线层结构(redistribution layer,rdl)。在一些实施例的装电路10的制造方法中,重布线层结构例如于进行电子元件耦接工艺前可先进行电性检测,电子元件例如包括集成电路(integrated circuit,ic),但不限于。本揭露实施例的封装电路的制造方法包括检测步骤,以减少电子元件(例如集成电路)耦接至导通状况不佳的电路结构rd。藉此,封装电路10的制造方法具有简化工艺或减少成本的效果。以下简单说明封装电路10的制造方法的步骤。

30.首先,提供基板100。封装电路10的基板100可包括硬质基板、可挠性基板或前述的组合,基板100的材料例如可包括玻璃、石英、陶瓷、蓝宝石、塑胶、聚碳酸酯(polycarbonate,pc)、聚酰亚胺(polyimide,pi)、聚丙烯(polypropylene,pp)或聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、其他合适的材料或前述材料的组合,但不以此为限。基板100的透光率不加以限制,基板100可为透光基板、半透光基板或不透光基板。

31.接着,在基板100表面的法线方向z上,于基板100上形成电路结构rd。电路结构rd具有多个导电接垫。详细来说,电路结构rd包括设置于基板100上的内连线结构120及设置于内连线结构120上的多个导电接垫141、142,但不限于此。在一些实施例中,内连线结构120例如是电路结构rd中的下层电路层,内连线结构120包括多层介电层与多层导电层交互堆叠的叠层(图未示),但不限于此。介电层可包括单层或多层结构,其材料可包括有机材料、无机材料或前述的组合,但不以此为限。所述有机材料可包含聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、聚乙烯(polyethylene,pe)、聚醚砜

(polyethersulfone,pes)、聚碳酸酯(polycarbonate,pc)、聚甲基丙烯酸甲酯(polymethylmethacrylate,pmma)、聚酰亚胺(polyimide,pi)、感光型聚酰亚胺(photo sensitive polyimide,pspi)或前述的组合,而所述无机材料可包含氮化硅、氧化硅、氮氧化硅或前述的组合,但不以此为限。所述导电层可为单层导电材料或多层导电材料的堆叠,导电层的材料可包括钼(molybdenum,mo)、镍(nickel,ni)、铬(chromium,cr)、钨(tungsten,w)、铝(aluminum,al)、钛(titanium,ti)、铜(copper,cu)、锡(tin,sn)、银(silver,ag)、金(gold,au)、其他合适的金属或上述材料的合金或组合。在一些实施例中,多层导电层可分别由多层介电层所隔开,多层导电层可通过多个贯穿介电层的连接结构(未示出)以互相电性连接,但不以此为限。

32.在一些实施例中,多个导电接垫(例如导电接垫141及导电接垫142)设置于内连线结构120上。具体来说,内连线结构120上设置或形成一层绝缘层130,绝缘层130可图案化以具有多个开孔(未标示),多个导电接垫(例如导电接垫141及导电接垫142)可分别对应且设置在此些绝缘层130的开孔中。多个导电接垫(例如导电接垫141及导电接垫142)可分别与内连线结构120中的导电层耦接,但不以此为限。图1所示的导电接垫的数目不限制本揭露的实施例,导电接垫的数目可依据使用者的需求而增加或减少。在一些实施例中,导电接垫例如是作为电路结构rd的导电凸块(bump),导电接垫在后续工艺中例如将与电子元件(例如集成电路)耦接。

33.在一些实施例中,导电接垫的材料可相似于上述内连线结构120中的导电层,例如包括钼、镍、铬、钴、锆、钨、铝、钛、铜、锡、银、金、其他合适的金属、或上述材料的合金或组合。导电接垫(例如导电接垫141及导电接垫142)可为单层金属层或多层金属层堆叠的叠构,但不以此为限。

34.在一些实施例中,不同导电接垫(例如导电接垫141及导电接垫142)的顶面可以齐平或不齐平。举例来说,如图1,导电接垫141的顶面与导电接垫142的顶面可不齐平。

35.在一些实施例中,导电接垫141的厚度t1可相同或不同于导电接垫142的厚度t2,但不以此为限。厚度t1及厚度t2可定义为该导电接垫于基板100表面的法线方向z上的最大厚度。

36.在一些实施例中,于完成电路结构rd后,封装电路10可进行电子元件(例如集成电路)的耦接等工艺以应用于半导体领域、显示领域或其他电子装置领域。在进行上述电子元件(例如集成电路)的耦接工艺之前,可先通过检测步骤以判断导电接垫(例如导电接垫141及导电接垫142)的电性质量以减少将电子元件(例如集成电路)设置于不符合电性质量要求的封装电路的风险。

37.在本实施例中,在执行检测步骤之前,形成液晶层lc于电路结构rd上。一些实施例中,液晶层lc例如包括聚合型分散液晶(polymer-dispersed liquid crystal film,pdlc)、胆固醇液晶、高分子液晶、染料液晶(dye-doped liquid crystal)、电泳显示介质、其它合适材料或上述的组合。在一些实施例中,液晶层lc包括的液晶分子包括负型液晶或正型液晶。

38.在一些实施例中,在设置液晶层lc于电路结构rd上后,可根据液晶层lc的材料特性选择性地进行固化(curing)工艺,以完成液晶层lc设置。一些实施例中,液晶层lc可整面地或局部地覆盖在电路结构rd(导电接垫141与导电接垫142)上。液晶层lc可具有厚度t3,

厚度t3可定义为液晶层lc于基板100表面的法线方向z上的最大厚度。在一些实施例中,液晶层lc的厚度t3可为2微米至50微米(例如:2微米≦厚度t3≦50微米)或5微米至30微米(5微米≦厚度t3≦30微米),但不以此为限。在一些实施例中,液晶层lc中可设置多个间隔物(spacer;图未示),间隔物可用以维持液晶层的厚度,但不以此为限。

39.接着,在液晶层lc上形成透明导电层160。透明导电层160的材料包括氧化铟锡(indium tin oxide,ito)、氧化铟(indium oxide,in2o3)、氧化锡(tin oxide,sno2)、氧化锌(zinc oxide,zno)、其他合适材料或上述的组合,但不以此为限。

40.接着,提供检测装置200。检测装置200例如是检测头(detector head)。在一些实施例中,检测装置200可包括感测器202。感测器202例如包括光感测器(photosensor)、图像感测器(image sensor)或其它合适的感测器。在一些实施例中,以光感测器、图像感测器或其它合适的感测器以检测液晶层lc转动的结果。

41.接着,执行检测步骤。检测步骤包括,首先,提供电源信号,以分别施加预设的电压至多个导电接垫中的至少一者(包括导电接垫141或导电接垫142)及透明导电层160,以产生电场。以图1为例,通过分别施加预设的电压至不同的导电接垫,此些导电接垫与透明导电层160之间例如可产生垂直电场。接着,当此些导电接垫如预期接受到预设的电压时而产生电场,此电场会改变液晶层lc中的液晶分子(未标示)的排列,例如液晶分子可根据其特性而依据电场而转动。接着,可选择性使用具有指向性的光源300作为检测电路结构rd的检测光。在一些实施例中,光源300也可为非指向性的光源,例如包括环境光源,但不限于此。接着,使用者可根据液晶层lc中液晶分子受电场转动的结果来判断多个导电接垫(包括导电接垫141或导电接垫142)的导通状况。

42.在一些实施例的检测步骤中,可通过检测光被多个导电接垫(包括导电接垫141或导电接垫142)的反射程度来判断此些导电接垫的导通状况或电性质量。举例来说,以导电接垫141所接收的电压值相近预定电压值(即与导电接垫141连接的线路中可能正常导通),而导电接垫142所接收的电压值低于预定电压值(即与导电接垫142连接的线路中可能发生短路而无法接收到预定电压值)来说明,导电接垫141与透明导电层160之间的液晶层lc会受到导电接垫141与透明导电层160之间所产生的电场(例如垂直电场)而如预期的转动,使光源300所发射的检测光可通过液晶层lc,并经由导电接垫141(例如导电接垫141的表面)而反射。另外,因导电接垫142所接收的电压值低于预定电压值,故导电接垫142与透明导电层160之间可能无法产生预期的电场(例如垂直电场),故位于导电接垫142与透明导电层160之间的液晶层lc可能无法如预期的转动(或转动的程度不如预期),使光源300所发射的检测光通过位于导电接垫142与透明导电层160之间液晶层lc的量会不同于位于导电接垫141与透明导电层160之间液晶层lc,后续经由导电接垫142(例如导电接垫142的表面)而反射的光量也会不同。上述检测光在导电接垫141或在导电接垫142上的所反射的光可被检测装置200的感测器202所检测并输出,可通过分别将导电接垫141的反射光或导电接垫142的反射光以图像或数值文字来呈现,藉此判断不同导电接垫及其分别所连接的线路的导通状况,以判断是否有短路问题。详细来说,由于导电接垫141的电压接近预定电压值,故对应导电接垫141上(或位于导电接垫141与透明导电层160之间)的液晶层lc中的液晶分子受到电场而转动,使较多的检测光通过且经由导电接垫141反射,此些反射光例如为第一反射光。由于导电接垫142的电压低于预定电压值,故对应导电接垫142上(或位于导电接垫142与透

明导电层160之间)的液晶层lc中的液晶分子受到电场而转动的比例较少,使较少的检测光通过且经由导电接垫142反射,此些反射光光例如为第二反射光,第一反射光所产生的图像强度(例如图像光的亮暗程度)或文字数值可能大于第二反射光所产生的图像强度或文字数值。相较于导电接垫141,导电接垫142可能显示较暗的图像而被判断不符合预期的标准,故使用者可判断第二导电接垫142的导通状况为异常。上述的说明为示意性地解释检测步骤中判断此些导电接垫的导通状况的原理,不旨在限制本揭露导电接垫141、142的导通状况。

43.如此,使用者可通过上述的图像的亮暗或数值的大小来判断导电接垫141或导电接垫142的导通状况是否符合预期的标准。如判断不符合预期的标准,则可视为导电接垫的导通状况为异常。在其它实施例,可根据封装电路的叠层状况、或液晶层材料的选择不同而有其它的判断导电接垫是否导通的方式。

44.须注意的是,本案的检测步骤不限定需将不同的导电接垫(例如导电接垫141及导电接垫142)施加相同的预定电压(即预定电压值相同)。在一些实施例中,导电接垫141的预定电压值与导电接垫142的预定电压值可以不同,可分别依据每个导电接垫于检测步骤中所产生的图像亮暗或数值大小的结果进行导电接垫的导通状况的判断。在一些实施例中,本案的检测步骤不限定需将不同的导电接垫(例如导电接垫141及导电接垫142)于同一时间点施加预定电压,不同的导电接垫(例如导电接垫141及导电接垫142)亦可分别于不同时间点施加预定电压,并分别与透明导电层160之间产生电场,并根据所对应的液晶层lc受电场所转动的结果来分别判断所述不同导电接垫的导通状况。

45.本揭露一实施例的封装电路10的制造方法可将液晶层lc形成于待检测的电路结构rd上,再根据液晶层lc中液晶分子受到电场转动的结果来判断导电接垫141、142的导通状况,此种检测方式为非接触式检测,可减少导电接垫(例如导电接垫141及导电接垫142)于检测时受到的损害的风险。另外,由于液晶层lc设置于电路结构rd上,检测装置200与电路结构rd的检测距离h1可不受限制。检测距离h1的定义为检测装置200的检测表面至透明导电层160的顶面(邻近于检测装置200的表面)之间的最短距离,但不以此为限。在一些实施例中,检测装置200与电路结构rd之间的检测距离h1可以大于1厘米。此外,由于封装电路10的制造方法可在制造过程中进行检测步骤,可减少后续在不符合规格的封装电路上进行电子元件耦接工艺的机率,减少成本或提升质量。

46.在一些实施例中,封装电路10的制造方法还可选择性包括,在进行检测步骤前,先设置偏光元件210于液晶层lc(或透明导电层160)上。以图1为例,偏光元件210设置于液晶层lc与检测装置200之间。在一些实施例中,偏光元件210设置于透明导电层160与检测装置200之间。在一些实施例中,偏光元件210可以直接设置于透明导电层160上,但不以此为限。在上述的偏光元件210的设置下,反射光的亮暗对比可更显著,可增加于检测步骤中对导电接垫的导通状况的判断灵敏度。此外,于一些实施例中(未示出),于设置液晶层lc的步骤之前,可根据液晶层lc的种类选择性在电路结构rd上形成液晶配向层(未示出),但不以此为限。

47.接着,于检测步骤完成后,去除液晶层lc。去除液晶层lc的方式包括使用丙酮、酒精或其它合适的溶剂去除,但不限于此。在一些实施例中,去除液晶层lc的方式包括物理撕开的方式,但不以此为限。在一些实施例中,可将液晶层lc和/或透明导电层160设于一基底

上,后续将设有液晶层lc和/或透明导电层160设于基底(可参考后续图5的基底150)设置于电路结构rd上,而基底(可参考后续图5的基底150)可位于电路结构rd与液晶层lc之间,后续如上所述完成检测步骤后,可通过撕除基底(可参考后续图5的基底150)以将液晶层lc与透明导电层160一起去除,但不限于此。上述基底可包括软性基底,例如聚酰亚胺基板或其它合适的材料,但不限于此。

48.在一些实施例中,撕除的基底(其上设有液晶层lc与透明导电层160)可以重复使用在其他的待检测的封装电路上,藉此节省成本或省略工艺程序。

49.以下将列举其他实施例以作为制作方法的说明。在此必须说明的是,下述实施例沿用前述实施例的元件标号与部分内容,其中采用相同的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

50.图2为本揭露一实施例的裁切前的封装电路的剖面示意图。图3为图2的裁切前的封装电路的剖面线a-a’的剖面示意图。为了附图清楚及方便说明,图2及图3省略示出了若干元件。本实施例所示的制造方法与图1的封装电路10的制造方法的差异在于,封装电路的制造方法还包括形成框胶160与电路结构rd上,且框胶160可环绕液晶层lc。

51.本实施例的封装电路的制造方法可包括先在裁切前的基板100’(例如母板)上形成多个裁切前的封装电路20’,再通过裁切工艺来形成多个单一的封装电路(例如图1所示的封装电路10)。具体来说,本实施例的制造方法包括:首先,提供裁切前的基板100’(母板),可在后续工艺中被裁切成多封装元件),此些封装元件分别具有封装电路20’。

52.接着,在基板100’上形成多个电路结构rd。请同时参考图2及图3,内连线结构120设置于基板100’上。接着,导电接垫(例如导电接垫141及导电接垫142)设置于内连线结构120上。在一些实施例中,多个裁切前的封装电路20’可在x轴上和/或y轴上依续排列,但不限于此,x轴大致垂直于y轴,且x轴或y轴垂直于基板100表面的法线方向z。在一些实施例中,多个裁切前的封装电路20’可例如以阵列或其它方式排列。在一些实施例中,多个裁切前的封装电路20’可以沿着x轴排成多个横行,或沿着y轴排成多个直列。举例来说,在裁切前的基板100’上可包括三个横行及四个直列的裁切前封装电路20’。须注意的是,图2所示的裁切前封装电路20’的数目及其排列方式并非用于限制本揭露,母板100’可裁切出的封装电路的数目及排列方式可依使用者的需求调整。

53.接着,在电路结构rd上形成框胶180,框胶180可分别环绕至少一或多个裁切前封装电路20’。在一些实施例中,框胶180可环绕多个裁切前封装电路20’中的导电接垫(例如导电接垫141及导电接垫142)。如图2所示,在基板100表面的法线方向z上,框胶180的外型可具有弧角的矩形,但不以此为限,框胶180可根据需求而设计其它外型。在一些实施例中,框胶180所环绕的裁切前封装电路20’的数量也可以更多或更少。框胶180所环绕的裁切前封装电路20’的排列方式可包括多个横行或多个多排或上述的组合,不限于图2所示的数目或排列。框胶180的材料例如包括光敏性光阻、光敏性树脂或热固化树脂或其它合适材料,但不以此为限。

54.接着,形成液晶层lc于多个导电接垫(例如导电接垫141及导电接垫142)上,框胶180可环绕液晶层lc。在一些实施例中,框胶180的高度可高于液晶层lc,使液晶层lc不会溢出框胶180外。

55.接着,形成透明导电层160于液晶层lc上,透明导电层160可选择性设置于或未设置于框胶180上,但不以此为限。

56.接着,可选择性设置偏光元件210于液晶层lc上。然后,进行检测步骤。如上所述,先分别施加预设的电压至导电接垫141(和/或导电接垫142)及透明导电层160,以产生电场(例如垂直电场)转动位于导电接垫141(和/或导电接垫142)及透明导电层160之间的液晶层lc中的液晶分子。接着,光源300的检测光可部份的穿过偏光元件210,并根据液晶分子的转动状况照射在导电接垫141或导电接垫142上。然后,上述检测光经由导电接垫141或导电接垫142将光反射,此些反射光可被检测装置200的感测器202所检测并输出图像图像或数值文字,但不限于此。使用者可通过上述的图像的亮暗或数值的大小来判断导电接垫141或导电接垫142的导通状况是否符合预期的标准。

57.接着,使用者可进行后续的裁切步骤以将多个未裁切的封装电路20’彼此分离,且可根据前述的导电接垫的检测结果决定是否于封装电路20’耦接电子元件。

58.图4为本揭露另一实施例的封装电路于检测步骤的剖面示意图。为了附图清楚及方便说明,图4省略示出了若干元件。本实施例所示的封装电路30于检测步骤时的配置大致相似于图1的封装电路10于检测步骤时的配置,因此两实施例中相同与相似的构件于此不再重述。本实施例不同于检测封装电路10的配置之处主要在于:于设置液晶层lc的步骤后(未在于液晶层lc上设置透明导电层160),接着提供检测装置200并进行检测步骤。

59.本实施例的检测步骤包括,首先,提供电源信号,以分别施加预设的电压至多个导电接垫中的至少相邻两者,以产生电场,而施加于多个导电接垫中的至少两者的电压可以不同。上述的电接垫中的至少相邻两者例如为导电接垫141(邻近于导电接垫142)及导电接垫142,或者为导电接垫142及导电接垫143(邻近于导电接垫142),但不以此为限。以图4为例,使用者可分别施加预设的电压至导电接垫141及导电接垫142,使导电接垫141与导电接垫142之间产生电场(例如水平电场)。水平电场例如为垂直于基板100表面的法线方向z上的电场。

60.接着,上述产生的电场(例如水平电场)会改变液晶层lc中的液晶分子的转动,例如导致液晶分子根据电场的方向而转动,但不限于此。接着,可选择性使用具有指向性的光源300作为检测光。接着,相似于图1的实施例,使用者可根据液晶层lc中液晶分子受电场转动的结果来判断此些导电接垫(包括导电接垫141、导电结构142或导电结构143)的导通状况。上述的分别施加预设的电压至导电接垫141及导电接垫142,或者分别施加预设的电压至导电接垫142及导电接垫143(邻近于导电接垫142),以产生电场,可例如在不同时间点测试,通过将导电接垫142交替式的与相邻的不同导电接垫(例如导电接垫141及导电接垫143,但不限于此)分别检测,以获得此些导电接垫(包括导电接垫141、导电结构142或导电结构143)的导通状况。

61.举例来说,以导电接垫141的电压值低于预定电压值,导电接垫142与相邻的导电接垫143的电压值接近预定电压值,导电接垫141与导电接垫143分别邻近于导电接垫142且位于导电接垫142的相对两侧来说明。由于位于导电接垫141与导电接垫142上的液晶层lc受到电场(水平电场)后的转动较少(即液晶分子无法达到预期的转动程度),而导电接垫142与导电接垫143上的液晶层lc受到电场后的转动较多(即液晶分子大致达到预期的转动程度),因此检测光通过于导电接垫141与导电接垫142上方的液晶层lc的量降低,故此检测

光被反射的量较预期的低(即检测装置200所检测的亮度较低),而检测光通过于导电接垫142与导电接垫143上方的液晶层lc的量较符合预期,故此检测光被反射的量可符合预期(即检测装置200所检测的亮度较符合预期)。藉此,使用者可通过如上述的交替式的测试比对来判断导电接垫(包括导电接垫141、导电结构142或导电结构143)的导通状况。

62.上述的封装电路30的制造方法为非接触式检测的技术,减少导电接垫于检测时受到的损害的风险。检测装置200与电路结构rd的检测距离h1可不受限制。封装电路30的制造方法可获致与上述实施例相似的优良技术效果。

63.图5为本揭露另一实施例的封装电路于检测步骤的剖面示意图。为了附图清楚及方便说明,图5省略示出了若干元件。本实施例所示的封装电路40于检测步骤时的配置大致相似于图1的封装电路10于检测步骤时的配置,因此两实施例中相同与相似的构件于此不再重述。本实施例不同于检测封装电路10的配置之处主要在于:封装电路40的制造方法可包括设置基底150于电路结构rd与液晶层lc之间d。举例来说,于提供电路结构rd的步骤之后,先将液晶层lc和/或透明导电层160形成于基底150上,再将基底150(已形成液晶层lc和/或透明导电层160)设置于电路结构rd上,使基底设置于电路结构rd与液晶层lc和/或透明导电层160之间。在一些实施例中,基底150可包括软板,例如聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、其他合适的材料或前述材料的组合,但不以此为限。在上述的设置下,于完成检测步骤之后,可简单的去除基底150以移除液晶层lc(和/或透明导电层160)。在一些实施例中,去除基底150的方式包括物理撕除的方式,但不以此为限。如此一来,基底150、液晶层lc和/或透明导电层160的叠构可重复使用在其他待检测的封装电路上,藉此节省成本或省略工艺程序。

64.在一些实施例中(未示出),可先选择性地在基底150上形成配向层(图未示)、液晶层lc(和/或透明导电层160),配向层例如可位于液晶层lc与电路结构rd之间,但不限于此。

65.上述的封装电路40的制造方法为非接触式检测的技术,减少导电接垫于检测时受到的损害的风险。检测装置200与电路结构rd的检测距离h1可不受限制。此外,封装电路40的制造方法还可获致与上述实施例相似的优良技术效果。

66.图6为本揭露另一实施例的封装电路于检测步骤的剖面示意图。为了附图清楚及方便说明,图6省略示出了若干元件。本实施例所示的封装电路50的配置大致相似于图5的封装电路40,因此两实施例中相同与相似的构件于此不再重述。本实施例不同于封装电路40的配置之处主要在于:封装电路50的制造方法还包括设置一基底170于透明导电层160(和/或液晶层lc)上。

67.举例来说,于提供电路结构rd的步骤之后,先将液晶层lc(和/或透明导电层160)形成于基底150上,基底150(已形成液晶层lc和/或透明导电层160)设置于电路结构rd上,接着,再将基底170形成于液晶层lc和/或透明导电层160上,但不限于此。

68.在其它实施例,于形成电路结构rd的步骤之后,先将液晶层lc(和/或透明导电层160)形成于基底170上,并将基底170(已形成液晶层lc和/或透明导电层160)翻转以使液晶层lc朝向电路结构rd设置于电路结构rd或基底150(于形成电路结构rd之后可先设置基底150于电路结构rd上)上,使液晶层lc(和/或透明导电层160)设置于基底170及基底150之间,但不限于此。在此实施例中可选择性不设置基底150,即电路结构rd与液晶层lc之间可未设置基底150。

69.在其它实施例中,液晶层lc及透明导电层160亦可先分别形成于不同的基底上,例如液晶层lc形成于基底150上,而透明导电层160形成于基底170上,后续可如图6的层叠顺序设置于电路结构rd上。

70.在一些实施例中,基底150及基底170的材料可以相同或不同。在上述的设置下,于完成检测步骤之后,可以简单的去除基底150和/或基底170,以移除形成于基底150和/或基底170上的液晶层lc和/或透明导电层160。

71.相似的,去除基底150和/或基底170的方式包括物理撕除的方式,但不以此为限。如此一来,基底150、液晶层lc、透明导电层160和/或基底170的叠构可使用在其他待检测的封装电路上。藉此可重复使用简化工艺或节省成本。

72.在上述的设置下,封装电路50的制造方法可以达成非接触式检测的技术,减少导电接垫于检测时受到的损害的风险。检测装置200与电路结构rd的检测距离h1可不受限制。

73.以下将通过图7及图8简单地说明制造的流程以及检测步骤的原理。

74.图7为本揭露另一实施例的封装电路的制造方法的流程图。图8为本揭露另一实施例的电路结构的局部放大立体示意图。为了附图清楚及方便说明,图8省略示出了若干元件。电路结构的制造方法1100包括以下步骤。

75.在步骤1101中,提供基板。

76.在步骤1102中,形成电路结构于基板上,电路结构具有多个导电接垫。

77.在步骤1103中,形成液晶层于电路结构上。

78.在执行步骤1103前,可选择性地先执行步骤1104。在步骤1104中,形成框胶于电路结构上,后续再行步骤1103,形成液晶层于电路结构上,且框胶环绕液晶层。

79.在步骤1105中,形成透明导电层于液晶层上。

80.在步骤1106中,分别施加预设的电压至多个导电接垫中的至少一者及透明导电层以产生电场。在步骤1106中,所产生的电场例如是垂直电场,但不以此为限。

81.在步骤1107中,执行检测步骤,包括根据液晶层受电场所转动的结果来判断多个导电接垫的导通状况。

82.请参考图8,内连线结构120上设置有导电接垫140(可以是图1的导电接垫141或导电接垫142)。液晶层lc的液晶分子lc’形成于内连线结构120和/或导电结构140上。透明导电层160设置于液晶分子lc’上。导电接垫140与透明导电层160可分别耦接至电源装置400,经由电源装置400分别施加预设的电压至多个导电接垫140中的至少一者与透明导电层160上,受到预设的电压的导电接垫140及透明导电层160之间会产生电场,电场会改变位于导电接垫140及透明导电层160之间的液晶分子lc’,导致液晶分子lc’依据电场的方向而转动。后续,可选择性使用指向性的光源300,发射出检测光,检测光的光束l1例如可通过液晶层lc而经由导电接垫140反射。

83.在一些实施中,举例液晶层包括染料液晶分子,而液晶分子lc’的转动方向可朝平行电场的方向举例说明,当导电接垫140导通以可接收到如预设的电压时,导电接垫140及透明导电层160之间可产生预期的电场(垂直电场),故位于导电接垫140及透明导电层160之间的液晶分子lc’可以大致朝平行于电场的方向上转动,而染料分子的转动可顺着液晶分子lc’的方向转动,故检测光的光束l1可穿透被转动的液晶分子lc’和/或染料分子以被导电接垫140所反射,被反射出来的反射光l1’可被检测装置(如图1所示)所检测。此外,未

位于导电接垫140及透明导电层160之间以外的其它液晶分子lc’和/或染料分子,因较远离于电场,故可大致不转动,故通过此些区域的液晶分子lc’和/或染料分子的检测光的光束l2可能至少部份被染料分子所吸收,但不限于此。因此,使用者可通过观察反射光l1’的亮度来判断液晶层lc的转动结果,以液晶层lc的转动结果来判断导电接垫140是否导通以接收到预设的电压。通过上述的检测方法,可减少在不符合规格的封装电路上进行后续工艺的机率。藉此减少成本或提升质量。

84.在步骤1108中,去除液晶层。在一些实施例中,如上所述,去除下来的液晶层和/或透明导电层可以重复使用在其他待检测的封装电路上。

85.图9为本揭露另一实施例的封装电路的制造方法的流程图。电路结构的制造方法1200包括以下步骤。

86.在步骤1201中,提供基板。

87.在步骤1202中,形成电路结构于基板上,电路结构具有多个导电接垫。

88.在步骤1203中,形成液晶层于电路结构上。

89.在执行步骤1203前,可选择性地先执行步骤1204。在步骤1204中,形成框胶于电路结构上,后续再行步骤1203,形成液晶层于电路结构上,且框胶环绕液晶层。

90.在步骤1205中,分别施加预设的电压至多个导电接垫中的至少相邻两者以产生电场。在步骤1205中,所产生的电场例如是水平电场,但不以此为限。

91.在步骤1206中,执行检测步骤,包括根据液晶层受电场所转动的结果来判断多个导电接垫的导通状况。

92.在步骤1207中,去除液晶层。在一些实施例中,去除下来的液晶层与透明导电层可以使用在其他待检测的封装电路上。藉此,可重复使用液晶层和/或透明导电层于检测步骤中,进而可以简化工艺或节省成本。

93.图10为本揭露又一实施例的封装电路的制造方法的流程图。电路结构的制造方法1300包括以下步骤。

94.在步骤1301中,提供基板。

95.在步骤1302中,形成电路结构于基板上,电路结构具有多个导电接垫。

96.在步骤1303中,液晶层(和/或透明导电层)形成于基底上,基底(已形成液晶层和/或透明导电层)再设置于电路结构上,使基底设置于电路结构与液晶层(和/或透明导电层)之间。

97.在步骤1304中,分别施加预设的电压至多个导电接垫中的至少一者及透明导电层以产生电场(例如垂直电场)。在步骤1305中,执行检测步骤,包括根据液晶层受电场所转动的结果来判断多个导电接垫的导通状况。

98.在步骤1306中,去除液晶层(或去除基底及去除形成于基底上的液晶层和/或透明导电层)。在一些实施例中,去除下来的液晶层和/或透明导电层可以重复使用在其他待检测的封装电路上。藉此简化工艺或节省成本。

99.图11为本揭露再一实施例的封装电路的制造方法的流程图。电路结构的制造方法1400包括以下步骤。

100.在步骤1401中,提供基板。

101.在步骤1402中,形成电路结构于基板上,电路结构具有多个导电接垫。

102.在步骤1403中,液晶层先形成于基底上,基底(已形成液晶层)再设置于电路结构上,使基底设置于电路结构与液晶层之间。

103.在步骤1404中,分别施加预设的电压至多个导电接垫中的至少相邻两者以产生电场(例如水平电场)。在步骤1405中,执行检测步骤,包括根据液晶层受电场所转动的结果来判断多个导电接垫的导通状况。

104.在步骤1406中,去除液晶层(或去除基底及去除形成于基底上的液晶层)。在一些实施例中,去除下来的液晶层可以重复使用在其他待检测的封装电路上。藉此简化工艺或节省成本。

105.综上所述,在本揭露一实施例的封装电路的制造方法中,由于可将液晶层形成于待检测的电路结构上,再根据液晶层中液晶分子受到电场转动的结果来判断导电接垫的导通状况,此检测方法为非接触式检测,可减少导电接垫于检测时受到的损害的风险。另外,由于液晶层设置于电路结构上,因此检测装置与电路结构的距离不受限制。此外,可在封装电路的制造过程中进行检测步骤,可减少在不符合规格的封装电路上进行电子元件的耦接工艺的机率,减少成本或提升质量。

106.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。