1.本发明涉及一种光电探测器。

背景技术:

2.近年来,已经提出了可用于成像和传感应用的光电探测器。具体地,已经提出了一种将入射光量检测为电流或电压的动态变化的光电探测器(例如,专利文献1)。这种光电探测器能够用作光子计数传感器、tof(飞行时间)传感器等。

3.引用列表

4.专利文献

5.专利文献1:国际公开wo 2018/167567

6.非专利文献

7.非专利文献1:okhonin et al.,“a dynamic operation of a pin photodiode”applied physics letters,(the united states of america),2015,106,031115

技术实现要素:

8.期望研究应用于图像传感器等的光电探测器的具体结构。例如,期望研究应用于多个像素布置成矩阵状的像素阵列的上述光电探测器的结构。

9.因此,期望提供一种能够提高像素阵列上的入射光的检测特性的光电探测器。

10.根据本发明实施例的光电探测器包括:设置于半导体基板的多个光电转换部。每个光电转换部包括:第一导电类型的第一区域,设置在半导体基板的第一表面所在侧;第二导电类型的第二区域,设置在半导体基板的与第一表面相对的第二表面所在侧;第三导电类型的第三区域,设置在半导体基板的第一区域和第二区域之间的区域中;第一电极,从第二表面沿半导体基板的厚度方向延伸;像素隔离层,具有绝缘性;和第二电极,从第二表面所在侧电连接至第二区域。第三区域吸收入射光。第一电极在底面电连接至第一区域。像素隔离层设置于第一电极的侧面。

11.根据本发明实施例的光电探测器包括:第一导电类型的第一区域,设置在半导体基板的第一表面所在侧;第二导电类型的第二区域,设置在半导体基板的与第一表面相对的第二表面所在侧;和第三导电类型的第三区域,设置在第一区域和第二区域之间的区域中。第三区域吸收入射光。根据本实施例的光电探测器使第一电极从半导体基板的第二表面沿半导体基板的厚度方向延伸且在底面电连接至第一区域,并且使第二电极从半导体基板的第二表面所在侧电连接至第二区域。由此,可以为根据本实施例的光电探测器设置布线层,该布线层可以例如在半导体基板的与光入射面相反的面上电连接至第一电极或第二电极。

附图说明

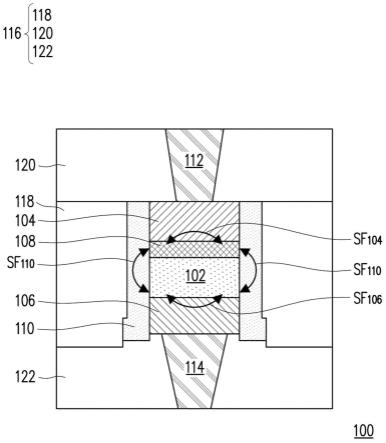

12.图1是示意性地图示根据本发明实施例的光电探测器的基本构造的说明图。

13.图2是图示光电探测器的电流-电压特性的示意曲线图。

14.图3是图示要施加于光电探测器的偏压的极性变化的曲线图。

15.图4是图示根据偏压的极性变化从光电探测器流出的电流的延迟的曲线图。

16.图5a是图示入射到光电探测器的光与电流增大相对于偏压变化的延迟时间之间的关系示例的示意曲线图。

17.图5b是图示入射到光电探测器的光与电流增大相对于偏压变化的延迟时间之间的关系示例的示意曲线图。

18.图5c是图示入射到光电探测器的光与电流增大相对于偏压变化的延迟时间之间的关系示例的示意曲线图。

19.图6是光电探测器的更具体的构造的垂直截面图。

20.图7是图示相对于偏压的变化而导致的电流变化的曲线图。

21.图8a是图示光电探测器在图7的(1)时刻的电子和空穴的移动的垂直截面图。

22.图8b是图示光电探测器在图7的(2)时刻的电子和空穴的移动的垂直截面图。

23.图8c是图示光电探测器在图7的(3)时刻的电子和空穴的移动的垂直截面图。

24.图8d是图示光电探测器在图7的(4)时刻的电子和空穴的移动的垂直截面图。

25.图9a是图示光电探测器在图7的(1)的各时刻在a-aa切割面中的能带结构的曲线图。

26.图9b是图示光电探测器在图7的(2)的各时刻在a-aa切割面中的能带结构的曲线图。

27.图9c是图示光电探测器在图7的(3)的各时刻在a-aa切割面中的能带结构的曲线图。

28.图9d是图示光电探测器在图7的(4)的各时刻在a-aa切割面中的能带结构的曲线图。

29.图10是根据本发明第一实施例的光电探测器的基本结构的垂直截面图。

30.图11是根据本实施例的光电探测器的基本结构的第一表面侧的平面图。

31.图12a是根据第一变形例的光电探测器的结构的垂直截面图。

32.图12b是根据第一变形例的光电探测器的结构的第二表面侧的平面图。

33.图13是根据第二变形例的光电探测器的结构的垂直截面图。

34.图14是根据第三变形例的光电探测器的结构的垂直截面图。

35.图15a是根据第四变形例的光电探测器的结构的垂直截面图。

36.图15b是根据第四变形例的光电探测器的结构的第二表面侧的平面图。

37.图16是根据第五变形例的光电探测器的结构的垂直截面图。

38.图17是根据第六变形例的光电探测器的结构的垂直截面图。

39.图18a是根据第七变形例的光电探测器的结构的垂直截面图。

40.图18b是根据第七变形例的光电探测器的结构的第二表面侧的平面图。

41.图19是根据第八变形例的光电探测器的结构的垂直截面图。

42.图20是根据第九变形例的光电探测器的结构的垂直截面图。

43.图21是根据第十变形例的光电探测器的结构的垂直截面图。

44.图22a是根据第十一变形例的光电探测器的结构的垂直截面图。

45.图22b是沿着图22a的a-aa切割面获取的平面图。

46.图23a是根据第十二变形例的光电探测器的结构的垂直截面图。

47.图23b是沿着图23a的b-bb切割面获取的平面图。

48.图24是根据第十三变形例的光电探测器的结构的垂直截面图。

49.图25a是根据第十四变形例的光电探测器的结构的垂直截面图。

50.图25b是沿着图25a的c-cc切割面获取的平面图。

51.图26是根据第十五变形例的光电探测器的结构的垂直截面图。

52.图27是根据第十五变形例的光电探测器的结构的垂直截面图。

53.图28是根据第十六变形例的光电探测器的结构的垂直截面图。

54.图29是根据第十七变形例的光电探测器的结构的垂直截面图。

55.图30是用于图示图31a至31j的各者中所示的平面图的切割面的垂直截面图。

56.图31a是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

57.图31b是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

58.图31c是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

59.图31d是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

60.图31e是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

61.图31f是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

62.图31g是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

63.图31h是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

64.图31i是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

65.图31j是说明像素隔离层、第一电极和通孔(via)的平面布置的变形例的第一表面侧的平面图。

66.图32是图示了根据实施例的光电探测器的tof传感器操作的示例的时序图。

67.图33是用于tof传感器的光源的说明图。

68.图34a是说明光电探测器在图32的时刻(1)的状态的垂直截面图。

69.图34b是说明光电探测器在图32的时刻(2)的状态的垂直截面图。

70.图34c是说明光电探测器在图32的时刻(3)的状态的垂直截面图。

71.图35a是根据第一变型例的光电探测器的结构的垂直截面图。

72.图35b是根据第一变型例的光电探测器的结构的垂直截面图。

73.图36是图示根据第一变型例的光电探测器的驱动电压的示例的时序图。

74.图37a是根据第二变型例的光电探测器的结构的从第二表面侧观察到的平面图。

75.图37b是光电探测器的结构的在图37a的a-aa切割面中的垂直截面图。

76.图37c是光电探测器的结构的在图37a的b-bb切割面中的垂直截面图。

77.图38是图示起到dpd传感器和pd的作用的光电探测器所包括的像素电路的等效电路的示例的电路图。

78.图39a是根据第三变型例的光电探测器的结构的从第二表面侧观察到的平面图。

79.图39b是根据第三变型例的光电探测器的结构的沿着图39a的a-aa切割面获得的垂直截面图。

80.图39c是根据第三变型例的光电探测器的结构的沿着图39a的b-bb切割面获得的垂直截面图。

81.图40是根据本发明的第二实施例的光电探测器的基本结构的垂直截面图。

82.图41是根据本实施例的光电探测器的基本结构的从第一表面侧观察到的平面图。

83.图42是根据第一变形例的光电探测器的构造的垂直截面图。

84.图43是根据第二变形例的光电探测器的构造的垂直截面图。

85.图44是根据第三变形例的光电探测器的构造的垂直截面图。

86.图45是根据第四变形例的光电探测器的构造的垂直截面图。

87.图46是根据第五变形例的光电探测器的构造的垂直截面图。

88.图47是根据第六变形例的光电探测器的构造的垂直截面图。

89.图48a是根据第七变形例的光电探测器的构造的第一表面侧的平面图。

90.图48b是光电探测器的构造的在图48a的a-aa切割面中的垂直截面图。

91.图48c是光电探测器的构造的在图48a的b-bb切割面中的垂直截面图。

92.图49是根据第八变形例的光电探测器的构造的垂直截面图。

93.图50是根据第九变形例的光电探测器的构造的垂直截面图。

94.图51是根据第十变形例的光电探测器的构造的垂直截面图。

95.图52是根据第十一变形例的光电探测器的构造的垂直截面图。

96.图53是根据第十二变形例的光电探测器的构造的垂直截面图。

97.图54是根据第十三变形例的光电探测器的构造的垂直截面图。

98.图55是根据第十四变形例的光电探测器的构造的垂直截面图。

99.图56是根据第十五变形例的光电探测器的构造的垂直截面图。

100.图57是根据第十六变形例的光电探测器的构造的垂直截面图。

101.图58是根据第十七变形例的光电探测器的构造的垂直截面图。

102.图59是根据第十八变形例的光电探测器的构造的垂直截面图。

103.图60是用于说明参照图40说明的光电探测器的基本结构中的第一区域、第二区域和控制栅极的平面布置的第一表面侧的平面图。

104.图61a是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

105.图61b是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

106.图61c是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表

面侧的平面图。

107.图61d是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

108.图61e是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

109.图61f是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

110.图61g是用于说明第一区域、第二区域和控制栅极的平面布置的变形例的第一表面侧的平面图。

111.图62是将光电探测器应用于3行

×

3列的像素阵列的平面构造的顶视图。

112.图63是图示了在将光电探测器应用于3行

×

3列的像素阵列的情况下的等效电路的电路图。

113.图64是按时间顺序图示了在将施加至光电探测器的偏压从反向偏压反转为正向偏压之后的电荷的移动的示意图。

114.图65是按时间顺序图示了在将施加至光电探测器的偏压从反向偏压反转为正向偏压之后能带结构的变化的图表。

115.图66是根据本发明的第三实施例的光电探测器的基本结构的垂直截面图。

116.图67是根据第一变形例的光电探测器的结构的垂直截面图。

117.图68是根据第二变形例的光电探测器的结构的垂直截面图。

118.图69是根据第三变形例的光电探测器的结构的垂直截面图。

119.图70是根据第四变形例的光电探测器的结构的垂直截面图。

120.图71是根据第五变形例的光电探测器的结构的垂直截面图。

121.图72是根据第六变形例的光电探测器的结构的垂直截面图。

122.图73a是说明像素隔离层、绝缘层、第二区域和第二电极的布置和形状的变形例的第二表面侧到的平面图。

123.图73b是说明像素隔离层、绝缘层、第二区域和第二电极的布置和形状的变形例的第二表面侧的平面图。

124.图74是根据本发明的第四实施例的光电探测器的基本结构的垂直截面图。

125.图75a是图示根据本实施例的光电探测器的能带结构的曲线图。

126.图75b是图示根据本实施例的光电探测器的能带结构的曲线图。

127.图76a是根据第一变形例的光电探测器的结构的垂直截面图。

128.图76b是根据第一变形例的光电探测器的结构的第二表面侧的平面图。

129.图77a是根据第二变形例的光电探测器的结构的垂直截面图。

130.图77b是根据第二变形例的光电探测器的结构的第二表面侧的平面图。

131.图78a是根据第三变形例的光电探测器的结构的垂直截面图。

132.图78b是根据第三变形例的光电探测器的结构的第二表面侧的平面图。

133.图79a是根据第四变形例的光电探测器的结构的垂直截面图。

134.图79b是根据第四变形例的光电探测器的结构的第二表面侧的平面图。

135.图80是根据第五变形例的光电探测器的结构的垂直截面图。

136.图81a是根据第六变形例的光电探测器的结构的垂直截面图。

137.图81b是根据第六变形例的光电探测器的结构的第二表面侧的平面图。

138.图82a是根据第七变形例的光电探测器的结构的垂直截面图。

139.图82b是根据第七变形例的光电探测器的结构的第二表面侧的平面图。

140.图83a是根据第八变形例的光电探测器的结构的垂直截面图。

141.图83b是根据第八变形例的光电探测器的结构的第一表面侧的平面图。

142.图84a是根据第九变形例的光电探测器的结构的垂直截面图。

143.图84b是根据第九变形例的光电探测器的结构的第一表面侧的平面图。

144.图85是根据第十变形例的光电探测器的结构的垂直截面图。

145.图86a是根据第十一变形例的光电探测器的结构的垂直截面图。

146.图86b是根据第十一变形例的光电探测器的结构的第一表面侧的平面图。

147.图87是根据第十二变形例的光电探测器的结构的垂直截面图。

148.图88是根据第十三变形例的光电探测器的结构的垂直截面图。

149.图89是根据第十四变形例的光电探测器的结构的垂直截面图。

150.图90是根据第五实施例的第一结构例的光电探测器的结构的垂直截面图。

151.图91a是根据第一结构例的光电探测器的平面结构的示例的顶视图。

152.图91b是根据第一结构例的光电探测器的平面结构的示例的顶视图。

153.图92是根据第二结构例的光电探测器的结构的垂直截面图。

154.图93a是根据第二结构例的光电探测器的平面结构的示例的顶视图。

155.图93b是根据第二结构例的光电探测器的平面结构的示例的顶视图。

156.图94是根据第三结构例的光电探测器的结构的垂直截面图。

157.图95a是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

158.图95b是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

159.图96a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

160.图96b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

161.图97a是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

162.图97b是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

163.图98a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

164.图98b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

165.图99是根据第四结构例的光电探测器的结构的垂直截面图。

166.图100a是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

167.图100b是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

168.图101a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层741的这一区域的示例的平面图。

169.图101b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层741的这一区域的示例的平面图。

170.图102a是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

171.图102b是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

172.图103a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

173.图103b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

174.图104是根据第五结构例的光电探测器的结构的垂直截面图。

175.图105是根据第六结构例的光电探测器的结构的垂直截面图。

176.图106是根据第七结构例的光电探测器的结构的垂直截面图。

177.图107是根据第八结构例的光电探测器的结构的垂直截面图。

178.图108是根据第九结构例的光电探测器的结构的垂直截面图。

179.图109是根据第十结构例的光电探测器的结构的垂直截面图。

180.图110是根据第十一结构例的光电探测器的结构的垂直截面图。

181.图111是根据第十二结构例的光电探测器的结构的垂直截面图。

182.图112是根据第十三结构例的光电探测器的结构的垂直截面图。

183.图113a是根据第十三结构例的光电探测器的平面结构的示例的顶视图。

184.图113b是根据第十三结构例的光电探测器的平面结构的示例的顶视图。

185.图114是根据第十四结构例的光电探测器的结构的垂直截面图。

186.图115a是根据第十四结构例的光电探测器的平面结构的示例的顶视图。

187.图115b是根据第十四结构例的光电探测器的平面结构的示例的顶视图。

188.图116是根据第十五结构例的光电探测器的结构的垂直截面图。

189.图117a是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

190.图117b是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

191.图118a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

192.图118b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

193.图119a是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

194.图119b是在包含第三区域的半导体层的正面侧形成有钉扎层的这一区域的示例的平面图。

195.图120a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层

的这一区域的示例的平面图。

196.图120b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

197.图121是根据第十六结构例的光电探测器的结构的垂直截面图。

198.图122a是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

199.图122b是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

200.图123a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

201.图123b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

202.图124a是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

203.图124b是在电荷产生层的正面侧形成有钉扎层的这一区域的示例的平面图。

204.图125a是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

205.图125b是在包含第三区域的半导体层与埋设绝缘膜之间的界面处形成有钉扎层的这一区域的示例的平面图。

206.图126是根据第十七结构例的光电探测器的结构的垂直截面图。

207.图127是根据第十八结构例的光电探测器的结构的垂直截面图。

208.图128a是根据本发明的第六实施例的光电探测器的结构的第二表面侧的平面图。

209.图128b是光电探测器的结构的在图128a的a-aa切割面中的垂直截面图。

210.图128c是光电探测器的结构的在图128a的b-bb切割面中的垂直截面图。

211.图129是光电探测器包含的像素电路中所包括的像素晶体管的布置的示例的平面图。

212.图130是图示起到dpd传感器和pd的作用的光电探测器所包括的像素电路的等效电路的示例的电路图。

213.图131是图示根据本实施例的光电探测器的tof传感器操作的示例的时序图。

214.图132是说明tof传感器所使用的光源的说明图。

215.图133a是说明光电探测器在图131的时刻(1)的状态的垂直截面图。

216.图133b是说明光电探测器在图131的时刻(2)的状态的垂直截面图。

217.图133c是说明光电探测器在图131的时刻(3)的状态的垂直截面图。

218.图134是图示根据本实施例的光电探测器的pd操作的示例的时序图。

219.图135a是说明光电探测器在图134的时刻(1)的状态的垂直截面图。

220.图135b是说明光电探测器在图134的时刻(2)的状态的垂直截面图。

221.图135c是说明光电探测器在图134的时刻(3)的状态的垂直截面图。

222.图135d是说明光电探测器在图134的时刻(4)的状态的垂直截面图。

223.图135e是说明光电探测器在图134的时刻(5)的状态的垂直截面图。

224.图136是图示根据本实施例的光电探测器为像素阵列时的功能构造的框图。

225.图137a是根据第一变形例的光电探测器的结构的第二表面侧的平面图。

226.图137b是光电探测器的结构的在图137a的a-aa切割面中的垂直截面图。

227.图137c是光电探测器的结构的在图137a的b-bb切割面中的垂直截面图。

228.图138a是根据第二变形例的光电探测器的结构的第二表面侧的平面图。

229.图138b是光电探测器的结构的在图138a的a-aa切割面中的垂直截面图。

230.图138c是光电探测器的结构的在图138a的b-bb切割面中的垂直截面图。

231.图139a是根据第三变形例的光电探测器的结构的第二表面侧的平面图。

232.图139b是光电探测器的结构的在图139a的a-aa切割面中的垂直截面图。

233.图139c是光电探测器的结构的在图139a的b-bb切割面中的垂直截面图。

234.图140a是根据第四变形例的光电探测器的结构的第二表面侧的平面图。

235.图140b是光电探测器的结构的在图140a的a-aa切割面中的垂直截面图。

236.图140c是光电探测器的结构的在图140a的b-bb切割面中的垂直截面图。

237.图141a是根据第五变形例的光电探测器的结构的第二表面侧的平面图。

238.图141b是光电探测器的结构的在图141a的a-aa切割面中的垂直截面图。

239.图141c是光电探测器的结构的在图141a的b-bb切割面中的垂直截面图。

240.图142a是根据第六变形例的光电探测器的结构的第二表面侧的平面图。

241.图142b是光电探测器的结构的在图142a的a-aa切割面中的垂直截面图。

242.图142c是光电探测器的结构的在图142a的b-bb切割面中的垂直截面图。

243.图143a是根据第七变形例的光电探测器的结构的第二表面侧的平面图。

244.图143b是光电探测器的结构的在图143a的a-aa切割面中的垂直截面图。

245.图143c是光电探测器的结构的在图143a的b-bb切割面中的垂直截面图。

246.图144a是根据第八变形例的光电探测器的结构的第二表面侧的平面图。

247.图144b是光电探测器的结构的在图144a的a-aa切割面中的垂直截面图。

248.图144c是光电探测器的结构的在图144a的b-bb切割面中的垂直截面图。

249.图145a是根据第九变形例的光电探测器的结构的第二表面侧的平面图。

250.图145b是光电探测器的结构的在图145a的a-aa切割面中的垂直截面图。

251.图145c是光电探测器的结构的在图145a的b-bb切割面中的垂直截面图。

252.图146a是根据第十变形例的光电探测器的结构的第二表面侧的平面图。

253.图146b是光电探测器的结构的在图146a的a-aa切割面中的垂直截面图。

254.图146c是光电探测器的结构的在图146a的b-bb切割面中的垂直截面图。

255.图147a是根据第十一变形例的光电探测器的结构的第二表面侧的平面图。

256.图147b是光电探测器的结构的在图147a的a-aa切割面中的垂直截面图。

257.图147c是光电探测器的结构的在图147a的b-bb切割面中的垂直截面图。

258.图148是图示了其中多个像素布置成矩阵状的像素阵列的平面构造的示例的示意图。

259.图149是说明根据本实施例的光电探测器的dpd操作和pd操作之间的切换的概念图。

260.图150是图示根据本实施例的光电探测器的dpd操作和pd操作之间的切换的流程的示例的流程图。

261.图151是图示通过dpd进行光子计数操作的概要的框图。

262.图152是图示入射到dpd上的光子与检测信号之间关系的曲线图。

263.图153是图示根据本实施例的光电探测器的光子计数操作的示例的时序图。

264.图154a是光电探测器在图153的时刻(1)的状态的垂直截面图。

265.图154b是光电探测器在图153的时刻(2)的状态的垂直截面图。

266.图154c是光电探测器在图153的时刻(3)的状态的垂直截面图。

267.图155是图示根据本实施例的光电探测器应用于进行光子计数操作的像素阵列的功能构造的框图。

268.图156是根据本发明第七实施例的光电探测器的结构的垂直截面图。

269.图157是说明从光电探测器输出的电流的各种时间响应的曲线图。

270.图158是图示相对于图157所示的各种时间响应的线性偏差的曲线图。

271.图159是根据本实施例的光电探测器的像素阵列构造的平面图。

272.图160是图示图159所示的像素阵列中的普通像素的输出与参考像素的输出之间关系的曲线图。

273.图161是说明普通像素和参考像素的平面布置的第一变形例的示意平面图。

274.图162是沿着图161的a-aa切割面获取的横截面构造的垂直截面图。

275.图163是说明普通像素和参考像素的平面布置的第二变形例的示意平面图。

276.图164是沿着图163的b-bb切割面获取的横截面构造的垂直截面图。

277.图165是说明普通像素和参考像素的平面布置的第三变形例的示意平面图。

278.图166是沿着图165的c-cc切割面获取的横截面构造的垂直截面图。

279.图167是说明普通像素和参考像素的平面布置的第四变形例的示意平面图。

280.图168是普通像素和参考像素的横截面构造的第五变形例的垂直截面图。

281.图169是图示参考像素的开口面积与上升正向电流的延迟时间之间关系的曲线图。

282.图170是图示根据本实施例的光电探测器为像素阵列时的第一电路构造的框图。

283.图171是图示根据本实施例的光电探测器为像素阵列时的第二电路构造的框图。

284.图172是图示根据本实施例的光电探测器为像素阵列时的第三电路构造的框图。

285.图173是图示根据本实施例的光电探测器为像素阵列时的第四电路构造的框图。

286.图174是光电探测器的堆叠结构的示例的示意性立体图。

287.图175是应用光电探测器的固态成像元件的基板构造的立体图。

288.图176是光电探测器的受光芯片的平面构造的平面图。

289.图177是光电探测器的逻辑芯片的平面构造的平面图。

290.图178是图示光电探测器的电路构造的框图。

291.图179是图示应用光电探测器的固态成像器件的构造的框图。

292.图180a是应用光电探测器的固态成像器件的有效像素的横截面构造示例的垂直截面图。

293.图180b是应用光电探测器的固态成像器件的遮光像素(shielding pixel)的横截面构造示例的垂直截面图。

294.图181是图示了作为使用了传感器芯片的电子装置的距离图像传感器的构造例的框图,在该传感器芯片中使用了光电探测器。

295.图182是图示了测距模块的构造例的框图,该测距模块通过使用光电探测器输出

测距信息。

296.图183a是在电子用作信号载体的情况下的光电探测器的构造的垂直截面图。

297.图183b是在空穴用作信号载体的情况下的光电探测器的构造的垂直截面图。

具体实施方式

298.下文将参照附图详细说明本发明的实施例。下面说明的实施例是本发明的具体示例。根据本发明的技术不应限于以下实施方式。此外,根据本发明的每个部件的布置、尺寸、尺寸比例等不限于附图中所示的方式。

299.应注意,将按以下顺序进行说明。

300.0.光电探测器的原理

301.1.第一实施例

302.2.第二实施例

303.3.第三实施例

304.4.第四实施例

305.5.第五实施例

306.6.第六实施例

307.7.第七实施例

308.8.应用例

309.9.附录

310.《0.光电探测器的原理》

311.首先,参照图1至图4对根据本发明实施例的光电探测器的光检测原理进行说明。图1是示意性地图示根据本实施例的光电探测器10的基本构造的说明图。图2是图示光电探测器10的电流-电压特性的示意曲线图。图3是图示要施加于光电探测器10的偏压的极性变化的曲线图。图4是图示根据偏压的极性变化从光电探测器10流出的电流的延迟的曲线图。

312.应注意,在本说明书中,纵向或上/下方向是指基板或层的厚度方向。此外,横向或左/右方向是指基板或层的面内的一个方向(例如,横截面图中基板或层的切割方向)。

313.如图1所示,根据本实施例的光电探测器10包括第一区域11、第二区域12和设置在第一区域11和第二区域12之间的第三区域13。

314.第一区域11例如是电连接至地等的第一导电类型(例如,n型)的半导体区域。第二区域12是与能够控制施加电压的电极电连接的第二导电类型(例如,p型)的半导体区域。第三区域13是设置在第一区域11和第二区域12之间的第三导电类型(例如,i型)的半导体区域。第三区域13吸收入射光。

315.即,光电探测器10是所谓的pin二极管。如图2所示,要施加的偏压的极性极大地改变电压-电流特性。具体而言,因为向第二区域12施加的偏压是具有负电压的反向偏压,所以无论施加的偏压如何,在第一区域11和第二区域12之间几乎没有电流流动。与此相反,因为在向第二区域12施加正电压的正向偏压状态下,偏压是正向偏压,所以随着所施加的偏压增大,在第一区域11和第二区域12之间突然电流流动。

316.这里,如图3和图4所示,在施加到光电探测器10的偏压的极性从反向偏压变为正向偏压的情况下,光电探测器10流出的电流从电流ir(对应于偏压vr)增大到电流if(对应于

偏压vf)之前有一个时间t的延迟。在这种情况下,从电流ir变化到电流if的延迟时间t根据光电探测器10的第三区域13中吸收的光的强度而变化。这使得光电探测器10能够通过在施加的偏压的极性改变的情况下测量电流增大的延迟时间来估计入射光的强度。这种光电探测器10也被称为例如dpd(动态光电二极管)传感器。

317.随后,参照图5a至5c,更具体地说明入射到光电探测器10上的光的强度与电流增大相对于偏压变化的延迟时间之间的关系。图5a至5c均是图示了入射到光电探测器10上的光与电流增大相对于偏压变化的延迟时间之间的关系的示例的示意曲线图。

318.如图5a所示,在没有光入射的情况下,假设光电探测器10中电流增大相对于偏压的极性变化的延迟时间为t1。在这样的光电探测器10中,如图5b所示,入射光使电流增大相对于偏压的极性变化的延迟时间为t2,短于t1。此外,在光电探测器10中,如图5c所示,比图5b的入射光更强的入射光致使电流增大相对于偏压的极性变化的延迟时间为t3,仍短于t1。这使得这种光电探测器10能够通过测量从偏压的极性变化到电流增大所经过的时间来计算入射光的量。

319.此外,参照图6至图9d,更详细地说明电流增大之前经过的延迟时间根据光电探测器10中的入射光量而改变的原理。图6是图示光电探测器10的更具体构造的垂直截面图。图7是图示相对于偏压的变化,电流变化的曲线图。图8a至8d是图示光电探测器10在图7的(1)至(4)各时刻的电子和空穴的移动的垂直截面图。图9a至9d是图示光电探测器10在图7的(1)至(4)各时刻的在a-aa切割面中的能带结构的曲线图。

320.如图6所示,光电探测器10包括例如第一区域11、第二区域12、第三区域13、第一电极21、第一表面绝缘层16、像素隔离层15、第二电极22、控制栅极25和栅极绝缘膜26。

321.第一区域11是设置在诸如硅(si)的半导体基板的第一表面所在侧的第一导电类型区域(例如,n 层)。第二区域12是设置在与诸如硅(si)的半导体基板的第一表面相反的第二表面所在侧的第二导电类型区域(例如,p 层)。第三区域13是设置在诸如硅(si)的半导体基板的第一区域11和第二区域12之间的第三导电类型区域(例如,i层)。

322.第一电极21设置在半导体基板的第一表面上,第一电极与半导体基板的第一表面之间插入有第一表面绝缘层16。第一电极21通过贯穿第一表面绝缘层16的通孔等电连接至第一区域11。第一电极21用作例如阴极电极。

323.像素隔离层15是由在厚度方向上贯穿半导体基板的绝缘体设置的。例如,像素隔离层15设置为将设置在半导体基板的面内方向上的多个像素中的每一个像素都彼此电隔离。

324.第二电极22设置在半导体基板的第二表面上。第二电极22电连接至第二区域12。第二电极22用作例如阳极电极。

325.控制栅极25是设置在半导体基板的第二表面上的栅极电极,并且在控制栅极25与半导体基板的第二表面之间插入有栅极绝缘膜26。控制栅极25设置为通过施加电压来控制第三区域13中势垒(potential barrier)pb的高度。稍后说明势垒pb。

326.第一电极21、第二电极22和控制栅极25可以均通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料制成。第一表面绝缘层16、像素隔离层15和栅极绝缘膜26可以均通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体制成。

327.这里,如图7所示,施加到第一电极21的电压表示为vc,施加到第二电极22的电压表示为va,且施加到控制栅极25的电压表示为vg。在这种情况下,可以以反向偏压模式控制光电探测器10,例如,通过将第一电极21的电压vc控制为0v,且将第二电极22的电压va和控制栅极25的电压vg控制为-1v。此外,可以以正向偏压模式控制光电探测器10,例如,通过将第一电极21的电压vc控制为0v,且将第二电极22的电压va和控制栅极25的电压vg控制为 1v。

328.这里,在反向偏压模式的状态(1)下,如图8a所示,第三区域13中的电子e被排出至第一区域11,而第三区域13中的空穴h被排出至第二区域12。因此,如图9a所示,这种情况下的光电探测器10的能带结构具有第二区域12侧高且第一区域11侧低的结构。这使得第三区域13处于耗尽状态。

329.接着,在电压的极性从反向偏压模式转变为正向偏压模式的状态(2)下,如图8b所示,在与第一区域11和第二区域12相邻的区域中产生势垒pb。即,这种情况下的光电探测器10的能带结构具有下述结构:其中,如图9b所示,光电探测器10包括在第一区域11和第二区域12之间凹入或凸出的势垒pb。这阻止了电子e和空穴h在第三区域13中的流动,因此几乎没有电流流过光电探测器10。

330.随后,在正向偏压模式的光电探测器10被光照射的状态(3)下,如图8c所示,在耗尽状态的第三区域13中产生了由入射光的光电转换而获得的电子e和空穴h。在这种情况下,在光电探测器10的能带结构中,如图9c所示,通过对入射光进行光电转换而获得的电子e和空穴h降低势垒pb的高度。这使电子e逐渐从第一区域11流出或使空穴h逐渐从第二区域12流出。因此,流动的电子e和空穴h进一步降低势垒pb的高度。

331.因此,在正向偏压模式的状态(4)下,如图8d所示,在与第一区域11和第二区域12相邻的区域中产生的势垒pb消失。这使具有正向方向的电流在光电探测器10中流动。即,这种情况下的光电探测器10的能带结构是大致平坦的结构,其中,如图9d所示,曾存在于第一区域11和第二区域12之间的凹入或凸出的势垒pb消失。

332.因此,在光电探测器10中,在施加的偏压的极性从反向偏压变为正向偏压的情况下,势垒pb消失的速度根据入射光的量而不同。所以,光电探测器10能够通过利用具有正向方向的电流开始流动之前经过的时间测量势垒pb消失之前经过的时间来测量光的入射量。

333.下文将在第一至第七实施例中分别说明其原理已在上文中说明的光电探测器10的更具体结构。应注意,下文中说明的像素对应于根据本发明的“光电转换部”的具体示例。

334.《1.第一实施例》

335.(基本结构)

336.首先,参照图10和11说明根据本发明第一实施例的光电探测器的基本结构。图10是根据本实施例的光电探测器100的基本结构的垂直截面图,图11是根据本实施例的光电探测器100的基本结构的第一表面侧的平面图。

337.如图10所示,光电探测器300包括例如第一区域110、第二区域120、第三区域130、第一电极111、通孔112、第一表面绝缘层151、像素隔离层150、第二电极121、控制栅极161和栅极绝缘膜162。

338.第一区域110是设置在诸如硅(si)的半导体基板的第一表面侧的第一导电类型区域(例如,n 层)。第二区域120是设置在诸如硅(si)的半导体基板的与第一表面相反的第二

表面侧的第二导电类型区域(例如,p 层)。第三区域130是设置在诸如硅(si)的半导体基板的第一区域110和第二区域120之间的第三导电类型区域(例如,i层)。

339.第一电极111设置在半导体基板的第一表面上方,并且第一表面绝缘层151设置于第一电极与第一表面之间。第一电极111通过延伸穿过第一表面绝缘层151的通孔112等电连接到第一区域110。第一电极111例如起到阴极电极的作用。如图11所示,第一电极111例如沿像素之间的边界设置为跨越像素隔离层150。第一电极111通过为每个像素设置的通孔112电连接至各像素的第一区域110。这使得第一电极111能够向被像素隔离层150电隔离的各像素的第一区域110提供共用电势。

340.像素隔离层150被设置为在厚度方向上穿透半导体基板并且将在半导体基板的面内方向上设置的多个像素彼此电隔离。如图11所示,像素隔离层150可以沿着例如在半导体基板的面内方向上以矩阵布置的各个像素之间的边界以晶格形式设置。

341.第二电极121设置在半导体基板的与第一表面相反的第二表面上。第二电极121电连接至第二区域120。第二电极121例如用作阳极电极。

342.控制栅极161是设置在半导体基板的第二表面上方的栅极电极,并且在控制栅极与第二表面之间设置有栅极绝缘膜162。电压施加使得控制栅极161能够控制第三区域130中的势垒。

343.第一电极111、通孔112、第二电极121及控制栅极161可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属、多晶硅(poly-si)或其他导电材料来设置。第一表面绝缘层151、像素隔离层150以及栅极绝缘膜162可通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体来设置。

344.根据本实施例的光电探测器100被设置为背面(即,第一表面)发光cmos(互补型mos)图像传感器。这使得能够减少作为光入射表面的后表面侧上的布线,并增大后表面侧的开口率。此外,根据本实施例的光电探测器100具有在半导体基板的厚度方向上布置的第一区域110和第二区域120。因此,能够进一步减少占用面积。这允许光电探测器100能够更有效地使像素小型化。此外,像素隔离层150在半导体基板的厚度方向上延伸,这使得根据本实施例的光电探测器100能够抑制像素之间的串扰。因此,能够进一步降低噪声。

345.(变形例)

346.随后,参考图12a至31j描述根据本实施例的光电探测器100的结构的变形例。

347.(第一变形例)

348.图12a是根据第一变形例的光电探测器100a的结构的垂直截面图。图12b是根据第一变形例的光电探测器100a的结构的从第二表面侧的平面图。

349.如图12a和12b所示,第一区域110可以设置在例如被像素隔离层150所限定的区域的大致整个上方。第二区域120可以以岛状的形式设置在例如被像素隔离层150限定的区域的大致中间。此外,控制栅极161可以设置为例如在半导体基板的面内方向上围绕第二区域120和第二电极121的外围。

350.根据第一变形例,光电探测器100a具有布置在半导体基板的厚度方向上的第一区域110和第二区域120,从而使得能够进一步减小占用面积。此外,将像素隔离层150设置于像素的整个外围,使得光电探测器100a能够抑制像素之间的串扰。

351.(第二变形例)

352.图13是根据第二变形例的光电探测器100b的结构的垂直截面图。

353.如图13所示,还可以在像素隔离层150内设置第三电极150b。施加电压vpin使得第三电极150b能够隔着像素隔离层150控制第三区域130的电势。第三电极150b可通过使用例如铝、铜、钨、钛或钽等金属、多晶硅或其他导电材料来设置。需要注意的是,像素隔离层150插入在第三电极150b与第三区域130之间并且因此确保了像素之间的电绝缘。

354.根据第二变形例,对第三区域130的电势的控制光使得电探测器100b能够加强像素隔离层150相对于第三区域130的钉扎。因此,光电探测器100b能够进一步降低噪声。这使得能够进一步提高入射光的检测特性.

355.(第三变形例)

356.图14是根据第三变形例的光电探测器100c的结构的垂直截面图。

357.如图14所示,可在像素隔离层150内进一步设置金属层150c。需要注意的是,像素隔离层150插入在金属层150c与第三区域130之间,并且因此确保了像素之间的电绝缘。金属层150c具有遮光性能。这使得能够防止从倾斜方向入射到第一表面上的光进入相邻像素。金属层150c可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)或它们的合金等金属来设置。

358.根据第三变形例,金属层150c使得光电探测器100c能够防止像素之间的光入射。因此,能够进一步抑制像素之间的串扰。

359.(第四变形例)

360.图15a是根据第四变形例的光电探测器100d的结构的垂直截面图。图15b是根据第四变形例的光电探测器100d的结构从第二表面侧的平面图。

361.如图15a所示,控制栅极161d可以设置为具有垂直栅极结构。具体来说,控制栅极161d可以设置为在半导体基板的厚度方向上从半导体基板的第二表面侧延伸。此外,埋入半导体基板中的控制栅极161d的侧表面和底面可以设置有栅极绝缘膜162d。在控制栅极161d的周围可以设置有第二导电类型(例如,p型)的杂质区域163。在这种情况下,如图15b所示,控制栅极161d被设置为在半导体基板的面内方向上包围第二区域120的外周。第二导电类型(例如,p型)的杂质区域163被进一步设置为围绕控制栅极161d。

362.根据第四变形例,光电探测器100d使得能够进一步提高在邻近第二区域120的区域中生成的势垒的可控性。因此,能够进一步提高入射光.的检测特性。

363.(第五变形例)

364.图16是根据第五变形例的光电探测器100e的结构的垂直截面图。

365.如图16所示,控制栅极161e可设置为具有垂直栅极结构。此外,电极164可电连接至杂质区域163。施加电压vpin使得电极164能够控制杂质区域163的电势。

366.根据第五变形例,光电探测器100e能够通过控制将电压vpin施加至杂质区域163作为负电压而进一步加强第二区域120的钉扎效应。因此,光电检测器100e使得能够进一步提高入射光的检测特性。

367.(第六变形例)

368.图17是根据第六变形例的光电探测器100f的结构的垂直截面图。

369.如图17所示,各像素的第二区域120、控制栅极161f、栅极绝缘膜162f和杂质区域163的在半导体基板的厚度方向上的形成深度可以是不同的。这使得光电探测器100f能够

包括厚度在像素间是不同的第三区域130。每个第三区域130吸收入射光。这使得不同像素的第三区域130能够吸收相应的不同的波长带的光。

370.根据第六变形例,光电探测器100f能够使得不同像素检测不同的波长带的光。因此,能够执行更复杂的感测。

371.(第七变形例)

372.图18a是根据第七变形例的光电探测器100g的结构的垂直截面图。图18b是根据第七变形例的光电探测器100g的结构的从第二表面侧的平面图。

373.如图18a所示,控制栅极161g可设置为具有垂直栅极结构。控制栅极161g可以被设置为穿透第二区域120并且隔着栅极绝缘膜162g埋在半导体基板中。具体地,如图18b所示,第二区域120可以在被像素隔离层150限定的区域的在半导体基板的面内方向上的大致中心处以圆形设置。控制栅极161g可以设置为在中间穿透第二区域120。

374.根据第七种变型,光电探测器100g能够进一步提高在靠近第二区域120的区域中产生的势垒的可控性。因此,能够进一步提高入射光的检测特性.

375.(第八变形例)

376.图19是根据第八变形例的光电探测器100h的结构的垂直截面图。

377.如图19所示,控制栅极161h可以设置为具有垂直栅极结构。控制栅极161h可以设置为穿透第二区域120并且隔着栅极绝缘膜162h埋在半导体基板中。此外,各像素的第二区域120、控制栅极161h以及栅极绝缘膜162h的在半导体基板的厚度方向上的形成深度可以是不同的。这使得光电探测器100h能够包括不同像素的厚度不同的第三区域130。每个第三区域130吸收入射光。这使得不同像素的第三区域130能够吸收相应的不同波长带的光。

378.根据第八变形例,光电探测器100h能够检测像素之间不同波长带的各个光。因此,能够执行更复杂的感测。

379.(第九变形例)

380.图20是根据第九变形例的光电探测器100i的结构的垂直截面图。

381.如图20所示,各个像素的第一区域110的在半导体基板的厚度方向上的形成深度可以是不同的。这使得光电探测器100i能够包括在像素间的厚度不同的第三区域130。每个第三区域130吸收入射光.这使得不同像素的第三区域130能够吸收相应的不同波长带的光。

382.根据第九变形例,光电探测器100i能够检测像素之间不同波长带的各个光。因此,能够执行更复杂的感测。

383.(第十变形例)

384.图21是根据第十变形例的光电探测器100j的结构的垂直截面图。

385.如图21所示,光电探测器100j的第二表面(即,与后表面相对的前表面)可以进一步设置有多层布线层170,该多层布线层170连接至包括电路部181的电路板180。多层布线层170包括布线和通孔。多层布线层170通过使用电极接合结构183(也被称为cucu接合结构)将布线和通孔与从电路板180的绝缘层182露出的电极电连接。

386.根据第十变形例,光电探测器100j使得能够在半导体基板的厚度方向上堆叠电路板180。这使得能够进一步减小芯片面积。电路板180包括电路部181。

387.(第十一变形例)

388.图22a是根据第十一变形例的光电探测器100k的结构的垂直截面图。图22b是沿图22a的a-aa切割平面截取的平面图。

389.如图22a所示,光电探测器100k的第二表面(即,与后表面相对的前表面)可进一步设置有多层布线层170,该多层布线层170接合至包括电路部181的电路板180。

390.在这里,可以在由像素隔离层150所限定的整个像素区域上设置电极接合结构183k(也被称为cucu接合结构)。电极接合结构183k将多层布线层170的布线和通孔与从电路板180的绝缘层182露出的电极电连接。这使得电极接合结构183k能够通过反射穿过第三区域130并且进入多层布线层170侧的光来提高传感器的光电转换效率。具体地,如图22b所示,当电极或布线被分割以保持通孔171和172彼此电隔离时,电极接合结构183k可以被设置在整个像素上。通孔171和172连接至不同的电极。

391.根据第十一变形例,光电探测器100k使得第三区域130能够具有更高的光电转换效率。因此,能够提高入射光的检测灵敏度。

392.(第十二变形例)

393.图23a是根据第十二变形例的光电探测器100l的结构的垂直截面图。图23b是沿图23a的b-bb切割平面截取的平面图。

394.如图23a所示,光电探测器100l的第二表面(即,与后表面相对的前表面)可进一步设置有多层布线层170,该多层布线层170连接至包括电路部181的电路板180。

395.在这里,可以在由像素隔离层150限定的整个像素区域上设置有布线173。布线173被包括在多层布线层170中。这使得配线173能够通过反射穿过第三区域130并进入多层布线层170侧的光来提高第三区域130的光电转换效率。具体地说,如图23b所示,电连接至控制栅极161的布线173可以设置在整个像素上以包围第二电极121的外围。

396.根据第十二变形例,光电探测器100l使得第三区域130能够具有更高的光电转换效率。因此,能够提高入射光的检测灵敏度。

397.(第十三变形例)

398.图24是根据第十三变形例的光电探测器100m的结构的垂直截面图。

399.如图24所示,光电探测器100m的第一表面(即,作为光入射面的背表面)可进一步设置有散射结构155m。散射结构155m是以小于或等于入射光的波长的重复周期设置的凹凸结构。散射结构155m的示例包括蛾眼结构等。对进入光电探测器100m的光进行散射使得散射结构155m能够降低入射光穿过第三区域130的可能性。应注意,散射结构155m可以通过处理半导体基板的第一表面来形成,或者通过在半导体基板的第一表面上堆叠不均匀结构体来形成。

400.根据第十三变形例,光电探测器100m能够通过散射入射光提高第三区域的光电转换效率。因此,光电探测器100m能够提高入射光的检测灵敏度。

401.(第十四变形例)

402.图25a是根据第十四变形例的光电探测器100n的结构的垂直截面图。图25b是沿图25a的c-cc切割平面获取的平面图。

403.如图25a所示,光电探测器100n的第一表面(即,作为光入射面的背表面)可进一步设置有衍射栅格结构155n。例如,如图25b所示,衍射栅格结构155n可以具有如下结构:其中,多个凹部和多个突起以同心圆的形状以与入射光的波长对应的间隔形成有。衍射栅格

结构155n使得进入光电探测器100n的光分支到多个路径中,从而使得能够将入射光会聚在像素中的预定位置。

404.根据第十四变形例,光电探测器100n能够通过将入射光会聚在像素中的预定位置提高第三区域130的光电转换效率。因此,光电检测器100n使得能够提高入射光的检测灵敏度。

405.(第十五变形例)

406.图26是根据第十五变形例的光电探测器100o的结构的垂直截面图,图27是根据第十五变形例的光电探测器100p的结构的垂直截面图。

407.如图26和27所示,像素隔离层150o和150p可设置为在半导体基板的厚度方向上延伸到半导体基板的厚度的中间点处,而不是从第一表面到第二表面穿透半导体基板。即使这样的构造也使得像素隔离层150o和150p能够抑制相邻像素之间的串扰。

408.具体而言,如图26所示,在光电探测器100o中,像素隔离层150o可以设置为从半导体基板的第一表面侧沿半导体基板的厚度方向延伸至半导体基板未被穿透的程度。此外,如图27所示,在光电检测器100p中,像素隔离层150p可以被设置为在半导体基板的厚度方向上从半导体基板的第二表面侧延伸到半导体基板未被穿透的程度。

409.根据第十五变形例,光电探测器100o和100p能够降低制造步骤中的加工难度。因此,能够提高制造效率。应注意,可以将第十五变形中描述的组件与第一到第十四变形例中描述的各个组件组合。

410.(第十六变形例)

411.图28是根据第十六变形例的光电探测器100q的结构的垂直截面图。

412.如图28所示,光电探测器100q不包括像素隔离层150,但可能包括第一区域110和第三区域130作为在多个像素上连续延伸的区域。即使这样的构造也使得光电检测器100q能够针对每个像素检测入射光。

413.根据第十六变形例,光电探测器100q能够降低制造步骤中的加工难度。因此,能够提高制造效率。

414.(第十七变形例)

415.图29是根据第十七变形例的光电探测器100r的结构的垂直截面图。

416.如图29所示,光电探测器100r在半导体基板的第一表面侧上设置有第二导电类型(例如,p型)的第一区域110r,并且在与第一表面相对的第二表面侧上设置有第一导电类型(例如,n型)的第二区域120r。在这种情况下,第一电极111电连接至第一区域110r且用作阳极电极,第二电极121电连接至第二区域120r且用作阴极电极。即使这样的构造也使得光电探测器100r能够针对每个像素检测入射光。

417.根据第十七变形例,光电探测器100r能够交换导电区域的极性。这使得能够增加结构设计的自由度。

418.(第十八变形例)

419.在第十八变形例中,说明在半导体基板的第一表面上的像素隔离层150、第一电极111和通孔112。图30是用于图示针对图31a至31j中的各者所示的平面图的切割平面的垂直横截面图。图31a至31j的各者是从第一表面侧的平面图,描述了像素隔离层150、第一电极111和通孔112的平面布置的变化。

420.图31a到31j的各者示出了沿图30的b-bb切割平面截取的横截面结构。换句话说,图31a至31j的各者示出了在半导体基板的第一表面上的像素隔离层150、第一电极111和通孔112的平面布置。需要注意的是,即使在不设置像素隔离层150的情况下,第一电极111和通孔112也能够具有与下文中类似的平面布置。

421.如图31a所示,例如,每个第一电极111可设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧边。通孔112可以与像素隔离层150隔离,并且沿第一电极111的边缘设置在像素中。

422.如图31b所示,例如,每个第一电极111可设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧边。通孔112可以与像素隔离层150相邻并且可以沿着像素的内边缘设置。

423.如图31c所示,例如,每个第一电极111可设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧边。通孔112可以与像素隔离层150分隔并且在矩形像素的四个角的每一个角处以岛的形状设置。

424.如图31d所示,例如,每个第一电极111可设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧边。通孔112可以与像素隔离层150相邻并且在矩形像素的四个角的每一个角处以岛的形状设置。

425.如图31e所示,例如第一电极111可设置在像素隔离层150的两个平行侧边。像素隔离层150设置在矩形像素的每一侧。通孔112可以与像素隔离层150分隔并且在矩形像素的四个角的每一个角处以岛的形状设置。在这种情况下,在相互平行的方向上延伸的第一电极111在没有设置光接收单元的区域(也称为光学黑部)中彼此电连接。

426.如图31f所示,例如第一电极111可设置在像素隔离层150的两个平行侧边。像素隔离层150设置在矩形像素的每一侧。通孔112可以与像素隔离层150相邻并且在矩形像素的四个角的每一个角处以岛的形状设置。在这种情况下,在相互平行的方向上延伸的第一电极111在没有设置光接收单元的区域(也称为光学黑部)中彼此电连接。

427.如图31g所示,例如各第一电极111可设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧边。通孔112可以与像素隔离层150分隔并且唯一一个通孔112可以在矩形像素的左上角以岛的形状设置。

428.如图31h所示,例如,每个第一电极111可以设置在像素隔离层150上。像素隔离层150设置在矩形像素的每一侧。通孔112可以与像素隔离层150相邻并且唯一一个通孔112可以在矩形像素的左上角以岛的形状设置。

429.如图31i所示,例如,第一电极111可设置在像素隔离层150的两个平行侧边。像素隔离层150设置在矩形像素的每一侧。通孔112可以与像素隔离层150分隔并且唯一一个通孔112可以在矩形像素的左上角以岛的形状设置。在这种情况下,在相互平行的方向上延伸的第一电极111在没有设置光接收区域的区域(也称为光学黑部)中彼此电连接。

430.如图31j所示,例如,第一电极111可设置在像素隔离层150的两个平行侧边。像素隔离层150设置在矩形像素的每一侧。通孔112可以与像素隔离层150相邻并且唯一一个通孔112可以在矩形像素的左上角以岛的形状设置。在这种情况下,在相互平行的方向上延伸的第一电极111在没有设置光接收区域的区域(也称为光学黑部)中彼此电连接。

431.在第一电极111和通孔112的平面布置中,第一电极111具有较小的面积使得像素

能够具有较高的开口率。这使得能够提高光电检测器100的检测灵敏度。此外,通孔112设置为多个点而不是一个点。此外,通孔112被设置为线而不是多个点。这使得能够吸收在半导体基板的面内方向上的第一区域110的电位波动。这使得光电探测器100具有更高的入射光检测稳定性。换言之,可以通过将这些方面因素考虑进去来恰当地设计光电探测器100的半导体基板的第一表面上的像素隔离层150、第一电极111和通孔112的平面布置,以使光电探测器100的检测特性成为期望的特性。

432.(操作示例)

433.接下来,参考图32至34c说明根据本实施例的用作tof(飞行时间)传感器的光电探测器100的操作示例。图32是示出根据本实施例的光电探测器100的tof传感器操作的示例的时序图。图33是描述用于tof传感器的光源的说明图。图34a是说明在图32中的时刻(1)处的光电探测器100的状态的垂直截面图。图34b是说明在图32中的时刻(2)处的光电探测器100的状态的垂直截面图。图34c是说明在图32中的时刻(3)处的光电探测器100的状态的垂直截面图。

434.如图32和34a所示,首先,在图32中的(1)时刻将正电压施加到要施加至开关晶体管的栅极的电压v

sw

以导通开关晶体管。随后,假设被施加至第二电极121的电压va为负电压(例如,-1v)。在这种情况下,要施加到第一电极111的电压vc为0v。因此,在光电探测器100的第一区域110和第二区域120之间施加了反向偏压。需要注意的是,要施加到控制栅极161的电压vg被设定为负电压(例如,-1v)。

435.如图32、33和34b所示,在图32中的时刻(2)处将脉冲负电压v

light

施加到诸如激光二极管或led(发光二极管)等光源ld,以用脉冲光照射目标。同时,施加正电压(例如, 1v)作为要施加至第二电极121的电压va,以在光电探测器100的第一区域110和第二区域120之间施加正向偏置。此外,要施加到控制栅极161的电压vg被设定为正电压(例如, 1v)。

436.此后,在目标上被反射的脉冲光进入光电探测器100,并且从第二电极121输出的电流值随着从时刻(2)起的延迟而增大。这使得光电探测器100能够通过计算光源ld的发光时刻t2与光检测的延迟时间t1之间的差来计算到目标的距离。

437.此外,如图32和34c所示,作为在图32中的时刻(3)处被施加至第二电极121的电压va,负电压(例如,-1v)被施加。这将在光电检测器100的第一区域110与第二区域120之间施加反向偏压。因此,光电检测器100的状态被复位。需要注意的是,要施加到控制栅极161的电压vg可类似地设定为负电压(例如,-1v)。

438.将上述操作作为一帧重复,这使得光电探测器100能够针对每一帧检测到目标的距离。

439.(变型例)

440.接着,参考图35a至39c说明根据本实施例的光电探测器100的结构的第一到第三变型例。

441.(第一变型例)

442.图35a是根据第一变型例的光电探测器100s的结构的垂直截面图。图35b是根据第一变型例的光电探测器100s的结构的垂直截面图。图36是示出根据第一变型例的光电探测器100s中的驱动电压的示例的时序图。

443.如图35a所示,光电探测器100s在半导体基板的第二表面侧设置有电势控制区域

165,以代替控制栅极161和栅极绝缘膜162。光电探测器100s使得能够通过向电势控制区域165施加电压来控制在邻近第二区域120的区域中产生的势垒。

444.电势控制区域165是第一导电类型的区域(例如,n 层)。电势控制区域165被设置为围绕第二区域120的外围并且绝缘层166介于电势控制区域165与第二区域120之间。换句话说,如图35b所示,半导体基板的第二表面侧在由像素隔离层150限定的区域的大致中间处设置有岛状的第二区域120。此外,绝缘层166被设置为围绕第二区域120的外围并且电势控制区域165被设置为围绕绝缘层166的外围。

445.即使在这样的构造中,如图36所示,对施加到电势控制区域165的电压vg的与控制栅极161同样的控制使得光电检测器100s能够检测入射光。

446.(第二变型例)

447.图37a是根据第二变型例的光电探测器100t的从第二表面侧的结构平面图。图37b是图37a的a-aa剖切面中的光电探测器100t的结构的垂直截面图。图37c是图37a的b-bb剖切面中的光电探测器100t的结构的垂直截面图。

448.如图37a至37c所示,根据第二变型例的光电探测器100t与根据第一变型例的光电探测器100s的不同之处在于,根据第二变型例的光电探测器100t还包括传输栅极和浮动扩散部,并且也能够用作一般的光电二极管(pd)。此外,根据第二变型例的光电探测器100t设置有在像素隔离层150内的金属层150t,金属层150t具有遮光特性。

449.具体而言,如图37a和37b中所示,与根据第一变型例的光电探测器100t相同地,光电探测器100t包括第一区域110、第三区域130、第二区域120、绝缘层166、电势控制区域165和向电势控制区域165施加电压的电极167。这使得光电探测器100t能够在半导体基板的平面的第一方向(图37a中的纵向)上用作dpd传感器。

450.此外,如图37a和37c所示,光电探测器100t包括第一区域110、第三区域130、第二区域120、第一导电类型区域191、传输栅极trg、第二导电类型的浮动扩散部fd和提取电极193。这使得光电探测器100t在半导体基板的平面的与第一方向正交的第二方向(图37a中的横向)上作为普通的pd工作。

451.具体地说,将电压施加到设置于半导体基板的第二表面上方的传输栅极trg上,传输栅极trg与第二表面之间设置有栅极绝缘膜192,从而使得能够将电荷从第二区域120通过第一导电类型区域191传输至浮动扩散部fd。例如从提取电极193将传输至浮动扩散部fd的电荷提取到像素电路等。

452.需要注意的是,包括在像素电路中的像素晶体管例如可以被设置在与像素隔离层150相邻地设置的像素晶体管区域tr中。例如,像素晶体管区域tr可以设置有包括在像素电路中的复位晶体管、放大晶体管、选择晶体管和开关晶体管中的至少一个或多个。像素晶体管区域tr中设置的各个晶体管可以例如通过挖掘半导体基板而设置的绝缘层而被彼此电绝缘。

453.根据第二变型例的光电探测器100t可以包括例如其等效电路如图38所示的像素电路。图38是示出用作dpd传感器和pd的光电探测器100t中包含的像素电路的等效电路的示例的电路图。应注意,dpd/pd表示具有pin二极管结构的光电转换部,在pin二极管结构中层叠有上述的第一区域110、第三区域130以及第二区域120。

454.如图38所示,作为dpd传感器侧的像素电路,光电转换部dpd通过开关晶体管sw电

连接至电源va。此外,作为pd侧的像素电路,光电转换部pd通过传输晶体管trg电连接至浮动扩散部fd。

455.此外,电源vd通过复位晶体管rst进一步连接到浮动扩散部fd。此外,放大晶体管amp的栅极连接至浮动扩散部fd。放大晶体管amp的漏极连接至电源vd,放大晶体管amp的源极通过选择晶体管sel连接至外部输出output。应注意,dpd传感器侧的电源va和pd侧的电源vd可以是彼此不同的电源,也可以是相同的电源。根据第二变型例的光电探测器100t包括这样的像素电路。这使得根据第二变型例的光电探测器100t能够同时用作dpd传感器和pd。

456.(第三变型例)

457.图39a是根据第三变型例的光电探测器100u的结构的从第二表面侧的平面图。图39b是根据第三变型例的光电探测器100u的结构在图39a的a-aa切割面中的垂直截面图。图39c是根据第三变型例的光电探测器100u的结构在图39a的b-bb切割面中的垂直截面图。

458.如图39a至39c所示,根据第三变型例的光电探测器100u与根据第二变型例的光电探测器100t的不同之处在于,根据第三变型例的光电探测器100u未设置有像素隔离层150和设置在像素隔离层150中的金属层150t。已经针对根据第二变型例的光电探测器100t说明了根据第三变型例的光电探测器100u的其他组件,因此这里不再赘述。

459.即使这样的构造也使得根据第三变型例的光电探测器100u能够与根据第二变型例的光电探测器100t一样既用作dpd传感器又用作pd。

460.《2.第二实施例》

461.(基本结构)

462.接下来,参考图40和41说明根据本发明第二实施例的光电探测器的基本结构。图40是根据本实施例的光电探测器200的基本结构的垂直截面图,图41是根据本实施例的光电探测器200的基本结构的从第一表面侧的平面图。

463.如图40所示,光电探测器200包括例如第一区域210、第二区域220、第三区域230、第一电极211、第二电极221,第二表面绝缘层251、像素隔离层250、控制栅极261和栅极绝缘膜262。

464.像素隔离层250被设置为在厚度方向上穿透半导体基板,并且将在半导体基板的面内方向上设置的多个像素彼此电隔离。如图41所示,像素隔离层250例如可以设置为包围矩形形状的像素的外围。

465.第一区域210是第一导电类型的区域(例如,n 层),其被设置于诸如硅(si)等的半导体基板且与像素隔离层250接触。如图41所示,第一区域210可设置为与围绕矩形形状的像素的外围的像素隔离层250的一侧接触。钉扎效应使得第一区域210能够抑制在与像素隔离层250的界面231处的电荷(例如,空穴)感应。

466.第二区域220是第二导电类型的区域(例如,p 层),其被设置于诸如硅(si)等的半导体基板且与像素隔离层250接触。如图41所示,第二区域220可设置为与围绕矩形形状的像素的外围的像素隔离层250的相对的另一侧接触。钉扎效应使得第二区域220能够抑制在与像素隔离层250的界面231处的电荷(例如,空穴)感应。

467.第三区域230是设置于第一区域210与第二区域220之间的第三导电类型的区域(例如,i层)。如图41所示,第三区域230可以是在被像素隔离层250限定的像素区域中的被

夹在第一区域210与第二区域220之间的区域。

468.第一电极211设置在半导体基板的第一表面上。第一电极211电连接至第一区域210。第一区域210例如用作阴极电极。与第一电极211一样地,第二电极221设置在半导体基板的第一表面上并电连接至第二区域220。第二电极221例如用作阳极电极。

469.控制栅极261是设置在半导体基板的第一表面上方的栅极电极,在第一表面与控制栅极261之间设置有栅极绝缘膜262。控制栅极261被设置为通过电压施加来控制在第三区域230中生成的势垒。

470.第二表面绝缘层251设置在与半导体基板的第一表面相反的第二表面上。第二表面绝缘层251与像素隔离层250的底面接触。这使得第一区域210、第二区域220以及第三区域230能够与相邻像素电隔离。这使得光电探测器200能够进一步抑制相邻像素之间的串扰。第二表面绝缘层251例如可以是soi(绝缘体上硅)基板的埋置氧化膜(box层:埋置氧化层)。

471.第一电极211、第二电极221以及控制栅极261可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属、多晶硅(poly-si)或其他导电材料来设置。第二表面绝缘层251、像素隔离层250以及栅极绝缘膜262可通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体来设置。

472.根据本实施例的光电探测器200具有将相邻像素彼此隔离的像素隔离层250。此外,均具有高浓度的导电杂质的第一区域210和第二区域220被设置为与像素隔离层250接触。这使得光电探测器200能够借助钉扎效应通过增大第一区域210与像素隔离层250之间的界面231处的电子浓度而更少可能地诱导空穴。此外,能够借助钉扎效应通过增大第二区域220与像素隔离层250之间的界面231处的空穴浓度而更少可能地诱导电子。这使得光电探测器200能够抑制由半导体基板与像素隔离层250之间的界面231处感应的电荷导致的暗电流的产生。因此,能够减少暗时噪声。

473.(变形例)

474.下面,将参考图42至61g说明根据本实施例的光电探测器200的结构的变形例。

475.(第一变形例)

476.图42是根据第一变形例的光电探测器200a的结构的垂直截面图。

477.如图42所示,控制栅极261可以设置为与第二区域220相邻。光电探测器200a使用通过光电转换入射光生成的电荷来降低在与第二区域220相邻的区域中产生的势垒。这使得光电探测器200a能够促进电荷在第一区域210与第二区域220之间移动。控制栅极261设置为与第二区域220相邻,因此这使得能够以更高的精度控制在与所述电极相邻的区域中产生的势垒。

478.根据第一变形例,光电探测器200a使得能够进一步提高在与第二区域220相邻的区域中生成的势垒的可控性。因此,能够进一步提高入射光的检测特性。

479.(第二变形例)

480.图43是根据第二变形例的光电探测器200b的结构的垂直截面图。

481.如图43所示,光电探测器200b可包括多个控制栅极。具体地,光电探测器200b可以包括第一控制栅极261-1和第二控制栅极261-2。第一控制栅极261-1是设置在半导体基板的第一表面上方的栅极电极并且与第一区域210相邻,在第一控制栅极261-1与第一表面之

间设置有栅极绝缘膜262-1。第一控制栅极261-1被设置用于通过施加电压来控制在与第一区域210相邻的区域中生成的势垒。另外,第二控制栅极261-2是设置在半导体基板的第一表面上方的栅极电极并且与第二区域220相邻,在第二控制栅极261-2与第一表面之间设置有栅极绝缘膜262-2。第二控制栅极261-2被设置用于通过施加电压来控制在与第二区域220相邻的区域中生成的势垒。

482.根据第二变形例,多个控制栅极261-1和261-2使得光电探测器200b能够以更高的精度控制在第三区域230中产生的势垒。这使得能够进一步提高入射光的检测特性。

483.(第三变形例)

484.图44是根据第三变形例的光电探测器200c的结构的垂直截面图。

485.如图44所示,光电探测器200c还可包括复位电极263。具体地,复位电极263设置在形成在半导体基板的第一表面侧上的第二导电类型区域264上。复位电极263被设置用于例如在在光电检测器200c完成检测入射光的情况下从第三区域230排出第三区域230内剩余的电荷。复位电极263可通过使用例如铝、铜、钨、钛或钽等金属、多晶硅或其他导电材料来设置。

486.根据第三变形例,光电探测器200c能够更可靠地从第三区域230排出电荷。因此,能够进一步降低在检测入射光的情况下产生的噪声。

487.(第四变形例)

488.图45是根据第四变形例的光电探测器200d的结构的垂直截面图。

489.如图45所示,光电探测器200d还可包括设置在第三区域230上的电荷产生层232。电荷产生层232通过使用与设置有第三区域230的半导体基板的半导体材料不同的半导体材料而形成。电荷产生层232设置在半导体基板的与光的入射面相对应的第一表面上。电荷产生层232通过对在第三区域230中不会被光电转换的光进行光电转换,由此生成由入射光产生的电荷。例如,在具有第三区域230的半导体基板是硅基板的情况下,电荷产生层232可以是通过使用锗(ge)、硅锗(sige)或化合物半导体等形成的层。

490.根据第四变形例,光电探测器200d使得电荷产生层232能够对未被设置有第三区域230的半导体基板光电转换的波长的光进行光电转换。这使得能够进一步拓宽可检测光的波长范围。

491.(第五变形例)

492.图46是根据第五变形例的光电探测器200e的结构的垂直截面图。

493.如图46所示,光电探测器200e的第一表面(即,光的入射面)可进一步设置有散射结构255e。散射结构255e是以低于或等于入射光的波长的重复周期而设置的凹凸结构。散射结构255e的示例包括蛾眼结构等。使进入光电探测器200e的光散射,这使得散射结构255e能够降低入射光穿透第三区域230的可能性。应注意,散射结构255e可以通过处理半导体基板的第一表面来形成,或者通过在半导体基板的第一表面上堆叠凹凸结构体来形成。

494.根据第五变形例,光电探测器200e能够通过散射入射光来提高第三区域230的光电转换效率。因此,光电检测器200e使得能够提高入射光的检测灵敏度。

495.(第六变形例)

496.图47是根据第六变形例的光电探测器200f的结构的垂直截面图。

497.如图47所示,光电探测器200f的第一表面(即,光的入射面)可进一步设置有衍射

栅格结构255f。衍射栅格结构255f例如可以是其中彼此平行的直线状凹陷和凸起以与入射光的波长相对应的间隔布置的结构,或者是其中多个凹陷和多个凸起以与入射光的波长相对应的间隔形成为同心圆的形状。衍射栅格结构255f使得进入光电探测器200f的光分支到多个路径中,从而使得能够将入射光会聚在像素中的预定位置处。

498.根据第六变形例,光电探测器200f能够通过将入射光会聚在预定位置处来提高第三区域230的光电转换效率。因此,光电检测器200f使得能够提高入射光的检测灵敏度。

499.(第七变形例)

500.图48a是根据第七变形例的光电探测器200g的结构的第一表面侧的平面图。图48b是图48a的a-aa切割面中的光电探测器200g的结构的垂直截面图。图48c是图48a的b-bb切割面中的光电探测器200g的结构的垂直截面图。

501.如图48a至48c中所示,可在像素隔离层250内进一步设置第三电极252。具体来说,像素隔离层250包围像素的四个侧面,并且第三电极252可以在像素的与和第一区域210以及第二区域220接触的两侧相正交的两侧设置在像素隔离层250内。控制施加电压vpin为负电压,这使得第三电极252能够经由像素隔离层250控制第三区域230的电势。第三电极252可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属、多晶硅(poly-si)或其他导电材料来设置。需要注意的是,像素隔离层250插入在第三电极252与第三区域230之间,并且因此确保了像素之间的电绝缘。

502.根据第七变形例,光电探测器200g能够通过控制第三区域230的电势来加强不与第一区域210和第二区域220接触的像素隔离层250的钉扎。这使得光电探测器200g能够控制在不与第一区域210和第二区域220接触的像素隔离层250与第三区域230之间的界面处生成的电荷。因此,能够进一步降低噪声。

503.(第八变形例)

504.图49是根据第八变形例的光电探测器200h的结构的垂直截面图。

505.如图49所示,在第二表面绝缘层251内可进一步设置背栅极电极252h。具体地,背栅极电极252h可在第三区域230下方设置在第二表面绝缘层251内并且在半导体基板的面内方向上延伸。控制施加电压vpin位于负电压,使得背栅极电极252h能够经由第二表面绝缘层251控制第三区域230的电势。背栅极电极252h可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属、多晶硅(poly-si)或其他导电材料来设置。

506.根据第八变形例,背栅电极252h使得光电探测器200h能够控制第三区域230的电势。因此,能够在第三区域230和第二表面绝缘层251之间的界面处进行钉扎。这使得光电探测器200h能够控制在第三区域230和第二表面绝缘层251之间的界面处生成的电荷。因此,能够进一步降低噪声。

507.(第九变形例)

508.图50是根据第九变形例的光电探测器200i的结构的垂直截面图。

509.如图50所示,光电探测器200i可以在像素隔离层250内设置有第一电极212和第二电极222。在这种情况下,第一电极212被设置为在半导体基板的厚度方向上呈台阶状。这使得第一电极212能够在台阶的底面上电连接至第一区域210。此外,第二电极222类似地设置为在半导体基板的厚度方向上呈台阶状。这使得第二电极222能够在台阶的底面上电连接至第二区域220。

510.能够通过用导电材料填充第一开口和第二开口形成均具有这样的结构的第一电极212和第二电极222。第一开口沿厚度方向从第一表面延伸穿过半导体基板到达第二表面。第二开口的开口宽度大于第一开口的开口宽度。第二开口是通过在厚度方向上挖掘半导体基板的一半而形成的。这使得光电探测器200i能够通过两阶段的挖掘在像素隔离层250内形成第一电极212和第二电极222,从而具有图50中所示的结构。像素隔离层250类似地通过两阶段挖掘而形成。

511.在光电探测器200i中,第一区域210在设置于第一电极212的台阶底面上电连接至第一电极212。另外,第二区域220类似地在设置于第二电极222的台阶底面上电连接至第二电极222。第一区域210和第二区域因此以远离第一表面的方式设置在半导体基板内部。这使得很难从半导体基板的第一表面进入第一区域210和第二区域220附近的区域。在这种情况下,光电探测器200i不必设置控制栅极261。

512.同时,光电探测器200i还可包括设置在半导体基板的第一表面侧的第四电极265。第四电极265设置在形成于半导体基板的第一表面侧的第二导电类型区域266上。第四电极265能够经由第二导电类型区域266控制第三区域230的电势。这使得第四电极265能够通过将负电压施加至第三区域230来抑制在第三区域230与像素隔离层250之间的界面处生成的电荷。这使得光电探测器200i能够进一步降低噪声。第四电极265可通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属、多晶硅(poly-si)或其他导电材料来设置。

513.根据第九变形例,光电探测器200i能够调制第一区域210和第二区域220的形成深度。这使得光电探测器200i能够控制在与第一区域210和第二区域220相邻的区域中生成的势垒的电容。

514.(第十变形例)

515.图51是根据第十变形例的光电探测器200j的结构的垂直截面图。

516.如图51所示,光电探测器200j与根据第九变形例的光电探测器200i的不同之处在于第一区域210和第二区域220在形成深度上被设置为是彼此不同的。第一区域210和第一电极212的接触位置的深度不同于第二区域220和第二电极222的接触位置的深度。

517.根据第十变形例,光电探测器200j能够独立地控制在与第一区域210相邻的区域中产生的势垒的电容。此外,这还使得光电探测器200j能够调制在施加正向偏压之后流动的正向电流量。

518.(第十一变形例)

519.图52是根据第十一变形例的光电探测器200k的结构的垂直截面图。

520.如图52所示,光电探测器200k与根据第九变形例的光电探测器200i的不同之处在于,设置在半导体基板的第一表面侧的第四电极265k设置在第一导电类型区域267上。具体地,第四电极265k设置在形成在半导体基板的第一表面侧上的第一导电类型区域267上。能够通过第一导电类型区域267排出第三区域230内的电荷。例如,第四电极265k可以通过将正电压施加至第一导电类型区域267以将第三区域230内的电子排出至第三区域230的外部。

521.根据第十一变形例,光电探测器200k能够更可靠地从第三区域230放电。因此,能够进一步减少在检测入射光的情况下产生的噪声。

522.(第十二变形例)

523.图53是根据第十二变形例的光电探测器200l的结构的垂直截面图。

524.如图53所示,光电探测器200l与根据第十一变形例的光电探测器200k的不同之处在于,不同像素的第一导电类型区域267的在半导体基板的厚度方向上的形成深度被形成为是不同的。这使得在光电探测器200l中的不同像素的用于吸收入射光的第三区域230的厚度是不同的。因此,能够针对每个像素改变具有灵敏度的波长带。

525.根据第十二变形例,光电探测器200l能够针对各个像素检测不同波段的各种光。因此,能够执行更复杂的感测。

526.(第十三变形例)

527.图54是根据第十三变形例的光电探测器200m的结构的垂直截面图。

528.如图54所示,光电探测器200m与根据第九变形例的光电探测器200i的不同之处在于,第二区域220和第二电极222分别以类似于根据第一变形例的光电探测器200a的第二区域和第二电极的构造而形成。

529.根据第十三变形例,光电探测器200m能够独立地控制在与第一区域210相邻的区域中产生的势垒的电容。此外,这还使得光电探测器200m能够调制在施加正向偏压之后流动的正向电流的量。

530.(第十四变形例)

531.图55是根据第十四变形例的光电探测器200n的结构的垂直截面图。

532.如图55所示,像素隔离层250n可以被设置为沿半导体基板的厚度方向延伸到半导体基板的厚度的中点,而不是从第一表面到第二表面穿透半导体基板。即使这样的构造也使得像素隔离层250n能够抑制相邻像素之间的串扰。例如,像素隔离层250n可以设置为从半导体基板的第一表面侧沿着半导体基板的厚度方向延伸至半导体基板未被穿透的程度。

533.根据第十四变形例,光电探测器200n使得能够降低在制造步骤中的处理难度。因此,能够提高制造效率。

534.(第十五变形例)

535.图56是根据第十五变形例的光电探测器200o的结构的垂直截面图。

536.如图56所示,光电探测器200o的第一表面可以进一步设置有多层布线层270,多层布线层270连接至包括电路部281的电路板280。多层布线层270包括布线和通孔。多层布线层270通过使用电极接合结构283(也被称为cucu接合结构)将布线和通孔与从电路板280的绝缘层282露出的电极电连接。应注意,光电探测器200o的与第一表面相反的第二表面(即,光的入射面)可设置有第二表面绝缘层251,以保护其中形成有第三区域230的半导体基板。

537.根据第十五变形例,光电探测器200o使得电路板280能够在半导体基板的厚度方向上堆叠。这使得能够进一步减小芯片面积。电路板280包括电路部281。

538.(第十六变形例)

539.图57是根据第十六变形例的光电探测器200p的结构的垂直截面图。

540.如图57所示,光电探测器200p的第二表面(即,与后表面相对的前表面)可以进一步设置有多层布线层270,该多层布线层270接合至包括电路部281的电路板280。

541.在这里,可以在由像素隔离层250限定的整个像素区域上设置布线273。布线273被包括在多层布线层270中。这使得布线273能够通过对穿过第三区域230并进入多层布线层270侧的光进行反射以提高第三区域230的光电转换效率。具体地说,电连接至控制栅极261

的布线273可以设置在第一电极211与第二电极221之间的区域上。

542.根据第十六变形例,光电探测器200p使得第三区域230能够具有更高的光电转换效率。因此,能够提高入射光的检测灵敏度。

543.(第十七变形例)

544.图58是根据第十七变形例的光电探测器200q的结构的垂直截面图。

545.如图58所示,光电探测器200q的第二表面(即,与后表面相对的前表面)可进一步设置有多层布线层270,多层布线层270接合至包括电路部281的电路板280。

546.在这里,可以在由像素隔离层250限定的整个像素区域上设置电极接合结构283q(也称为cucu接合结构)。电极接合结构283q电连接多层布线层270的布线和通孔与从电路板280绝缘层282露出的电极。这使得电极接合结构283q能够通过对穿过第三区域230并进入多层布线层270侧的光进行反射以提高第三区域230的光电转换效率。具体地,电极接合结构283q可以设置在电连接至第一电极211的电极接合结构与电连接至第二电极221的电极接合结构之间的区域中。

547.根据第十七变形例,光电探测器200q使得第三区域230能够具有更高的光电转换效率。因此,能够提高入射光的检测灵敏度。

548.(第十八变形例)

549.图59是根据第十八变形例的光电探测器200r的结构的垂直截面图。

550.如图59所示,光电探测器200r的第二表面(即,与后表面相对的前表面)可进一步设置有多层布线层270,多层布线层270接合至包括电路部281的电路板280。这里,像素隔离层250r可以设置为沿半导体基板的厚度方向延伸至半导体基板的厚度的中间点,而不是从第二表面到第一表面穿透半导体基板。即使这样的构造也使得像素隔离层250r能够以抑制相邻像素之间的串扰。例如,像素隔离层250r可以设置为在半导体基板的厚度方向上从半导体基板的第二表面侧延伸至半导体基板未被穿透的程度。

551.根据第十八变形例,光电探测器200r能够降低制造步骤中的加工难度。因此,能够提高制造效率。

552.(第十九变形例)

553.在第十九变形例中,说明了第一电极210、第二区域220以及控制栅极261在半导体基板的第一表面上的平面布置的变化。图60是第一表面侧的平面图,其图示了在参照图40说明的光电探测器200的基本结构中的第一区域210、第二区域220以及控制栅极261的平面布置。图61a至61g中的各者均是第一表面侧的平面图,分别图示了第一区域210、第二区域220以及控制栅极261的平面布置的变形。

554.如图60所示,在具有基本结构的光电探测器200中,像素隔离层250被设置为例如以矩形形状围绕像素的外围。在这种情况下,第一区域210可设置为与以矩形形状围绕像素的外围的像素隔离层250的四侧中的一侧相接触。第二区域220可设置为与像素隔离层250的与上述一侧相反的另一侧相接触。像素隔离层250以矩形的形状包围像素的外围。控制栅极261可以沿着第二区域220的与像素隔离层250相反的一侧设置。

555.这里,如图61a所示,例如,第一区域210可以设置在由矩形的像素隔离层250所包围的像素的四个角之中的一个角处。第二区域220可设置在由矩形的像素隔离层250所包围的像素的四个角之中的与第一区域210对角线相对的角处。控制栅极261可沿着第二区域

220的与像素隔离层250相反的两侧设置。

556.如图61b所示,例如,第一区域210可以设置在由矩形的像素隔离层250所包围的像素的四个角之中的一个角处。第二区域220可设置为与第一区域210分隔并且与包围矩形的像素的外周的像素隔离层250的一侧接触。控制栅极261可沿第二区域220的与像素隔离层250相反的一侧设置。

557.如图61c所示,例如,第一区域210可以设置为与具有矩形形状的包围像素的外周的像素隔离层250的一侧接触。第二区域220可设置为与第一区域210分隔,并且设置在被矩形的像素隔离层250包围的像素的四个角之中的一个角处。控制栅极261可以沿第二区域220的与像素隔离层250相反的两侧设置。

558.如图61d所示,例如,第一区域210可以设置在与被矩形的像素隔离层250包围的像素的四个角之中的一个角处。第二区域220可设置为与第一区域210分隔,并且与具有矩形形状的包围像素的外周的像素隔离层250的两侧接触。控制栅极261可以沿第二区域220的与像素隔离层250相反的两侧设置。

559.如图61e所示,例如,第一区域210可以设置为与具有矩形形状的包围像素的外周的像素隔离层250的两侧接触。第二区域220可设置为与第一区域210分隔,并且设置在被矩形的像素隔离层250包围的像素的四个角之中的一个角处。控制栅极261可以沿第二区域220的与像素隔离层250相反的两侧设置。

560.如图61f所示,例如,第一区域210可以设置在被矩形的像素隔离层250包围的像素的一侧的中央。第二区域220可设置为与第一区域210分隔,并且与具有矩形形状的包围像素的外周的像素隔离层250的三侧接触。控制栅极261可以设置为沿第二区域220的与像素隔离层250相反的三侧设置。

561.如图61g所示,例如,第一区域210可设置为与具有矩形形状的包围像素的外周的像素隔离层250的三侧接触。第二区域220可以设置为与第一区域210分隔,并且可以设置在被矩形的像素隔离层250包围的像素的一侧的中央。控制栅极261可以设置为沿第二区域220的不与像素隔离层250相邻的三侧设置。

562.第一区域210和第二区域220的面积是确定在第一区域210和第二区域220附近产生的势垒的电容的因素之一。因此,可以通过考虑下述因素而适当地设定第一区域210和第二区域220区域的面积:是否通过使用由光电转换产生的空穴和电子来降低第一区域210或第二区域220的势垒的高度,并且在光电探测器200中产生正向电流。

563.(应用示例)

564.随后,参考图62和63说明应用示例,在图62和63中,根据本实施例的光电探测器200被应用于像素阵列.图62是其中将光电探测器200应用于3行

×

3列的像素阵列的平面构造的顶视图。图63是图示了在将光电检测器200应用于3行

×

3列的传感器200的情况下的等效电路的电路图。

565.如图62所示,根据本实施例的光电探测器200被像素隔离层250针对各个像素而隔离。根据本实施例的光电探测器200具有用于各个像素的平面矩阵布置。但是,关于第一区域210、第三区域230以及第二区域220,光电探测器200被布置为使得相邻像素的第一区域210、第三区域230和第二区域220的布置顺序是相反的。

566.此外,如图62和63所示,各个像素的第一区域210电连接至公共阴极电极ct,并且

各像素的控制栅极261电连接至公共栅极电极gate。此外,各像素的第二区域220电连接至各个像素的单独的阳极电极an。提供给各个像素的各阳极电极an输出像素的信号电流。

567.这样的平面布置使得根据本实施例的光电探测器200能够在根据本实施例的光电探测器200被设置为像素阵列的情况下以更高的面积效率布置。这使得光电探测器200能够具有更小的芯片面积。

568.《3.第三实施例》

569.(基本结构)

570.接着,参照图64至66说明根据本发明第三实施例的光电探测器的基本结构。

571.首先,参照图64和65说明根据本实施例的光电探测器的基本特性。根据本实施例的光电探测器是所谓的dpd传感器,其通过测量在所施加的偏压从反向偏压反转为正向偏压的情况下,直到正向电流流动为止的延迟时间来检测入射光。图64是按时间顺序图示将施加于光电探测器的偏压从反向偏压反转为正向偏压后的电荷移动的示意图。图65是按时间顺序图示将施加于光电探测器的偏压从反向偏压反转为正向偏压后的能带结构变化的曲线图。

572.如图64和65的各者的(1)所示,在施加到光电探测器的偏压从反向偏压反转为正向偏压的情况下,光电探测器首先使电子e从阴极电极(第一电极)朝向p 层(第二区域)周围的能带结构的下降区(也称为跌落区)流动。

573.如图64和65的各者的(2)所示,这降低p 层(第二区域)周围的势垒(减小跌落区的尺寸)。因此,更多的空穴h从p 层(第二区域)流出。

574.此外,如图64和65的各者的(3)所示,从p 层(第二区域)流出的空穴h降低了n 层(第一区域)周围的势垒。这进一步增加从n 层(第一区域)到p 层(第二区域)周边流动的电子e。之后,更多空穴h从p 层(第二区域)流出,更多电子e从n 层(第一区域)流出。这降低了n 层(第一区域)周围和p 层(第二区域)周围的势垒。

575.此后,如图64和65的各者的(4)所示,p 层(第二区域)和n 层(第一区域)之间的势垒消失。光电探测器进入稳态,其中正向电流在阴极电极(第一电极)和阳极电极(第二电极)之间流动。

576.在根据本实施例的光电探测器中,从反向偏压到正向偏压的反转到通过上述行为达到稳定状态的时间根据入射光的强度而变化。这是因为入射光的光电转换所产生的电子加速了电子e从阴极电极(第一电极)流入p 层(第二区域)周围的跌落区。这使根据本实施例的光电探测器可以通过测量在施加的偏压从反向偏压反转为正向偏压的情况下直到正向电流流动为止的延迟时间来检测入射光。

577.随后,参照图66说明根据本发明第三实施例的光电探测器的基本结构。图66是根据本实施例的光电探测器500的基本结构的垂直截面图。

578.如图66所示,光电探测器500包括第一区域510、第二区域520、第三区域530、第一电极511、第二电极521、第四区域525和绝缘层570。

579.第一区域510是设置在诸如硅(si)等半导体基板的第一表面侧的第一导电类型区域(例如,n 层)。例如,第一区域510可以设置在半导体基板的第一表面侧的整个表面上。

580.第二区域520是设置在诸如硅(si)等半导体基板的与第一表面相反的第二表面侧的第二导电类型区域(例如,p 层)。例如,第二区域520可以以岛状设置在半导体基板的第

二表面侧。

581.第三区域530是设置在诸如硅(si)等半导体基板的第一区域510和第二区域520之间的第三导电类型区域(例如,i层)。

582.第一电极511设置在半导体基板的第一表面。第一电极511电连接至第一区域510。第一电极511用作例如阴极电极。例如,第一电极511可以是共用电极,其设置在半导体基板的第一表面上以遍布多个像素并且向各个像素的第一区域510提供共用电势。

583.第二电极521设置在半导体基板的与第一表面相反的第二表面。第二电极521电连接至第二区域520。第二电极521用作例如阳极电极。

584.第一电极511和第二电极521可以各自通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。

585.第四区域525是在半导体基板的深度方向上与第二区域520接触设置的第一导电类型的区域(例如,n层)。具体地,第四区域525可以是在第二区域520的正下方设置在半导体基板内部的且具有比第一区域510低的杂质浓度的第一导电类型区域。

586.绝缘层570在半导体基板的面内方向上围绕第二区域520。绝缘层570被设置为到达在半导体基板的厚度方向上比第二区域520更深的区域。例如,绝缘层570可以设置在半导体基板的包括第二区域520周边的第二表面的整个表面上,或者可以仅设置在以岛状设置的第二区域520周围的区域中。绝缘层570可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

587.根据本实施例的光电探测器500例如可以用于测量入射光子数的光子计数应用。这里,为了适当地测量入射光子的数量,理想的是在参照图64和65的各者说明的状态转变中,光电探测器500由一个电子(即,一个光子)从(1)所示的状态转变为(2)所示的状态。为此,变得很重要的是,光电探测器500减小邻近于第二区域520产生的势垒的电容以进一步提高相对于势垒的每个电子的调制力(即,影响程度)。

588.根据本实施例的光电探测器500可以通过形成具有小面积的岛状第二区域520进一步减小第二区域520中产生的电容的大小,且可以通过使用绝缘层570围绕第二区域520的周边将产生电容的区域限制在第二区域520下方的区域。此外,光电探测器500在第二导电类型的第二区域520的下方设置有第一导电类型的第四区域525。这使得能够通过内置电势(built-in potential)而产生势垒。这使光电探测器500具有由内置电势而产生的势垒,且使得在与第二区域520相邻的区域中产生的势垒的电容变小。这使得光电探测器500能够以较少数量的电子来操作。

589.(变形例)

590.随后,参照图67至73b说明根据本实施例的光电探测器500的结构的变形例。

591.(第一变形例)

592.图67是根据第一变形例的光电探测器500a的结构的垂直截面图。

593.如图67所示,第一区域510和第一电极511可以设置在半导体基板的第二表面侧(即,设置有第二区域520和第二电极521的表面侧)。在这种情况下,除了围绕第二区域520周边的绝缘层570之外,还可以在设置于同一表面侧的第一区域510与第二区域520之间进一步设置面内隔离层552。面内隔离层552通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。面内隔离层552可以被形成为到达比

第一区域510和第二区域520的形成深度更深的区域。

594.根据第一变形例,光电探测器500a在半导体基板的同一表面侧设置有第一区域510、第一电极511、第二区域520和第二电极521。这可以进一步简化制造步骤。因此,光电探测器500a可以降低制造步骤的工艺难度。

595.(第二变形例)

596.图68是根据第二变形例的光电探测器500b的结构的垂直截面图。

597.如图68所示,光电探测器500b与根据第一变形例的光电探测器500a的不同之处在于,绝缘层570设置为遍布半导体基板的整个第二表面。具体地,绝缘层570可以设置在半导体基板的第二表面的除了设置有第一区域510和第二区域520的区域之外的区域中。

598.根据第二变形例,光电探测器500b可以提高第一区域510和第二区域520的电荷收集效率。

599.(第三变形例)

600.图69是根据第三变形例的光电探测器500c的结构的垂直截面图。

601.如图69所示,光电探测器500c与根据第二变形例的光电探测器500b的不同之处在于,第四区域525c设置为在半导体基板上延伸到绝缘层570的下方。具体地,第四区域525c可以设置到比绝缘层570的形成深度更深的区域。第四区域525c可以设置为延伸到绝缘层570下方的半导体基板的内部。

602.根据第三变形例,光电探测器500c可以提高第一区域510和第二区域520的电荷收集效率。

603.(第四变形例)

604.图70是根据第四变形例的光电探测器500d的结构的垂直截面图。

605.如图70所示,光电探测器500d与根据第三变形例的光电探测器500c的不同之处在于,每个区域中的导电类型的极性互换。具体地,第一区域510d是第二导电类型区域(例如,p 层)。第一区域510d设置在半导体基板的第二表面侧,以与第二区域520d相隔离。第二区域520d是第一导电类型区域(例如,n 层)。第二区域520d以岛状设置在半导体基板的第二表面这一侧。第四区域525d是第二导电类型区域(例如,p层)。第四区域525d设置为在半导体基板的深度方向上与第二区域520d接触。例如,第四区域525d可以设置为在第二区域520d正下方的半导体基板内部在绝缘层570下方延伸。

606.第一电极511设置在半导体基板的第二表面。第一电极511电连接至第一区域510d。第一电极511用作例如阴极电极。第二电极521设置在半导体基板的第二表面。第二电极521电连接至第二区域520d。第二电极521用作例如阳极电极。绝缘层570在半导体基板的面内方向上围绕第二区域520d。绝缘层570设置为到达在半导体基板的厚度方向上比第二区域520d更深的区域。

607.根据第四变形例,在施加的偏压从反向偏压反转为正向偏压的情况下,光电探测器500d可以通过空穴而不是电子的运动的触发而工作。

608.(第五变形例)

609.图71是根据第五变形例的光电探测器500e的结构的垂直截面图。

610.如图71所示,光电探测器500e与根据第三变形例的光电探测器500c的不同之处在于,第一区域510设置在半导体基板的第一表面侧。

611.具体地,第一区域510是第一导电类型区域(例如,n 层)。第一区域510设置为遍布半导体基板的第一表面侧的整个表面。第二区域520是第二导电类型区域(例如,p 层)。第二区域520以岛状设置在与半导体基板的与第一表面相反的第二表面侧。第四区域525是第一导电类型区域(例如,n层)。第四区域525也设置为在半导体基板的深度方向上与第二区域520接触,以在绝缘层570下方延伸。

612.第一电极511隔着第一表面绝缘层551设置在半导体基板的第一表面上。第一电极511通过贯穿第一表面绝缘层551的通孔512等与第一区域510电连接。第二电极521设置在半导体基板的与第一表面相反的第二表面。第二电极521电连接至第二区域520。绝缘层570在半导体基板的面内方向上围绕第二区域520。绝缘层570设置为到达在半导体基板的厚度方向上比第二区域520更深的区域。

613.根据第五变形例,光电探测器500e具有背面(即,第一表面)照射型结构。因此,能够提高产生的电荷数量与入射光的比率(即,量子效率)。

614.(第六变形例)

615.图72是根据第六变形例的光电探测器500f的结构的垂直截面图。

616.如图72所示,光电探测器500f与根据第五变形例的光电探测器500e的不同之处在于,在像素之间还设置有像素隔离层550。

617.具体地,像素隔离层550设置为在厚度方向上贯穿半导体基板以围绕像素区域。像素隔离层550将相邻像素彼此电隔离,从而能够抑制相邻像素之间的串扰。像素隔离层550可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

618.根据第六变形例,光电探测器500f具有在相邻像素之间的更高的物理或电隔离特性。因此,能够抑制像素之间的串扰。

619.随后,参照图73a和73b说明根据第六变形例的光电探测器500f的半导体基板的第二表面上的像素隔离层550、绝缘层570、第二区域520和第二电极521的布置和形状的变形例。图73a和73b均是说明像素隔离层550、绝缘层570、第二区域520和第二电极521的布置和形状的变形例的从第二表面侧观察到的平面图。

620.例如,如图73a所示,第二区域520和第二电极521可以以矩形形状设置在像素区域的大致中心。像素区域是像素隔离层550以矩形形状限定的。绝缘层570可以以具有圆角的矩形形状围绕第二区域520和第二电极521的周边。应注意,像素隔离层550、绝缘层570、第二区域520和第二电极521的形心可以彼此相同也可以彼此不同。

621.例如,如图73b所示,第二区域520和第二电极521可以以圆形或椭圆形设置在像素区域的大致中心。像素区域是像素隔离层550以矩形形状限定的。绝缘层570可以以具有圆角的矩形形状围绕第二区域520和第二电极521的周边。应注意,像素隔离层550、绝缘层570、第二区域520和第二电极521的形心可以彼此相同也可以彼此不同。

622.图73b所示的平面形状消除了第二区域520和第二电极521上的电场集中并且能够稳定电场。因此,能够减小在与第二区域520相邻的区域中产生的势垒的电容。此外,这种平面形状使得能够更容易地将第二区域520和第二电极521小型化。

623.《4.第四实施例》

624.(基本结构)

625.接着,参照图74至75b说明根据本发明第四实施例的光电探测器的基本结构。图54是根据本实施例的光电探测器600的基本结构的垂直截面图。图75a和75b均是图示根据本实施例的光电探测器600的能带结构的曲线图。

626.如图74所示,光电探测器600包括例如第一区域610、第二区域620、第三区域630、第四区域625、第五区域615、第一电极611、通孔(via)612、第一表面绝缘层651、像素隔离层650和第二电极621。

627.第一区域610是设置在诸如硅(si)等半导体基板的第一表面侧的第一导电类型区域(例如,n 层)。第二区域620是设置在诸如硅(si)等半导体基板的与第一表面相反的第二表面侧的第二导电类型区域(例如,p 层)。第四区域625是第一导电类型的区域(例如,n 层),其设置为在半导体基板的比第二区域620更深的内部与第二区域620接触。第五区域615是第二导电类型的区域(例如,p 层),其设置为在半导体基板的比第一区域610更深的内部与第一区域610接触。第三区域630是设置在半导体基板的第四区域625和第五区域615之间的第三导电类型的区域(例如,i层)。

628.换言之,光电探测器600是通过使用第一区域610、第二区域620、第三区域630、第四区域625和第五区域615形成的pn/i/pn二极管。

629.第一电极611隔着第一表面绝缘层651设置在半导体基板的第一表面上。第一电极611通过贯穿第一表面绝缘层651的通孔612等与第一区域610电连接。第一电极611用作例如阴极电极。例如,第一电极611跨越沿像素之间的边界设置的像素隔离层650延伸。第一电极611通过为每个像素设置的通孔612电连接至每个像素的第一区域610。即,第一电极611是向每个像素的第一区域610提供共用电势的共用电极。

630.像素隔离层650设置为在厚度方向上贯穿半导体基板,并且将在半导体基板的面内方向上设置的多个像素中的每一个彼此电隔离。例如,像素隔离层650可以沿着半导体基板的面内方向上以矩阵布置的各像素之间的边界以网格图案设置。

631.第二电极621设置在半导体基板的与第一表面相反的第二表面。第二电极621电连接至第二区域620。第二电极621用作例如阳极电极。

632.第一电极611、通孔612和第二电极621可以各自通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。第一表面绝缘层651和像素隔离层650可以分别通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

633.例如,即使在施加的偏压从反向偏压反转为正向偏压之后光子没有立即到达,根据包括pin二极管的比较例的光电探测器也可能产生正向电流。这是因为在施加的偏压从反向偏压反转为正向偏压的情况下,根据阴极电极侧产生的势垒的高度,扩散电流容易从阴极电极流过势垒。这导致阳极电极侧的能带结构具有变浅的下降区(也称为跌落区)。根据比较例的光电探测器即使光子没有到达,也可能产生正向电流。

634.根据本实施例的光电探测器600包括pn/i/pn二极管。如图75a所示,光电探测器600能够通过使用第一区域610和第五区域615的pn结而形成的内置电势在第一电极611侧稳定地形成能带的势垒。第一电极611是阴极电极。这使光电探测器600能够抑制由扩散电流引起的电子的移动。因此,能够抑制没有光子入射情况下的正向电流的产生。这使根据本实施例的光电探测器600能够抑制错误识别信号(aliasing)的发生。

635.例如,可以如下地使这样的光电探测器600进入工作。

636.具体地,如图55b所示,首先,光子入射到光电探测器600上产生光电子。产生的光电子填充能带结构的跌落区,以使能带结构的跌落区变浅(s1)。这导致空穴电流从作为阳极电极的第二电极621流向作为阴极电极的第一电极611,由内置电势形成在第一电极611侧的能带势垒消失(s2)。这使正向电流可以从作为阴极电极的第一电极611流向作为阳极电极的第二电极621(s3)。

637.(变形例)

638.随后,参照图76a至89说明根据本实施例的光电探测器600的结构的变形例。

639.(第一变形例)

640.图76a是根据第一变形例的光电探测器600a的结构的垂直截面图。图76b是根据第一变形例的光电探测器600a的结构的第二表面侧的平面图。

641.如图76a和76b所示,第二区域620可以例如设置为大致在由像素隔离层650限定的整个区域上。类似地,第一区域610、第四区域625和第五区域615可以各自设置为大致在由像素隔离层650(未图示)限定的整个区域上。与此相比,例如,第二电极621可以在由像素隔离层650限定的区域的大致中心处以岛状设置。

642.根据第一变形例,光电探测器600a具有在半导体基板的厚度方向上布置的第一区域610、第二区域620、第四区域625和第五区域615,从而可以减小占有面积。此外,通过在像素的整个周边上设置像素隔离层650,可以使光电探测器600a抑制像素之间的串扰。

643.(第二变形例)

644.图77a是根据第二变形例的光电探测器600b的结构的垂直截面图。图77b是根据第二变形例的光电探测器600b的结构的从第二表面侧观察到的平面图。

645.如图77a和77b所示,可以在像素隔离层650的在半导体基板的第二表面侧设置控制电极661。控制电极661可以控制第四区域625的电势。控制电极661可以通过控制第四区域625的电势来控制形成在第二电极621侧的能带结构的跌落区的深度以及填充该跌落区所需的电荷量。

646.具体地,控制电极661可以设置为在半导体基板的厚度方向上从半导体基板的第二表面侧延伸。控制电极661可以电连接至第四区域625。例如,控制电极661可以包括位于侧面的侧壁绝缘层662。控制电极661的宽度可以大于像素隔离层650的宽度,且控制电极661可以设置为延伸至第四区域625以电连接至第四区域625。控制电极661可以通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si)或其他导电材料而制成。侧壁绝缘层662可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

647.根据第二变形例,光电探测器600b能够更高精度地控制入射光的检测特性。

648.(第三变形例)

649.图78a是根据第三变形例的光电探测器600c的结构的垂直截面图。图78b是根据第三变形例的光电探测器600c的结构的从第二表面侧观察到的平面图。

650.如图78a和78b所示,可以在半导体基板的第二表面侧将控制电极661c设置在像素隔离层650中。控制电极661c能够控制第五区域615的电势。控制电极661c能够通过控制第五区域615的电势来控制形成在第一电极611侧的能带结构的势垒高度。

651.具体地,控制电极661c可以设置为在半导体基板的厚度方向上从半导体基板的第二表面侧延伸。控制电极661c可以电连接至第五区域615。例如,控制电极661c可以包括位于侧面的侧壁绝缘层662c。控制电极661c的宽度可以大于像素隔离层650的宽度,且控制电极661c可以设置为延伸至第五区域615以电连接至第五区域615。控制电极661c可以通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si)或其他导电材料而制成。侧壁绝缘层662c可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

652.根据第三变形例,光电探测器600c能够更高精度地控制入射光的检测特性。

653.(第四变形例)

654.图79a是根据第四变形例的光电探测器600d的结构的垂直截面图。图79b是根据第四变形例的光电探测器600d的结构的第二表面侧的平面图。

655.如图79a和79b所示,第二区域620d可以通过在半导体基板的第二表面侧以岛状设置而设置为具有比第一区域610小的体积。此外,第四区域625d可以设置为覆盖第二区域620d的侧面和底面。即,光电探测器600d可以设置为使第二电极621侧的第二区域620d和第四区域625d的pn结的面积小于第一电极611侧的第一区域610和第五区域615的pn结的面积。

656.这使光电探测器600d可以通过减小与第二电极621侧的第二区域620d相邻的区域中产生的电容来控制为了填充形成在第二电极621侧的能带结构的跌落区而所需的电荷量。这使光电探测器600d能够以较少数量的光电子而操作。

657.根据第四变形例,光电探测器600d能够进一步提高入射光的检测特性。

658.(第五变形例)

659.图80是根据第五变形例的光电探测器600e的结构的垂直截面图。

660.如图80所示,光电探测器600e与根据第四变形例的光电探测器600d的不同之处在于,控制电极663进一步电连接至第四区域625e。例如,控制电极663可以设置在半导体基板的第二表面且电连接至第四区域625e。控制电极663可以通过控制第四区域625e的电势,以控制形成在第二电极621侧的能带结构的跌落区深度以及控制为了填充该跌落区所需的电荷量。控制电极663可以通过使用诸如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。

661.根据第五变形例,光电探测器600e能够更高精度地控制入射光的检测特性。

662.(第六变形例)

663.图81a是根据第六变形例的光电探测器600f的结构的垂直截面图。图81b是根据第六变形例的光电探测器600f的结构的从第二表面侧观察到的平面图。

664.如图81a和81b所示,光电探测器600f与根据第四变形例的光电探测器600d的不同之处在于,控制栅极664进一步设置在第四区域625f上。控制栅极664可以设置在第四区域625f上,栅极绝缘膜665插入在控制栅极664与第四区域625f之间且具有围绕第二区域620f周边的平面形状。控制栅极664可以通过施加电压来控制第四区域625f的电势,以控制形成在第二电极621侧的能带结构的跌落区深度以及为了填充该跌落区所需的电荷量。

665.控制栅极664可以通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si)或其他导电材料而制成。栅极绝缘膜665可以通过使用诸如硅氧化物

(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

666.根据第六变形例,光电探测器600f能够更高精度地控制入射光的检测特性。

667.(第七变形例)

668.图82a是根据第七变形例的光电探测器600g的结构的垂直截面图。图82b是根据第七变形例的光电探测器600g的结构的从第二表面侧观察到的平面图。

669.如图82a和82b所示,光电探测器600g还可以设置有在半导体基板的面内方向上围绕第二区域620g和第四区域625g的绝缘层670。

670.具体地,第二区域620g和第四区域625g可以以岛状设置在由像素隔离层650限定的像素区域的大致中心。绝缘层670可以设置为围绕第二区域620g和第四区域625g的周边。绝缘层670在半导体基板的面内方向上围绕第二区域620g和第四区域625g。绝缘层670被设置为到达在半导体基板的厚度方向上比第二区域620g更深的区域。绝缘层670可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

671.具有小面积的岛状第二区域620g可以使绝缘层670进一步减小第二区域620g中产生的电容的大小。此外,绝缘层670围绕第二区域620g的周边,这使得能够将在第二区域620g中产生电容的区域限制在第二区域620g内部的半导体基板。这使绝缘层670能够通过减小在第二区域620g中产生的电容来控制为了填充形成在第二电极621侧的能带结构的跌落区而所需的电荷量。这使得光电探测器600g能够以较少数量的光电子而操作。

672.根据第七变形例,光电探测器600g能够进一步提高入射光的检测特性。

673.(第八变形例)

674.图83a是根据第八变形例的光电探测器600h的结构的垂直截面图。图83b是根据第八变形例的光电探测器600h的结构的第一表面侧的平面图。

675.如图83a和83b所示,光电探测器600h与根据第一变形例的光电探测器600a的不同之处在于,pn/i/pn二极管形成在半导体基板的面内方向,不是形成在半导体基板的厚度方向。此外,在光电探测器600h中,第一电极611和第二电极621均设置在半导体基板的第一表面。

676.具体地,第一区域610h沿着像素隔离层650限定矩形像素区域的一侧设置在半导体基板的第一表面侧的区域的一部分中。第五区域615h设置在隔着第一区域610h与像素隔离层650相对的区域中,以使第五区域615h覆盖第一区域610h的侧面和底面。第二区域620h沿着像素隔离层650限定矩形像素区域的相对的另一侧设置在半导体基板的第一表面侧的区域的一部分中。第四区域625h设置在与像素隔离层650相对的区域中,第二区域620h插入两者之间,以使第四区域625h覆盖第二区域620h的侧面和底面。第三区域630设置在第五区域615h和第四区域625h之间的区域中。第一电极611设置在从半导体基板的第一表面露出的第一区域610h上,第二电极621设置在从半导体基板的第一表面露出的第二区域620h上。

677.根据第八变形例,能够在半导体基板的同一表面上形成光电探测器600g的第一电极611和第二电极621。这使得能够更容易地形成电极。

678.(第九变形例)

679.图84a是根据第九变形例的光电探测器600i的结构的垂直截面图。图84b是根据第九变形例的光电探测器600i的从第一表面侧观察到的平面图。

680.如图84a和84b所示,光电探测器600i与根据第八变形例的光电探测器600h的不同之处在于,第一区域610i、第五区域615i、第四区域625i和第二区域620i设置为从半导体基板的第一表面延伸至与第一表面相反的第二表面。这使第一区域610i和第二区域620i可以通过覆盖像素隔离层650与第三区域630之间的界面,来抑制由于钉扎效应而在该界面处的电荷的感应。

681.根据第九变形例,光电探测器600i能够抑制在半导体基板和像素隔离层650之间的界面处的电荷的感应。这能够进一步降低噪声。

682.(第十变形例)

683.图85是根据第十变形例的光电探测器600j的结构的垂直截面图。

684.如图85所示,光电探测器600j与根据第八变形例的光电探测器600h的不同之处在于,第一控制电极663j-1进一步电连接至第五区域615j,且第二控制电极663j-2进一步电连接至第四区域625j。

685.具体地,第五区域615j可以设置为覆盖第一区域610j的侧面和底面,且第一控制电极663j-1可以设置在从半导体基板的第一表面露出的第五区域615j上。此外,第四区域625j可以设置为覆盖第二区域620j的侧面和底面,且第二控制电极663j-2可以设置在从半导体基板的第一表面露出的第四区域625j上。第一控制电极663j-1和第二控制电极663j-2可以分别通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。

686.第一控制电极663j-1可以通过控制第五区域615j的电势来控制形成在第一电极611侧的势垒的高度。此外,第二控制电极663j-2可以通过控制第四区域625j的电势,以控制形成在第二电极621侧的能带结构的跌落区深度以及为了填充该跌落区而所需的电荷量。

687.根据第十变型,光电探测器600j能够更准确地控制入射光的检测特性。

688.(第十一变形例)

689.图86a是根据第十一变形例的光电探测器600k的结构的垂直截面图。图86b是根据第十一变形例的光电探测器600k的结构的从第一表面侧观察到的平面图。

690.如图86a和86b所示,光电探测器600k与根据第八变形例的光电探测器600h的不同之处在于:光电探测器600k在第五区域615k上还设置有第一控制栅极664k-1,且光电探测器600k在第四区域625k上还设置有第二控制栅极664k-2。

691.具体地,第一控制栅极664k-1可以隔着栅极绝缘膜665k-1设置在第五区域615k上。第五区域615k设置为覆盖第一区域610k的侧面和底面。第二控制栅极664k-2可以隔着栅极绝缘膜665k-2设置在第四区域625k上。第四区域625k设置为覆盖第二区域620k的侧面和底面。

692.第一控制栅极664k-1和第二控制栅极664k-2可以分别通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。栅极绝缘膜665k-1和665k-2可以分别通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

693.第一控制栅极664k-1能够通过施加电压控制第五区域615k的电势来控制形成在第一电极611侧的势垒的高度。此外,第二控制栅极664k-2能够通过施加电压控制第四区域

625k的电势来控制形成在第二电极621侧的能带结构的跌落区深度以及为了填充该跌落区而所需的电荷量。

694.根据第十一变形例,光电探测器600k能够更准确地控制入射光的检测特性。

695.(第十二变形例)

696.图87是根据第十二变形例的光电探测器600l的结构的垂直截面图。

697.如图87所示,光电探测器600l与根据第一变形例的光电探测器600a的不同之处在于,包括有第一区域610l、第五区域615l、第三区域630l、第四区域625l和第二区域620l的半导体基板通过使用硅以外的半导体而形成。

698.例如,包括有第一区域610l、第五区域615l、第三区域630l、第四区域625l和第二区域620l的半导体基板可以通过使用硅锗(sige)或iii-v族化合物半导体等而形成。

699.根据第十二变形例,光电探测器600l能够控制可检测光的波长带。应注意,也可以将第十二变形例与上述第一至第十一变形例以及稍后说明的第十三和第十四变形例中的任一者组合。

700.(第十三变形例)

701.图88是根据第十三变形例的光电探测器600m的结构的垂直截面图。

702.如图88所示,在像素隔离层650内部还可以设置金属层681。金属层681具有遮光性。这能够防止从斜向入射到半导体基板的第一表面的光进入相邻的像素。金属层681可以通过使用例如诸如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属或其合金而制成。

703.根据第十三变形例,金属层681使光电探测器600m能够防止光进入像素之间。因此,能够进一步抑制像素之间的串扰。应注意,也能够将第十三变形例与上述第一至第十二变形例和稍后说明的第十四变形例中的任一者组合。

704.(第十四变形例)

705.图89是根据第十四变形例的光电探测器600n的结构的垂直截面图。

706.如图89所示,光电探测器600n还可以包括隔着层间绝缘膜(未图示)设置在半导体基板的第二表面侧的反射层682。具体地,反射层682可以对入射至半导体基板的第一表面后穿过第三区域630且入射在半导体基板的第二表面侧的光进行反射。这使反射层682能够将入射光限制在包括第三区域630的半导体基板中。因此,能够提高第三区域630中的光电转换效率。

707.反射层682可以设置在由像素隔离层650限定的整个像素区域上。反射层682可以通过使用例如诸如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属或其合金而制成。

708.根据第十四变形例,光电探测器600n使第三区域630具有更高的光电转换效率。因此,能够提高入射光的检测灵敏度。应注意,也能够将第十四变形例与上述第一至第十三变形例中的任一者组合。

709.《5.第五实施例》

710.随后,参照图90至128说明根据本发明第五实施例的光电探测器。

711.根据本实施例的光电探测器在诸如硅的半导体层与绝缘体层之间的界面处设置有:含有低浓度的第二导电类型杂质的层(例如,p层)或者具有负固定电荷或静电特性的层。

712.这使得包含第二导电类型杂质的层可以将在半导体层与绝缘体层之间的界面处

产生的界面态的电子与该层中的空穴再结合。因此,能够抑制由于在半导体层与绝缘体层之间的界面处产生的电子而引发的错误信号或暗电流。此外,具有负固定电荷或静电特性的层能够通过负电场在层界面处形成空穴积累层(hole accumulation layer)。这能够抑制在半导体层与绝缘体层之间的界面处的电荷(电子)产生。此外,具有负固定电荷或静电特性的层能够使在半导体层与绝缘体层之间的界面处产生的电荷(电子)消失在空穴积累层中。这能够抑制由于在半导体层与绝缘体层之间的界面处产生的电子而导致的错误信号或暗电流。

713.根据本实施例的光电探测器在半导体层与绝缘体之间的界面处设置有吸收如上所述地在该界面处产生的电荷的层(下文中,也称为钉扎层)。这能够进一步抑制错误识别信号或暗电流的产生。

714.对于根据本实施例的光电探测器,在下文中,作为第一至第十二结构例,将说明如下结构示例:在每个结构例中,将含有第二导电类型杂质的层用作钉扎层;并且作为第十三至第十八结构例,将说明如下结构示例:在每个结构例中,将具有负固定电荷或静电特性的层用作钉扎层。

715.(第一结构例)

716.图90是根据第一结构例的光电探测器700a的结构的垂直截面图。图91a和91b分别是根据第一结构例的光电探测器700a的平面结构的示例的顶视图。图90所示的光电探测器700a的横截面结构对应于分别沿着图91a和91b的a-aa切割面获取的横截面结构。

717.如图90所示,光电探测器700a包括例如第一区域710、第二区域720、第三区域730、钉扎层741、绝缘膜740、控制栅极761和栅极绝缘膜762。

718.第一区域710是设置在诸如硅(si)等半导体基板上的第一导电类型区域(例如,n 层)。第二区域720是设置在诸如硅(si)等半导体基板上的第二导电类型区域(例如,p 层)。第三区域730是设置在诸如硅(si)等半导体基板的除了第一区域710和第二区域720之外的区域中的第三导电类型区域(例如,i层)。

719.控制栅极761是隔着栅极绝缘膜762设置在半导体基板上的栅极电极。控制栅极761设置为通过施加电压来控制第三区域730中的势垒。控制栅极761可以通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si)或其他导电材料而制成。栅极绝缘膜762可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

720.控制栅极761设置为例如围绕第二区域720。例如,如图91a所示,控制栅极761可以在第一区域710和第二区域720的布置方向上设置在第二区域720的两侧。或者,如图91b所示,控制栅极761也可以设置为围绕第二区域720的整个周边。

721.这里,在第一区域710和第二区域720的布置方向上,第一区域710和控制栅极761之间的区域用作光电探测器700a中的光吸收区域731。光电探测器700a可以检测入射在光吸收区域731上的光。

722.例如,用作阴极电极的第一电极(未图示)电连接至第一区域710。此外,例如,用作阳极电极的第二电极(未图示)电连接至第二区域720。

723.绝缘膜740设置在诸如硅(si)等半导体基板的正面。绝缘膜740通过使用例如诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘材料而制成。

绝缘膜740可以例如是形成在硅基板正面的天然氧化膜。或者,绝缘膜740可以是单独设置在半导体基板正面以保护第三区域730的保护层。

724.钉扎层741是杂质浓度低于第二区域720的第二导电类型区域(例如,p层)。钉扎层741是设置在诸如硅(si)等半导体基板与绝缘膜740之间的界面处。应注意,钉扎层741与第一区域710或第二区域720之间的距离可以设置为使得光电探测器700a操作期间的最大电场小于0.5mev/cm。钉扎层741可以例如设置在光吸收区域731的半导体基板与绝缘膜740之间的界面处。光吸收区域731设置在第一区域710和控制栅极761之间。

725.钉扎层741能够使在半导体基板与绝缘膜740之间的界面处产生的界面态的电子与钉扎层741中的空穴复合。这使钉扎层741能够抑制在半导体基板与绝缘膜740之间的界面处产生的电子流入第三区域730的耗尽层而导致错误信号或暗电流。

726.根据第一结构例,光电探测器700a能够抑制错误识别信号(aliasing)或暗电流的产生。

727.(第二结构例)

728.图92是根据第二结构例的光电探测器700b的结构的垂直截面图。图93a和93b分别是根据第二结构例的光电探测器700b的平面结构的示例的顶视图。图92中所示的光电探测器700b的横截面结构对应于分别沿着图93a和93b的a-aa切割面获取的横截面结构。

729.如图92、93a和93b所示,光电探测器700b与根据第一结构例的光电探测器700a的不同之处在于,除了光吸收区域731,钉扎层741也设置在半导体基板的整个表面。具体地,钉扎层741可以设置为进一步围绕设置有第一区域710、第二区域720和控制栅极761的区域的周边。

730.根据第二结构例,光电探测器700b能够进一步抑制由于在半导体基板和绝缘膜740之间的界面处产生的电子而产生错误信号或暗电流。

731.(第三结构例)

732.图94是根据第三结构例的光电探测器700c的结构的垂直截面图。图95a、95b、97a和97b分别是如下区域的示例的平面图:在该区域中,钉扎层741形成在包括第三区域730的半导体层的正面侧。图96a、96b、98a和98b分别是如下区域的示例的平面图:在该区域中,钉扎层741形成在包括第三区域730的半导体层与埋设绝缘膜782之间的界面处。应注意,图94所示的光电探测器700c的横截面结构对应于分别沿着图95a至98b的a-aa切割面获取的横截面结构。

733.如图94所示,光电探测器700c包括例如第一区域710、第二区域720、第三区域730、钉扎层741、绝缘膜740、控制栅极763、栅极绝缘膜764、埋设绝缘膜782和支撑基板781。

734.支撑基板781例如是硅(si)基板等半导体基板。埋设绝缘膜782通过使用例如硅氧化物(sio

x

)而形成,并设置在支撑基板781上。此外,通过使用硅(si)等形成的半导体层设置在埋设绝缘膜782上。

735.换言之,其中形成有光电探测器700c的半导体基板是所谓的soi(绝缘体上硅)基板。支撑基板781对应于soi基板的支撑基板,埋设绝缘膜782对应于soi基板的box(buried oxide,埋设氧化物)层,且埋设绝缘膜782上的半导体层对应于soi基板的有源层。

736.第一区域710是设置在埋设绝缘膜782上的半导体层中的第一导电类型区域(例如,n 层)。第二区域720是设置在埋设绝缘膜782上的半导体层中的第二导电类型区域(例

如,p 层)。第三区域730是设置在第一区域710和第二区域720之间的半导体层中的第三导电类型区域(例如,i层)。第一区域710和第二区域720可以分别设置为在半导体层的厚度方向上延伸且从半导体层的正面到达埋设绝缘膜782。

737.例如,用作阴极电极的第一电极(未图示)电连接至第一区域710。此外,例如,用作阳极电极的第二电极(未图示)电连接至第二区域720。

738.控制栅极763设置为埋入在形成于半导体层上的栅极绝缘膜764中。控制栅极763也可以例如设置在与第一区域710或第二区域720相邻的区域中。控制栅极763通过施加电压来控制第三区域730中的势垒。

739.控制栅极763可以通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si)或其他导电材料而制成。栅极绝缘膜764可以通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

740.例如,如图95a至96b所示,第一区域710和第二区域720可以各自设置为在相对于半导体层的面内方向的一个方向上延伸。多个控制栅极763可以设置在第一区域710和第二区域720之间的与第一区域710和第二区域720相邻的区域中。在图75a至76b中,在第一区域710和第二区域720的布置方向上设置的多个控制栅极763之间的区域用作光电探测器700c中的光吸收区域731。

741.此外,如图97a至图98b所示,第一区域710和第二区域720可以各自设置为在相对于半导体层的面内方向的一个方向上延伸。控制栅极763可以以环状矩形形状设置在第一区域710和第二区域720之间的区域中。具体地,控制栅极763可以以如下的环状矩形设置:该环状矩形包括与第一区域710和第二区域720相邻的两条边和将这两条边彼此连接的两条边。在图97a至98b中,环状矩形的控制栅极763内部的区域是光电探测器700c中的光吸收区域731。

742.绝缘膜740设置在包括第三区域730的半导体层的正面。绝缘膜740通过使用例如诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘材料而制成。绝缘膜740可以例如是形成在半导体层正面上的天然氧化膜。或者,绝缘膜740可以是单独设置在半导体层正面上以保护第三区域730的保护层。

743.钉扎层741是杂质浓度低于第二区域720的第二导电类型区域(例如,p层)。钉扎层741设置在包括第三区域730的半导体层与绝缘膜740之间的界面和包括第三区域730的半导体层与埋设绝缘膜782之间的界面中的一个或两个界面处。

744.钉扎层741能够使在包含第三区域730的半导体层与绝缘膜740或埋设绝缘膜782之间的界面处产生的界面态的电子与钉扎层741中的空穴再结合。这使钉扎层741能够抑制在半导体层与绝缘膜740或埋设绝缘膜782之间的界面处产生的电子流入第三区域730的耗尽层而产生错误信号或暗电流。

745.这里,如图95a和97a所示,设置在包含第三区域730的半导体层与绝缘膜740之间界面处的钉扎层741可以设置在控制栅极763之间或设置到位于内侧的光吸收区域731。或者,如图95b和97b所示,设置在包含第三区域730的半导体层与绝缘膜740之间界面处的钉扎层741除了设置在光吸收区域731上,还可以设置在半导体基板的整个表面上。具体地,钉扎层741可以设置为进一步围绕设置有第一区域710、第二区域720和控制栅极763的区域的周边。

746.与此相比,如图96a和98a所示,设置在包含第三区域730的半导体层与埋设绝缘膜782之间界面处的钉扎层741可以设置在第一区域710和第二区域720之间的区域中。或者,如图96b和98b所示,设置在包括第三区域730的半导体层与埋设绝缘膜782之间界面处的钉扎层741不仅是设置在光吸收区域731上,而且设置在半导体基板的整个表面上。具体地,钉扎层741可以设置为进一步围绕设置有第一区域710和第二区域720的区域的周边。即,设置在包括第三区域730的半导体层与埋设绝缘膜782之间界面处的钉扎层741可以设置为延伸到控制栅极763下方的区域。

747.根据第三结构例,即使在其中形成有光电探测器700c的基板是soi基板的情况下,光电探测器700c也能够抑制错误识别信号或暗电流的产生。

748.(第四结构例)

749.图99是根据第四结构例的光电探测器700d的结构的垂直截面图。图100a、100b、102a和102b分别是如下区域的示例的平面图,其中,在电荷产生层783的正面侧形成钉扎层741。图101a、101b、103a和103b分别是如下区域的示例的平面图,其中,在包含第三区域730的半导体层与埋设绝缘膜782之间界面处形成钉扎层741。应注意,图99所示的光电探测器700d的横截面结构对应于沿着图100a至103b的各者的a-aa切割面获取的横截面结构。

750.如图99所示,光电探测器700d与根据第三结构例的光电探测器700c的不同之处在于:在包含第三区域730的半导体层上设置有电荷产生层783,且在电荷产生层783的正面上设置有钉扎层741。

751.电荷产生层783通过使用半导体材料制成,且设置在半导体层上的控制栅极763之间或内侧的区域中。电荷产生层783可以通过对入射光进行光电转换来产生电荷。例如,电荷产生层783可以通过使用锗(ge)、砷化镓(gaas)和硅锗(sige)中的一种或其混合物而形成。或者,电荷产生层783可以通过使用掺杂低浓度或高浓度导电杂质的硅而形成。

752.这使电荷产生层783例如对第三区域730中未被光电转换的波长带中的光进行光电转换。此外,电荷产生层783可以通过例如以与第三区域730中相同的方式光电转换入射光来提高光电探测器700d的量子效率。

753.如图100a至图101b所示,多个控制栅极763设置在被设置为沿相同方向延伸的第一区域710和第二区域720之间的区域中以与第一区域710和第二区域720相邻。在图100a至图101b中,在第一区域710和第二区域720的布置方向上的各控制栅极763之间的区域用作光电探测器700d中的光吸收区域731。

754.如图102a至图103b所示,控制栅极763可以以环状矩形设置在被设置为沿相同方向延伸的第一区域710和第二区域720之间的区域中。具体地,控制栅极763可以以这样的环状矩形设置,该矩形包括与第一区域710和第二区域720相邻的两条边和将这两条边彼此连接的两条边。在图102a至103b中,环状矩形控制栅极763内部的区域是光电探测器700d中的光吸收区域731。

755.绝缘膜740设置在电荷产生层783的正面。绝缘膜740通过使用例如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘材料而制成。绝缘膜740可以例如是形成在电荷产生层783正面上的天然氧化膜。或者,绝缘膜740可以是单独设置以保护电荷产生层783的保护层。

756.钉扎层741是杂质浓度比第二区域720低的第二导电类型区域(例如,p层)。钉扎层

741设置在电荷产生层783和绝缘膜740之间界面和包含第三区域730的半导体层和埋设绝缘膜782之间界面中的一个或两个界面处。钉扎层741能够抑制在电荷产生层783与绝缘膜740之间的界面处或在包含第三区域730的半导体层与埋设绝缘膜782之间的界面处产生的电荷流入第三区域730的耗尽层而产生错误信号或暗电流。

757.这里,如图100a和102a所示,设置在电荷产生层783与绝缘膜740之间的界面处的钉扎层741可以设置在控制栅极763之间或设置到位于内侧的光吸收区域731。或者,如图100b和102b所示,设置在电荷产生层783与绝缘膜740之间的界面处的钉扎层741除了可以设置在光吸收区域731上,还可以设置在半导体基板的整个表面上。具体地,钉扎层741可以设置为进一步围绕设置有第一区域710、第二区域720和控制栅极763的区域的周边。

758.与此相比,如图101a和103a所示,设置在包含第三区域730的半导体层与埋设绝缘膜782之间界面处的钉扎层741可以设置在第一区域710和第二区域720之间的平面区域中。

759.此外,如图101b和103b所示,设置在包括第三区域730的半导体层和埋设绝缘膜782之间界面处的钉扎层741不仅是设置在光吸收区域731上,而且设置在半导体基板的整个表面上。具体地,钉扎层741可以设置为进一步围绕设置有第一区域710和第二区域720的区域的周边。即,设置在包含第三区域730的半导体层与埋设绝缘膜782之间界面处的钉扎层741可以设置为延伸到控制栅极763下方的区域。

760.根据第四结构例,光电探测器700d能够提高对于入射光的光电转换特性。

761.(第五结构例)

762.图104是根据第五结构例的光电探测器700e的结构的垂直截面图。

763.如图104所示,光电探测器700e与根据第三结构例的光电探测器700c的不同之处在于:其中,形成有光电探测器700e的基板不是soi基板而是诸如硅基板等半导体基板。在这种情况下,钉扎层741可以设置在包含第三区域730的半导体基板与绝缘膜740之间的界面处。

764.根据第五结构例,光电探测器700e可以通过使用更便宜的基板来降低制造成本。

765.(第六结构例)

766.图105是根据第六结构例的光电探测器700f的结构的垂直截面图。

767.如图105所示,光电探测器700f与根据第三结构例的光电探测器700c的不同之处在于:在包含第三区域730的半导体层上设置有单片结构784,且钉扎层741形成在单片结构784的侧面。

768.单片结构784是通过对一个半导体基板进行加工而形成的结构。单片结构784设置在半导体层上的控制栅极763之间,或设置在内侧的区域中。单片结构784是光电转换入射光的光吸收层。单片结构784可以包括例如硅(si)、锗(ge)或碳化硅(sic)等。这使光电探测器700f可以提高对于入射光的光电转换特性。

769.这里,在单片结构784的与和第三区域730的堆叠表面相反的表面上可以设置有接触层785。接触层785例如是第二导电类型区域(例如,p 层)。光电探测器700f可以通过经由接触层785向单片结构784施加电压来控制单片结构784的电势。

770.此外,单片结构784的侧面设置有绝缘膜740。绝缘膜740通过使用例如诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘材料而制成。绝缘膜740可以例如是形成在单片结构784的侧面上的天然氧化膜。或者,绝缘膜740可以是单独设

置以保护单片结构784的保护层。

771.钉扎层741是杂质浓度比第二区域720低的第二导电类型区域(例如,p层)。钉扎层741设置在单片结构784的侧面与绝缘膜740之间的界面以及包含第三区域730的半导体层与埋设绝缘膜782之间的界面中的至少一个界面处。钉扎层741能够抑制在单片结构784的侧面与绝缘膜740之间的界面处或在包含第三区域730的半导体层与埋设绝缘膜782之间的界面处产生的电荷流入第三区域730的耗尽层而产生错误信号或暗电流。

772.根据第六结构例,即使在设置有单片结构784的情况下,光电探测器700f仍能够抑制错误识别信号或暗电流的产生。

773.(第七结构例)

774.图106是根据第七结构例的光电探测器700g的结构的垂直截面图。

775.如图106所示,光电探测器700g与根据第四结构例的光电探测器700d的不同之处在于:其中,形成有光电探测器700g的基板是诸如硅基板等半导体基板。在这种情况下,钉扎层741可以设置在包含第三区域730的半导体基板与绝缘膜740之间的界面处。

776.根据第七结构例,光电探测器700g可以通过使用更便宜的基板来降低制造成本。

777.(第八结构例)

778.图107是根据第八结构例的光电探测器700h的结构的垂直截面图。

779.如图107所示,光电探测器700h与根据第六结构例的光电探测器700f的不同之处在于:其中形成有光电探测器700h的基板是不包括支撑基板781的soi基板。在这种情况下,钉扎层741可以设置在单片结构784的侧面与绝缘膜740之间的界面处以及包含第三区域730的半导体层与单片结构784之间的界面处中的至少一个界面处。

780.根据第八结构例,光电探测器700h能够通过降低整体构造来使芯片更小。

781.(第九结构例)

782.图108是根据第九结构例的光电探测器700i的结构的垂直截面图。

783.如图108所示,光电探测器700i与根据第二结构例的光电探测器700b的不同之处在于,第一区域710设置在半导体基板的与设置有第二区域720的表面相反的表面。即,光电探测器700i与根据第二结构例的光电探测器700b的不同之处在于,第一区域710、第三区域730和第二区域720沿半导体基板的厚度方向布置。

784.具体地,第二区域720设置在半导体基板的第二表面侧。相反地,第一区域710设置在半导体基板的与设置有第二区域720的第二表面相反的第一表面侧。第三区域730是第三导电类型区域(例如,i层)。第三区域730设置在半导体基板的第一区域710和第二区域720之间。

785.这里,绝缘膜740设置在半导体基板的设置有第二区域720的第二表面。因此,钉扎层741可以设置在半导体基板的设置有第二区域720的第二表面与绝缘膜740之间的界面处。

786.根据第九结构例,光电探测器700i可以在半导体基板的厚度方向上布置第一区域710、第三区域730和第二区域720。这能够使芯片面积更小。

787.(第十结构例)

788.图109是根据第十结构例的光电探测器700j的结构的垂直截面图。

789.如图109所示,光电探测器700j与根据第九结构例的光电探测器700i的不同之处

在于设置了多个第二区域720。

790.具体地,多个第二区域720设置在半导体基板的第二表面侧以彼此隔离。此外,控制栅极761隔着栅极绝缘膜762设置在每个第二区域720周围的半导体基板上方。控制栅极716可以设置在第二区域720的两侧,或控制栅极716可以设置为围绕第二区域720的整个周边。

791.这里,在光电探测器700j中,多个第二区域720以及多个控制栅极761的各者之间的区域是光吸收区域731。绝缘膜740设置在光吸收区域731的半导体基板上。因此,钉扎层741可以设置在半导体基板的设置有光吸收区域731的第二表面与绝缘膜740之间的界面处。

792.根据第十结构例,光电探测器700j能够更有效地从第三区域730提取电流。

793.(第十一结构例)

794.图110是根据第十一结构例的光电探测器700k的结构的垂直截面图。

795.如图110所示,光电探测器700k包括第一区域710、第一电极711、第二区域720、第二电极721、第三区域730、复位区域791、复位电极766、栅极绝缘膜767、接地区域792、接地电极765、面内隔离层753和钉扎层741。

796.第一区域710、第一电极711、第二区域720、第二电极721和第三区域730已经相对于根据第一结构例的光电探测器700a等进行了说明,且因此在此不再说明。应注意,光电探测器700k在半导体基板的同一表面侧设置有第一区域710、第一电极711、第二区域720和第二电极721。

797.复位区域791是第一导电类型区域(例如,n 层)。复位电极766隔着栅极绝缘膜767设置在复位区域791上。通过从复位电极766施加电压,复位区域791可以将剩余在第三区域730内的电荷排出到第三区域730的外部。复位区域791可以设置在第二区域720的两侧,或复位区域791可以设置为围绕第二区域720的周边。

798.接地区域792是第二导电类型区域(例如,p 层)。接地区域792电连接至接地电极765并向第三区域730提供接地电势。接地区域792可以设置为与第一区域710和第二区域720隔离。

799.面内隔离层753设置在第一区域710、第二区域720、复位区域791和接地区域792之间,该第一区域710、第二区域720、复位区域791和接地区域792设置在包含第三区域730的半导体基板的同一表面侧。面内隔离层753通过使用诸如硅氧化物(sio

x

)、硅氮化物(sin

x

)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而形成。面内隔离层753将第一区域710、第二区域720、复位区域791和接地区域792彼此隔离。面内隔离层753可以设置为延伸至比第一区域710、第二区域720、复位区域791和接地区域792中的每一个的形成深度更深的区域。

800.在光电探测器700k中,钉扎层741可以设置在包含第三区域730的半导体基板与作为绝缘体的各面内隔离层753之间的界面处。具体地,钉扎层741可以设置为覆盖埋入在半导体基板中的面内隔离层753的侧面和底面。

801.根据第十一结构例,光电探测器700k能够抑制错误识别信号或暗电流的产生,并且提高电极之间的电隔离特性。

802.(第十二结构例)

803.图111是根据第十二结构例的光电探测器700l的结构的垂直截面图。

804.如图111所示,光电探测器700l包括例如第一区域710、第二区域720、第三区域730、第一电极711、通孔712、第一表面绝缘层751、像素隔离层750、第二电极721、控制栅极761和栅极绝缘膜762。

805.第一区域710是设置在诸如硅(si)等半导体基板的第一表面侧的第一导电类型区域(例如,n 层)。第二区域720是设置在诸如硅(si)等半导体基板的与第一表面相反的第二表面侧的第二导电类型区域(例如,p 层)。第三区域730是设置在诸如硅(si)等半导体基板的第一区域710和第二区域720之间的第三导电类型区域(例如,i层)。

806.第一电极711隔着第一表面绝缘层751设置在半导体基板的第一表面上。第一电极711通过贯穿第一表面绝缘层751的通孔712等与第一区域710电连接。第一电极711用作例如阴极电极。第一电极711例如设置为沿着像素之间的边界跨越像素隔离层750。第一电极711通过为每个像素设置的通孔712电连接至每个像素的第一区域710。

807.像素隔离层750设置为在厚度方向上贯穿半导体基板,并且将设置在半导体基板的面内方向上的多个像素中的每一个彼此电隔离。例如,像素隔离层750可以沿着在半导体基板的面内方向上以矩阵布置的各像素之间的边界以网格图案设置。

808.第二电极721设置在半导体基板的与第一表面相反的第二表面。第二电极721电连接至第二区域720。第二电极721用作例如阳极电极。

809.控制栅极761是隔着栅极绝缘膜762设置在半导体基板的第二表面上的栅极电极。控制栅极761可以通过施加电压来控制第三区域730中的势垒。

810.第一电极711、通孔712、第二电极721和控制栅极761可以分别通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。第一表面绝缘层751、像素隔离层750和栅极绝缘膜762可以分别通过使用诸如硅氧化物(sio

x

)、硅氮化物(sinx)、硅氮氧化物(sion)或所谓的低k材料等绝缘体而制成。

811.在光电探测器700l中,钉扎层741可以设置在像素隔离层750与第三区域730之间的界面处。具体地,钉扎层741可以设置为覆盖像素隔离层750的侧面。

812.根据第十二结构例,即使在光电探测器700l设置为背照式像素阵列结构的情况下,光电探测器700l也能够抑制错误识别信号或暗电流的产生。

813.(第十三结构例)

814.图112是根据第十三结构例的光电探测器700m的结构的垂直截面图。图113a和113b各自是根据第十三结构例的光电探测器700m的平面结构的示例的顶视图。图112所示的光电探测器700m的横截面结构对应于分别沿图113a和113b的a-aa切割面获取的横截面结构。

815.如图112、113a和113b所示,第十三结构例对应于这样的结构:将根据第一结构例的第二导电类型的钉扎层741替换为具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明钉扎层742以外的部件。应注意,钉扎层742可以如图112所示堆叠在半导体基板上,也可以如稍后说明的图116所示埋入在半导体基板内部。

816.钉扎层742是具有负固定电荷的层或具有负静电特性的层。钉扎层742可以通过使用例如下列的材料而形成:氧化硅(sio2)、氮化硅(sin)、氮氧化硅(sion)、氧化铪(hfo2)、氧化铝(al2o3)、氧化锆(zro2)、五氧化二钽(ta2o5)、氧化钛(tio2)、氧化镧(la2o3)、氧化镨(pr2o3)、氧化铈(ceo2)、氧化钕(nd2o3)、氧化钷(pm2o3)、氧化钐(sm2o3)、氧化铕(eu2o3)、氧化

钆(gd2o3)、氧化铽(tb2o3)、氧化镝(dy2o3)、氧化钬(ho2o3)、氧化铥(tm2o3)、氧化镱(yb2o3)、氧化镥(lu2o3)、氧化钇(y2o3)或各种树脂等。此外,钉扎层742可以形成为多层膜,其通过将上述的多种材料组合并堆叠而形成。应注意,钉扎层742可以通过使用任何其他材料而形成,只要该材料是具有负固定电荷或负静电特性的绝缘材料即可。

817.根据第十三结构例,光电探测器700m能够抑制错误识别信号或暗电流的产生。

818.(第十四结构例)

819.图114是根据第十四结构例的光电探测器700n的结构的垂直截面图。图115a和115b分别是根据第十四结构例的光电探测器700n的平面结构的示例的顶视图。图114所示的光电探测器700n的横截面结构对应于分别沿着图115a和115b的a-aa切割面获取的横截面结构。

820.如图114至图115b所示,第十四结构例对应于这样的结构:将根据第二结构例的第二导电类型的钉扎层741替换为在第十三结构例中已经说明的具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明每个部件。应注意,钉扎层742可以如图114所示堆叠在半导体基板上,也可以如稍后说明的图116所示埋入在半导体基板内部。

821.根据第十四结构例,光电探测器700n能够进一步抑制由于在半导体基板和绝缘膜740之间的界面处产生的电子而产生错误信号或暗电流。

822.(第十五结构例)

823.图116是根据第十五结构例的光电探测器700o的结构的垂直截面图。图117a、117b、119a和119b分别是如下区域的示例的平面图,其中,在包含第三区域730的半导体层的表面侧形成有钉扎层742。图118a、118b、120a和120b是这样区域的示例的平面图,其中,在包含第三区域730的半导体层与埋设绝缘膜782之间的界面处形成钉扎层742。应注意,图116所示的光电探测器700o的横截面结构对应于沿着图117a至120b的各者的a-aa切割面获取的横截面结构。

824.如图116至图120b所示,第十五结构例对应于这样的结构,其中,将根据第三结构例的第二导电类型的钉扎层741替换为在第十三结构例中已经说明的具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明每个部件。应注意,钉扎层742可以如图116所示埋入在半导体基板内部,也可以如上述的图112和114所示堆叠在半导体基板上。

825.根据第十五结构例,即使在其中形成有光电探测器700o的基板是soi基板的情况下,光电探测器700o也能够抑制错误识别信号或暗电流的产生。

826.(第十六结构例)

827.图121是根据第十六结构例的光电探测器700p的结构的垂直截面图。图122a、122b、124a和124b分别是如下区域的示例的平面图:其中,在电荷产生层783的表面侧形成有钉扎层742。图123a、123b、125a和125b分别是如下区域的示例的平面图:其中,在包含第三区域730的半导体层与埋设绝缘膜782之间的界面处形成有钉扎层742。应注意,图121所示的光电探测器700p的横截面结构对应于沿着图122a至125b的各者的a-aa切割面获取的横截面结构。

828.如图121至图125b所示,第十六结构例对应于这样的结构:将根据第四结构例的第二导电类型的钉扎层741替换为在第十三结构例中已经说明的具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明每个部件。应注意,钉扎层742可以如图121所示埋

入在电荷产生层783内部,也可以如上述的图112和114所示堆叠在电荷产生层783上。

829.根据第十六结构例,光电探测器700p能够提高对于入射光的光电转换特性。

830.(第十七结构例)

831.图126是根据第十七结构例的光电探测器700q的结构的垂直截面图。

832.如图126所示,第十七结构例对应于如下结构:其中,将根据第十一结构例的第二导电类型的钉扎层741替换为在第十三结构例中已经说明的具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明每个部件。

833.根据第十七结构例,光电探测器700q能够抑制错误识别信号或暗电流的产生,并且提高电极之间的电隔离性。

834.(第十八结构例)

835.图127是根据第十八结构例的光电探测器700r的结构的垂直截面图。

836.如图127所示,第十八结构例对应于如下结构:其中,将根据第十二结构例的第二导电类型的钉扎层741替换为在第十三结构例中已经说明的具有负固定电荷或静电特性的钉扎层742。因此,这里将不再详细说明每个部件。

837.根据第十八结构例,即使在光电探测器700r设置为背照式像素阵列结构的情况下,光电探测器700r也能够抑制错误识别信号或暗电流的产生。

838.《6.第六实施例》

839.(基本结构)

840.接着,参照图128a至130说明根据本发明第六实施例的光电探测器的基本结构。图128a是根据本实施例的光电探测器800的结构的从第二表面侧观察到的平面图。图128b是光电探测器800的结构在图128a的a-aa切割面中的垂直截面图。图128c是光电探测器800的结构在图128a的b-bb切割面中的垂直截面图。图129是光电探测器800中包括的像素电路中的像素晶体管的布置示例的平面图。图130是图示用作dpd传感器和pd的光电探测器800中包括的像素电路的等效电路的示例的电路图。

841.如图128a至128c所示,光电探测器800包括例如第一区域810、第二区域820、第三区域830、第一电极811、第二电极821、控制栅极cg、第一导电类型区域891、传输栅极trg、浮动扩散部fd和提取电极893。

842.第一区域810是设置在诸如硅(si)等半导体基板的第一表面侧的第一导电类型区域(例如,n 层)。第二区域820是设置在诸如硅(si)等半导体基板的与第一表面相反的第二表面侧的第二导电类型区域(例如,p 层)。例如,第二区域820可以以岛状设置,大致位于矩形像素区域的中心。第三区域830设置在诸如硅(si)等半导体基板的第一区域810和第二区域820之间且导电杂质浓度低于第一区域810的第一导电类型区域(例如,n-层)。

843.第一电极811设置在半导体基板的第一表面。第一电极811电连接至第一区域810。第一电极811用作例如阴极电极。第二电极821设置在半导体基板的与第一表面相反的第二表面。第二电极821电连接至第二区域820。第二电极821用作例如阳极电极。

844.控制栅极cg是隔着栅极绝缘膜(未图示)设置在半导体基板的第二表面上的栅极电极。控制栅极cg可以通过施加电压来控制第三区域830中的势垒。例如,控制栅极cg可以在半导体基板的平面中的第一方向(即,图128a的a-aa切割面的延伸方向)上设置在第二区域820的两侧。

845.第一导电类型区域891是设置在半导体基板的第二表面侧的第一导电类型区域(例如,n层)。第一导电类型区域891例如设置为导电杂质浓度低于第一区域810的导电杂质浓度且高于第三区域830的导电杂质浓度。第一导电类型区域891设置为从第二区域820沿半导体基板的平面中的与第一方向正交的第二方向(即,图128a的b-bb切割面的延伸方向)延伸。

846.浮动扩散部fd是具有比第二区域820更高的导电杂质浓度的第二导电类型区域(例如,p 层)。浮动扩散部fd设置在半导体基板的第二表面侧。浮动扩散部fd可以设置在从第二区域820沿第二方向延伸的第一导电类型区域891的端侧。

847.传输栅极trg是隔着栅极绝缘膜(未图示)设置在半导体基板的第二表面上的栅极电极。传输栅极trg设置在第二区域820和浮动扩散部fd之间,并且通过施加电压将电荷从第二区域820传输到浮动扩散部fd。

848.这里,第一导电类型区域891可以设置到传输栅极trg下方的区域以及围绕设置有浮动扩散部fd的区域的区域中。这使第一导电类型区域891可以用作将电荷从第二区域820传输到浮动扩散部fd的沟道。此外,第一导电类型区域891能够防止在第三区域830中光电转换得到的电荷直接进入浮动扩散部fd。

849.提取电极893设置在半导体基板的第一表面并且电连接至浮动扩散部fd。提取电极893可以将在浮动扩散部fd中积累的电荷输出到像素电路等。

850.第一电极811、第二电极821、控制栅极cg、传输栅极trg和提取电极893可以分别通过使用例如铝(al)、铜(cu)、钨(w)、钛(ti)或钽(ta)等金属,多晶硅(poly-si),或其他导电材料而制成。

851.因此,如图128a和128b所示,光电探测器800包括第一区域810、第二区域820、第三区域830、第一电极811、第二电极821和控制栅极cg。这使光电探测器800可以用作dpd(动态光电二极管)传感器。

852.此外,如图128a和128c所示,光电探测器800包括例如第一区域810、第二区域820、第三区域830、第一电极811、第一导电类型区域891、传输栅极trg、浮动扩散部fd和提取电极893。这使光电探测器800可以用作一般的pd(光电二极管)。

853.这里,在光电探测器800用作一般的pd的情况下,从浮动扩散部fd提取出的电荷通过像素电路的信号处理被转换为像素信号。

854.图130图示了光电探测器800中包括的像素电路的等效电路图。注意,图130中的dpd/pd表示具有第一区域810、第三区域830和第二区域820的pin二极管结构的光电转换部。

855.如图130所示,dpd传感器的像素电路包括光电转换部dpd和开关晶体管sw。在dpd传感器的像素电路中,光电转换部dpd通过开关晶体管sw与电源va电连接。

856.pd的像素电路包括光电转换部pd、传输晶体管trg、浮动扩散部fd、复位晶体管rst、放大晶体管amp和选择晶体管sel。在pd的像素电路中,光电转换部pd通过传输晶体管trg电连接至浮动扩散部fd。此外,电源vd还通过复位晶体管rst连接至浮动扩散部fd。此外,放大晶体管amp的栅极连接至浮动扩散部fd。放大晶体管amp的漏极连接至电源vd,放大晶体管amp的源极通过选择晶体管sel连接至外部输出output。应注意,dpd传感器侧的电源va和pd侧的电源vd可以是彼此不同的电源,也可以是同一个电源。

857.光电探测器800包括这样的像素电路。这使光电探测器800可以用作dpd传感器和pd。

858.此外,如图129所示,包括在上述像素电路中的像素晶体管中的至少任何一个或多个可以形成在光电探测器800的像素晶体管区域tr中。具体地,复位晶体管rst、放大晶体管amp、选择晶体管sel或开关晶体管sw可以形成在像素晶体管区域tr中,该像素晶体管区域tr设置在像素区域的第一方向(即,图128a的a-aa切割面的延伸方向)的两端。

859.例如,复位晶体管rst和放大晶体管amp可以形成在传输栅极trg一侧的像素晶体管区域tr中。此外,选择晶体管sel和开关晶体管sw可以形成在传输栅极trg另一侧的像素晶体管区域tr中。

860.(操作示例)

861.随后,参照图131至133c说明根据本实施例的光电探测器800作为tof(飞行时间)传感器的操作示例。

862.图131是图示根据本实施例的光电探测器800的tof传感器的操作的示例的时序图。图132是说明tof传感器所使用的光源的说明图。图133a是说明光电探测器800在图111的时刻(1)的状态的垂直截面图。

863.图133b是说明光电探测器800在图111的时刻(2)的状态的垂直截面图。图133c是说明光电探测器800在图111的时刻(3)的状态的垂直截面图。

864.如图131和133a所示,首先,在图131的时刻(1)将正电压施加到电压v

sw

以施加到开关晶体管sw的栅极,以使开关晶体管sw导通。随后,假设施加到第二电极821的电压va是负电压(例如,-1v)。在这种情况下,施加到第一电极811的电压vc为0v。因此,在光电探测器800的第一区域810和第二区域820之间施加反向偏压。应注意,施加到控制栅极cg的电压v

con

被设置为负电压(例如,-1v)。

865.这里,如图131、132和133b所示,在图131的时刻(2)施加脉冲负电压v

light

到诸如激光二极管或led(发光二极管)等光源ld,以使用脉冲光照射目标。同时,将正电压(例如, 1v)作为要施加至第二电极821的电压va进行施加,以在光电探测器800的第一区域810和第二区域820之间施加正向偏压。此外,施加到控制栅极cg的电压v

con

被设置为正电压(例如, 1v)。

866.之后,目标反射的脉冲光入射到光电探测器800上,从第二电极821输出的电流值随着从时刻(2)延迟而增大。这使光电探测器800可以通过计算光源ld的发光时刻t2与光检测延迟时间t1之间的差来计算到目标的距离。

867.此外,如图131和133c所示,在图131的时刻(3)将负电压(例如,-1v)作为电压va施加到第二电极821。这在光电探测器800的第一区域810和第二区域820之间施加反向偏压。光电探测器800的状态因此被复位。应注意,施加到控制栅极cg的电压v

con

可以被同样设置为负电压(例如,-1v)。

868.通过以从(1)到(3)的时间为一帧重复上述操作,光电探测器800可以针对每一帧检测与目标的距离。

869.与此相对地,施加到传输栅极trg的栅极的电压v

trg

和施加到复位晶体管rst的栅极的电压v

rst

在整个一帧中为0v。传输栅极trg和复位晶体管rst是pd侧的像素电路。此外,与浮动扩散部fd电连接的提取电极893的电压在整个一帧中不改变。

870.此外,参照图134至135e说明根据本实施例的光电探测器800作为pd的操作示例。

871.图134是图示根据本实施例的光电探测器800的pd操作的示例的时序图。图135a是说明光电探测器800在图134的时刻(1)的状态的垂直截面图,图135b是说明光电探测器800在图134的时刻(2)的状态的垂直截面图。图135c是说明光电探测器800在图134的时刻(3)的状态的垂直截面图,图135d是说明光电探测器800在图134的时刻(4)的状态的垂直截面图。图135e是说明光电探测器800在图134的时刻(5)的状态的垂直截面图。

872.如图134和135a所示,首先,在图134的时刻(1)将施加到开关晶体管sw的栅极的电压v

sw

设置为0v,以使开关晶体管sw截止,且将施加到第二电极821的电压va设置为0v。此外,将脉冲电压v

rst

(例如, 1v)施加到复位晶体管rst的栅极,以将浮动扩散部fd中积累的电荷排出到电源vd,使浮动扩散部fd的状态复位。

873.然后,如图135b所示,将脉冲电压v

trg

(例如,-3v)施加到传输晶体管trg的栅极,以将存在于第二区域820中的电荷传输到浮动扩散部fd,使第二区域820的状态复位。这使光电探测器800在图134的时刻(2)开始接收入射光。

874.随后,如图134和135c所示,光电探测器800对入射在第三区域830上的光进行光电转换并将光电转换得到的电荷积累在第二区域820中。

875.如图134和135d所示,从图134的时刻(1)开始经过预定时间后,在图134的时刻(4)将脉冲电压v

rst

(例如, 1v)施加到复位晶体管rst的栅极,以将浮动扩散部fd中积累的电荷排出到电源vd,使浮动扩散部fd的状态复位。

876.如图135e所示,然后将脉冲电压v

trg

(例如,-3v)施加到传输晶体管trg的栅极以将第二区域820中积累的电荷传输到浮动扩散部fd,并且从提取电极893读出信号电荷。这使光电探测器800在图114的时刻(5)进入与图134的时刻(2)相同的状态。这可以再次开始接收入射光。

877.以从(1)到(4)的时间为一帧重复上述操作。这使光电探测器800为每一帧将对应于接收光量的电荷转换为电信号,并将该电信号输出为图像信号。

878.(像素阵列的电路结构)

879.此外,参照图136说明在根据本实施例的光电探测器800构造为多个像素以矩阵布置的像素阵列的情况下的电路构造的示例。图136是图示根据本实施例的光电探测器800为像素阵列时的功能构造的框图。

880.如图136所示,dpd控制电路801、dpd信号检测电路803、pd控制电路802和pd信号检测电路804连接至每个像素的光电转换部dpd/pd。

881.每个像素的dpd控制电路801和dpd信号检测电路803连接至dpd水平控制部8210、dpd信号处理部8220和垂直控制单元8300。此外,每个像素的pd控制电路802和pd信号检测电路804连接至pd水平控制部8110、pd信号处理部8120和垂直控制单元8300。此外,每个像素连接至切换光电转换部dpd/pd的dpd操作或pd操作的dpd/pd切换控制单元8400。

882.dpd/pd切换控制单元8400连接至dpd水平控制部8210、pd水平控制部8110和每个像素。dpd/pd切换控制单元8400通过输出dpd/pd切换信号来切换每个像素的dpd/pd操作。

883.应注意,dpd/pd操作的切换可以一次对所有像素进行,也可以对像素阵列的每个预定像素进行,这取决于诸如成像或测距之类的应用。此外,dpd/pd操作可以以分时方式进行切换,或可以针对每一帧进行切换。

884.垂直控制单元8300连接至dpd水平控制部8210和pd水平控制部8110。在光电转换部dpd/pd进行dpd操作和pd操作的情况下,垂直控制单元8300将读出信号逐行输出到dpd水平控制部8210和pd水平控制部8110。

885.在输入每行的读出信号的情况下,dpd水平控制部8210逐列读出每个像素的dpd信号,并将读出的dpd信号输出到dpd信号处理部8220。

886.在对输入的dpd信号进行信号处理之后,dpd信号处理部8220将经过信号处理的dpd信号作为tof数据输出。

887.在输入每行的读出信号的情况下,pd水平控制部8110逐列读出每个像素的pd信号,并将读出的pd信号输出到pd信号处理部8120。

888.在对输入的pd信号进行信号处理之后,pd信号处理部8120将经过信号处理的pd信号作为图像数据输出。

889.tof光源控制单元8500连接至垂直控制单元8300和dpd信号处理部8220。tof光源控制单元8500控制在tof操作期间发光的光源ld的发光时刻。tof光源控制单元8500可以通过将光源ld的发光时刻信号输出到垂直控制单元8300和dpd信号处理部8220来控制dpd信号的信号处理或dpd信号的读出。

890.(变形例)

891.随后,参照图137a至147c说明根据本实施例的光电探测器800的结构的变形例。

892.(第一变形例)

893.图137a是根据第一变形例的光电探测器800a的结构的从第二表面侧观察到的平面图。图137b是光电探测器800a的结构在图137a的a-aa切割面中的垂直截面图。图137c是光电探测器800a的结构在图137a的b-bb切割面中的垂直截面图。

894.如图137a至137c所示,光电探测器800a与参照图128a至128c说明的光电探测器800的不同之处在于,光电探测器800a还包括第一导电类型区域895、溢流栅极ofg、溢流漏极ofd和放电电极897。

895.第一导电类型区域895是设置在半导体基板的第二表面侧的第一导电类型区域(例如,n层)。第一导电类型区域895设置为例如导电杂质的浓度低于第一区域810的浓度且导电杂质的浓度高于第三区域830的浓度。第一导电类型区域895可以设置为在与第一导电类型区域891的延伸方向相反的方向上从第二区域820延伸。

896.溢流漏极ofd是导电杂质浓度高于第二区域820的第二导电类型区域(例如,p 层)。溢流漏极ofd设置在半导体基板的第二表面侧。溢流漏极ofd可以设置在从第二区域820延伸的第一导电类型区域895的端侧。

897.溢流栅极ofg是隔着栅极绝缘膜(未图示)设置在半导体基板的第二表面上的栅极电极。溢流栅极ofg设置在第二区域820和溢流漏极ofd之间。溢流栅极ofg控制电荷从第二区域820向溢流漏极ofd的排放。

898.这里,第一导电类型区域895可以设置于在溢流栅极ofg下方的区域和设置有溢流漏极ofd的区域周围的区域中。这使第一导电类型区域895可以用作将电荷从第二区域820排出到溢流栅极ofg的沟道。此外,第一导电类型区域895可以防止第三区域830光电转换得到的电荷直接进入溢流漏极ofd。

899.放电电极897设置在半导体基板的第一表面且电连接至溢流漏极ofd。放电电极

897电连接至电源。放电电极897能够将排出至溢流漏极ofd的电荷进一步排出至电源。

900.这使光电探测器800a能够将在pd操作期间产生的超过饱和电荷量的电荷从第二区域820排出到溢流漏极ofd。被排出到溢流漏极ofd的电荷通过放电电极897进一步排出到电源。这使光电探测器800a能够抑制在pd操作期间产生光晕。

901.根据第一变形例,光电探测器800a还包括溢流栅极ofg和溢流漏极ofd,从而能够抑制pd操作期间的光晕。

902.(第二变形例)

903.图138a是根据第二变形例的光电探测器800b的结构的第二表面侧的平面图。图138b是光电探测器800b的结构在图138a的a-aa切割面中的垂直截面图。图138c是光电探测器800b的结构在图138a的b-bb切割面中的垂直截面图。

904.如图138a至138c所示,光电探测器800b与参照图128a至128c说明的光电探测器800的不同之处在于光电探测器800b还包括限定像素区域的像素隔离层850。