1.本发明涉及一种基于概率计算的模拟译码电路停止准则的译码方法,具体涉及一种针对ldpc编码方式的基于概率计算的模拟译码电路停止准则的译码方法,属于通信信号处理领域。

背景技术:

2.模拟概率信号处理(analog probability processing,简称app)技术以概率图模型(probabilistic graphical model)作为连接算法与处理器架构设计的桥梁,将cmos电路亚阈值区域下电流电压指数特性与迭代消息传递算法(iterative message-passing algorithms,简称impas)紧密耦合,实现了概率信号处理芯片的研制工作。与目前常用的数字信号处理器(如:arm、dsp、fpga等)相比,概率信号处理器在信号处理精度、功耗、可靠性等诸多方面具有显著优势,因此概率信号处理器已在仿生设备、超长续航生物信号检测以及通信雷达信号处理器等方面取得了诸多应用。

3.在通信信号处理领域,针对诸如:信道均衡、多用户检测、多用户干扰消除、信道编译码等概率密集型问题,概率信号处理技术已经有较为广泛的应用。其中,信道编译码技术作为概率信号处理技术的出发点和重要研究方向,其对应的模拟译码芯片可以以远低于数字处理器的功耗以及芯片面积实现相同的信号处理功能。特别的,低密度奇偶校验(low density parity check,简称ldpc)码作为近年来性能优异的信道编译码,因具备接近香农极限的性能以及可并行处理的特点已被广泛应用于多种商业标准,如802.11、802.16、dvb-s2、ccsds和5g等。

4.近年来,基于模拟概率信号处理技术的ldpc译码器因结合了概率译码以及电流模技术的特点,其在功耗、处理能效以及处理鲁棒性等方面较数字译码器均有了跨数量级的性能提升。然而,就模拟译码电路而言,传统的停止准则通过基于校验式(ch

t

=0)成立以及基于最大迭代次数进行判断,其中基于校验式成立的硬判决造成电路实现复杂度高,且基于最大迭代次数的判断造成系统吞吐量受限。因此亟需开展与模拟译码电路完美耦合的低功耗低复杂度迭代译码停止准则算法以及对应的概率译码方法及系统设计。

技术实现要素:

5.为了解决现有技术存在的下述技术缺陷:(一)传统ldpc译码停止准则和译码过程应用于模拟译码电路时,硬判决导致电路实现复杂度高、处理功耗高;(二)传统ldpc译码停止准则和译码过程基于最大迭代次数进行译码迭代时,存在无效迭代过程,系统处理时延高,吞吐量受限;本发明主要目的是提供一种基于概率计算的模拟译码电路停止准则的译码方法,将ldpc译码图模型中校验节点归一化满足概率的进化图案与译码器状态紧密耦合,以进化图案收敛性分析指导模拟译码电路的最优停止准则,以此构建适用于模拟译码电路的概率图模型和信息更新传递算法,提出ldpc模拟译码电路的基于该停止准则的译码方法;进而本发明具有如下优点:(一)在概率域给出与ldpc模拟译码电路完美耦合的最优

停止准则及译码算法,有效降低电路实现复杂度和动态功耗;(二)实时在线判断译码状态并减少无效迭代过程,降低译码处理时延,提高系统吞吐量。本发明还能够根据ldpc译码因子图模型实现基于适用于模拟译码电路的停止准则的译码器。

6.本发明的目的是通过下述技术方案实现的。

7.本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,包括如下步骤:

8.步骤一,针对ldpc模拟译码电路建立因子图模型。

9.根据校验矩阵h

judge

构建具有校验约束关系的因子图模型g=(vns∪cns,ξ),其中vns代表变量节点集合,cns代表校验节点集合,ξ代表连接变量节点和校验节点的边集合。

10.校验节点集合中每个cn对应校验矩阵的行维度,表示校验约束关系式中ki表示受该校验方程约束的码字索引;x表示符号值,取值为0或1;变量节点集合中每个vn对应校验矩阵的列维度,表示每比特信息;每个ξ对应校验矩阵h

judge

中1的所在位置,表示因子图中信息的更新与传递。

11.校验矩阵h

judge

每行中1的个数表明对应校验方程约束码字的个数,且1在该行中的位置表明所约束的码字位数,在因子图中该校验节点与被约束码字对应的变量节点相连接。同理,矩阵每列中值为1时表明该码字受此校验方程约束,在因子图中该变量节点与相对应校验节点连接。即当校验矩阵h

judge

中第m行第n列值为1时,表明第m个码字受第n个校验方程的约束,此时变量节点vnm与校验节点cnn在因子图上相连,迭代过程中节点更新的信息在该边上相互传递。

12.因子图的输入信息集合是vo=(v1,v2,...vk),vk表示码字信道似然概率p(yi|xi),其中,xi是发射符号,yi是接收符号,迭代过程完成后,因子图的输出信息集合是b=(b1,b2,...bk),bk表示码字的近似后验概率信息其中,bk表示符号值,y表示信道接收序列信息集合,表示信道传输过程中的未知参数;所示未知参数包括:定时同步信息、载波相位信息。

13.步骤二,针对ldpc模拟译码电路停止准则建立因子图模型。

14.在步骤一建立的ldpc译码因子图模型基础上,添加校验节点满足概率检测节点g=(g1,g2,...,gk)以及校验节点归一化满足概率统计节点g

ave

。

15.校验节点cns=(c1,c2,...,ck)向与其相连的校验节点满足概率检测节点g=(g1,g2,...,gk)单向传递信息,其中gk表示第k个检测节点,ck表示第k个校验节点,即检测节点g的输入为:

[0016][0017]

其中,cn表示接收概率信息的校验节点,vm表示传递概率信息的变量节点,gi表示检测节点符号索引,即校验节点传递值为0或1,上标k表示译码迭代周期;h为校验矩阵约束,y为信道接收序列,p为概率。v

m'

∈n(cn)\gi表示v

m'

属于与校验节点cn相连的,但不包括变量节点gi的所有变量节点集合;表示对除了gi以外所有变量节点的函数求和,ic(cn)表示校验节点cn对应的校验约束,即:

[0018][0019]

δ为函数,表示为:当时δ=1,当时δ=0;当该不包含变量gi的校验约束成立时,除变量gi以外满足该约束的所有变量节点的符号信息乘积之和即为校验节点传递信息。

[0020]

检测节点g的输出为校验节点满足概率该式代表在已知信道接收序列y和校验矩阵h的条件下,经过k次迭代后校验方程检测节点输出校验关系gi为0的概率,即该校验方程成立的概率;所述概率表示为:

[0021][0022]gave

的输出为校验节点归一化满足概率p(g(k)),即对所有检测节点g的输出值做归一化:

[0023][0024]

其中,表示校验节点满足概率,num(c)表示校验节点数目。

[0025]

在传统ldpc译码因子图中,信息在变量节点和校验节点之间进行双向传递,本发明在此基础上添加校验节点满足概率检测节点g以及校验节点归一化满足概率统计节点g

ave

,且信息从校验节点单向传递给校验节点满足概率检测节点g。因此,停止准则因子图模型和对应硬件的增加不影响传统ldpc译码过程,即能够通过在传统译码电路上直接添加停止准则相关电路实现译码器电路设计,有效降低电路实现复杂度和动态功耗。

[0026]

步骤三,初始化变量节点。

[0027]

根据高斯白噪声信道的概率分布,信道码字变量节点初始化信息为:

[0028][0029]

其中,xi表示接收序列的符号索引,取值为0或1,y

l

表示接收序列的幅值,l表示接收序列索引,σ2为信道噪声方差,表示第一次迭代周期中变量节点的更新信息。

[0030]

步骤四,校验节点更新。

[0031]

校验节点向变量节点传递更新概率信息集合即在已知信道接收序列y和校验矩阵h的条件下,校验节点向变量节点传递符号xi为0或1的概率,校验节点更新信息为:

[0032][0033]

其中,cn表示接收概率信息的校验节点,vm表示传递概率信息的变量节点,xi表示信息符号索引,取值为0或1,v

m'

∈n(cn)\vm表示v

m'

属于与校验节点cn相连的,不包括变量节点vm的所有变量节点集合,~{vm}表示除了vm以外的所有变量节点集合,上标k表示译码迭代周期。校验节点信息代表除vm以外与校验节点cn相连的所有变量节点

模二和为0的概率密度函数表征。

[0034]

步骤五,变量节点更新。

[0035]

变量节点向校验节点传递更新概率信息集合即在已知信道接收序列y和校验矩阵h的条件下,变量节点向校验节点传递符号xi为0或1的概率,根据校验约束关系和校验节点信息,变量节点更新信息集合为:

[0036][0037]

其中,vm表示传递概率信息的变量节点,cn表示接收概率信息的校验节点,c

n'

∈n(vm)\cn表示c

n'

属于与变量节点vm相连的,不包括校验节点cn的所有校验节点集合,上标k表示译码迭代周期;其中,α

mn

为参数,使得关系式满足

[0038]

步骤六,迭代停止准则判断:通过校验节点归一化满足概率统计节点g

ave

输出的校验节点归一化满足概率p(g(k))的收敛性对译码状态进行判断,符合迭代停止准则时停止译码,跳转到步骤七进行码字判决输出,否则跳转到步骤四继续进行迭代译码,直至符合迭代停止准则。

[0039]

因子图节点g

ave

输出校验节点归一化满足概率p(g(k)):

[0040][0041]

由校验节点归一化满足概率p(g(k))在迭代过程中的变化趋势可知,迭代译码过程中,当码字为可译码型时,校验节点归一化满足概率p(g(k))的值由0.5逐渐趋近于1并收敛。当码字由于自身误码率限制为不可译码型时,校验节点归一化满足概率p(g(k))的值可能在0.5到0.9之间任一区间内逐渐收敛,此时为收敛但不可译码型,或在0.5到0.9之间任一区间内持续震荡,此时为不收敛码型。根据不同信噪比下码型的分布统计知大多数码型为收敛码型。

[0042]

基于此,停止准则表示为:(一)当译码达到最大迭代次数时停止迭代。(二)当校验节点归一化满足概率p(g(k))达到译码成功阈值门限时停止迭代,此时译码成功;当校验节点归一化满足概率p(g(k))符合收敛阈值门限时停止迭代,此时码字达到收敛状态,后续迭代过程为无效迭代,无需继续进行迭代更新步骤。

[0043]

停止准则给定三个阈值参数t,β,n用于判断译码是否收敛。其中t表示译码成功阈值门限,β表示变化范围阈值门限,n表示判断收敛的连续周期阈值门限。

[0044]

停止准则具体实现过程为:首先判断当前迭代周期的校验节点归一化满足概率p(g(k))是否大于译码成功阈值门限t,当p(g(k))大于等于t时停止迭代译码。当p(g(k))小于t时,如果n个连续迭代周期内p(g(k))收敛,即|p(g(k))-p(g(k-1))|的幅值变化均在β之内,停止迭代译码。

[0045]

判断p(g(k))收敛的具体步骤为:比较当前迭代周期p(g(k))和前一迭代周期p(g(k-1))的值,若|p(g(k))-p(g(k-1))|小于变化范围阈值β则计数器加1,否则置为0,当连续n个周期的|p(g(k))-p(g(k-1))|均小于变化阈值时计数器等于n,此时判断该码字在迭代过程中达到收敛状态,停止迭代译码。

[0046]

步骤七,比特判决输出,得到译码后的码字序列,完成ldpc译码。

[0047]

当符合迭代停止准则时,对序列进行近似后验概率更新并判决输出码字,变量节点的近似后验概率为:

[0048][0049]cn'

∈n(vm)表示c

n'

属于与变量节点vm相连的所有校验节点集合,根据近似后验概率进行比特判决,当时,比特vm判决输出1,当时,比特vm判决输出0,以此得到译码后的码字序列,完成ldpc译码。

[0050]

本发明通过以上七个步骤,根据校验节点归一化满足概率的收敛性分析指导停止准则判断,并利用信道先验信息和校验矩阵信息得到码字的近似后验概率,实现模拟译码器的译码。根据步骤一和步骤二中ldpc译码及停止准则因子图模型,本发明能够进一步对因子图模型相对应的译码器硬件进行设计与分析,实现基于适用于模拟译码电路停止准则的译码器。

[0051]

有益效果:

[0052]

1、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,结合概率信号处理技术和cmos电路亚阈值特征,在概率域设计出与ldpc模拟译码电路完美耦合的最优停止准则和译码算法,能够同时具备模拟亚阈值信号处理的低功耗、高精度特性。

[0053]

2、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,能够降低传统译码停止准则中硬判决在模拟电路上的实现复杂度,并且减少传统译码算法中近似后验概率在每次迭代周期中的更新步骤,该特点降低系统功耗。

[0054]

3、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,在传统译码算法的基础上,通过分析模拟译码电路停止准则因子图中校验节点归一化满足概率进化图案的收敛性实时判断译码状态。在保证误码性能的基础上,本发明通过减小译码平均迭代次数降低系统处理时延,提高系统吞吐量。

[0055]

4、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,具有普适性,不受信噪比条件约束,即无需进行信道估计操作。

[0056]

5、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,通过检测进化图案的早期收敛减少不必要的迭代过程,降低译码器的动态功耗,且该停止准则译码方法同时适用于数字电路。

[0057]

6、本发明公开的一种基于概率计算的模拟译码电路停止准则的译码方法,在ldpc传统译码因子图模型信息双向传递的基础上,增添停止准则因子图节点,且信息单向传递给停止准则检验节点。该过程不影响正常译码过程,即停止准则图模型电路部分不影响原译码电路结构,此特点简化译码器整体电路的设计与实现过程。

附图说明

[0058]

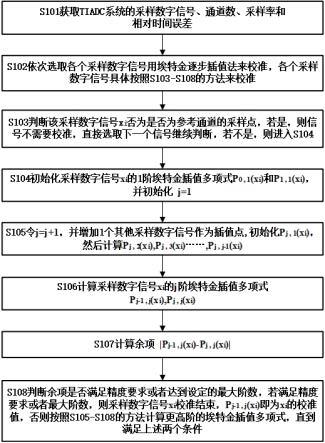

图1是本发明所述的一种基于概率计算的模拟译码电路停止准则的译码方法流程示意图;

[0059]

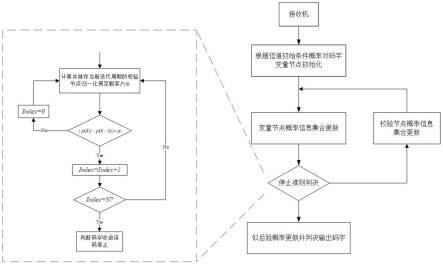

图2是本发明实施例所述的以概率图模型表征的迭代概率消息传递算法的ldpc译码因子图模型;

[0060]

图3是本发明实施例所述的基于概率计算的模拟译码电路停止准则的ldpc译码因子图模型;

[0061]

图4是本发明实施例所述的根据校验节点归一化满足概率判断不同信噪比条件下不同码型的分布统计;

[0062]

图5是本发明实施例所述的参考ccsds 131.1-0-1标准中(1024,512)码型,基于概率计算的模拟译码电路停止准则的ldpc译码的误码率曲线;

[0063]

图6是本发明实施例所述的参考ccsds 131.1-0-1标准中(1024,512)码型,基于概率计算的模拟译码电路停止准则的ldpc译码的平均迭代次数曲线。

具体实施方式

[0064]

为使本发明的上述目的、特征和优点更易于理解,以下结合附图和具体实施方式对其进行进一步的详细说明,本实施例为针对美国深空通信ccsds 131.1-0-1标准中ldpc码型的一种基于概率计算的模拟译码电路停止准则的ldpc译码方法,本实施例中系统参数如下表所示:

[0065]

参数详情每帧符号数512码率1/2打孔方式校验位末256位调制方式bpsk信道模型高斯白噪声译码器最大迭代次数100

[0066]

如图1所示,本实施例具体实施步骤如下:

[0067]

步骤一,针对ldpc模拟译码电路建立因子图模型。

[0068]

根据校验矩阵h

judge

构建具有校验约束关系的因子图模型g=(vns∪cns,ξ),其中vns代表变量节点集合,cns代表校验节点集合,ξ代表连接变量节点和校验节点的边集合。

[0069]

校验节点集合中每个cn对应校验矩阵的行维度,表示校验约束关系式中ki表示受该校验方程约束的码字索引;x表示符号值,取值为0或1;变量节点集合中每个vn对应校验矩阵的列维度,表示每比特信息;每个ξ对应校验矩阵h

judge

中1的所在位置,表示因子图中信息的更新与传递。

[0070]

校验矩阵h

judge

每行中1的个数表明对应校验方程约束码字的个数,且1在该行中的位置表明了所约束的码字位数,在因子图中该校验节点与被约束码字对应的变量节点相连接。同理,矩阵每列中值为1时表明该码字受此校验方程约束,在因子图中该变量节点与相对应校验节点连接。即当校验矩阵h

judge

中第m行第n列值为1时,表明第m个码字受第n个校验方程的约束,此时变量节点vnm与校验节点cnn在因子图上相连,迭代过程中节点更新的信息在该边上相互传递。

[0071]

ccsds校验矩阵是由循环子矩阵构成的准循环矩阵。针对ccsds标准中准循环校验矩阵,本实例由大小为256的子循环矩阵m以3

×

5拼接构造得到512

×

1280的校验矩阵h

judge

。该码型的因子图模型如图2所示。

[0072]

因子图的输入信息集合是vo=(v1,v2,...vk),vk表示码字信道似然概率p(yi|xi),其中,xi是发射符号,yi是接收符号,迭代过程完成后,因子图的输出信息集合是b=(b1,b2,...bk),bk表示码字的近似后验概率信息其中,bk表示符号值,y表示信道接收序列信息集合,表示信道传输过程中的未知参数;所示未知参数包括:定时同步信息、载波相位信息。

[0073]

步骤二,针对ldpc模拟译码电路停止准则建立因子图模型。

[0074]

在步骤一建立的ldpc译码因子图模型基础上,添加校验节点满足概率检测节点g=(g1,g2,...,gk)以及校验节点归一化满足概率统计节点g

ave

。

[0075]

校验节点cns=(c1,c2,...,ck)向与其相连的校验节点满足概率检测节点g=(g1,g2,...,gk)单向传递信息,其中gk表示第k个检测节点,ck表示第k个校验节点,即检测节点g的输入为:

[0076][0077]

其中,cn表示接收概率信息的校验节点,vm表示传递概率信息的变量节点,gi表示检测节点符号索引,即校验节点传递值为0或1,上标k表示译码迭代周期;h为校验矩阵约束,y为信道接收序列,p为概率。v

m'

∈n(cn)\gi表示v

m'

属于与校验节点cn相连的,但不包括变量节点gi的所有变量节点集合;表示对除了gi以外所有变量节点的函数求和,ic(cn)表示校验节点cn对应的校验约束,即:

[0078][0079]

δ为函数,表示为:当时δ=1,当时δ=0;当该不包含变量gi的校验约束成立时,除变量gi以外满足该约束的所有变量节点的符号信息乘积之和即为校验节点传递信息。

[0080]

检测节点g的输出为校验节点满足概率该式代表在已知信道接收序列y和校验矩阵h的条件下,经过k次迭代后校验方程检测节点输出校验关系gi为0的概率,即该校验方程成立的概率;所述概率表示为:

[0081][0082]gave

的输出为校验节点归一化满足概率p(g(k)),即对所有检测节点g的输出值做归一化:

[0083][0084]

其中,表示校验节点满足概率,num(c)表示校验节点数目。

[0085]

在传统ldpc译码因子图中,信息在变量节点和校验节点之间进行双向传递,本发明在此基础上添加校验节点满足概率检测节点g以及校验节点归一化满足概率统计节点g

ave

,且信息从校验节点单向传递给校验节点满足概率检测节点g。因此,停止准则因子图模

型和对应硬件的增加不影响传统ldpc译码过程,即能够通过在传统译码电路上直接添加停止准则相关电路实现译码器电路设计,有效降低电路实现复杂度和动态功耗。

[0086]

步骤三,初始化变量节点。

[0087]

根据高斯白噪声信道的概率分布,信道码字变量节点初始化信息为:

[0088][0089]

其中,xi表示接收序列的符号索引,取值为0或1,y

l

表示接收序列的幅值,l表示接收序列索引,σ2为信道噪声方差,表示第一次迭代周期中变量节点的更新信息。

[0090]

本实例针对ccsds标准中(1024,512)码型构造生成、校验矩阵构,为使码型符合所给定码率需对码字进行打孔,即在发射端对编码码字保留部分校验位不发送,并在接收端的相应码字位置处补0进行译码,本实施例选取校验位的后256位比特数据打孔,使其码率为1/2。

[0091]

步骤四,校验节点更新。

[0092]

校验节点向变量节点传递更新概率信息集合即在已知信道接收序列y和校验矩阵h的条件下,校验节点向变量节点传递符号xi为0或1的概率,校验节点更新信息为:

[0093][0094]

其中,cn表示接收概率信息的校验节点,vm表示传递概率信息的变量节点,xi表示信息符号索引,取值为0或1,v

m'

∈n(cn)\vm表示v

m'

属于与校验节点cn相连的,不包括变量节点vm的所有变量节点集合,~{vm}表示除了vm以外的所有变量节点集合,上标k表示译码迭代周期。校验节点信息代表除vm以外与校验节点cn相连的所有变量节点模二和为0的概率密度函数表征。

[0095]

步骤五,变量节点更新。

[0096]

变量节点向校验节点传递更新概率信息集合即在已知信道接收序列y和校验矩阵h的条件下,变量节点向校验节点传递符号xi为0或1的概率,根据校验约束关系和校验节点信息,变量节点更新信息集合为:

[0097][0098]

其中,vm表示传递概率信息的变量节点,cn表示接收概率信息的校验节点,c

n'

∈n(vm)\cn表示c

n'

属于与变量节点vm相连的,不包括校验节点cn的所有校验节点集合,上标k表示译码迭代周期;其中,α

mn

为参数,使得关系式满足

[0099]

步骤六,迭代停止准则判断:通过校验节点归一化满足概率统计节点g

ave

输出的校验节点归一化满足概率p(g(k))的收敛性对译码状态进行判断,符合迭代停止准则时停止译码,跳转到步骤七进行码字判决输出,否则跳转到步骤四继续进行迭代译码,直至符合迭代停止准则。

[0100]

因子图节点g

ave

输出校验节点归一化满足概率p(g(k)):

[0101][0102]

由校验节点归一化满足概率p(g(k))在迭代过程中的变化趋势可知,迭代译码过程中,当码字为可译码型时,校验节点归一化满足概率p(g(k))的值由0.5逐渐趋近于1并收敛。当码字由于自身误码率限制为不可译码型时,校验节点归一化满足概率p(g(k))的值可能在0.5到0.9之间任一区间内逐渐收敛,此时为收敛但不可译码型,或在0.5到0.9之间任一区间内持续震荡,此时为不收敛码型。根据不同信噪比下码型的分布统计知大多数码型为收敛码型。

[0103]

基于此,停止准则表示为:(一)当译码达到最大迭代次数时停止迭代。(二)当校验节点归一化满足概率p(g(k))达到译码成功阈值门限时停止迭代,此时译码成功;当校验节点归一化满足概率p(g(k))符合收敛阈值门限时停止迭代,此时码字达到收敛状态,后续迭代过程为无效迭代,无需继续进行迭代更新步骤。

[0104]

停止准则给定三个阈值参数t,β,n用于判断译码是否收敛。其中t表示译码成功阈值门限,β表示变化范围阈值门限,n表示判断收敛的连续周期阈值门限。

[0105]

停止准则具体实现过程为:首先判断当前迭代周期的校验节点归一化满足概率p(g(k))是否大于译码成功阈值门限t,当p(g(k))大于等于t时停止迭代译码。当p(g(k))小于t时,如果n个连续迭代周期内p(g(k))收敛,即|p(g(k))-p(g(k-1))|的幅值变化均在β之内,停止迭代译码。

[0106]

判断p(g(k))收敛的具体步骤为:比较当前迭代周期p(g(k))和前一迭代周期p(g(k-1))的值,若|p(g(k))-p(g(k-1))|小于变化范围阈值β则计数器加1,否则置为0,当连续n个周期的|p(g(k))-p(g(k-1))|均小于变化阈值时计数器等于n,此时判断该码字在迭代过程中达到收敛状态,停止迭代译码。

[0107]

步骤七,比特判决输出,得到译码后的码字序列,完成ldpc译码。

[0108]

当符合迭代停止准则时,对序列进行近似后验概率更新并判决输出码字,变量节点的近似后验概率为:

[0109][0110]cn'

∈n(vm)表示c

n'

属于与变量节点vm相连的所有校验节点集合,根据近似后验概率进行比特判决,当时,比特vm判决输出1,当时,比特vm判决输出0,以此得到译码后的码字序列,完成ldpc译码。

[0111]

该实施例码型的模拟译码电路停止准则的ldpc译码方法,根据校验节点归一化满足概率的收敛性分析判断停止准则,降低了传统停止准则中硬判决带来的译码器实现复杂度,减少迭代周期中的硬判决步骤从而降低了系统功耗,同时,通过减少无效迭代次数降低了译码处理时延,提高系统吞吐量。

[0112]

针对该实施例码型进行误码率和平均迭代次数的仿真分析,观察三个阈值参数的设置对译码性能的影响,部分参数仿真结果如图5和图6所示。如图5所示,基于该实施例停止准则的译码与基于传统校验式判决停止准则的译码所得误码率基本近似,当参数设置为

{t,n,β}={0.97,0.001,5}时,该实施例与传统译码误码率近似,保证了误码准确性。如图6所示,当中低信噪比时,基于该实施例停止准则的译码较传统停止准则译码的平均迭代次数降低了50%以上,极大降低了译码处理时延,进而提高系统吞吐量。

[0113]

针对该实施例码型,当阈值门限参数满足:t为0.96~0.99区间范围内,n为3~5,β为0.001~0.003区间范围内时译码器有较优性能。当译码成功阈值门限t小于0.96时,高信噪比条件下容易出现虚警造成误码率较大,t在0.96~0.99区间范围内,误码率性能较好且相差不大。连续周期阈值门限n在3~5区间范围内时,n越大平均迭代次数越大,但误码率性能越好,当β在0.001~0.003区间范围内时译码性能较好。

[0114]

以上所述的具体描述,对发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。