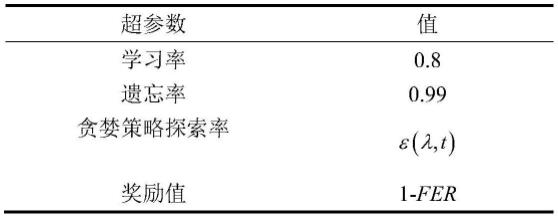

一种基于改进埃特金逐步插值法的tiadc系统采样时间误差校准方法

技术领域

1.本发明涉及时间交织adc时间误差校准技术领域,具体涉及一种基于改进埃特金逐步插值法的tiadc系统采样时间误差校准方法。

背景技术:

2.现代电子系统中的信号频率不断提高,信号越来越复杂,例如雷达一类的电子系统,要求模数转换器(adc)在满足一定采样率的同时还具有较高的分辨率,但目前adc受制造工艺水平的限制,单个adc的性能很难同时满足高速率和高采样率。因此时间交织模数转换器(tiadc)应运而生。

3.tiadc是一种并行交替型adc,利用多片采样速率较低的adc芯片,采用并行交替采样的方法,拼接出符合需求采样速率的ad采样系统,是一种相对容易实现且低廉的提升采样率的解决方案。由多片adc子芯片采用时间交织结构实现的采样系统,虽然采样速率能够满足要求,但芯片在生产过程中,受到制造工艺的制约,子通道芯片不可能做到完全一致,各通道采样时钟精度也很难满足tiadc的要求,因此会产生偏置失配误差、增益失配误差和时间失配误差,三种误差严重影响了tiadc的性能。在这三种失配误差中,时间失配误差的校准方法比其他两种失配误差复杂,因此,国内外的研究重点在于tiadc的时间失配误差校准方法,而在这些方法中,全数字域的后台校准方案是目前的研究热点,而在这种校准方案中,文献(杨扩军.tiadc系统校准算法研究与实现[d]. 电子科技大学,2015)提出一种利用拉格朗日插值滤波器来补偿时间失配误差的方法,该方法精度较高,适用于任意子通道数的tiadc系统,但是拉格朗日插值法的阶数与输入信号的频率成正相关,即随着输入信号的频率的提高,拉格朗日插值滤波器的阶数也要提高才能达到较好的校准效果。因此,拉格朗日插值滤波器的缺点在于其阶数是固定的,如果阶数太大,对于输入频率较低的信号来说计算量就过大,而如果阶数太小,频率较高的输入信号的校准效果会较差。

技术实现要素:

[0004]

针对以上问题,本发明提出一种基于改进埃特金逐步插值法的tiadc 系统采样时间误差校准方法,其特点是改进了埃特金逐步线性插值公式,将埃特金逐步线性插值公式应用到tiadc时间误差校准领域;在提高埃特金逐步插值法的阶数时,改进了所增加插值点的选取方法,提高了插值算法的精度。该方法优点在于可根据tiadc系统采样信号的频率和设定的精度要求自适应确定埃特金逐步插值法的阶数。本发明包括:

[0005]

获取tiadc系统的采样数字信号、通道数、采样率和相对时间误差;

[0006]

依次选取各个采样数字信号,按照以下方法校准:

[0007]

判断该采样数字信号否为是否为参考通道的采样点,若是,则信号不需要校准,直接选取下一个信号继续判断,若不是,则用埃特金逐步插值法校准该采样数字信号;

[0008]

所述埃特金逐步插值法校准采样数字信号的方法如下:

[0009]

步骤1、初始化j=1,并初始化采样数字信号xi的1阶埃特金插值多项式p

0,1

(xi)和p

1,1

(xi);

[0010]

步骤2、令j=j 1,并增加1个其他采样数字信号作为插值点,并初始化p

j,1

(xi),然后计算p

j,2

(xi),p

j,3

(xi)

……

p

j,j-1

(xi);

[0011]

步骤3、计算采样数字信号xi的j阶埃特金插值多项式p

j-1,j

(xi),p

j,j

(xi);

[0012]

步骤4、计算余项|p

j-1,l

(xi)-p

j,l

(xi)|;

[0013]

步骤5、判断余项是否满足精度要求或者达到设定的最大阶数,若满足精度要求或者最大阶数,则采样数字信号xi校准结束,p

j-1,j

(xi)即为xi的校准值,否则按照步骤2至步骤5的方法计算更高阶的埃特金插值多项式,直到满足上述两个条件。

[0014]

所述的埃特金逐步插值校准法的步骤1中,p

0,1

(xi)和p

1,1

(xi)按分别按式(1)和式(2)初始化:

[0015]

p

0,1

(xi)=xiꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

[0016]

p

1,1

(xi)=x

i 1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

[0017]

所述的埃特金逐步插值校准法的步骤2中,p

j,2

(xi),p

j,3

(xi)

……

p

j,j-1

(xi) 的计算方法如式(3)所示:

[0018]

p

j,l

(xi)=p

l-2,l-1

(xi) h

l-2,j

(p

l-2,l-1

(xi)-p

j,l-1

(xi))

ꢀꢀꢀ

(3)

[0019]

式(3)中,p

j,l

(xi)表示采样数字信号xi的l阶埃特金逐步插值多项式,下标j只是用于区分采用不同采样数字信号做插值运算所得到的校准值,没有其他特殊含义。因此式(3)表明,两个l-1阶插值多项式进行线性组合后就能得到一个l阶插值多项式。其中,按照埃特金逐步插值法的定义,系数h的计算公式如式(4)所示:

[0020][0021]

表示第个采样数字信号有时间误差的采样时刻,ni为第i个采样数字信号的理论采样时刻,这些采样时刻是无法准确获取的,因此无法按照埃特金逐步插值公式的定义求h

d,e

;将和ni按式(5)和式(6)展开:

[0022][0023]

mi=itsꢀꢀꢀ

(6)

[0024]

最终式(4)可以化简为式(7):

[0025][0026]

式(7)中,α表示相对时间误差。

[0027]

所述的埃特金逐步插值校准法的步骤2中,需要增加1个其他采样数字信号作为插值点,该插值点的选取方法如下:

[0028]

假设要计算采样数字信号xi的j阶埃特金逐步插值多项式,则需要增加第个采样数字信号做插值运算,并用该采样数字信号初始化 p

j,1

(xi):

[0029]

[0030]

按照这个方法增加插值点,能保证要校准的采样数字信号xi位于这些插值点的中点{

…

x

i-2

,x

i-1

,xi,x

i 1

,x

i 2

…

}(对于采样时刻来说是中点),并能提高埃特金逐步插值法的精度。

[0031]

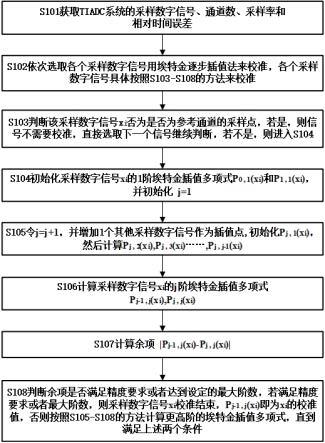

埃特金逐步插值法校准采样数字信号的计算流程可以参考图2。

附图说明

[0032]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0033]

图1是本发明一种基于改进埃特金逐步插值法的tiadc系统采样时间误差校准方法的总流程示意图;

[0034]

图2是本发明的埃特金逐步插值法校准每个采样数字信号时的计算流程示意图;

[0035]

图3是用本发明方法仿真时,得到的校准信号前(上图)和校准信号后(下图)的频谱图,其中输入数字信号归一化频率为0.05;

[0036]

图4是图3校准时,其中100个采样数字信号校准时所用阶数的曲线图;

[0037]

图5是用本发明方法仿真时,得到的校准信号前(上图)和校准信号后(下图)的频谱图,其中输入数字信号归一化频率为0.35;

[0038]

图6是图5校准时,其中100个采样数字信号校准时所用阶数的曲线图;

具体实施方式

[0039]

下面将结合本发明实施例中的附图,对本发明具体实施例中的技术方案进行清楚、完整地描述(以下描述中的各个埃特金插值多项式p

b,c

(xi),简记为 p

b,c

):

[0040]

s101假设已经获取了tiadc系统的采样率fs、采样数字信号 x0,x1,

……

,xk和通道数为m,假设各子通道的时间误差已经估计出,且为 0,δt1,

……

,δt

m-1

,设第0通道为参考通道,所以δt0=0,则相对时间误差为 0,a1,

……

,a

m-1

,其中a=δt/ts,ts为tiadc系统的采样间隔,且ts=1/fs;

[0041]

s102初始化i=0;

[0042]

s103选取第i个采样数字信号xi,假设本方法选取第0通道为参考通道,所以判断xi是否为第0通道的采样数字信号,若xi是第0通道的采样数字信号,则跳到s106;若xi不是第0通道的采样点,则进入s103;

[0043]

s104初始化p

0,1

=xi,p

1,1

=x

i 1

,初始化j=1;p

b,c

表示采样数字信号xi采用埃特金逐步插值法校准后的值,其中下标c表示阶数,下标b只是用于区分采用不同采样数字信号做插值运算所得到的校准值,没有其他特殊含义;

[0044]

s105令j=j 1,增加第个采样数字信号做插值运算,即并初始化p

j,1

:

[0045][0046]

初始化l=2;

[0047]

如果l》j-1,则进入s106,而当l≤j-1,则利用改进的埃特金逐步插值公式(2)计算p

j,l

:

[0048]

p

j,l

=p

l-2,l-1

h

l-2,j

(p

l-2,l-1-p

j,l-1

)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

[0049]

其中,按照埃特金逐步插值公式,h

d,e

的定义如式(3)所示:

[0050][0051]

继续累加l,计算p

j,l

,直到计算完p

j,2

,p

j,3

,

……

,p

j,j-1

。

[0052]

s106求更高阶的埃特金逐步插值法校准值p

j-1,j

和p

j,j

:

[0053]

p

j-1,j

=p

j-2,j-1

h

j-2,j-1

(p

j-2,j-1-p

j-1,j-1

)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(4)

[0054]

p

j,j

=p

j-2,j-1

h

j-2,j

(p

j-2,j-1-p

j,j-1

)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(5)

[0055]

s107计算插值多项式的误差(或者称为余项)p

err

:

[0056]

p

err

=|p

j-1,l-p

j,l

|

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(6)

[0057]

s108如果p

err

《ε或者j=j

max

时,则采样数字信号xi校准结束,最终xi的校准值yi等于:

[0058]

yi=p

j-1,j

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(7)

[0059]

令i=i 1,并按照s103至s108的方法校准下一个采样数字信号xi。

[0060]

如果不满足p

err

《ε或者j=j

max

的条件时,则按照s105至s108的方法增加插值点计算更高阶埃特金插值多项式,直到满足条件为止;

[0061]

按照以上步骤校准完所有采样数字信号后,输出校准后的数字信号 y0,y1,

……

,yk。

[0062]

图3是用本发明方法仿真时,得到的校准信号前(上图)和校准信号后(下图)的频谱图,其中输入数字信号归一化频率为0.05,采样数字信号点数为51200 个,ε=0.0002,j

max

=100,通道数为4,可以看出校准后的频谱图中,时间误差造成的杂散频谱已经基本消除;

[0063]

图4是图3校准时,其中100个采样数字信号校准时所用阶数的曲线图,其中,图片标题是这51200个采样数字信号校准时的平均阶数;

[0064]

图5是用本发明方法仿真时,得到的校准信号前(上图)和校准信号后(下图)的频谱图,其中输入数字信号归一化频率为0.35,采样数字信号点数为51200 个,ε=0.0002,j

max

=100,通道数为4,可以看出校准后的频谱图中,时间误差造成的杂散频谱已经降低了很多,基本消除;

[0065]

图6是图5校准时其中100个采样数字信号校准时所用阶数的曲线图,其中,图片标题是这51200个采样数字信号校准时的平均阶数,可以看出,当输入数字信号归一化频率为0.35的平均阶数比输入数字信号归一化频率为0.05时的平均阶数大约高了20,说明当输入信号的频率提高时,埃特金插值校准法所需要的阶数也会相应增加;

[0066]

以上所揭露的仅为本发明一种较佳实施例而已,当然不能以此来限定本发明之权利范围,本领域普通技术人员可以理解实现上述实施例的全部或部分流程,并依本发明权利要求所作的等同变化,仍属于发明所涵盖的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。