1.本发明涉及光子晶体逻辑门技术领域,尤其涉及一种可实现七种逻辑状态的准周期光子晶体全光逻辑门。

背景技术:

2.第三次科学技术革命之后,随着集成工艺技术的不断提高,半导体电子芯片的信息存储量和处理速度得到了巨大的提升。但是近几十年来,人们对设备接收、发送和处理信息的能力有了更高的要求,而半导体电子芯片的发热和传输损耗一直影响着其性能。而光子晶体是一种折射率呈周期性排列的人工微结构,其功耗低、性能稳定、发热量少的优点引起了研究人员的注意。

3.在未来的全光网络中,光交换、光计算和光传输是实现全光信号处理的核心单元,而它们都要以全光逻辑门为基础工作。因此,设计出尺寸紧凑、延迟时间短的全光逻辑结构是非常重要的。目前的全光逻辑门在逻辑转换时都需要改变光子晶体的基本结构和光功率,这在实际应用中是非常困难的。而且大部分的结构都只能实现七种基本逻辑门中的两三种,也导致了逻辑门功能不全面的问题。

技术实现要素:

4.针对现有技术中存在不足,本发明提供了一种可实现七种逻辑状态的准周期光子晶体全光逻辑门,在不改变光子晶体结构的情况下,可以产生七种不同的逻辑状态。

5.本发明是通过以下技术手段实现上述技术目的的。

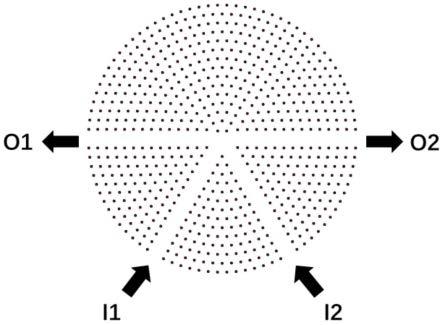

6.一种可实现七种逻辑状态的六重准周期光子晶体全光逻辑门,包括若干介质柱,若干所述介质柱呈六重准周期型排列,形成若干同心圆环,从所述逻辑门的中心逆时针沿着0

°

、180

°

、 240

°

和300

°

方向各删除一排介质柱构建出四条波导,其中两个所述波导作为输入端口,另外两个所述波导作为输出端口,所述输入端口的逻辑状态用bpsk技术控制。

7.进一步地,还包括两个相位调制器,两个输入端口分别对应一个所述相位调制器,通过所述相位调制器控制所述输入端口信号的相位。

8.进一步地,所述介质柱的材料为硅,背景介质是空气。

9.进一步地,所述介质柱折射率为3.48,空气的折射率为1。

10.进一步地,相邻两个同心圆环沿径向的距离为a,所述介质柱半径r=0.11*a。

11.进一步地,从所述逻辑门的中心逆时针沿着240

°

和300

°

的两个波导为两个输入端口。

12.进一步地,对于第一输入端口,输入光的相位为π视为逻辑0,输入光的相位为0视为逻辑1,对于第二输入端口,输入光的相位为-π/2视为逻辑0,输入光的相位为π/2视为逻辑 1,实现xor和xnor两种逻辑门

13.进一步地,对于第一输入端口,输入光的相位为π/2视为逻辑1,输入光的相位为0视为逻辑0;对于第二输入端口,输入光的相位为π视为逻辑1,输入光的相位为-π/2视为逻

辑0,实现nor和and两种逻辑门。

14.进一步地,对于第一输入端口,输入光的相位为π/2被视为逻辑1,输入光的相位为0 被视为逻辑0;对于第二输入端口,输入光的相位为π被视为逻辑1,输入光的相位为-π/2被视为逻辑0,实现or和nand两种逻辑门。

15.进一步地,对于第一输入端口持续出射相位为π的光,对于第二输入端口,输入光的相位为π/2被视为逻辑1,输入光的相位为-π/2被视为逻辑0,实现not逻辑门。

16.本发明的有益效果:

17.1)本发的准周期光子晶体全光逻辑门,进行逻辑转换时不需要改变光子晶体的结构,调控方法简单快速,能实现实时有效调控。

18.2)本发明的准周期光子晶体全光逻辑门,可将七种基本的逻辑门全部实现,且响应时间短、占地面积小。

附图说明

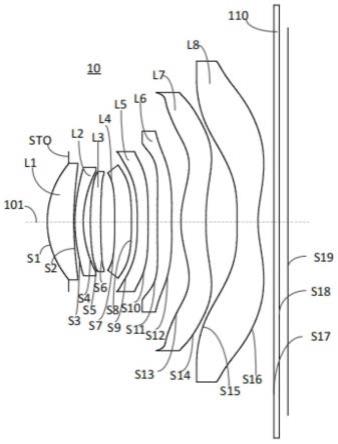

19.图1是sunflower型六重准周期光子晶体结构示意图;

20.图2为根据本发明实施例的可实现七种逻辑状态的准周期光子晶体全光逻辑门的结构示意图;

21.图3为根据本发明实施例的bpsk原理。

22.图4是xor和xnor逻辑门,(a)为x=y=0的电场分布图,(b)为x=0,y=1的电场分布图,(c)为x=1,y=0的电场分布图,(d)为x=y=1的电场分布图;

23.图5是nor和and逻辑门,(a)为x=y=0电场分布图,(b)为x=0,y=1电场分布图, (c)为x=1,y=0电场分布图,(d)为x=y=1的电场分布图;

24.图6是or和nand逻辑门,(a)为x=y=0电场分布图,(b)为x=0,y=1电场分布图, (c)为x=1,y=0电场分布图,(d)为x=y=1的电场分布图;

25.图7是not逻辑门,(a)为x=y=0,(b)为x=0,y=1的电场分布图;

26.图8是xor和xnor逻辑门,(a)为x=y=0、(b)为x=0,y=1、(c)为x=1,y=0、(d) 为x=y=1的归一化功率随时间的响应曲线;

27.图9是nor和and逻辑门,(a)为x=y=0、(b)为x=0,y=1、(c)为x=1,y=0、(d) 为x=y=1的归一化功率随时间的响应曲线;

28.图10是or和nand逻辑门,(a)为x=y=0、(b)为x=0,y=1、(c)为x=1,y=0、 (d)为x=y=1的归一化功率随时间的响应曲线;

29.图11是not逻辑门,(a)为x=y=0,(b)为x=0,y=1的归一化功率随时间的响应曲线。

具体实施方式

30.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

31.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“轴向”、“径向”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系

为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

32.下面首先结合附图具体描述根据本发明实施例的一种可实现七种逻辑状态的准周期光子晶体全光逻辑门。

33.请参照图1和图2,根据本发明实施例的一种可实现七种逻辑状态的准周期光子晶体全光逻辑门,包括若干介质柱和两个相位调制器,若干介质柱呈sunflower型六重准周期型排列,形成若干同心圆环,从所述逻辑门的中心逆时针沿着0

°

、180

°

、240

°

和300

°

方向各删除一排介质柱构建出四条波导,其中沿着240

°

和300

°

的两个波导作为输入端口,另外两个所述波导作为输出端口,两个输入端口各分别对应一个所述相位调制器,通过所述相位调制器用 bpsk技术控制所述输入端口信号的相位。

34.进一步的,本实施例中介质柱的材料为硅,背景介质是空气。折射率为3.48,空气的折射率为1。

35.sunflower型结构是一种非周期性晶体结构。这种类型的准晶结构有一个统一的坐标公式可以表示为:

[0036][0037][0038]

其中,α代表相邻两环之间的距离,m代表第一环中的介质柱个数,n代表圆环的序数, n代表某个介质柱在第n环的序数。本实施例中,α=661nm,介质柱半径为r=0.11*a,m=6, n=12。

[0039]

以下说明采用bpsk控制的原理:

[0040]

假设在第一输入端口1输入光,如图3(a)所示,两个输出端口都有相同输出。假设在第二输入端口2输入光,两个输出端口同样有光输出,如图3(b)所示。假设第一输入端口1和 2分别输入相位差为0或π的光,则两输出端口都有光输出,如图3(c)所示。假设第一输入端口1和2分别输入相位差为π/2的光,则光只从一个输出端口输出,如图3(d)所示。本发明将利用bpsk技术来设计逻辑门输出端口的逻辑状态由输出端口的光强度决定,输出端口的归一化强度大于60%设定为逻辑1,小于40%设定为逻辑0。

[0041]

本发明实施例的准周期光子晶体全光逻辑门,在不改变光子晶体结构的情况下,通过改变两个输入端口的初始相位,使不同相位的信号光在光子晶体内部发生干涉,从而可以产生七种不同的逻辑状态,并且两个输出端口可以分别实现两种不同的逻辑门。以下对可以实现的七种逻辑状态做出说明:

[0042]

若想实现xor和xnor两种逻辑门,对于第一输入端口1,输入光的相位为π被视为逻辑0,输入光的相位为0被视为逻辑1。对于第二输入端口2,输入光的相位为-π/2被视为逻辑0,输入光的相位为π/2被视为逻辑1。根据上述规定,逻辑门取决于以下相位条件:输入逻辑状态为“00”时,电场分布图如4a图所示。根据图8a,o1和o2端口的归一化强度分别为1%和210%,所以o1端口的逻辑值为0,o2端口的逻辑值为1;输入逻辑状态为“01”时,电场分布图

如图4b所示。根据图8b,o1和o2端口的归一化强度分别为150%和1%,所以o1端口的逻辑值为1,o2端口的逻辑值为0;输入逻辑状态为“10”时,电场分布图如图 4c所示。根据图8c,o1和o2端口的归一化强度分别为150%和1%,所以o1端口的逻辑值为1,o2端口的逻辑值为0;输入逻辑状态为“11”时,电场分布图如图4d所示。根据图8d, o1和o2端口的归一化强度分别为1%和210%,所以o1端口的逻辑值为0,o2端口的逻辑值为1。

[0043]

表1 xor和xnor函数bpsk信号的逻辑值

[0044][0045]

若想实现nor和and两种逻辑门,对于第一输入端口1,输入光的相位为π/2被视为逻辑1,输入光的相位为0被视为逻辑0。对于第二输入端口2,输入光的相位为π被视为逻辑1,输入光的相位为-π/2被视为逻辑0。根据上述规定,逻辑门取决于以下相位条件:输入逻辑状态为“00”时,电场分布图如图5a所示。根据图9a,o1和o2端口的归一化强度分别为150%和1%,所以o1端口的逻辑值为1,o2端口的逻辑值为0;输入逻辑状态为“01”时,电场分布图如图5b所示。根据图9b,o1和o2端口的归一化强度分别为30%和30%,所以 o1端口的逻辑值为0,o2端口的逻辑值为0;输入逻辑状态为“10”时,电场分布图如图5c 所示。根据图9c,o1和o2端口的归一化强度分别为30%和30%,所以o1端口的逻辑值为 0,o2端口的逻辑值为0;输入逻辑状态为“11”时,电场分布图如图5d所示。根据图9d,o1 和o2端口的归一化强度分别为1%和210%,所以o1端口的逻辑值为0,o2端口的逻辑值为1。

[0046]

表2 nor和and函数bpsk信号的逻辑值

[0047][0048]

若想实现or和nand两种逻辑门,对于第一输入端口1,输入光的相位为π/2被视为逻辑1,输入光的相位为0被视为逻辑0。对于第二输入端口2,输入光的相位为π被视为逻辑1,输入光的相位为-π/2被视为逻辑0。根据上述规定,逻辑门取决于以下相位条件:输入逻辑状态为“00”时,电场分布图如图6a所示。根据图10a,o1和o2端口的归一化强度分别为1%和210%,所以o1端口的逻辑值为0,o2端口的逻辑值为1;输入逻辑状态为“01”时,电场分布图如图6b所示。根据图10b,o1和o2端口的归一化强度分别为260%和260%,所以o1端口的逻辑值为1,o2端口的逻辑值为1;输入逻辑状态为“10”时,电场分布图如图 6c所示。根据图10c,o1和o2端口的归一化强度分别为260%和260%,所以o1端口的逻辑值为1,o2端口的逻辑值为1;输入逻辑状态为“11”时,电场分布图如图6d所示。根据图 10d,o1和o2端口的归一

化强度分别为150%和1%,所以o1端口的逻辑值为1,o2端口的逻辑值为0。

[0049]

表3 nand和or函数bpsk信号的逻辑值

[0050][0051]

若想实现not逻辑门,对于第一输入端口1持续出射相位为π的光,对于第二输入端口 2,输入光的相位为π/2被视为逻辑1,输入光的相位为-π/2被视为逻辑0。根据上述规定,逻辑门取决于以下相位条件:输入逻辑状态为“0”时,电场分布图如图7a所示。根据图11a, o2端口的归一化强度为210%,o2端口的逻辑值为1;输入逻辑状态为“1”时,电场分布图如图7b所示。根据图11b,o2端口的归一化强度为1%,o2端口的逻辑值为0。

[0052]

表4 not函数bpsk信号的逻辑值

[0053][0054]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

[0055]

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在不脱离本发明的原理和宗旨的情况下在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。