ipd高通滤波器

技术领域

1.本技术属于滤波器技术领域,尤其涉及一种ipd(integrated passive device,集成无源器件)高通滤波器。

背景技术:

2.滤波器的主要功能是抑制滤波器通带以外不需要的信号,并根据其频率分离信号。射频滤波器可以改变通过它们的正弦波形的幅度和相位,或者更简单的说,射频滤波器可以从信号中去除不需要的频率分量,并同时保留所需的频率分量。射频滤波器旨在用于处理整个无线电频谱中的信号,涵盖广播电台、电视、无线通信、科学研究和军事/国防领域。因此,滤波器的性能直接影响着整个无线通信系统的通信品质。

3.由于使用场合的特殊性,如常用与机载、弹载、车载电子、无线局域网、雷达收发系统、卫星定位等,用来导航、遥测等,所以质量轻、体积小等性能变得格外重要,因此滤波器的小型化设计也是人们一直追求和设计的热点。随着近年来无线通信系统的迅猛发展,通讯设备及元件也逐渐朝着微型化、高性能、高集成化和低成本的方向发展。

4.微波高通滤波器就是允许高频信号通过,而使低频信号衰减截止的微波器件。作为微波滤波器中的一种,高通滤波器同样有着广泛的应用。在现代的应用背景下,一般都要求高通滤波器具有较宽的带宽、较低的插损、较高的带外抑制和较高的端口反射。理论上,要达到高抑制就需要增加滤波器的阶数,这就必然会增加滤波器的插损,使得阻抗匹配比较困难,而且会增加滤波器的体积。要实现较大的带宽,就需要增大耦合量,使两个谐振腔靠的更近,但是也受到制作工艺的限制。

技术实现要素:

5.本技术的目的在于提供一种结构紧凑、宽带宽、高抑制、低插损和易加工的ipd高通滤波器。

6.本技术实施例的第一方面提供了一种ipd高通滤波器,包括有保护层、砷化镓基板、接地底板和接地铜柱,所述保护层和接地底板分别设置于所述砷化镓基板的上表面和下表面;所述砷化镓基板的上表面设有高通滤波电路,所述保护层覆盖在所述高通滤波电路之上,所述高通滤波电路包括:

7.输入端口,顶部裸露于所述保护层;

8.输出端口,顶部裸露于所述保护层;

9.n个滤波电容,分别通过传输线串联连接在所述输入端口和所述输出端口之间;

10.n-1个谐振电路,一一对应地连接到相邻两个所述滤波电容的传输线和接地焊盘之间,所述接地焊盘通过所述接地铜柱连接到所述接地底板,n≥4。

11.在其中一个实施例中,除与所述输入端口和所述输出端连接的两个滤波电容之外的其他滤波电容由n个的单体电容通过传输线串联构成,各所述单体电容的尺寸和容值一致,且所述单体电容的容值为所述滤波电容的容值的n倍,n≥2。

12.在其中一个实施例中,所述滤波电容为4个,所述串联谐振电路为3个。

13.在其中一个实施例中,所述串联谐振电路包括谐振电感和谐振电容,所述谐振电感和所述谐振电容串联在所述传输线和所述接地焊盘之间,该传输线用于连接两个相邻的所述滤波电容。

14.在其中一个实施例中,所述滤波电容和所述谐振电容为mim结构。

15.在其中一个实施例中,所述谐振电感为平面螺旋结构。

16.在其中一个实施例中,在所述输入端口和输出端口的两侧分别设有通过所述接地铜柱连接到所述接地底板的接地端口,所述接地端口的顶部裸露于所述保护层上。

17.在其中一个实施例中,所述输入端口和所述输出端口的尺寸为100um

×

100um,所述接地焊盘的尺寸为84um

×

84um。

18.在其中一个实施例中,所述ipd高通滤波器的尺寸为1.3mm

×

0.7mm

×

0.1mm。

19.在其中一个实施例中,所述ipd高通滤波器的通带频率为24ghz~40ghz。

20.本技术实施例与现有技术相比存在的有益效果是:本技术提供的ipd高通滤波器基于砷化镓基板设置,滤波电容和谐振电路规律排布,且将接地面板设置在基本的背面,使得整个高通滤波器具有结构紧凑、宽带宽、高抑制、低插损和易加工的特点。

附图说明

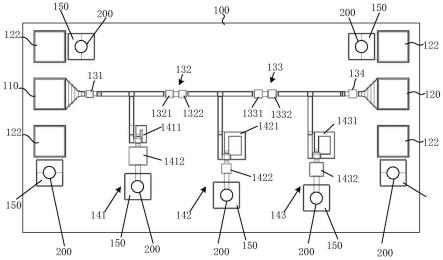

21.图1为本技术实施例提供的ipd高通滤波器的结构示意图;

22.图2为本技术实施例提供的ipd高通滤波器的仿真曲线图。

具体实施方式

23.为了使本技术所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

24.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

25.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

26.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

27.请参阅图1,本技术实施例提供了一种ipd高通滤波器,包括有保护层(图未示)、砷化镓基板100、接地底板(图未示)和接地铜柱200,保护层和接地底板分别设置于砷化镓基板100的上表面和下表面;砷化镓基板100的上表面设有高通滤波电路,保护层覆盖在高通滤波电路之上,高通滤波电路包括输入端口110、输出端口120、n个滤波电容(本示例中包括

滤波电容131、滤波电容132、滤波电容133和滤波电容134)、n-1个谐振电路(本示例中包括谐振电路141、谐振电路142和谐振电路143)。

28.输入端口110的顶部裸露于保护层;输出端口120的顶部裸露于保护层;进一步地,在输入端口110和输出端口120的两侧分别设有通过接地铜柱200连接到接地底板的接地端口122,接地端口122的顶部裸露于保护层上。输入端口110与两侧的接地端口122构成射频输入共面端,输出端口120与两侧的接地端口122构成射频输出共面端。

29.在另一个实施例中,输入端口110与其两侧接地端口122构成输入测试端口,输出端口120与其两侧接地端口122构成输出测试端口。用于实现器件的测试和调试。

30.滤波电容131、滤波电容132、滤波电容133和滤波电容134通过传输线串联连接在输入端口110和输出端口120之间;谐振电路141、谐振电路142和谐振电路143一一对应地连接到相邻两个滤波电容的传输线和接地焊盘150之间,接地焊盘150通过接地铜柱200连接到接地底板,n≥4,本示例中,n=4,构成7阶串联椭圆函数响应高通滤波器结构。在其他实施例中,n可以为5、6、7等。

31.可以理解的是,接地铜柱200贯穿砷化镓基板100的上表面和下表面,接地焊盘150覆盖在接地铜柱200的顶部。

32.基于砷化镓基板设置,滤波电容和谐振电路规律排布,且将接地面板设置在基本的背面,使得整个高通滤波器具有结构紧凑、宽带宽、高抑制、低插损和易加工的特点。

33.在其中一个实施例中,除与输入端口110和输出端连接的两个滤波电容131、滤波电容134之外的其他滤波电容132、滤波电容133,滤波电容132由单体电容1321和单体电容1322通过传输线串联构成,滤波电容133由单体电容1331和单体电容1332通过传输线串联构成。

34.各单体电容1321、单体电容1322、单体电容1331、单体电容1332的尺寸和容值一致,且单体电容1321、单体电容1322、单体电容1331、单体电容1332的容值为滤波电容的容值的n倍,n≥2。在其他实施例中,可以将所有滤波电容131、滤波电容132、滤波电容133和滤波电容134都采用n个的单体电容通过传输线串联构成,这样可以保证单体电容的加工精度,提升整体电路的带内性能稳定性。

35.在示例中,中间的滤波电容132由单体电容1321和单体电容1322串联构成,滤波电容133由单体电容1331和单体电容1 332串联构成。因为单体电容1321、单体电容1322、单体电容1331、单体电容1332的整体尺寸与电容值呈负相关,而单个滤波电容132或滤波电容133的尺寸与电容值正相关。因此,考虑到电容加工的制程能力以及加工精度,因此选择采用n个的容值较大的单体电容1321、单体电容1322、单体电容1331、单体电容1332串联的结构去替代一个容值较小的滤波电容132和滤波电容133,这样可以保证单体电容1321、单体电容1322、单体电容1331、单体电容1332的加工精度,提升整体电路的带内性能稳定性。

36.在其中一个实施例中,谐振电路141、谐振电路142和谐振电路143整体包括谐振电感1411、谐振电感1421、谐振电感1431、谐振电容1412、谐振电容1422和谐振电容1432,谐振电感1411和谐振电容1412串联在用于连接两个相邻的滤波电容131与滤波电容132之间的传输线和接地焊盘150之间,谐振电感1421和谐振电容1422串联在用于两个相邻的滤波电容132与滤波电容133之间的传输线和接地焊盘150之间,谐振电感1431和谐振电容1432串联在用于连接两个相邻的滤波电容133和滤波电容134之间的传输线和接地焊盘150之间。

用来大幅衰减高于预设频率之外的谐波,以构成7阶串联椭圆函数响应高通滤波器结构。

37.本实施例中,ipd高通滤波器包括第一滤波电容131、第一单体电容1321、第二单体电容1322、第三单体电容1331、第四单体电容1332、第四滤波电容134、第一串联谐振电路141、第二串联谐振电路142和第三串联谐振电路143。第一单体电容1321和第二单体电容1322通过传输线构成第二滤波电容132,第三单体电容1331和第四单体电容1332通过传输线构成第三滤波电容133。保证了单体电容1321、单体电容1322、单体电容1331、单体电容1332的加工精度,提升整体电路的带内性能稳定性。

38.第一串联谐振电路141包括第一谐振电感1411和第一谐振电容1412,第一滤波电容131和第一单体电容1321通过传输线连接第一谐振电感1411,第一谐振电感1411通过传输线与第一谐振电容1412串联,第一谐振电容1412通过传输线与接地焊盘150、接地铜柱200连接到接地面板实现接地。用来大幅衰减高于第一串联谐振电路141的预设频率之外的谐波。

39.第二串联谐振电路142包括第二谐振电感1421和第二谐振电容1422,第二单体电容1322和第三单体电容1331通过传输线连接第二谐振电感1421,第二谐振电感1421通过传输线与第二谐振电容1422串联,第二谐振电容1422通过传输线与接地焊盘150、接地铜柱200连接到接地面板实现接地。用来大幅衰减高于第二串联谐振电路141的预设频率之外的谐波。

40.第三串联谐振电路143包括第三谐振电感1431和第三谐振电容1432,第四单体电容1332和第四滤波电容130通过传输线连接第三谐振电感1431,第三谐振电感1431通过传输线与第三谐振电容1432串联,第三谐振电容1432通过传输线与接地焊盘150、接地铜柱200连接到接地面板实现接地。用来大幅衰减高于第三串联谐振电路141的预设频率之外的谐波。

41.通过三个串联谐振电路141、谐振电路142和谐振电路143设定了一个24ghz~40ghz之内的通带频率,可以将频率24ghz~40ghz的之外的谐波滤除。

42.其中,单体电容1321,单体电容1322,单体电容1331,单体电容1332,滤波电容131,滤波电容134,谐振电容1412,谐振电容1422,谐振电容1432可以采用无源电容器,比如mim(即金属-介质-金属)结构。这种mim结构器件制作工艺简单,成本低,且容值稳定,可靠性高。

43.其中,谐振电感1411,谐振电感1421,谐振电感1431为平面螺旋结构,三个谐振电感1411,谐振电感1421,谐振电感1431呈矩形的平面螺旋结构,且第一谐振电感1411的面积、第二谐振电感1421的电容面积、第三谐振电感1431的面积依次增大。这种mim结构器件成本低,容值稳定,且可靠性好。

44.其中,谐振电感1411,谐振电感1421,谐振电感1431可以采用铜箔布置而成。

45.其中,各个传输线也可以采用铜箔布置而成。

46.在一个示例中,输入端口110(焊盘)和输出端口120(焊盘)的尺寸为100um

×

100um,接地焊盘150的尺寸为84um

×

84um。ipd高通滤波器的尺寸为1.3mm

×

0.7mm

×

0.1mm。

47.可以理解的是,上述尺寸仅仅是作为其中一种示例,在具体制作时,可以将上述尺寸作为参照并进行适当修改。另外,本实施例中,ipd高通滤波器的通带频率为24ghz~40ghz。

48.本技术集总参数的设计方法来实现,结构简单,加工工艺成熟,完成一款通带频率为24ghz-40ghz的ipd高通滤波器的研制。

49.根据仿真结果图2所示,在24ghz~40ghz范围内:

50.s11<-15db,说明被反射回来的损耗小,达到阻抗匹配;

51.s21>-2db,说明其插入损耗小,传输特性良好,

52.在19.93ghz时:

53.s21<-20db,说明矩形系数好,具有陡峭的截止频率;

54.在dc~17.92ghz时:

55.s21<-40db,在dc~12.92ghz时,s21<-45db,具有高带外抑制特性。

56.高通滤波器芯片尺寸为1.3mm

×

0.7mm

×

0.1mm,达到小型化、高带外抑制、低插损、宽频带、小型化的目的。

57.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。