1.本公开的实施例涉及一种仲裁器及电子装置。

背景技术:

2.仲裁器(arbiter)是数字设计中非常常见的模块,应用也非常广泛。当有两个或两个以上的模块需要占用同一个资源的时候,需要由仲裁器来决定由哪一个模块来占有这个资源。仲裁器有多种使用场景,例如,在多个主设备同时访问同一个从设备的读地址、多个主设备同时访问同一个从设备的写地址、从不同的从设备同时返回多个写回应信号、从不同的从设备同时返回多个读数据、多个源试图同时访问同一个共享层时,都需要仲裁器完成仲裁,确定占用资源的对象。

技术实现要素:

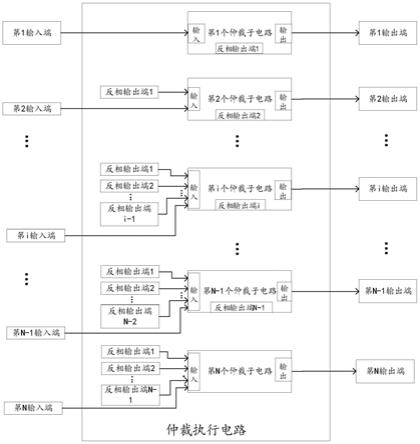

3.本公开至少一实施例提供一种仲裁器,包括仲裁执行电路,其中,所述仲裁执行电路包括n个输入端、与n个输入端一一对应的n个输出端和n个仲裁子电路,所述n个输入端按优先级从高到低的顺序依次包括第1输入端、第2输入端、......、第n-1输入端至第n输入端,所述n个仲裁子电路的输入端和输出端分别与所述n个输入端和所述n个输出端一一对应电连接;除与所述第n输入端电连接的第n个仲裁子电路之外的其他n-1个仲裁子电路还包括反相输出端,所述n-1个仲裁子电路中的每个仲裁子电路配置为对电连接的对应的输入端输入的信号进行反相处理并将反相处理结果通过所述每个仲裁子电路的反相输出端输出;与所述第1输入端电连接的第1个仲裁子电路还配置为将所述第1输入端输入的信号输出至n个输出端中对应的第1输出端;与第i输入端电连接的第i个仲裁子电路还和i-1个仲裁子电路的反相输出端电连接,其中,所述i-1个仲裁子电路为与所述第1输入端至第i-1输入端电连接的仲裁子电路,所述第i个仲裁子电路还被配置为对所述第i输入端输入的信号,以及所述i-1个仲裁子电路的反相输出端输出的信号进行逻辑与运算,将运算结果输出至所述n个输出端中与所述第i输入端对应的第i输出端,其中,n为大于等于2的整数,i为整数且依次取2至n。

4.例如,在本公开至少一实施例提供的仲裁器中,第1个仲裁子电路包括反相模块,所述反相模块与所述第1输入端和所述第1个仲裁子电路的反相输出端电连接,且配置为对所述第1输入端输入的信号进行反相处理,并将反相处理结果通过所述第1个仲裁子电路的反相输出端输出。

5.例如,在本公开至少一实施例提供的仲裁器中,所述第i个仲裁子电路包括反相模块和与运算模块,所述反相模块与所述第i输入端和所述第i个仲裁子电路的反相输出端电连接,且配置为对所述第i输入端输入的信号进行反相处理,并将反相处理结果通过所述第i个仲裁子电路的反相输出端输出;所述与运算模块与所述第i输出端、所述第i输入端、所述i-1个仲裁子电路的反相输出端电连接,且配置为对所述第i输入端输入的信号、以及所述i-1个仲裁子电路的反相输出端输出的信号进行与运算,将运算结果输出至所述第i输出

端。

6.例如,在本公开至少一实施例提供的仲裁器中,所述第n个仲裁子电路还和所述n-1个仲裁子电路的反相输出端电连接,所述第n个仲裁子电路还被配置为,对所述第n输入端输入的信号以及所述n-1个仲裁子电路的反相输出端输出的信号进行逻辑与运算,将运算结果输出至对应的第n输出端。

7.例如,在本公开至少一实施例提供的仲裁器中,所述第n个仲裁子电路包括与运算模块,所述与运算模块与所述第n输出端、所述第n输入端、所述n-1个仲裁子电路的反相输出端电连接,且配置为对所述第n输入端输入的信号、以及所述n-1个仲裁子电路的反相输出端输出的信号进行与运算,将运算结果输出至所述第n输出端。

8.例如,在本公开至少一实施例提供的仲裁器中,所述反相模块包括反相器,所述与运算模块包括至少一个与门。

9.例如,在本公开至少一实施例提供的仲裁器中,所述与运算模块包括一个与门,所述一个与门的输入端口的总数大于等于i,所述一个与门的输入端口分别与所述第i输入端和所述i-1个仲裁子电路的反相输出端电连接,所述一个与门的输出端口与所述第i输出端电连接。

10.例如,在本公开至少一实施例提供的仲裁器中,所述运算模块包括m级与运算单元,每级与运算单元包括至少一个与门;第一级与运算单元包括p1个与门,所述p1个与门的输入端口与所述第i输入端和所述i-1个仲裁子电路的反相输出端分别电连接;第j级与运算单元包括pj个与门,所述pj个与门的输入端口与第j-1级与运算单元包括的p

j-1

个与门的输出端口分别电连接;第m级与运算单元包括1个与门,所述1个与门的输出端口与所述第i输出端电连接;其中,p1、pj、p

j-1

、m和j均为正整数,j大于1小于等于m,m大于1。

11.例如,在本公开至少一实施例提供的仲裁器中,p1根据i和p1个与门中的各个与门的输入端口的数量确定;pj根据p

j-1

和pj个与门中的各个与门的输入端口的数量确定。

12.例如,在本公开至少一实施例提供的仲裁器中,每个仲裁子电路还包括至少一个缓冲器,所述第1个仲裁子电路中的缓冲器位于所述第1输入端和对应的输出端之间;所述第i个仲裁子电路中的缓冲器位于所述第i输入端和所述与运算模块之间。

13.例如,在本公开至少一实施例提供的仲裁器中,所述第n个仲裁子电路中的缓冲器位于所述第n输入端和所述与运算模块之间。

14.例如,在本公开至少一实施例提供的仲裁器中,所述n个输出端输出的信号组成独热编码形式。

15.例如,在本公开至少一实施例提供的仲裁器中,所述仲裁器还包括优先级选择电路,所述优先级选择电路配置为在选择信号的控制下,将n个请求信号按照从低位至高位或高位至低位的顺序分别输入至所述第1输入端、所述第2输入端、.....、所述第n-1输入端和所述第n输入端。

16.例如,在本公开至少一实施例提供的仲裁器中,所述选择信号包括第一选择信号和第二选择信号,所述n个请求信号构成二进制序列,响应于所述选择信号为所述第一选择信号,所述优先级选择电路配置为在所述第一选择信号的控制下,将所述n个请求信号按照低位至高位的顺序分别输入所述第1输入端至所述第n输入端,所述仲裁器的优先级顺序为低位优先级最高;响应于所述选择信号为所述第二选择信号,所述优先级选择电路配置为

在所述第二选择信号的控制下,将所述n个请求信号按照高位至低位的顺序分别输入所述第1输入端至所述第n输入端,所述仲裁器的优先级顺序为高位优先级最高。

17.例如,在本公开至少一实施例提供的仲裁器中,所述优先级选择电路包括分别与所述n个输入端对应的n个2路选择模块,每个2路选择模块包括第一输入端口、第二输入端口和输出端口,每个2路选择模块配置为在所述选择信号的控制下,将所述第一输入端口或所述第二输入端口中的信号从所述输出端口输出;其中,所述仲裁器还包括分别与所述n个输入端一一对应的n个信号输入端,所述n个请求信号按照从低位至高位或高位至低位的顺序分别输入第1个信号输入端至第n个信号输入端;其中,所述n个2路选择模块中的第k个2路选择模块的输出端口电连接第k输入端,所述第k个2路选择模块的第一输入端口电连接至所述n个信号输入端中的第k个信号输入端,所述第k个2路选择模块的第二输入端口电连接至所述n个信号输入端中的第n 1-k个信号输入端,其中,k为正整数且小于等于n。

18.例如,在本公开至少一实施例提供的仲裁器中,所述n个输出端输出的信号组成独热编码形式,所述仲裁器还包括转换电路,所述转换电路与所述n个输出端电连接,且配置为将所述n个输出端输出的独热编码形式信号转换为对应的二进制索引值。

19.本公开至少一实施例提供一种电子装置,该电子装置包括上述任一实施例的仲裁器。

附图说明

20.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

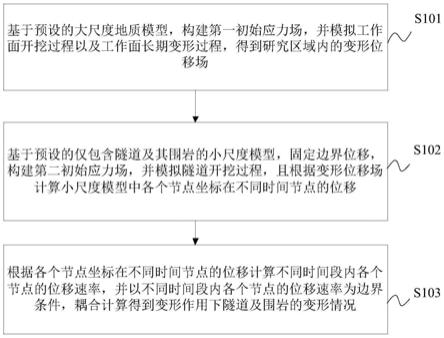

21.图1为本公开至少一实施例提供的仲裁器的结构示意图;

22.图2为本公开至少一实施例提供的第1个仲裁子电路的示意性结构图;

23.图3a为本公开至少一实施例提供的第i个仲裁子电路的示意性结构图;

24.图3b为本公开至少一实施例提供的第n个仲裁子电路的示意性结构图;

25.图4a为本公开至少一实施例提供的仲裁子电路的示意性结构图;

26.图4b为本公开至少一实施例提供的第n个仲裁子电路的示意性结构图;

27.图4c为本公开一实施例提供的仲裁子电路的示意性结构图;

28.图5为本公开至少一实施例提供的优先级选择电路的示意性结构图;

29.图6为本公开至少一实施例提供的仲裁器的模块示意图;

30.图7为本公开一实施例提供的仲裁器的示意性结构图。

具体实施方式

31.为了使得本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

32.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并

不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

33.为了保持本公开实施例的以下说明清楚且简明,本公开省略了部分已知功能和已知部件的详细说明。

34.仲裁器(arbiter)在电路中主要用于在多个源(source)同时发出请求时,根据相应的优先级来确定响应哪一个源。常用的仲裁器包括固定优先级仲裁器(fixed-priority)。

35.固定优先级仲裁器在多个源同时发起请求时,固定地设置一个源的优先级最高,即使在最高优先级被响应后,仍是最高优先级。也就是说,固定优先级仲裁器的多个源的优先级顺序保持不变。

36.例如,优先级顺序包括低位优先级最高(least sigificant bit,简称lsb)或高位优先级最高(most sigificant bit,简称msb)。例如,仲裁器的输入为多比特的请求信号,多比特请求信号包括n位(n为正整数)且构成二进制序列,每一位代表一个源(例如模块/逻辑电路)的请求信号。例如,若一个请求信号有效(例如比特位数值为1)代表对应的模块/逻辑电路请求占用资源,若一个请求信号无效(例如比特位数值为0)代表对应的模块/逻辑电路不请求占用资源。

37.例如,若优先级顺序为低位优先级最高,当n位中的第p位有效时,若第0位至第p-1位均无效,则仲裁器屏蔽第p 1位至第n-1位,选择响应第p位对应的源占用资源。例如,若优先级顺序为高位优先级最高,当n位中的第p位有效时,若第p 1位至第n-1位均无效,则仲裁器屏蔽第0位至第p-1位,选择响应第p位对应的源占用资源。这里,p为正整数且小于n。

38.例如,仲裁器输出的结果为独热编码形式的向量,也称热图向量(one-hot),热图向量为用于表示一项属性的特征向量,也就是同一时间向量中只有一个激活点。

39.表1示出了多比特请求信号以及多比特请求信号输入仲裁器后的热图向量形式的结果。

40.表1

41.多比特请求信号热图向量1111 11100000 00101010 10000000 10000000 01100000 0010

42.例如,若多比特请求信号包括8位,也即n=8,仲裁器的优先级顺序为低位优先级最高,比特位为1时表示该请求信号有效,比特位为0时表示该请求信号无效。如表1所示,当多比特请求信号为“1111 1110”时,第0位无效,第1位有效,则仲裁器选择响应第1位对应的源的请求,输出的热图向量形式的结果为“0000 0010”。针对多比特请求信号为“1010 1000”和“0000 0110”的原理相同,这里不再赘述。

43.目前,在实现仲裁器电路的过程中,大多采用较为复杂的逻辑实现,例如,在逻辑

综合过程中生成仲裁器对应的寄存器传输级(register transfer level,简称rtl)电路的逻辑实现复杂,使用的门级结构过多,导致综合后的面积过大。并且,由于综合结果复杂,在物理综合过程中生成的电路与寄存传输级电路中对应的部分也难以一一对应,增加了修改、调试的难度。

44.本公开至少一实施例提供了一种仲裁器,该仲裁器包括仲裁执行电路,其中,仲裁执行电路包括n个输入端、与n个输入端一一对应的n个输出端和n个仲裁子电路,n个输入端按优先级从高到低的顺序依次包括第1输入端、第2输入端、......、第n-1输入端至第n输入端,n个仲裁子电路分别与n个输入端和n个输出端一一对应电连接;除与第n输入端电连接的第n个仲裁子电路之外的其他n-1个仲裁子电路还包括反相输出端,n-1个仲裁子电路中的每个仲裁子电路配置为对电连接的对应的输入端输入的信号进行反相处理并将反相处理结果通过每个仲裁子电路的反相输出端输出;与第1输入端电连接的第1个仲裁子电路还配置为将第1输入端输入的信号输出至n个输出端中对应的输出端;与第i输入端电连接的第i个仲裁子电路还和i-1个仲裁子电路的反相输出端电连接,其中,i-1个仲裁子电路为与第1输入端至第i-1输入端电连接的仲裁子电路,第i个仲裁子电路还被配置为,对第i输入端输入的信号以及i-1个仲裁子电路的反相输出端的信号进行逻辑与运算,将运算结果输出至n个输出端中与第i输入端对应的第i输出端,其中,n为大于等于2的整数,i为整数且依次取2至n。

45.本公开至少一实施例提供了仲裁器的具体电路实现结构,这种实现方式极大地简化了仲裁器的电路实现,有利于后端的时序收敛。

46.下面结合附图,具体说明本公开至少一实施例提供的仲裁器的电路结构。

47.图1为本公开至少一实施例提供的仲裁器的结构示意图。

48.如图1所示,仲裁器包括仲裁执行电路。

49.例如,仲裁执行电路101包括n个输入端,如图1所示,n个输入端按优先级从高到低的顺序依次包括第1输入端、第2输入端、......、第n-1输入端至第n输入端。

50.例如,上述实施例的仲裁器实现为固定优先级仲裁器,第1输入端的优先级最高,若第1输入端的信号有效,则优先响应第1输入端对应的模块/逻辑电路的资源占用请求;当第1输入端的信号无效,第2输入端的信号有效时,优先响应第2输入端对应的模块/逻辑电路的资源占用请求,以此类推。

51.例如,在图1中,n个输入端的排列顺序按照第1输入端至第n输入端的顺序依次排列,但本公开不限于此,可以根据需要设置n个输入端的排列顺序。

52.例如,仲裁执行电路包括与n个输入端一一对应的n个输出端,如图1所示,n个输出端包括与第1输入端对应的第1输出端、与第2输入端对应的第2输出端、......、与第n-1输入端对应的第n-1输出端,以及与第n输入端对应的第n输出端。

53.例如,如图1所示,仲裁执行电路包括n个仲裁子电路,分别为第1个仲裁子电路、第2个仲裁子电路、...、第i个仲裁子电路、...、第n-1个仲裁子电路、第n个仲裁子电路。这里,i为正整数且大于2小于n-1。

54.需要说明的是,图1中为便于描述设置了至少5个仲裁子电路,在实践中最少可以设置两个仲裁子电路,也即n大于等于2。

55.例如,n个仲裁子电路分别与n个输入端和n个输出端一一对应电连接。例如,如图1

所示,第1个仲裁子电路与第1输入端和第1输出端电连接,第2个仲裁子电路与第2输入端和第2输出端电连接,以此类推。

56.例如,除与第n输入端电连接的第n个仲裁子电路之外的其他n-1个仲裁子电路还包括反相输出端。如图1所示,第1个仲裁子电路至第n-1个仲裁子电路均包括反相输出端,例如,第1个仲裁子电路包括反相输出端1,第2个仲裁子电路包括反相输出端2,以此类推。

57.例如,n-1个仲裁子电路(第1个仲裁子电路至第n-1个仲裁子电路)中的每个仲裁子电路配置为对电连接的对应的输入端输入的信号进行反相处理,并将反相处理结果通过每个仲裁子电路的反相输出端输出。例如,以第i个仲裁子电路为例,第i个仲裁子电路配置为对电连接的第i输入端输入的信号进行反相处理,将反相结果通过第i个仲裁子电路的反相输出端i输出。

58.例如,与第1输入端电连接的第1个仲裁子电路还配置为将第1输入端输入的信号输出至n个输出端中对应的输出端,例如,这里对应的输出端为第1输出端,也即第1个仲裁子电路还配置为将第1输入端输入的信号输出至第1输出端。

59.例如,与第i输入端电连接的第i个仲裁子电路还和i-1个仲裁子电路的反相输出端电连接,其中,i-1个仲裁子电路为与第1输入端至第i-1输入端电连接的仲裁子电路,第i个仲裁子电路还被配置为对第i输入端输入的信号,以及i-1个仲裁子电路的反相输出端的信号进行逻辑与运算,将运算结果输出至n个输出端中与第i输入端对应的第i输出端。

60.例如,如图1所示,第1个仲裁子电路的反相输出端标记为反相输出端1,第2个仲裁子电路的反相输出端标记为反相输出端2,...,第i个仲裁子电路的反相输出端标记为反相输出端i,以此类推。

61.例如,如图1所示,针对第2个仲裁子电路,第2个仲裁子电路不仅与第2输入端电连接,还与第1个仲裁子电路的反相输出端1电连接。第2个仲裁子电路配置为对第2输入端输入的信号、反相输出端1输出的第1输入端输入的信号的反相信号进行与运算,将与运算的结果输出至第2输出端。

62.例如,如图1所示,针对第i个仲裁子电路,第i个仲裁子电路不仅与第i输入端电连接,还与第1个仲裁子电路的反相输出端1、第2个仲裁子电路的反相输出端2、...、第i-1个仲裁子电路的反相输出端i-1电连接。

63.例如,第i个仲裁子电路配置为对第i输入端输入的信号、反相输出端1输出的第1输入端输入的信号的反相信号、反相输出端2输出的第2输入端输入的信号的反相信号、...、反相输出端i-1输出的第i-1输入端输入的信号的反相信号进行与运算,将与运算的结果输出至第i输出端。

64.例如,如图1所示,针对第n个仲裁子电路,第n个仲裁子电路还和n-1个仲裁子电路的反相输出端电连接。第n个仲裁子电路还被配置为,对第n输入端输入的信号以及n-1个仲裁子电路的反相输出端输出的信号进行逻辑与运算,将运算结果输出至对应的第n输出端。

65.例如,第1个仲裁子电路包括反相模块,反相模块配置为对第1输入端输入的信号进行反相处理,并将反相处理结果通过第1个仲裁子电路的反相输出端输出。

66.例如,反相模块包括反相器。

67.图2为本公开至少一实施例提供的第1个仲裁子电路的示意性结构图。

68.如图2所示,虚线框的部分为反相模块,反相模块具体实现为1个反相器,反相器的

第一端与第1输入端电连接,反相器的第二端与反相输出端1电连接。例如,反相器配置为对第1输入端输入的信号进行反相处理,将反相处理结果通过反相输出端1输出。

69.例如,如图2所示,第1个仲裁子电路还可以包括2个缓冲器。例如,第1个仲裁子电路中的2个缓冲器位于第1输入端和对应的输出端(也即第1输出端)之间。例如,2个缓冲器配置为调整电路时序。

70.当然,根据电路时序需要,还可以设置更多或更少的缓冲器,本公开对此不作限制。

71.图3a为本公开至少一实施例提供的第i个仲裁子电路的示意性结构图。例如,这里i可以取2至n-1,也即图3a示出了仲裁执行电路中的第2个仲裁子电路至第n-1个仲裁子电路的电路示意性结构。

72.例如,如图3a所示,第i个仲裁子电路包括由虚线框限定的反相模块和与运算模块。

73.例如,反相模块与第i输入端和第i个仲裁子电路的反相输出端(图3a中的反相输出端i)电连接,且配置为对第i输入端输入的信号进行反相处理,并将反相处理结果通过第i个仲裁子电路的反相输出端输出。

74.例如,如图3a所示,反相模块实现为反相器。反相器的第一端与第i输入端电连接,反相器的第二端与反相输出端i电连接。

75.例如,与运算模块与第i输出端、第i输入端、i-1个仲裁子电路的反相输出端(图3a中的反相输出端1、反相输出端2至反相输出端i-1)电连接,且配置为对第i输入端输入的信号、以及i-1个仲裁子电路的反相输出端输出的信号进行与运算,将运算结果输出至第i输出端。

76.例如,与运算模块包括至少一个与门,这些与门用于完成与运算。

77.例如,若与门的输入端口数量大于等于i,此时使用一个与门即可完成i个信号(第i输入端输入的信号、以及i-1个仲裁子电路的反相输出端输出的信号)的与运算。

78.例如,如图3a所示,与运算模块包括一个与门,该与门的输入端口的总数大于等于i,该与门的输入端口分别与第i输入端和i-1个仲裁子电路的反相输出端电连接,该与门的输出端口与第i输出端电连接。

79.例如,在一些实施例中,若与门的输入端口数量小于i,或者说,需要进行仲裁的输入端的数量n较大,此时,一些仲裁子电路中的与运算模块包括多个与门,多个与门构成m级与运算单元,每级与运算单元包括至少一个与门,由此完成i个信号的与运算。这里,m为大于1的正整数。

80.图3b为本公开至少一实施例提供的第n个仲裁子电路的示意性结构图。

81.例如,如图3b所示,第n个仲裁子电路包括由虚线框限定的与运算模块。

82.例如,与运算模块与第n输出端、第n输入端、n-1个仲裁子电路的反相输出端(图3b中的反相输出端1、反相输出端2至反相输出端n-1)电连接,且配置为对第n输入端输入的信号、以及n-1个仲裁子电路的反相输出端输出的信号进行与运算,将运算结果输出至第n输出端。

83.例如,与运算模块包括至少一个与门,这些与门用于完成与运算。

84.例如,若与门的输入端口数量大于等于n,此时使用一个与门即可完成n个信号(第

n输入端输入的信号、以及n-1个仲裁子电路的反相输出端输出的信号)的与运算。

85.例如,如图3b所示,与运算模块包括一个与门,该与门的输入端口的总数大于等于n,该与门的输入端口分别与第n输入端和n-1个仲裁子电路的反相输出端电连接,该与门的输出端口与第n输出端电连接。

86.例如,在一些实施例中,若与门的输入端口数量小于n,此时,一些仲裁子电路中的与运算模块包括多个与门,多个与门构成m级与运算单元,每级与运算单元包括至少一个与门,由此完成n个信号的与运算。这里,m为大于1的正整数。

87.图4a为本公开至少一实施例提供的仲裁子电路的示意性结构图。

88.例如,如图4a所示,该仲裁子电路包括与运算模块和反相模块。

89.例如,反相模块与图3a所示的仲裁子电路的结构、连接关系相同,这里不再赘述。

90.例如,与运算模块包括m级与运算单元。

91.如图4a所示,第一级与运算单元包括p1个与门,分别为与门a_1、...、与门a_p1,p1个与门的输入端口与第i输入端和i-1个仲裁子电路的反相输出端分别电连接。

92.例如,在图4a中,k表示与门的输入端口数量,k为大于等于2、小于i的正整数,p1为正整数。需要说明的是,在图4a中,为描述方便,设置每个与门的输入端口数量相同且均为k,但在实践过程中,也可以根据需要选择不同输入端口数量的与门,电路实现原理相同。

93.例如,p1根据i和p1个与门中的各个与门的输入端口的数量确定。例如,i=16,选择4输入与门构建第一级与运算单元,则此时p1=4。

94.例如,第j级与运算单元包括pj个与门,pj个与门的输入端口与第j-1级与运算单元包括的p

j-1

个与门的输出端口分别电连接。这里,j为正整数且j大于1小于等于m。

95.例如,pj根据p

j-1

和pj个与门中的各个与门的输入端口的数量确定。例如,p

j-1

=4,选择2输入与门构建第j级与运算单元,则此时pj=2。

96.例如,若第j级与运算单元包括pj个与门,若pj个与门的输入端口总数大于p

j-1

,则多余的输入端口连接高电平信号(例如对应常数1)即可。

97.例如,第i个仲裁子电路中与运算模块中的与运算单元的级数例如,第i个仲裁子电路中与运算模块中的与运算单元的级数这里,k表示与门的输入端口数量,表示向上取整函数。因此,与运算模块中的级数最多为在电路设计的单元库提供多输入端口与门的情况下(例如6输入与门或8输入与门),可以极大地减少组合逻辑的级数,简化电路实现,也有利于后端设计过程中的时序收敛。

98.例如,以图4a为例,在j=2时,第2级与运算单元包括p2个与门,分别为图4a中的b_1、...、b_p2,p2为正整数。例如,p2个与门的输入端口与第1级与运算单元包括的p1个与门的输出端口分别电连接,因此,p2个与门的输入端口总数应当大于等于p1。

99.如图4a所示,第m级与运算单元包括1个与门,该1个与门的输出端口与第i输出端电连接。

100.例如,如图3a和图4a所示,第i个仲裁子电路还包括1个缓冲器,第i个仲裁子电路中的缓冲器位于第i输入端和与运算模块(也即图3a中的与门或图4a中的第一级与运算单元)之间。例如,缓冲器配置为调整电路的时序。

101.图4b为本公开至少一实施例提供的第n个仲裁子电路的示意性结构图。

102.例如,如图4b所示,该仲裁子电路包括与运算模块。

103.例如,与运算模块包括m级与运算单元。

104.如图4b所示,第一级与运算单元包括p1个与门,分别为与门a_1、...、与门a_p1,p1个与门的输入端口与第n输入端和n-1个仲裁子电路的反相输出端分别电连接。

105.例如,p1根据n和p1个与门中的各个与门的输入端口的数量确定。例如,n=16,选择8输入与门构建第一级与运算单元,则此时p1=2。

106.例如,第j级与运算单元包括pj个与门,pj个与门的输入端口与第j-1级与运算单元包括的p

j-1

个与门的输出端口分别电连接。这里,j为正整数且j大于1小于等于m。

107.例如,pj根据p

j-1

和pj个与门中的各个与门的输入端口的数量确定。

108.例如,若第j级与运算单元包括pj个与门,若pj个与门的输入端口总数大于p

j-1

,则多余的输入端口连接高电平信号(例如对应常数1)即可。

109.如图4b所示,第m级与运算单元包括1个与门,该1个与门的输出端口与第n输出端电连接。

110.图4b中的第二级与运算单元至第m级与运算单元的具体结构、连接关系可以参考图4a的相关描述,这里不再赘述。

111.例如,如图3b和图4b所示,第n个仲裁子电路还包括1个缓冲器,第n个仲裁子电路中的缓冲器位于第n输入端和与运算模块(也即图3b中的与门或图4b中的第一级与运算单元)之间。例如,缓冲器配置为调整电路的时序。图4c为本公开一实施例提供的仲裁子电路的示意性结构图。

112.例如,i=8,k=4,也即该仲裁子电路为n个仲裁子电路中的第8个仲裁子电路,该仲裁子电路与前7个仲裁子电路的反相输出端(也即反相输出端1至反相输出端7)以及第8输入端电连接。该仲裁子电路的与运算模块包括2级与运算单元,每级与运算单元包括的与门的输入端口数量均为4。

113.如图4c所示,第一级与运算单元包括2个与门,与门a_1和与门a_2,也即p1=2。

114.与门a_1的四个输入端口与反相输出端1、反相输出端2、反相输出端3、反相输出端4电连接,且配置为对第1输入端输入的信号的反相信号、第2输入端输入的信号的反相信号、第3输入端输入的信号的反相信号、第4输入端输入的信号的反相信号进行与运算,得到第一中间结果。

115.与门a_2的四个输入端口与反相输出端5、反相输出端6、反相输出端7、第8输入端进行相连,且配置为对第5输入端输入的信号的反相信号、第6输入端输入的信号的反相信号、第7输入端输入的信号的反相信号、第8输入端输入的信号进行与运算,得到第二中间结果。

116.如图4c所示,第二级与运算单元包括1个与门,与门b_1,也即p2=1。

117.与门b_1与第一级与运算单元中的与门a_1、与门a_2的输出端口电连接,且配置为对第一中间结果和第二中间结果进行与运算,将与运算结果输出至第8输出端。

118.例如,若与门b_1也包括4个输入端口,则除和与门a_1和与门a_2的输出端口电连接的两个端口之外,剩余两个端口连接高电平信号即可。

119.关于第8个仲裁子电路的反相模块、反相输出端8的介绍参考前述内容,这里不再赘述。

120.如上所述,本公开至少一实施例提供的仲裁器,使用多个与门构建至少一级与运算单元实现与运算,利用与门、反相器、缓冲器等组合逻辑器件实现电路,简化了电路结构。在电路设计的单元库提供多输入端口与门的情况下(例如6输入与门或8输入与门),可以极大地减少组合逻辑的级数,简化电路实现,也有利于后端设计过程中的时序收敛。

121.此外,该电路结构也易于在不同综合阶段将电路元件进行对应。相对于逻辑综合阶段得到的寄存器传输级描述(register transfer level,简称rtl)电路,物理综合阶段增加了一些缓冲器用于调整电路时序,但由于电路整体结构得到简化并由一些组合逻辑器件组成,在物理综合阶段不会对rtl电路不会进行过多调整,易于得到一对一的元件映射关系,便于电路调试。

122.例如,n个输出端输出的信号组成独热编码形式。也就是说,n个输出端输出的信号中只有一位有效,该有效位指示了仲裁器响应的模块或逻辑电路。

123.例如,参考图1至图4c,第1个仲裁子电路将第1输入端输入的信号通过第1输出端输出,并且将第1输入端输入的信号的反相信号通过反相输出端1输出至第2个仲裁子电路至第n个仲裁子电路。因此,若第1输入端输入的信号有效(例如为“1”),则第1输出端输出有效信号,第2个仲裁子电路至第n个仲裁子电路由于接收了有效信号的反相信号(也即无效信号,例如“0”)并进行与运算,全部输出无效信号。

124.同理,若第1输入端输入的信号为无效信号,第2输入端输入的信号为有效信号,则第2个仲裁子电路对第1输入端输入的信号的反相信号和第2输入端输入的信号进行与运算,输出有效信号至第2输出端;第3个仲裁子电路至第n个仲裁子电路由于接收了第2输入端输入的有效信号的反相信号(也即无效信号)并进行与运算,全部输出无效信号。

125.因此,优先级高的输入端电连接的仲裁子电路在输入端输入的信号有效时,能够屏蔽低于该优先级的所有输入端的输入信号的输出,由此,实现高优先级的请求信号优先被响应。

126.例如,在一些实施例中,仲裁器还包括转换电路。转换电路与n个输出端电连接,且配置为将n个输出端输出的独热编码形式信号转换为对应的二进制索引值。该二进制索引值即为独热编码形式信号对应的指数级的索引值(index)。

127.例如,参考表1,若n个输入端输入的信号为“1010 1000”,此时,n个输出端输出的信号组成的独热编码形式信号为“00001000”。对该信号进行转换得到的二进制索引值为“011”,表示索引值为3,n个输出端中的第4个输出端输出有效信号。

128.例如,二进制索引值的长度例如,转换电路实现为编码器形式,配置为将n位独热编码形式的信号转换为m位的索引值。例如,若n=8,则m=3,此时转换电路可以使用8-3编码器实现。

129.例如,在一些实施例中,可以通过电路连线将多比特请求信号按照优先级从高到低的顺序输入n个输入端。此时,仲裁器在电路设计时需要预先规定仲裁器的优先级顺序。如果优先级顺序在使用过程中需要改变,此时是无法进行调整的。

130.本公开至少一实施例提供的仲裁器还包括优先级选择电路,该优先级选择电路配置为在选择信号的控制下,将n个请求信号按照从低位至高位或者从高位至低位顺序分别输入至第1输入端、第2输入端、.....、第n-1输入端和第n输入端。

131.因此,本公开至少一实施例提供的仲裁器的优先级顺序动态可调,在实际使用过

程中可以给定不同的选择信号选择不同的优先级顺序,例如优先级顺序可以为低位优先级最高或高位优先级最高,从而将n个请求信号从低位至高位(对应低位优先级最高)或高位至低位(对应高位优先级最高)的顺序分别输入第1输入端、第2输入端、.....、第n-1输入端和第n输入端。如前所述,第1输入端、第2输入端、.....、第n-1输入端和第n输入端本身已按照是按照优先级顺序进行排列。本公开少一实施例提供的仲裁器更加灵活,能够动态选择优先级顺序。

132.例如,n个请求信号构成二进制序列,该二进制序列包括从最低位至最高位排列的n位,例如,n个请求信号构成的二进制序列为“1111 1110”,则最右侧的“0”为最低位,最左侧的“1”为最高位。

133.例如,如前所述,固定优先级的仲裁器通常包括两种优先级顺序,低位优先级最高或高位优先级最高。例如,选择信号包括第一选择信号和第二选择信号,第一选择信号和第二选择信号不同。例如,第一选择信号用于选择优先级顺序为低位优先级最高(也即优先级顺序为lsb),第二选择信用于选择优先级顺序为高位优先级最高(也即优先级顺序为msb)。

134.例如,响应于选择信号为第一选择信号,优先级选择电路配置为在第一选择信号的控制下,将n个请求信号按照从低位至高位的顺序分别输入第1输入端至第n输入端,例如,此时仲裁器的优先级顺序为低位优先级最高;响应于选择信号为第二选择信号,优先级选择电路配置为在第二选择信号的控制下,将n个请求信号按照高位至低位的顺序分别输入第1输入端至第n输入端,例如,此时仲裁器的优先级顺序为高位优先级最高。

135.例如,第一选择信号可以是“0”,第二选择信号可以是“1”。

136.当然,本公开不限于此,第一选择信号和第二选择信号的形式,以及第一选择信号和第二选择信号与优先级顺序的关系可以根据需要具体指定。

137.例如,优先级选择电路包括分别与n个输入端一一对应的n个2路选择模块,每个2路选择模块包括第一输入端口、第二输入端口和输出端口,每个2路选择模块配置为在选择信号的控制下,将第一输入端口或第二输入端口中的信号从输出端口输出。例如,当2路选择模块接收到第一选择信号时,将第一输入端口的信号从输出端口输出,当2路选择模块接收到第二选择信号时,将第二输入端口的信号从输出端口输出。

138.例如,所述仲裁器还包括分别与n个输入端一一对应的n个信号输入端,n个请求信号按照从低位至高位或高位至低位的顺序分别输入第1个信号输入端至第n个信号输入端。

139.例如,n个2路选择模块中的第k个2路选择模块的第一输入端口与n个请求信号中沿从低位到高位顺序排列的第k个请求信号的信号输入端电连接,第k个2路选择模块的第二输入端口与n个请求信号中沿从高位到低位顺序排列的第k个请求信号的信号输入端电连接,这里,k为正整数且小于等于n。

140.例如,n个2路选择模块中的第k个2路选择模块的输出端口电连接第k输入端,第k个2路选择模块的第一输入端口电连接至n个信号输入端中的第k个信号输入端,第k个2路选择模块的第二输入端口电连接至n个信号输入端中的第n 1-k个信号输入端。

141.例如,在一种实施例中,n个请求信号按照从低位至高位的顺序分别输入第1个信号输入端至第n个信号输入端,仲裁器的优先级顺序为低位优先级最高,也即n个请求信号需要按照从低位至高位的顺序分别输入第1输入端至第n输入端,则此时第一选择信号可以是“0”,以选通每个2路选择模块的第一输入端口,从而将第1个信号输入端至第n个信号输

入端输入的n个请求信号按照从低位至高位输出至第1输入端至第n输入端。

142.例如,在另一种实施例中,n个请求信号按照从高位至低位的顺序分别输入第1个信号输入端至第n个信号输入端,仲裁器的优先级顺序为低位优先级最高,也即n个请求信号需要按照从低位至高位的顺序分别输入第1输入端至第n输入端,则此时第一选择信号可以是“1”,以选通每个2路选择模块的第二输入端口,从而将第1个信号输入端至第n个信号输入端输入的n个请求信号按照从低位至高位输出至第1输入端至第n输入端。

143.例如,2路选择模块可以实现为2路选择器。

144.图5为本公开至少一实施例提供的优先级选择电路的示意性结构图。

145.如图5所示,优先级选择电路包括n个2路选择模块,分别为2路选择器mux_1、2路选择器mux_2、2路选择器mux_3、...、2路选择器mux_n-1、2路选择器mux_n。

146.每个2路选择器包括两个输入端口,例如,每个2路选择器的上方输入端口称为第一输入端口,下方输入端口称为第二输入端口。

147.如图5所示,每个2路选择器均接收选择信号的控制,并在选择信号的控制下,分别从输出端口输出第一输入端口或第二输入端口的信号。

148.例如,信号输入端1至信号输入端n分别输入n个请求信号,每个请求信号包括有效或无效两种状态,例如,每个请求信号是1比特信号,在请求信号是1时,表示有效,在请求信号是0时,表示无效。

149.例如,n个请求信号排列成二进制序列时,n个请求信号按照低位至高位的顺序分别从信号输入端1至信号输入端n输入至优先级选择电路。也就是说,信号输入端1输入n个请求信号组成的二进制序列的最低位(例如第0位),信号输入端2输入n个请求信号组成的二进制序列的第1位,以此类推,信号输入端n输入n个请求信号组成的二进制序列的最高位(例如第n-1位)。

150.当然,图5示出了一种可能的实施例,例如,n个请求信号也可以按照高位至低位的顺序分别从信号输入端1至信号输入端n输入至优先级选择电路。也就是说,信号输入端1输入n个请求信号组成的二进制序列的最高位(例如第n-1位),信号输入端2输入n个请求信号组成的二进制序列的第n-2位,以此类推,信号输入端n输入n个请求信号组成的二进制序列的最低位(例如第0位)。此时,选择信号或各个输入端与2路选择模块的连接关系进行适应性调整即可。

151.下面以n个请求信号按照低位至高位的顺序分别从信号输入端1至信号输入端n输入至优先级选择电路为例,描述图5中的电路结构。

152.例如,如图5所示,多个2路选择模块中的第1个2路选择模块mux_1的第一输入端口与n个请求信号中沿从低位到高位顺序排列的第1个请求信号的信号输入端(也即信号输入端1)电连接,第1个2路选择模块mux_1的第二输入端口与n个请求信号中沿从高位到低位顺序排列的第1个请求信号的信号输入端(也即信号输入端n)电连接。

153.例如,如图5所示,多个2路选择模块中的第2个2路选择模块mux_2的第一输入端口与n个请求信号中沿从低位到高位顺序排列的第2个请求信号的信号输入端(也即信号输入端2)电连接,第2个2路选择模块mux_2的第二输入端口与n个请求信号中沿从高位到低位顺序排列的第2个请求信号的信号输入端(也即信号输入端n-1)电连接。

154.以此类推,如图5所示,多个2路选择模块中的第n个2路选择模块mux_n的第一输入

端口与n个请求信号中沿从低位到高位顺序排列的第n个请求信号的信号输入端(也即信号输入端n)电连接,第n个2路选择模块mux_n的第二输入端口与n个请求信号中沿从高位到低位顺序排列的第n个请求信号的信号输入端(也即信号输入端1)电连接。

155.例如,若n为奇数,则对于第(n 1)/2个2路选择模块,可以将第一输入端口和第二输入端口均连接从低位到高位顺序排列的第(n 1)/2个请求信号的信号输入端。或者,此时也可以设置n-1个2路选择模块,直接将第(n 1)/2个请求信号输出至对应的第(n 1)/2输入端。

156.图6为本公开至少一实施例提供的仲裁器的模块示意图。

157.如图6所示,该仲裁器接收两个输入参数,分别为选择信号和n位请求信号source[n-1:0],该仲裁器输出两个参数,分别为独热编码形式的信号oh_out[n-1:0]和二进制索引值ptr[m-1:0]。

[0158]

例如,n位请求信号通过n个信号输入端输入优先级选择电路,第1输出端至第n输出端分别输出n位的独热编码形式的信号oh_out[n-1:0],二进制索引值ptr[m-1:0]通过转换电路得到。

[0159]

例如,该仲裁器中包括1个预先指定的参数source_num,也即n。例如,在例化模块的过程中可以根据不同的n得到具体对应的电路结构。

[0160]

图7为本公开一实施例提供的仲裁器的示意性结构图。下面结合图7,具体说明本公开一实施例提供的仲裁器的完整电路结构。

[0161]

例如,如图7所示,该仲裁器包括仲裁执行电路、优先级选择电路和转换电路。

[0162]

例如,该仲裁器在例化时指定source_num为8,也即n=8。

[0163]

例如,优先级选择电路配置为将8个信号输入端(图7中的信号输入端1至信号输入端8)输入的8个请求信号按照优先级从高到低的顺序分别输入第1输入端至第8输入端。

[0164]

例如,仲裁执行电路配置为根据第1输入端至第8输入端输入的信号进行仲裁,输出独热编码形式的信号至第1输出端至第8输出端。

[0165]

例如,转换电路配置为将8个输出端输出的独热编码形式信号转换为对应的二进制索引值。例如,如图7所示,转换电路包括一个8-3编码器。

[0166]

例如,仲裁执行电路包括8个输入端、与8个输入端一一对应的8个输出端和8个仲裁子电路。例如,8个输入端分别为第1输入端至第8输入端,8个输出端分别为第1输出端至第8输出端。

[0167]

例如,第1输入端输入的信号的优先级最高,第2输入端输入的信号的优先级次之,依次类推,第8输入端输入的信号的优先级最低。

[0168]

例如,第1输入端和第1输出端与8个仲裁子电路中的第1个仲裁子电路电连接,第2输入端和第2输出端与8个仲裁子电路中的第2个仲裁子电路电连接,以此类推,第8输入端和第8输出端与8个仲裁子电路中的第8个仲裁子电路电连接。

[0169]

关于第1个仲裁子电路的电路结构参考图2的相关描述,这里不再赘述。

[0170]

例如,每个仲裁子电路中的反相器的输出端即为该仲裁子电路的反相输出端。

[0171]

例如,以第8个仲裁子电路为例,具体说明仲裁子电路的电路结构。

[0172]

例如,该仲裁子电路中的与运算模块包括一个8输入与门,8输入与门的8个输入端口分别与第1个仲裁子电路的反相输出端1(也即第1个仲裁子电路的反相器的输出端)至第

7个仲裁子电路的反相输出端7(也即第7个仲裁子电路的反相器的输出端)电连接,此外,该8输入与门还与第8输入端电连接。例如,该与门配置为对第1输入端的输入信号的反相信号、第2输入端的输入信号的反相信号、..、第7输入端的输入信号的反相信号以及第8输入端的输入信号进行与运算,将运算结果输出至第8输出端。

[0173]

例如,为调整电路时序,在第8输入端和与门之间还设置了一个缓冲器。

[0174]

例如,针对第2个仲裁子电路至第7个仲裁子电路中的与门,该与门可以均使用8输入与门,此时多余的输入端口连接高电平信号。例如,这些与门也可以使用6输入与门或4输入与门等,本公开对此不作限制。

[0175]

关于优先级选择电路的具体结构可以参考图5的相关描述,这里不再赘述。

[0176]

例如,8个信号输入端输入的8个请求信号构成的二进制序列为“10101000”,例如,8个请求信号组成的二进制序列按照低位至高位的顺序分别由信号输入端1至信号输入端8输入仲裁器,例如,信号输入端1输入“0”,信号输入端2输入端“0”,...,信号输入端7输入“0”,信号输入端8输入“1”。

[0177]

例如,选择信号设置为第一选择信号,选择将8个请求信号组成的二进制序列按照低位优先级最高原则输入仲裁执行电路。例如,每个2路选择模块配置为在第一选择信号的控制下将第一输入端口的信号输出,由此,信号输入端1的信号传输至第1输入端,信号输入端2的信号传输至第2输入端,...,信号输入端8的信号传输至第8输入端,从而将8个请求信号按照低位优先级最高原则输入仲裁执行电路。

[0178]

例如,仲裁执行电路中的第1个仲裁子电路至第3个仲裁子电路均输出“0”至相应的输出端;第4个仲裁子电路中的与运算模块对信号第1输入端至第3输入端输入的信号的反相信号以及第4输入端输入端的信号进行与运算,将与运算结果“1”输出至第4输入端。由于第4输入端输入的有效信号屏蔽了第5输入端至第8输入端,因此,第5输入端至第8输入端均输出“0”。因此,第1输出端至第8输出端分别输出“0”、“0”、“0”、“0”、“1”、“0”、“0”、“0”。

[0179]

例如,转换电路对8个输出端的独热编码形式的信号进行转换,输出二进制索引值“011”(3)。

[0180]

结合上述描述,本公开至少一实施例提供的仲裁器,能够动态实时调整仲裁器的优先级顺序,仲裁执行电路部分使用组合逻辑实现,简化电路结构,在单元库提供多输入端口的与门时,这种设计方式可以极大地减少组合逻辑的级数,有利于后端时序收敛。并且,该仲裁器提供两种输出格式,分别是独热编码形式和二进制索引值形式,利用转换电路实现独热编码形式到二进制索引值形式的转换。

[0181]

本公开至少一实施例还提供一种电子装置。例如,该电子装置包括如上任一实施例所述的仲裁器。

[0182]

例如,该电子装置可以实现为任意需要仲裁器的电路,例如,电路可以包括一个电路板或多个电路板的组合,在本技术实施例中,该一个电路板或多个电路板的组合可以包括:(1)一个或多个处理器;(2)与处理器相连接的一个或多个非暂时的存储器;以及(3)处理器可执行的存储在存储器中的固件。

[0183]

例如该数字电路可以包括大规模集成电路。例如该电子装置可以包括片上系统(system on chip,简称soc)等形态。

[0184]

例如,该电子装置可以包括中央处理器、图形处理器、张量处理器等具有数据处理

能力和/或指令执行能力的大规模集成电路,或者,该电子装置也可以包括实现特定功能的数字电路或数字电路单元。本公开对电子装置的功能、形态、用途不作限制,该电子装置包括本公开任一实施例所述的仲裁器即可。

[0185]

对于本公开,还有以下几点需要说明:

[0186]

(1)本公开实施例附图只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

[0187]

(2)为了清晰起见,在用于描述本发明的实施例的附图中,层或结构的厚度和尺寸被放大。可以理解,当诸如层、膜、区域或基板之类的元件被称作位于另一元件“上”或“下”时,该元件可以“直接”位于另一元件“上”或“下”,或者可以存在中间元件。

[0188]

(3)在不冲突的情况下,本公开的实施例及实施例中的特征可以相互组合以得到新的实施例。

[0189]

以上所述仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,本公开的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。