技术特征:

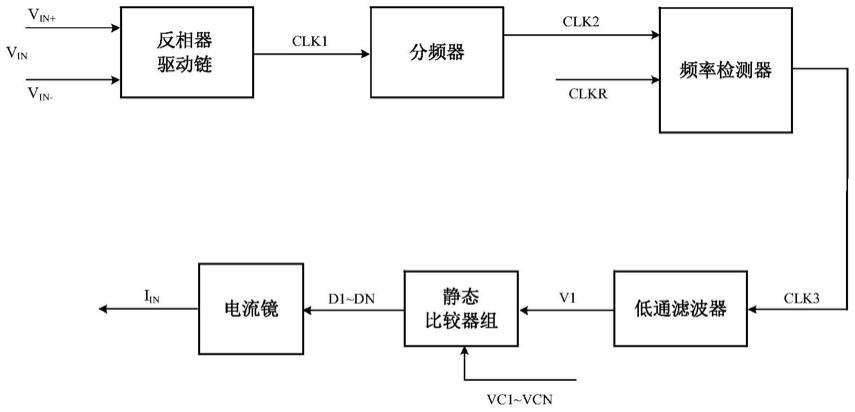

1.一种应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,包括:反相器驱动链,采集所述输入缓冲器的输入模拟信号,并将所述输入模拟信号转换为第一时钟信号;分频器,接收所述第一时钟信号,对所述第一时钟信号进行分频处理,得到第二时钟信号;频率检测器,接收参考时钟信号和所述第二时钟信号,对所述第二时钟信号进行频率检测,得到鉴频输出信号;低通滤波器,接收所述鉴频输出信号,将所述鉴频输出信号转换为直流形式的鉴频电压;静态比较器组,接收所述鉴频电压和n个不同大小的参考电压,将所述鉴频电压与n个所述参考电压分别进行比较,得到n位数字码;可控电流镜,接收n位所述数字码,在n位所述数字码的控制下为所述输入缓冲器提供大小可调的输入电流;其中,n为大于等于2的整数。2.根据权利要求1所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述反相器驱动链包括:第一反相单元,接所述输入模拟信号的一端,进行连续m次反相,得到并输出所述第一时钟信号;第二反相单元,接所述输入模拟信号的另一端,进行一次反相,悬空不输出;其中,m为大于等于2的整数。3.根据权利要求2所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述第一反相单元包括m个依次级联的cmos反相器,所述第二反相单元包括一个cmos反相器。4.根据权利要求3所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,在所述第一反相单元中,m个依次级联的所述cmos反相器中的nmos管的宽长比以s为公比呈等比数列分布,m个依次级联的所述cmos反相器中的pmos管的宽长比以s为公比呈等比数列分布,其中,s为大于等于2的整数。5.根据权利要求4所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述分频器包括l个依次级联的d触发器,第i个所述d触发器的正向输出端接第i 1个所述d触发器的时钟端,第j个所述d触发器的反向输出端接第j个所述d触发器的输入端,第一个所述d触发器的时钟端接所述第一时钟信号,第l个所述d触发器的正向输出端输出所述第二时钟信号,其中,l为大于等于2的整数,i为1~l-1的整数,j为1~l的整数。6.根据权利要求5所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述第二时钟信号的频率小于等于所述参考时钟信号频率的一半。7.根据权利要求6所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述频率检测器包括第一反相器、第二反相器、第三反相器、延时反相器链、或非门、第一与非门、第二与非门、第三与非门、第四与非门及rs触发器,所述第一反相器的输入端接所述参考时钟信号,所述第一反相器的输出端接所述第一与非门的第一输入端,所述第一与非门的输出端接所述异或门的第一输入端,所述异或门的输出端经依次串接的所述第二

反相器、所述延时反相器链、所述第三反相器后接所述第一与非门的第二输入端,所述第二与非门的第一输入端接所述第二时钟信号,所述第二与非门的输出端接所述rs触发器的直接置位端,所述第二与非门的输出端还接所述第三与非门的第一输入端和所述第四与非门的第一输入端,所述rs触发器的直接复位端接所述第一与非门的第二输入端,所述rs触发器的正向输出端接所述第三与非门的第二输入端,所述第三与非门的输出端接所述异或门的第二输入端,所述rs触发器的正向输出端还接所述第四与非门的第二输入端,所述第四与非门的输出端接所述第二与非门的第二输入端,所述第四与非门的输出端输出所述鉴频输出信号。8.根据权利要求7所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述静态比较器组包括n个并行设置的比较器,n个所述比较器的同相输入端分别接所述鉴频电压,n个所述比较器的反相输入端与n个所述参考电压一一对应连接,每个所述比较器的输出端输出一位数字码。9.根据权利要求8所述的应用于高速adc输入缓冲器的自适应电流产生电路,其特征在于,所述可控电流镜包括:第一电流镜单元,产生第一电流并对所述第一电流进行镜像输出,得到第二电流;第二电流镜单元,包括n条并行设置的电流镜支路,每条所述电流镜支路分别对所述第二电流进行镜像,n条所述电流镜支路与n位所述数字码一一对应连接,所述数字码控制所述电流镜支路的通断状态,n条所述电流镜支路的输出电流汇成所述输入电流。10.一种应用于高速adc输入缓冲器的自适应电流产生方法,其特征在于,根据所述输入缓冲器的输入模拟信号的频率自动调节所述输入缓冲器的输入电流,所述应用于高速adc输入缓冲器的自适应电流的产生方法包括:采集所述输入模拟信号,并将所述输入模拟信号转换为第一时钟信号;对所述第一时钟信号进行分频处理,得到第二时钟信号;对所述第二时钟信号进行频率检测,得到鉴频输出信号;将所述鉴频输出信号转换为直流形式的鉴频电压;将所述鉴频电压与n个不同大小的参考电压分别进行比较,得到n位数字码;在n位所述数字码的控制下,通过可控电流镜为所述输入缓冲器提供大小可调的输入电流;其中,n为大于等于2的整数。

技术总结

本发明提供一种应用于高速ADC输入缓冲器的自适应电流产生电路及方法,所述自适应电流产生电路包括反相器驱动链、分频器、频率检测器、低通滤波器、静态比较器组及可控电流镜;本发明先后依次通过反相器驱动链的转换、分频器的分频、频率检测器的频率检测及低通滤波器的转换,将输入缓冲器的输入模拟信号转换为直流形式的鉴频电压,再通过静态比较器组的多次比较,得到N位数字码,最后通过N位数字码来控制可控电流镜,可控电流镜在N位数字码的控制下为输入缓冲器提供大小可调的输入电流,输入电流的大小与输入模拟信号的频率大小正相关,这不仅可以有效避免过大输入电流造成的功耗浪费,还可以避免过大输入电流或过小输入电流造成的性能恶化。成的性能恶化。成的性能恶化。

技术研发人员:王翊舟 刘璐 徐代果 朱璨 蒋和全 李儒章 王健安 陈光炳 付东兵 俞宙 张正平

受保护的技术使用者:重庆吉芯科技有限公司

技术研发日:2022.03.02

技术公布日:2022/6/1

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。