1.本技术涉及电源供电技术领域,尤其涉及一种芯片供电电路与电子设备。

背景技术:

2.需要进行巨大的运算工作量的数据生成设备的功耗相当高,需要改进其供电技术。为了最大化电源的转换效率,可以在印刷电路板上采取芯片串联的供电方式,在电源输入端和接地端口之间形成多级串联的电压域。但是当芯片形成的级数特别多的时候,由于每一级芯片的辅供电端口都需要消耗电流,且最上级的芯片需要更高的电压,如此会使下级的芯片电流逐渐增加且每一级的芯片的电压不一致,不同级的芯片性能出现差异,降低数据生成设备的工作性能。

技术实现要素:

3.本技术提供了一种芯片供电电路与电子设备,可以提高各级芯片的平衡性,优化工作性能。

4.第一方面,本技术提供了一种芯片供电电路,所述方法包括:

5.至少两个芯片域,所述至少两个芯片域依次连接,两个相邻的芯片域中,上一级的芯片域的接地端口和下一级的芯片域的主供电端口连接;

6.至少一个电压转换电路,在两个相邻的芯片域中,上一级的芯片域的接地端口通过一个所述电压转换电路和下一级芯片域的辅供电端口连接,所述电压转换电路用于输出目标电压给所述辅供电端口。

7.在一个实施例中,所述芯片域均包括第一数量的芯片,所述第一数量为至少一个;

8.两个相邻的芯片域中,上一级的芯片域中的芯片的接地端口分别和下一级的芯片域中的芯片的主供电端口一一连接;

9.在两个相邻的芯片域中,上一级的芯片域中的芯片的接地端口均与所述电压转换电路的输入端连接,以及下一级芯片域中的芯片的辅供电端口均与所述电压转换电路的输出端连接。

10.在一个实施例中,最上级的芯片域中的芯片的主供电端口均与供电电源连接,最下级的芯片域中的芯片的接地端口均接地。

11.在一个实施例中,所述辅供电端口包括第一供电管脚和第二供电管脚,所述电压转换电路用于输出第一电压给所述第一供电管脚,以及输出第二电压给所述第二供电管脚。

12.在一个实施例中,所述电压转换电路包括第一变压电路和第二变压电路;

13.所述第一变压电路的输入端和所述上一级的芯片域的接地端口连接,所述第一变压电路的输出端和所述第一供电管脚连接,并为所述第一供电管脚提供第一电压;

14.所述第二变压电路的输入端和所述第一变压电路的输出端连接,所述第二变压电路的输出端和所述下一级的芯片域的第二供电管脚连接,并为所述第二供电管脚提供第二

电压。

15.在一个实施例中,所述第一变压电路为boost电路,所述第二变压电路为buck电路。

16.在一个实施例中,所述第一供电管脚为i/o单元,所述第二供电管脚为pll单元。

17.在一个实施例中,所述第一电压大于所述第二电压。

18.第二方面,本技术提供了一种电子设备,所述电子设备包括如上述任一实施例的芯片供电电路。

19.在一个实施例中,所述电子设备为数据生成设备。

20.本技术公开了一种芯片供电电路与电子设备,所述芯片供电电路包括:至少两个芯片域,所述至少两个芯片域依次连接,两个相邻的芯片域中,上一级的芯片域的接地端口和下一级的芯片域的主供电端口连接;至少一个电压转换电路,在两个相邻的芯片域中,上一级的芯片域的接地端口通过一个所述电压转换电路和下一级芯片域的辅供电端口连接,所述电压转换电路用于输出目标电压给所述辅供电端口。本技术实施例提供的芯片供电电路通过在两个相邻的芯片域中设置电压转换电路,可以使每个芯片域的辅供电端口从芯片域自身所在的电源域获取电能,可以提高各个芯片域的电压的平衡性,优化芯片域的工作性能和算力性能。

附图说明

21.为了更清楚地说明本技术实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

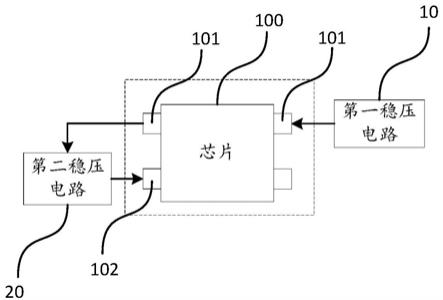

22.图1为本技术实施例提供的一种芯片供电电路的模块示意图;

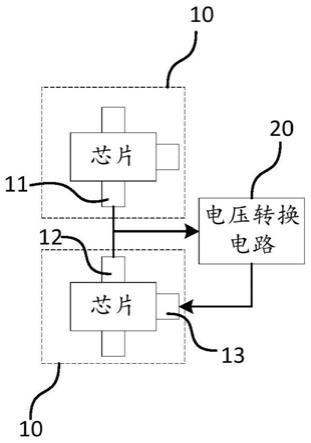

23.图2为本技术实施例提供的另一种芯片供电电路的模块示意图;

24.图3为本技术实施例提供的另一种芯片供电电路的模块示意图;

25.图4为本技术实施例提供的另一种芯片供电电路的模块示意图。

具体实施方式

26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

27.应当理解,在此本技术说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本技术。如在本技术说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。

28.还应当进一步理解,在本技术说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

29.图1为本技术实施例提供的一种芯片供电电路的模块示意图,如图1所示,芯片供电电路包括至少两个芯片域10和至少一个电压转换电路20。

30.至少两个芯片域10依次连接,两个相邻的芯片域10中,上一级的芯片域10的接地

端口11和下一级的芯片域10的主供电端口12连接;在两个相邻的芯片域10中,上一级的芯片域10的接地端口11通过一个电压转换电路20和下一级芯片域10的辅供电端口13连接,电压转换电路20用于输出目标电压给辅供电端口13。

31.其中,每个芯片域均设置有接地端口、主供电端口和辅供电端口,主供电端口用于为芯片域提供主要的电能,主供电端口一般是和供电电源连接,辅供电端口哟功能与为芯片域提供辅助的电能。多个芯片域依次连接,最上级的芯片域的主供电端口和供电电源连接,上一级的芯片域的接地端口和下一级的芯片域的主供电端口,以使上一级的芯片为下一级的芯片域提供主要的电能,最下级的芯片域的接地端口接地,多个芯片域形成串联供电。

32.可以从芯片域内部进行取电以为辅供电端口提供电能,通过电压转换电路将串联供电电路上的电压转换为辅供电端口所需要的目标电压。通过在两个相邻的芯片域中,将上一级的芯片域的接地端口通过一个电压转换电路和下一级芯片域的辅供电端口连接,使下一级的芯片域的辅供电端口直接从该芯片域自身所在的电源域获取电能,如此可以增加串联供电的电源域的平衡性,同时在印刷电路板布局时,可以减少走线、减小面积以及降低成本。

33.如图2所示,芯片供电电路包括多个芯片域10,每两个相邻的芯片域10中设置一个电压转换电路20,因此电压转换电路20的数量跟芯片域10的数量相对应,电压转换电路20的数量可以是芯片域10的数量减一。

34.本技术实施例提供的芯片供电电路通过在两个相邻的芯片域中设置电压转换电路,可以使每个芯片域的辅供电端口从芯片域自身所在的电源域获取电能,可以提高各个芯片域的电压的平衡性,优化芯片域的工作性能和算力性能。

35.在一个实施例中,芯片域10均包括第一数量的芯片,第一数量为至少一个;两个相邻的芯片域10中,上一级的芯片域10中的芯片的接地端口11分别和下一级的芯片域10中的芯片的主供电端口12一一连接;在两个相邻的芯片域10中,上一级的芯片域10中的芯片的接地端口11均与电压转换电路20的输入端连接,以及下一级芯片域10中的芯片的辅供电端口13均与电压转换电路20的输出端连接。

36.其中,每个芯片域都包括第一数量的芯片,因此在进行串联供电连接时,上一级的芯片域中的芯片均可以一一与下一级的芯片域中的芯片连接,芯片供电电路中包括第一数量的芯片串联电路。每个芯片设置有接地端口、主供电端口和辅供电端口,每个芯片域中也包括第一数量的接地端口、第一数量的主供电端口和第一数量的辅供电端口。

37.如图3所示,上一级的芯片域10中的每个芯片的接地端口11分别和下一级的芯片域10中的芯片的主供电端口12一一连接。在每两个相邻的芯片域10中,上一级的芯片域10中的芯片的接地端口11均与电压转换电路20的输入端连接,以及下一级芯片域10中的芯片的辅供电端口13均与电压转换电路20的输出端连接。电压转换电路从上一级的芯片域中获得电能,并转换为目标电压,为下一级的芯片域中的所有芯片的辅供电端口提供目标电压。

38.在一个实施例中,最上级的芯片域中的芯片的主供电端口均与供电电源连接,最下级的芯片域中的芯片的接地端口均接地。

39.其中,每个芯片域中的多个芯片之间并联,最上级的芯片域中的所有芯片的主供电端口均与供电电源连接,供电电源为第一数量的芯片串联电路提供主要的电能,最下级

的芯片域中的所有芯片的接地端口均接地。

40.在一个实施例中,如图4所示,辅供电端口13包括第一供电管脚131和第二供电管脚132,电压转换电路20用于输出第一电压给第一供电管脚131,以及输出第二电压给第二供电管脚132。

41.每个芯片上均设置有第一供电管脚和第二供电管脚,第一供电管脚和第二供电管脚需要获取不同电压的辅助电能,并为芯片内部进行不同电压的供电。

42.电压转换电路可以输出第一电压,以向芯片的第一供电管脚提供第一电压。电压转换电路还可以输出第二电压,向芯片的第二供电管脚提供第二电压。

43.在一个实施例中,如图4所示,电压转换电路20包括第一变压电路21和第二变压电路22;第一变压电路21的输入端和上一级的芯片域10的接地端口11连接,第一变压电路21的输出端和第一供电管脚131连接,并为第一供电管脚131提供第一电压;第二变压电路22的输入端和第一变压电路21的输出端连接,第二变压电路22的输出端和下一级的芯片域10的第二供电管脚132连接,并为第二供电管脚132提供第二电压。

44.其中,供电电源提供的电压,即芯片域的主供电端口上的电压,和第一电压以及第二电压的电压值均不相同,因此可以采用两个变压电路实现将主供电端口上的电压转换为第一电压和第二电压。

45.可选地,第一变压电路可以是升压电路,第二变压电路可以是降压电路。供电电源提供的电压一般是低于第一电压,第二电压低于第一电压,因此可以先将主供电端口上的电压通过第一变压电路升进行升压,得到第一电压,第一变压电路的输出端和第一供电管脚连接,以为芯片的第一供电管脚提供第一电压,同时第二变压电路的输入端和第一变压电路的输出端连接,以便第二变压电路可以将第一电压降压为第二电压,并为芯片的第二供电管脚提供第二电压。在一个实施例中,第一变压电路为boost电路,第二变压电路为buck电路。

46.其中,boost电路是一种开关直流升压电路,它可以使输出电压比输入电压高。buck电路是一种降压电路。通过boost电路和buck电路的组合,可以实现输出两种电压,并为芯片的第一供电管脚和第二供电管脚进行供电。

47.在一个实施例中,第一供电管脚为i/o单元,第二供电管脚为pll单元。

48.其中,i/o(input/output,输入/输出)单元的电压需求为第一电压,可选地,第一电压可以是1.8伏,pll(phase locked loop,锁相环)单元的电压需求为第二电压,可选地,第二电压为0.8伏。

49.本技术实施例还提供一种电子设备,所述电子设备包括如上述任一实施例的芯片供电电路。其中,电子设备中可以是包括多个芯片供电电路。

50.在一个实施例中,所述电子设备为数据生成设备。

51.以上,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。