1.本发明涉及静电防护技术,特别是涉及一种具有延长放电时间机制的静电防护电路。

背景技术:

2.静电放电(electrostatic discharge;esd)会造成电子组件、仪器设备永久性损坏,进而影响集成电路的电路功能,使产品无法正确工作。

3.静电放电的现象可能在芯片制造、封装、测试、存放或搬运的状况下产生。为了再现与预防静电放电,集成电路产品可通过静电防护的组件或者电路并搭配测试来增强集成电路对于静电放电的保护能力,进而提升电子产品的良品率。

技术实现要素:

4.为解决现有技术的问题,本发明的其中一目的在于提供一种具有延长放电时间机制的静电防护电路,以改善现有技术。

5.本发明包括一种具有延长放电时间机制的静电防护电路,包括:容阻电路、反向器、开关晶体管以及放电晶体管。容阻电路电性耦接于静电输入端以及接地端之间,并包括输入控制端,其中静电输入端预设于低态准位,并配置以接收静电输入。反向器包括:p型晶体管以及n型晶体管电路。p型晶体管电性耦接于静电输入端以及输出控制端。n型晶体管电路包括电性耦接于输出控制端以及接地端之间且互相串联的多个n型晶体管,n型晶体管的其中二者之间具有内部连接端,其中各p型晶体管以及n型晶体管的闸极受输入控制端控制。开关晶体管电性耦接于静电输入端以及内部连接端之间。放电晶体管电性耦接于静电输入端以及接地端之间,其中各开关晶体管以及放电晶体管的闸极受输出控制端控制。

6.有关本技术的特征、结构与功效,现配合附图作优选实施例详细说明如下。

附图说明

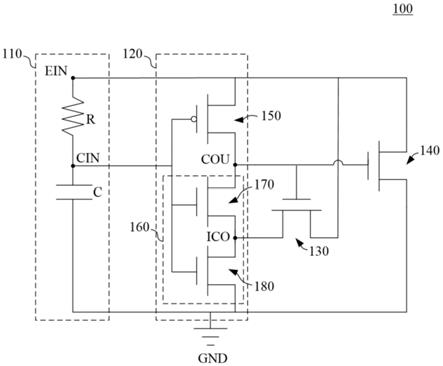

7.图1示出了本发明的一实施例中,一种具有延长放电时间机制的静电防护电路的电路图。

8.图2示出了本发明的一实施例中,静电防护电路在接收到静电输入时的电路图。

9.图3示出了本发明的一实施例中,静电防护电路在接收到静电输入经过默认时间后的电路图。

10.图4示出了本发明的一实施例中,静电防护电路在静电输入端经由放电晶体管完成放电后的电路图。

具体实施方式

11.本发明的其中一目的在于提供一种具有延长放电时间机制的静电防护电路,以通过开关晶体管的设置,在容阻电路的输入控制端于预设时间转态后,延长放电晶体管的导

通时间,以对静电输入端进行更长时间的放电。

12.请参照图1。图1示出了本发明的一实施例中,一种具有延长放电时间机制的静电防护电路100的电路图。静电防护电路100包括:容阻电路110、反向器120、开关晶体管130以及放电晶体管140。

13.容阻电路110电性耦接于静电输入端ein以及接地端gnd之间,并包括输入控制端cin。容阻电路110包括:电阻r以及电容c。其中,电阻r电性耦接于静电输入端ein以及输入控制端cin之间,电容c电性耦接于输入控制端cin以及接地端gnd之间。

14.在不同的实施例中,电阻r可以为(但不限于)一般电阻、晶体管电阻、多晶硅电阻或n型井电阻。电容c可以为(但不限于)一般电容、金氧半晶体管(metal-oxide-semiconductor;mos)电容、金属氧化物金属(metal-oxide-metal;mom)电容或金属绝缘层金属(metal-insulator-metal;mim)电容。然而,本发明并不以此为限制。

15.反向器120包括:p型晶体管150以及n型晶体管电路160。其中,p型晶体管150电性耦接于静电输入端ein以及输出控制端cou之间。n型晶体管电路160包括电性耦接于输出控制端cou以及接地端gnd之间且互相串联的n型晶体管170及n型晶体管180,n型晶体管170、180之间具有内部连接端ico。各p型晶体管150以及n型晶体管170、180的闸极均受输入控制端cin控制。

16.开关晶体管130电性耦接于静电输入端ein以及内部连接端ico之间。放电晶体管140电性耦接于静电输入端ein以及接地端gnd之间。其中,各开关晶体管130以及放电晶体管140的闸极受输出控制端cou控制。在本实施例中,开关晶体管130以及放电晶体管140均为单一个n型晶体管,例如(但不限于)n型金氧半晶体管或者npn双极接面晶体管。

17.以下将针对静电防护电路100的运作,进行更详细的说明。

18.请参照图2。图2示出了本发明的一实施例中,静电防护电路100在接收到静电输入esd时的电路图。

19.在静电输入端ein尚未接收到静电输入esd时,静电输入端ein将预设于低态准位。此时,电性耦接于静电输入端ein的容阻电路110,也将由于静电输入端ein位于低态准位,而使输入控制端cin位于低态准位。

20.当静电输入端ein接收到静电输入esd时,将从低态准位升高至高态准位(在图2中标示为“0-》1”)。此时,容阻电路110将使输入控制端cin在预设时间内维持低态准位(在图2中标示为“0”)。更详细地说,虽然容阻电路110中的电阻r与静电输入端ein电性耦接,但需要时间对电容c进行充电,来使输入控制端cin的电压准位升高。

21.因此,在预设时间前,输入控制端cin将由于电压准位尚未超过转态点而位于低态准位。在一实施例中,预设时间是由电阻r以及电容c的时间常数决定。在一实施例中,静电输入esd使静电输入端ein升高至高态准位所需的时间为纳秒(nanosecond;ns)等级,而容阻电路110使输入控制端cin升高至高态准位所需的时间为微秒(microsecond;μs)等级。

22.位于低态准位的输入控制端cin将通过反向器120使输出控制端cou升高至高态准位(在图2中标示为“0-》1”)。更详细地说,输入控制端cin将使p型晶体管150导通,以及使n型晶体管电路160关闭。导通的p型晶体管150将使高态准位的静电输入端ein对输出控制端cou充电,而升高至高态准位(在图2中标示为“0-》1”)。

23.高态准位的输出控制端cou将同时使开关晶体管130以及放电晶体管140导通。

24.开关晶体管130的导通将使高态准位的静电输入端ein对n型晶体管170、180之间的内部连接端ico进行充电。因此,内部连接端ico将升高至高态准位(在图2中标示为“0-》1”)而关闭n型晶体管电路160,进而使输出控制端cou维持于高态准位。

25.放电晶体管140的导通可形成(但不限于)电流id,以对静电输入端ein放电至接地端gnd。

26.请参照图3。图3示出了本发明的一实施例中,静电防护电路100在接收到静电输入esd经过默认时间后的电路图。

27.输入控制端cin在预设时间后升高至高态准位(在图3中标示为“0-》1”)。其中,高态准位的输入控制端cin将使p型晶体管150关闭。进一步地,输入控制端cin理应使n型晶体管电路160导通。

28.然而,开关晶体管130在此时维持导通,使高态准位的静电输入端ein对n型晶体管170、180之间的内部连接端ico进行充电,内部连接端ico将维持高态准位(在图2中标示为“1”)。因此,即便输入控制端cin为高态准位,n型晶体管电路160仍将因为内部连接端ico维持高态准位,而使n型晶体管170因为闸极与源极之间的压差不足而关闭,进而使n型晶体管电路160关闭。

29.关闭的n型晶体管电路160将使输出控制端cou维持于高态准位(在图2中标示为“1”),而使放电晶体管140继续导通形成电流id以对静电输入端ein放电。

30.请参照图4。图4示出了本发明的一实施例中,静电防护电路100在静电输入端ein经由放电晶体管140完成放电后的电路图。

31.当静电输入端ein放电至低态准位(在图2中标示为“1-》0”)时,将无法再经由开关晶体管130对内部连接端ico充电。为高态准位(在图4中标示为“1”)的输入控制端cin将使n型晶体管180导通以对内部连接端ico放电,使内部连接端ico从高态准位降至低态准位(在图4中标示为“1-》0”)。

32.无法维持高态准位的内部连接端ico,将使n型晶体管170因为闸极与源极之间的压差大于其阈值电压而导通。导通的n型晶体管电路160将进而使输出控制端cou降低至低态准位(在图4中标示为“1-》0”),而使放电晶体管140以及开关晶体管130关闭。

33.在一实施例中,容阻电路110将在一段时间后经由电容c的放电而使输入控制端cin降至低态准位(未标示于图中),而回复至尚未接收静电输入esd的状态。

34.在部分其他技术中,容阻电路的输入控制端于预设时间转态后,将使输出控制端随之转态,导致放电晶体管较早关闭而无法对静电输入端完全放电。

35.相对的,本发明中的静电防护电路100可通过开关晶体管130的设置,在容阻电路110的输入控制端cin于预设时间转态后,再延长放电晶体管140的导通时间,以对静电输入端ein进行更长时间的放电。

36.须注意的是,上述实施例中的部分组件,可在不影响静电防护电路100的操作下,以其他组件代替。举例而言,在一实施例中,开关晶体管130可通过一个附加反向器(未绘示于图中)电性耦接于输出控制端cou的p型晶体管。其中,p型晶体管可以为(但不限于)p型金氧半晶体管或者pnp双极接面晶体管。

37.类似地,在一实施例中,放电晶体管140也可通过一个附加反向器(未绘示于图中)电性耦接于输出控制端cou的p型晶体管。其中,p型晶体管可以为(但不限于)p型金氧半晶

体管或者pnp双极接面晶体管。

38.此外,在一实施例中,开关晶体管130也可包括多个电性串联的n型或p型晶体管,并均受到输出控制端cou的控制。

39.进一步地,在图1的实施例中,n型晶体管电路160包括的n型晶体管的数目为两个。然而在其他实施例中,n型晶体管电路160包括的n型晶体管的数目可为两个以上的任何数值,且内部连接端可设置在任意二相邻的n型晶体管之间。

40.需注意的是,上述的实施方式仅为一示例。于其他实施例中,本领域的普通技术人员应当可以在不违背本发明的精神下进行变动。

41.综合上述,本发明中具有延长放电时间机制的静电防护电路可通过开关晶体管的设置,在容阻电路的输入控制端于预设时间转态后,再延长放电晶体管的导通时间,以对静电输入端进行更长时间的放电。

42.虽然本技术的实施例如上所述,然而所述些实施例并非用来限定本技术,本技术领域普通技术人员可根据本技术的明示或隐含的内容对本技术的技术特征施以变化,凡此种种变化均可能属于本技术所寻求的专利保护范围。

43.附图标记说明

44.100:静电防护电路

45.110:容阻电路

46.120:反向器

47.130:开关晶体管

48.140:放电晶体管

49.150:p型晶体管

50.160:n型晶体管电路

51.170、180:n型晶体管

52.c:电容

53.cin:输入控制端

54.cou:输出控制端

55.ein:静电输入端

56.esd:静电输入

57.gnd:接地端

58.ico:内部连接端

59.id:电流

60.r:电阻

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。