1.各种实施方式总体上涉及显示设备,更具体地,涉及感测显示面板的像素信号的感测电路以及包括该感测电路的源极驱动器。

背景技术:

2.通常,显示设备包括显示面板、显示驱动设备和时序控制器。

3.显示驱动设备可以包括集成为芯片的源极驱动器。考虑到显示面板的尺寸和分辨率,显示驱动设备可以包括多个源极驱动器。该源极驱动器将从时序控制器提供的数字图像数据转换为源信号,并将源信号提供给显示面板。

4.源极驱动器感测显示面板的像素信号,并将像素信号转换为数字数据。

5.根据传统技术的源极驱动器可以包括感测像素信号的感测电路,并且每个感测电路可以包括将输入电流转换为电压的积分器。

6.然而,根据传统技术的源极驱动器的积分器根据面板负载在其性能上具有差异,并且需要用于多个通道中的每个的反馈电容器。

7.因此,需要降低面板负载对积分器的性能的影响,并通过排除积分器的反馈电容器来减小感测电路和源极驱动器的芯片面积。

8.此外,感测电路和源极驱动器需要用于采样像素信号的采样电容器。因此,为了减小感测电路和源极驱动器的芯片面积,需要实施具有较小尺寸的采样电容器。

技术实现要素:

9.各种实施方式涉及感测电路和包括该感测电路的源极驱动器,其能够降低面板负载对积分器的性能的影响,并且通过排除积分器的反馈电容器来减小芯片面积。

10.此外,各种实施方式涉及感测电路和包括该感测电路的源极驱动器,其能够通过减少用于采样的电流量而使用小尺寸的采样电容器,从而减小芯片面积。

11.在实施方式中,感测电路可以包括放大器电路,放大器电路配置成从显示面板接收输入电流,其中,放大器电路将输入电流转换为具有线性度的输出电流,并且输出电流的电流量小于输入电流的电流量。

12.在实施方式中,源极驱动器可以包括:感测电路,配置成通过感测从显示面板接收的输入电流来输出采样电压;全局放大器,配置成通过放大采样电压来输出放大的信号;以及模数转换器,配置成将放大的信号转换为数字数据,其中,感测电路包括放大器电路和采样电路,放大器电路配置成将输入电流转换为具有线性度的输出电流,并且输出电流的电流量小于输入电流的电流量,采样电路配置成通过对输出电流进行采样来输出采样电压。

13.如上所述,通过包括将输入电流转换为输出电流的放大器电路,可以降低面板负载对积分器的性能的影响,并且可以通过排除积分器的反馈电容器来减小芯片面积。

14.此外,与传统技术相比,放大器电路的参考电压可以设置为较低的电平。

15.此外,由于放大器电路配置成输出电流量小于输入电流的输出电流,因此用于采

样输出电流的采样电容器可以被设计成具有小的电容量。即,可以使用具有小面积的采样电容器来实施感测电路和源极驱动器,因此,可以减小芯片面积。

16.此外,可以精确地感测像素的信号,无论多个通道的数量是否增加。

附图说明

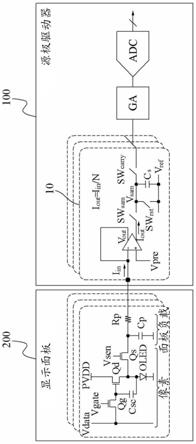

17.图1是根据实施方式的感测电路和包括该感测电路的源极驱动器的框图。

18.图2是根据实施方式的感测电路的电路图。

19.图3是图1和图2中所示的放大器电路的电路图。

20.图4是根据实施方式的感测电路的时序图。

具体实施方式

21.本公开公开了感测电路和包括该感测电路的源极驱动器的实施方式,其能够根据显示面板的负载来降低对积分器的性能的影响,并且通过排除积分器的反馈电容器来减小芯片面积。

22.在实施方式中,多个通道可以连接到显示面板的感测线,并且通过通道接收的输入电流可以限定为用于检测像素特性的像素信号。例如,像素特性可以包括驱动晶体管和有机发光二极管的阈值电压、迁移率等。

23.在实施方式中,多个通道中的每个可以包括感测电路,并且为了便于说明,将描述一个通道的感测电路。

24.在实施方式中,诸如第一和第二的术语可用于识别各种组件。这些组件不受诸如第一和第二的术语限制。

25.图1是根据实施方式的感测电路10和包括感测电路10的源极驱动器100的框图。

26.参考图1,显示设备可以包括显示面板200和源极驱动器100。

27.显示面板200可以包括以矩阵形式形成的像素。

28.每个像素可以包括有机发光二极管oled、存储电容器csc、驱动晶体管qd、栅极晶体管qg和感测晶体管qs。

29.vdata表示用于控制光发射的驱动电压,并且提供给栅极晶体管qg的漏极,并且vgate表示用于栅极晶体管qg的操作的栅极信号。因此,栅极晶体管qg可以通过栅极信号vgate切换驱动电压vdata到驱动晶体管qd的栅极的传输。

30.pvdd表示恒定电压,并且提供给驱动晶体管qd的漏极。因此,驱动晶体管qd可以根据通过栅极晶体管qg施加到驱动晶体管qd的栅极的驱动电压vdata的电平,控制通过恒定电压pvdd提供给有机发光二极管oled的电流量。

31.vsen表示用于控制感测晶体管qs的操作的感测控制信号。因此,感测晶体管qs可以根据感测控制信号vsen通过面板负载向感测电路10提供与充入到驱动晶体管qd和有机发光二极管oled之间的节点的电压对应的输入电流。

32.显示面板200的每个像素通过面板负载连接到源极驱动器100的感测电路10。可以理解,施加到每个像素的面板负载表示等效地形成在配置在感测晶体管qs和感测电路10之间的感测线上的电容器组件cp和电阻器组件rp。

33.源极驱动器100可以包括感测电路10、全局放大器ga和模数转换器adc。

34.感测电路10可以配置成与多个通道中的每个对应。通道意指显示面板200的每个面板负载(即,感测线)连接到感测电路10。源极驱动器100可以包括多个通道,并且感测电路10可以针对多个通道中的每个配置。

35.感测电路10可以从显示面板200的相应通道的像素接收输入电流iin。感测电路10配置成将输入电流iin转换为具有线性度的输出电流iout。产生的输出电流iout具有比输入电流iin更小的电流量。

36.感测电路10可以对通道的输出电流iout进行采样,并且可以向全局放大器ga输出采样电压vsam。与多个通道对应的感测电路10可以配置成依次输出采样电压vsam,并且为此,多路复用器(未示出)可以配置在感测电路10和全局放大器ga之间。

37.全局放大器ga可以放大依次从感测电路10输出的采样电压vsam,并且可以将放大的信号输出到模数转换器adc。

38.模数转换器adc可以将放大的信号转换为数字数据,并将数字数据提供给时序控制器(未示出)。时序控制器可以使用数字数据产生与像素特性对应的补偿数据,并且可以使用补偿数据校正图像数据。

39.图2是根据实施方式的感测电路10的电路图。图3是图1和图2中所示的放大器电路的电路图。

40.参考图2,感测电路10可以包括放大器电路20和采样电路30。放大器电路20配置成将输入电流iin转换为具有线性度的输出电流iout,并输出电流量小于输入电流iin的输出电流iout。采样电路30配置成对输出电流iout进行采样以输出采样电压vsam。

41.首先,将参考图3详细描述放大器电路20。

42.放大器电路20可以包括输入和负载级电路22、输出级电路24和电流镜电路26。

43.输入和负载级电路22可以包括接收输入电流iin的第一输入端vin(-)和接收第一参考电压vpre的第二输入端vin( )。

44.输入和负载级电路22可以响应于输入电流iin和第一参考电压vpre输出上拉信号up和下拉信号dn。详细地,输入和负载级电路22配置成产生与第一输入端vin(-)和第二输入端vin( )之间的电势差对应的上拉信号up和下拉信号dn。

45.输出级电路24配置成响应于上拉信号up和下拉信号dn,输出与输入电流iin对应的第一输出电压vout和与输入电流iin的第一标度对应的源电流。为此,输出级电路24可以包括第一输出级电路24a和第二输出级电路24b。

46.第一输出级电路24a可以响应于上拉信号up和下拉信号dn输出与输入电流iin对应的第一输出电压vout。例如,第一输出级电路24a可以包括串联连接在第一电源电压vdd的端子和接地电压的端子之间的pmos晶体管p1和nmos晶体管n1。pmos晶体管p1与nmos晶体管n1之间的节点可以限定为输出第一输出电压vout的第一输出端子ot1,并且第一输出级电路24a的第一输出端子ot1可以与输入和负载级电路22的第一输入端vin(-)互连。

47.第二输出级电路24b可以响应于上拉信号up和下拉信号dn形成与输入电流iin对应并流过电流路径ipath的源电流。例如,第二输出级电路24b可以包括串联连接在第一电源电压vdd的端子和接地电压的端子之间的pmos晶体管p2和nmos晶体管n2。pmos晶体管p2和nmos晶体管n2之间的节点可以限定为输出源电流的节点nd。

48.第二输出级电路24b可以配置成与第一输出级电路24a具有1:1的复制比例。复制

比例可以理解为根据包括在第一输出级电路24a和第二输出级电路24b中的晶体管的通道比例而流动的电流量之间的比例。

49.换言之,可以理解,第二输出级电路24b通过响应于上拉信号up和下拉信号dn以1:1的复制比复制第一输出级电路24a的与输入电流iin对应的电流来输出源电流。因此,可以理解,输入电流iin、第一输出级电路24a的电流和源电流限定为具有在第一标度内的电流量,并且具有相同的电流量。

50.电流镜电路26配置成从第二输出级电路24b的节点nd复制流经电流路径ipath的源电流,并且由此输出第二标度的输出电流iout,第二标度的输出电流iout具有比第一标度小的电流量。通过输出级电路24和电流镜电路26的复制,输出电流iout可以被输出为相对于输入电流iin具有线性度。例如,电流镜电路26可以相对于第二输出级电路24b的源电流以预设的1/n(n是大于1的正实数)的复制比复制输出电流iout。

51.电流镜电路26可以包括pmos晶体管p3和pmos晶体管p4。pmos晶体管p3配置在第二电源电压vcc的端子和节点nd之间,pmos晶体管p4配置在第二电源电压vcc的端子和第二输出端子ot2之间。pmos晶体管p3和pmos晶体管p4的栅极端子可以互连,并且可以连接到节点nd。

52.在电流镜电路26中,pmos晶体管p3和pmos晶体管p4可以具有n:1的通道比例。因此,电流镜电路26可以具有n:1的电流复制比。电流镜电路26的第二电源电压vcc可以设置为比输出级电路24的第一电源电压vdd低的电平。

53.通过上述配置,当源电流流过第二输出级电路24b时,电流镜电路26可以通过电流镜电路26的pmos晶体管p3的电流经由pmos晶体管p4和第二输出端子ot2输出电流量对应于源电流的1/n的输出电流iout。

54.回到参考图2,采样电路30可以对从放大器电路20输出的输出电流iout进行采样,并且可以输出采样电压vsam。

55.采样电路30可以包括第一开关swsam、采样电容器cs、第二开关swcarry和第三开关swrst。

56.第一开关swsam可以将从放大器电路20输出的输出电流iout传输到采样电容器cs。例如,多个通道的第一开关swsam可以同时导通。

57.采样电容器cs可以对通过第一开关swsam传输的输出电流iout进行采样。

58.第二开关swcarry可以将通过采样电容器cs采样的采样电压vsam输出到全局放大器ga。例如,多个通道的第二开关swcarry可以以预定的时间间隔依次导通。

59.第三开关swrst可以将采样电容器cs初始化为第二参考电压vref。

60.采样电路30的第二参考电压vref可以设置为比输入到放大器电路20的待与输入电流iin进行比较的第一参考电压vpre的电平低。

61.图4是根据实施方式的感测电路10的时序图。在图4中,波形swrst表示用于控制第三开关swrst的开关的信号,波形swsam表示用于控制第一开关swsam的开关的信号,并且on和off表示相应开关的导通和断开。

62.参考图2和图4,首先,感测电路10可以通过接通第一开关swsam和第三开关swrst将采样电容器cs的采样电压vsam初始化为第二参考电压vref。

63.然后,感测电路10可以通过导通第一开关swsam并断开第三开关swrst来通过采样

电容器cs对从放大器电路20输出的输出电流iout进行采样。

64.感测电路10可以对传输通过第一开关swsam的输出电流iout采样预设时间t1。采样电容器cs可以通过输出电流iout充电,并且由此,采样电压vsam可以在预设时间t1内上升。

65.接着,感测电路10可以通过断开第一开关swsam来保持采样电压vsam。

66.采样电压vsam的大小δv可以通过以下等式1来计算。

67.[等式1]

[0068][0069]

采样电压vsam的大小δv可以由相对于输入电流iin具有线性度的1/n的复制比例、采样时间t1和采样电容器cs的电容量来确定。

[0070]

随后,感测电路10可以通过导通第二开关swcarry来依次将采样电压vsam输出到全局放大器ga。

[0071]

从以上描述中可以看到,通过包括将输入电流转换为输出电流的放大器电路,根据实施方式的感测电路和包括该感测电路的源极驱动器可以减小面板负载对积分器的性能的影响,并且可以通过排除积分器的反馈电容器来减小芯片面积。

[0072]

此外,在根据实施方式的感测电路中,与传统技术相比,放大器电路的参考电压可以设置为较低的电平。

[0073]

此外,根据实施方式的感测电路和源极驱动器可以精确地感测像素的信号,无论多个通道的数量是否增加。

[0074]

此外,在根据实施方式的感测电路和源极驱动器中,放大器电路配置成输出电流量小于输入电流的输出电流。因此,用于对输出电流进行采样的采样电容器可以设计成具有小的电容量。因此,可以使用小面积的采样电容器来实施感测电路和源极驱动器,并且可以减小芯片面积。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。