1.本发明属于功率半导体器件领域,涉及绝缘栅双极型晶体管(igbt),特别是逆导型绝缘栅双极型晶体管(rc-igbt)器件以及其制备方法。

背景技术:

2.逆导型绝缘栅双极型晶体管(rc-igbt)器件,由于在同一个元胞中集成了绝缘栅双极型晶体管(igbt)和续流二极管(fwd),相比于分立igbt和fwd通过键合线封装集成为单个器件来说,能带来器件的功率密度提升、寄生电感降低和芯片面积利用率增加等优势,在功率模块中得到更多的应用。rc-igbt凭借上述高集成度的优势,已在软开关电路特别是感应加热应用中普及,但由于受到开关频率和开关损耗等限制,使其无法进一步在硬开关应用领域大规模推广。其中fwd反向恢复损耗过大是rc-igbt亟待解决的功耗问题之一。

3.rc-igbt元胞从背面结构上,可以将重掺杂p

集电区部分视为igbt元胞,将重掺杂n

集电区部分视为fwd元胞,如图1所示。由于rc-igbt元胞背面局部掺杂的差异,导致其在igbt模式正向导通时存在折回现象(snap back),会使得器件工作时电流易出现局部聚集,降低应用时的可靠性。现有技术普遍采用多个igbt元胞并联一个fwd元胞的结构来消除折回现象,而正面结构则均采用igbt的金属-氧化物-半导体结构(也称mos结构)。igbt正面结构中的p区为保证耐压与抑制闩锁效应,通常采用高掺杂p型区域,该高掺杂p型区域作为fwd元胞续流导通时的阳极,空穴注入效率过高,导致fwd元胞反向恢复时产生的反向恢复损耗过大,限制了器件整体开关功耗的降低。

4.为降低fwd元胞反向恢复损耗,现有技术中有采用正面局部区域寿命控制的方案。具体做法是:在正面pn结附近,采用h

或he

2

粒子注入的方式,在局部区域引入缺陷,增强载流子复合过程。fwd元胞正向导通时,可减小空穴的注入效率,进而降低反向恢复前漂移区内载流子数量,实现载流子分布正面低、背面高的分布;这种载流子分布,在fwd元胞反向恢复时能够实现又软又快的特性,可以减小反向恢复时间和反向恢复电荷,使得rc-igbt的反向恢复损耗降低。但上述技术方案存在高温漏电大、igbt模式下导通损耗增大等问题。

5.现有技术另一种方案是将rc-igbt的igbt元胞和fwd元胞正面结构独立设计,主要特点是可单独优化fwd元胞正面空穴注入效率,同时将对igbt元胞正面空穴注入效率的影响降低。具体做法是采用现有分立fwd器件正面结构,如speed(self-adjusting p emitter efficiency diode)结构。该技术方案原理是在正面p区内引入金属-p型半导体形成的肖特基结,增加正面空穴注入的势垒,不改变电子输运到正面发射极的过程。该技术方案可通过改变正面p型区掺杂浓度和发射极金属功函数,改变肖特基势垒高度,以调整空穴注入效率;但该技术中的参数设计受制于rc-igbt工艺过程,对反向恢复功耗的降低幅度有限制。业界还提出通过igbt元胞栅极控制的方法,在fwd元胞反向恢复之前将igbt元胞栅极开启,通过将正面电子电流导出的方式,降低反向恢复时载流子数量;但该方案使得栅驱动控制复杂,同时需要额外器件进行换向检测,不利于控制系统可靠性和成本。

6.根据上述现有rc-igbt反向恢复损耗降低技术所存在的问题,需要提供创新的器

件结构,在实现降低rc-igbt反向恢复损耗基础上,控制泄漏电流、保证igbt元胞性能不退化,以满足整个rc-igbt器件在恶劣应用环境下高可靠性的要求。

技术实现要素:

7.为解决上述提到的问题,本发明提出一种功率半导体器件,所述的器件包括有位于底部的集电极,位于集电极之上的交错排布的重掺杂第一导电类型阴极区和重掺杂第二导电类型集电区,位于重掺杂第一导电类型阴极区和重掺杂集电区(上的第一导电类型缓冲层,位于所述的第一导电类型缓冲层上的第一导电类型漂移区,以及位于器件顶部的发射极电极,所述的发射极电极和第一导电类型漂移区相隔;所述的第一导电类型漂移区上方设有一个以上的正面结构单元,每个所述的正面结构单元包括有:沟槽栅结构、与沟槽栅结构毗邻的第二导电类型基区、位于第二导电类型基区一侧隔断沟槽辅助栅结构和第二导电类型基区的轻掺杂第二导电类型基区、沟槽辅助栅结构和位于沟槽辅助栅结构底部的浮空fp区,所述的沟槽栅结构包括有第一栅介质层和第一栅电极;所述的浮空fp区与第二导电类型基区、轻掺杂第二导电类型基区隔断;所述第二导电类型基区上表面设有第一重掺杂第一导电类型发射区和重掺杂第二导电类型发射区,所述的轻掺杂第二导电类型基区上表面设有第二重掺杂第一导电类型发射区,所述的第一重掺杂第一导电类型发射区和第二重掺杂第一导电类型发射区通过所述的重掺杂第二导电类型发射区分隔;所述沟槽栅结构上表面设有隔离第一栅介质层和发射极电极的绝缘介质层;所述的第二栅电极、重掺杂第一导电类型发射区和重掺杂第二导电类型发射区通过发射极电极互连,所述发射极电极将所有的正面结构单元互连。

8.所述第一重掺杂第一导电类型发射区、第二重掺杂第一导电类型发射区、轻掺杂第二导电类型基区和第一导电类型漂移区构成穿通型三极管结构。

9.所述的第二导电类型基区、第一导电类型漂移区和浮空fp区构成jfet结构。

10.进一步地,所述重掺杂第一导电类型发射区掺杂浓度大于1e18cm-3

,且与发射极电极形成欧姆接触,通过调整所述轻掺杂第二导电类型基区结深和掺杂浓度,以改变三极管的穿通电压在0.3-1v。

11.进一步地,所述的沟槽辅助栅结构包括第二栅电极和第二栅介质层,所述的浮空fp区通过第二栅介质层和第二栅电极隔离,所述的第二栅介质层和与轻掺杂第二导电类型基区通过第二栅介质层隔离。

12.进一步地,所述的第二栅介质层材料为氧化硅、氧化铝、氮化硅和/或重掺杂多晶硅。

13.进一步地,所述的沟槽辅助栅结构包括有第二栅介质层和部分填充在沟槽内的发射极电极,所述的第二栅介质层和与轻掺杂第二导电类型基区通过第二栅介质层隔离,所述的浮空fp区的上表面与发射极电极相接触。

14.进一步地,所述的沟槽辅助栅结构形貌为倒梯形,所述的重掺杂第一导电类型发射区和轻掺杂第二导电类型基区按照倒梯形形貌设于沟槽辅助栅结构侧壁并向下延伸和所述的浮空fp区接触。

15.进一步地,沟槽栅结构为形貌为倒梯形。

16.进一步地,所述轻掺杂第二导电类型基区的掺杂浓度远小于第二导电类型基区和

浮空fp区,但数值上大于第一导电类型漂移区的掺杂浓度。

17.进一步地,所述栅介质层厚度小于栅电极的宽度,约为0.1-2微米,所述栅介质层材料为二氧化硅、氮化硅等绝缘材料。

18.进一步地,所述沟槽栅结构和沟槽辅助栅结构深度近似,在2-5微米之间。

19.进一步地,所述第二导电类型基区和浮空fp区掺杂剂量相同,与发射极电极形成肖特基接触。

20.进一步地,所述的重掺杂第二导电类型发射区横向宽度小于第二导电类型基区,占比在10%-90%范围内且可调。

21.进一步地,所述重掺杂第二导电类型发射区深度小于2微米,处于第二导电类型基区和第一导电类型漂移区形成pn结耗尽区之外。

22.进一步地,所述第二导电类型基区、第一导电类型漂移区和浮空fp区形成jfet结构的n型沟道宽度在0.1微米-2微米之间,使rc-igbt在耐压时jfet沟道完全夹断,正向导通时jfet沟道形成。

23.进一步地,所述沟槽栅结构、沟槽辅助栅结构形貌为倒梯形,且侧壁和底部由重掺杂第一导电类型发射区和浮空fp区完全包围。

24.进一步地,在同一元胞内,所述重掺杂第一导电类型发射区、轻掺杂第二导电类型基区、沟槽辅助栅结构和浮空fp区结构交替排列,以增加穿通型npn三极管结构密度。

25.进一步地,所述的浮空fp区为u型形貌,向上延伸至表面重掺杂第一导电类型发射区底部,所述浮空fp区形貌由离子注入角度和热推结时间决定。

26.本发明还提供上述功率半导体器件的制作方法,所述的制作方法包括如下的步骤:第一,形成第一导电类型漂移区,在所述第一导电类型漂移区上表面形成沟槽栅结构和沟槽辅助栅结构;通过控制刻蚀能量、刻蚀时间和钝化时间调整沟槽栅结构和沟槽辅助栅结构形貌;第二,在所述沟槽栅结构和沟槽辅助栅结构上表面形成掩蔽层保护沟槽栅结构侧壁,同时形成离子注入窗口,通过离子注入并高温推结形成第二导电类型基区和浮空fp区,高温推结的温度为900℃-1200℃;浮空fp区为u型形貌,u型形貌通过调整离子注入角度和热推结时间获得,位于沟槽辅助栅结构左右侧壁的肖特基接触通过在开接触区时采用湿法刻蚀去除掉沟槽辅助栅结构左右侧壁的栅介质层实现第三,在所述沟槽栅结构和沟槽辅助栅结构内壁形成栅介质层,之后形成栅电极;第四,在所述第二导电类型基区和沟槽辅助栅结构中间、第二导电类型基区毗邻沟槽栅结构的上表面形成轻掺杂第二导电类型基区,其次进行离子注入形成重掺杂第一导电类型发射区;所述的轻掺杂第二导电类型基区浓度远低于第二导电类型基区;第五,在所述第二导电类型基区上表面,形成重掺杂第二导电类型发射区离子注入窗口,之后进行离子注入;然后在器件上表面形成绝缘介质层;在所述绝缘介质层表面通过干法刻蚀形成接触孔,之后以金属溅射工艺形成正面发射极电极;或者将所述沟槽辅助栅结构表面绝缘介质层去除,之后再依次去除沟槽辅助栅结构内

填充的栅电极和栅介质层,直至出现浮空fp区上表面,接着将所述重掺杂第一导电类型发射区和重掺杂第二导电类型发射区表面绝缘介质层通过干法刻蚀形成接触孔,再以金属溅射工艺形成正面发射极电极,将沟槽辅助栅结构内部填充,直至正面发射极电极与浮空fp区上表面互连接触;第六,对器件背面进行处理形成第一导电类型缓冲层、重掺杂第二导电类型集电区、重掺杂第一导电类型阴极区和集电极。

27.具体来说包括有:对器件背面进行厚度减薄,之后形成第一导电类型缓冲层;接着在器件背面利用掩蔽层依次进行局部离子注入,分别形成交错排布的重掺杂第二导电类型集电区和重掺杂第一导电类型阴极区,最后在器件背面形成背面集电极。

28.相比于现有技术,本发明的有益效果在于:(1)通过引入穿通型npn三极管对正面电子电流的抽取,实现rc-igbt在续流时发射区空穴注入效率调整,相比于肖特基结和单个pn结势垒高度调整,穿通npn三极管势垒高度易调整,更易实现反向恢复损耗降低。

29.(2)正面电子抽取的势垒高度由pn结耗尽区构成,同时有jfet结构对高电场的屏蔽作用,可有效降低高电场下的泄漏电流。

30.(3)可实现与局部寿命控制技术接近的反向恢复损耗降低效果,降低了高温下的泄漏电流、工艺难度和制造成本。

31.(4)通过改变rc-igbt正面沟槽的密度和形貌,实现对穿通型npn面积和位置的调整,进而改变对电子抽取、正面空穴注入效率,增加了器件设计灵活性和设计维度。

32.(5)所述结构同时适应rc-igbt中的igbt元胞和fwd元胞,无需单独分区设计,在降低rc-igbt反向恢复损耗的同时,不会使rc-igbt的igbt工作模式下的特性退化。

附图说明

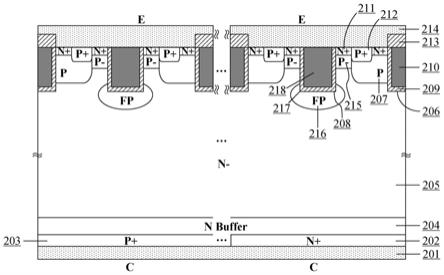

33.图1为现有技术的具有沟槽辅助栅的rc-igbt器件结构的横切面示意图。

34.图2为根据本发明的第一实施例的rc-igbt器件结构的横切面示意图。

35.图3至图8为根据本发明的第一实施例的主要制造步骤的横切面示意图。

36.图9为根据本发明的第二实施例的rc-igbt器件结构的横切面示意图。

37.图10至图17为根据本发明的第二实施例的主要制造步骤的横切面示意图。

38.图18为根据本发明的第三实施例的rc-igbt器件结构的横切面示意图。

39.图19为根据本发明的第四实施例的rc-igbt器件结构的横切面示意图。

具体实施方式

40.本发明提供一种rc-igbt器件及其制备方法,并有以下具体实施例。

41.需要指出的是,在以下实施例的说明中,rc-igbt的半导体衬底被认为由硅(si)材料构成。但是,该衬底亦可由其他任何适合该器件制造的材料构成,如碳化硅(sic),锗(ge)等。

42.需指出的是,本文件中所述的对应位置词如“上”、“下”、“左”、“右”、“前”、“后”是对应于参考图示的相对位置,具体实施中并不限制固定方向,本器件的正面结构由多个可重复型单元构成,以下主要阐述最小正面结构单元。在实际实施中,本器件正面结构中的

igbt元胞部分可由分立igbt现有技术的元胞结构替代;本器件结构不限制于硅基rc-igbt,对于硅基金属场效应晶体管(mosfet)、碳化硅基mosfet、碳化硅基rc-igbt同样适用。

43.实施例1图2为根据本发明的第一实施例的一种rc-igbt器件的横切面示意图。该器件结构具有:位于底部的集电极201,位于集电极201之上的重掺杂n

阴极区202和重掺杂p

集电区203交错排布,n型缓冲层204位于所述重掺杂n

阴极区202和重掺杂p

集电区203之上,n型漂移区205位于所述n型缓冲层204之上;所述n型漂移区205上表面为多个重复型正面结构,最小正面结构单元包括:沟槽栅结构206、p型基区207、沟槽辅助栅结构208、轻掺杂p-型基区215和浮空fp区216;所述沟槽栅结构206依次由第一栅介质层209和第一栅电极210填充,所述p型基区207与沟槽栅结构206毗邻,和所述第一栅电极210之间通过第一栅介质层209隔离;所述沟槽辅助栅结构208依次由第二栅介质层217和第二栅电极218构成,通过轻掺杂p-型基区215与p型基区207隔断;所述浮空fp区216位于沟槽辅助栅结构208底部,与沟槽辅助栅结构208内的第二栅电极218通过第二栅介质层217隔离,与p型基区207、轻掺杂p-型基区215通过n型漂移区205隔断;所述p型基区207和轻掺杂p-型基区215上表面均有重掺杂n

型发射区211,所述重掺杂n

型发射区211被p型基区207上表面重掺杂p

型发射区212分隔;所述沟槽栅结构206上表面有绝缘介质层213,所述绝缘介质层213将发射极电极214与沟槽栅结构206内的栅电极210隔离;所述沟槽辅助栅结构208内第二栅电极218、重掺杂n

型发射区211和重掺杂p

型发射区212通过发射极电极214互连,所述发射极电极214将多个重复型正面结构互连。特别地,所述重掺杂n

型发射区211、轻掺杂p-型基区215和n型漂移区205构成穿通型npn三极管结构,所述p型基区207、n型漂移区205和浮空fp区216构成jfet结构。

44.所述重掺杂n

型发射区211掺杂浓度大于1e18cm-3

,与发射极电极214形成欧姆接触。通过调整所述轻掺杂p-型基区215结深和掺杂浓度,以改变npn三极管的穿通电压在0.3-1v。

45.所述轻掺杂p-型基区215掺杂浓度远小于p型基区207和浮空fp区216,但数值上大于n型漂移区205掺杂浓度。所述栅介质层209厚度小于栅电极210的宽度,约为0.1-2微米,栅介质层材料为二氧化硅、氮化硅等绝缘材料。所述沟槽栅结构206和沟槽辅助栅结构208深度近似,在2-5微米之间。

46.所述p型基区207和浮空fp区216掺杂剂量相同,与发射极电极214形成肖特基接触。所述重掺杂p

型发射区212掺杂浓度大于1e18cm-3

,与发射极电极214形成欧姆接触;重掺杂p

型发射区212横向宽度小于p型基区207,占比在10%-90%范围内可调;进一步地,所述重掺杂p

型发射区212深度小于2微米,处于p型基区207和n型漂移区205形成pn结耗尽区之外。所述p型基区207、n型漂移区205和浮空fp区216形成jfet结构的n型沟道宽度在0.1微米-2微米之间,使rc-igbt在耐压时jfet沟道完全夹断,正向导通时jfet沟道形成。

47.在同一元胞内,所述重掺杂n

型发射区211、轻掺杂p-型基区215、沟槽辅助栅结构208和浮空fp区216结构交替排列,以增加穿通型npn三极管结构密度。

48.此外,本发明亦提供第一实施例的器件的制造方法,如图3-8所示:首先,形成n型漂移区205,在所述n型漂移区205上表面形成掩蔽层通过干法刻蚀的方式形成垂直型沟槽栅结构206和沟槽辅助栅结构208,沟槽深度在2-5微米,如图3所示。

49.接着,如图4所示,在所述沟槽栅结构206和沟槽辅助栅结构208上表面形成掩蔽层

保护沟槽栅结构侧壁,同时形成离子注入窗口,通过离子注入并高温推结形成p型基区207和浮空fp区216,一种常用的p型注入的离子为硼。

50.接着,如图5所示,在所述沟槽栅结构206和沟槽辅助栅结构208内壁通过高温热生长或化学气相沉积工艺形成栅介质层,之后通过化学气相沉积工艺形成栅电极,栅介质层材料可以是氧化硅、氧化铝、氮化硅,所述栅电极材料可以是重掺杂多晶硅。

51.接着,如图6所示,在所述p型基区207和沟槽辅助栅结构208中间位置,以及p型基区207毗邻沟槽栅结构206的上表面,通过干法刻蚀掩蔽层形成穿通型npn三极管离子注入窗口;首先进行p型离子注入并高温推结形成轻掺杂p-型基区215,一种常用的p型注入的离子为硼,其次进行n型离子注入形成重掺杂n

型发射区211,一种常用的n型注入的离子为砷;所述轻掺杂p-型基区215浓度远低于p型基区207,对p型基区207和重掺杂n

型发射区211掺杂浓度的改变可忽略不计。

52.接着,如图7所示,在所述p型基区207上表面,通过干法刻蚀掩蔽层形成重掺杂p

型发射区212离子注入窗口,之后进行p型离子注入,一种常用的p型注入的离子为硼;在器件上表面通过高温热生长或化学气相沉积工艺形成绝缘介质层213,在所述绝缘介质层213表面通过干法刻蚀形成接触孔,之后以金属溅射工艺形成正面发射极电极214。

53.最后,如图8所示,通过减薄工艺对器件背面厚度减薄,之后通过n型杂质扩散或离子注入工艺形成n型缓冲层204;接着在器件背面利用掩蔽层依次进行局部p型和n型离子注入,分别形成交错排布的重掺杂p

集电区203和重掺杂n

阴极区202,最后在器件背面通过金属溅射工艺形成背面集电极201。

54.实施例2图9为根据本发明的第二实施例的一种rc-igbt器件的横切面示意图。相比于图2中所示的第一实施例中的器件结构,第二实施例中的器件结构的不同之处在于浮空fp区316上表面与沟槽辅助栅结构308底部的发射极电极314直接相连,而图2中第一实施例浮空fp区216与发射极电极214之间形成肖特基接触。第二实施例这种设计增加了rc-igbt正面发射区的面积和空穴通路,肖特基接触可以控制空穴的注入效率,有利于降低器件导通压降和反向恢复损耗。

55.该器件结构具有:位于底部的集电极301,位于集电极301之上的重掺杂n

阴极区302和重掺杂p

集电区303交错排列,n型缓冲层304位于所述重掺杂n

阴极区302和重掺杂p 集电区303之上,n型漂移区305位于所述n型缓冲层304之上;所述n型漂移区305上表面为多个重复型正面结构,最小正面结构单元包括:沟槽栅结构306、p型基区307、沟槽辅助栅结构308、轻掺杂p-型基区315和浮空fp区316;所述沟槽栅结构306依次由第一栅介质层309和第一栅电极310填充,所述p型基区307与沟槽栅结构306毗邻,和所述第一栅电极310之间通过栅介质层309隔离;所述沟槽辅助栅结构308依次由第二栅介质层317和部分填充在沟槽内的发射极电极318构成,通过轻掺杂p-型基区315与p型基区307隔断,所述沟槽辅助栅结构308内的发射极电极314与轻掺杂p-型基区315通过第二栅介质层309隔离;所述浮空fp区316位于沟槽辅助栅结构308底部,与沟槽辅助栅结构308底部的发射极电极314直接相连,与沟槽辅助栅结构308侧壁的发射极电极314通过栅介质层309隔离;所述浮空fp区316与p型基区307、轻掺杂p-型基区315通过n型漂移区305隔断;所述p型基区307和轻掺杂p-型基区315上表面均有重掺杂n

型发射区311,所述重掺杂n

型发射区311被p型基区307上表面重掺

杂p

型发射区312分隔;所述沟槽栅结构306上表面有绝缘介质层313,所述绝缘介质层313将发射极电极314与沟槽栅结构306内的第一栅电极310隔离;所述沟槽辅助栅结构308内发射极电极314、重掺杂n

型发射区311和重掺杂p

型发射区312通过器件上表面发射极电极314互连,所述发射极电极314将多个重复型正面结构互连。特别地,所述重掺杂n

型发射区311、轻掺杂p-型基区315和n型漂移区305构成穿通型npn三极管结构,所述p型基区307、n型漂移区305和浮空fp区316构成jfet结构。

56.该器件的主要工作原理及其他关键结构参数与第一实施例中的器件一致,在此不再赘述。

57.此外,本发明亦提供第二实施例的器件的制造方法,如图10-17所示:首先,形成n型漂移区305,在所述n型漂移区305上表面形成掩蔽层通过干法刻蚀的方式形成垂直型沟槽栅结构306和沟槽辅助栅结构308,沟槽深度在2-5微米,如图10所示。

58.接着,如图11所示,在所述沟槽栅结构306和沟槽辅助栅结构308上表面形成掩蔽层保护沟槽栅结构侧壁,同时形成离子注入窗口,通过离子注入并高温推结形成p型基区307和浮空fp区316,一种常用的p型注入的离子为硼。

59.接着,如图12所示,在所述沟槽栅结构306和沟槽辅助栅结构308内壁通过高温热生长或化学气相沉积工艺形成栅介质层,之后通过化学气相沉积工艺形成第二栅介质层317和部分填充在沟槽内的发射极电极318,栅介质层材料可以是氧化硅、氧化铝、氮化硅,所述栅电极材料可以是重掺杂多晶硅。

60.接着,如图13所示,在所述p型基区307和沟槽辅助栅结构308中间位置,以及p型基区307毗邻沟槽栅结构306的上表面,通过干法刻蚀掩蔽层形成穿通型npn三极管离子注入窗口;首先进行p型离子注入并高温推结形成轻掺杂p-型基区315,一种常用的p型注入的离子为硼,其次进行n型离子注入形成重掺杂n

型发射区311,一种常用的n型注入的离子为砷;所述轻掺杂p-型基区315浓度远低于p型基区307,对p型基区307和重掺杂n

型发射区311掺杂浓度的改变可忽略不计。

61.接着,如图14所示,在所述p型基区307上表面,通过干法刻蚀掩蔽层形成重掺杂p

型发射区312离子注入窗口,之后进行p型离子注入,一种常用的p型注入的离子为硼;之后,在器件上表面通过高温热生长或化学气相沉积工艺形成绝缘介质层313。

62.接着,如图15所示,将所述沟槽辅助栅结构308表面绝缘介质层313通过干法刻蚀去除,之后使用干法或湿法刻蚀,依次去除沟槽辅助栅结构308内填充的第二栅介质层317和部分填充在沟槽内的发射极电极318,直至出现浮空fp区316上表面。

63.接着,如图16所示,将所述重掺杂n

型发射区311和重掺杂p

型发射区312表面绝缘介质层313通过干法刻蚀形成接触孔,之后以金属溅射工艺形成正面发射极电极314,将沟槽辅助栅结构308内部填充,直至正面发射极电极314与浮空fp区316上表面互连接触。

64.最后,如图17所示,通过减薄工艺对器件背面厚度减薄,之后通过n型杂质扩散或离子注入工艺形成n型缓冲层304;接着在器件背面利用掩蔽层依次进行局部p型和n型离子注入,分别形成交错排布的重掺杂p

集电区303和重掺杂n

阴极区302,最后在器件背面通过金属溅射工艺形成背面集电极301。

65.实施例3

图18为根据本发明第三实施例的rc-igbt器件元胞结构横截面示意图。相比于本发明第二实施例的器件结构而言,第三实施例的器件结构还具有以下特点:沟槽栅结构406和沟槽辅助栅结构408形貌为倒梯形,轻掺杂p-型基区415和其表面重掺杂n

型发射区411均位于沟槽辅助栅结构408左右侧壁。这种设计增加了沟槽辅助栅结构左右侧壁作为正面发射区面积,增大了导电面积,有利于提升穿通型npn三极管结构在正面的面积比,从而增强rc-igbt续流时的正面fwd元胞对电子的抽取,有利于降低反向恢复损耗。对于制造方法而言,通过采用bosch工艺控制刻蚀(etching)能量、刻蚀(etching)时间和钝化(passivation)时间实现沟槽栅结构406和沟槽辅助栅结构408形貌控制;位于沟槽辅助栅结构408左右侧壁的穿通型npn三极管结构,可通过在开接触区时通过湿法刻蚀去除掉沟槽辅助栅结构408左右侧壁的栅介质层实现。

66.实施例4图19为根据本发明第四实施例的rc-igbt器件元胞结构横截面示意图。相比于本发明第二实施例的器件结构而言,第四实施例的器件结构还具有以下特点:浮空fp区516为u型形貌,将沟槽辅助栅结构508左右侧壁和底部三面全包围,且均与发射极电极514互连形成肖特基接触,p型基区(507)、n型漂移区(505)和浮空fp区516构成jfet结构的电子沟道更窄。这种设计增加了jfet结构在rc-igbt耐压时对高电场的屏蔽效果,有利于降低泄漏电流大小;同时沟槽辅助栅结构508左右侧壁为发射区导电面积,特别是空穴的导电面积,有利于降低rc-igbt正向导通时的压降。

67.对于制造方法而言,所述浮空fp区516的u型形貌由离子注入角度和热推结时间控制,位于沟槽辅助栅结构508左右侧壁的肖特基接触,可通过在开接触区时通过湿法刻蚀去除掉沟槽辅助栅结构508左右侧壁的栅介质层509实现。

68.本发明的半导体器件的工作原理解释如下:以rc-igbt为例,当rc-igbt续流导通时,即栅极电压小于零、发射极至集电极电压vec高于导通压降时,此时rc-igbt中的fwd元胞处于小电流导通状态,igbt元胞正面存在空穴注入,对应背面几乎不导通。图1所示的现有rc-igbt器件结构,为保证igbt元胞部分的耐压与抑制闩锁效应,正面结构中的p区通常采用重掺杂,此时空穴注入效率过高,导致fwd元胞在随后的反向恢复过程损耗增大。

69.所提出结构的穿通npn三极管穿通压降经典值为0.7v,此时正面结构中进行空穴注入的主要是重掺杂p

型发射区、p型基区和浮空fp区;进一步的,当浮空fp区与发射极电极接触时,由于材料功函数差异使得浮空fp区、p型基区均可以与发射极电极形成肖特基接触。此肖特基结的极性特点使得fwd元胞续流导通时的压降,部分分布到肖特基结两端,从而使p型基区和浮空fp区电位下降,进而空穴的注入效率降低,而所形成的肖特基结对p型区内电子扩散到发射极电极的过程没有影响。所提结构相比于现有rc-igbt中的fwd元胞结构,同时引入了对漂移区内电子抽取的穿通型npn三极管结构,进而能降低正面空穴的注入效率,将发射极空穴电流转化为电子漂移电流,不会使导通压降显著增大。所提结构中的穿通型npn三极管在穿通时,npn的轻掺杂p-型基区电场强度大于1e4 v/cm,此时电子接近于达到速度饱和,且在轻掺杂p-型基区结深较浅时还会出现载流子速度过冲现象。此时漂移区靠近正面位置的电子,在npn轻掺杂p-型基区高电场作用下,以饱和速度输运到发射极电极,使得更多的发射区空穴电流转换为电子漂移电流,降低空穴的注入和漂移区内载流子

数量;进而使得小电流导通时,漂移区内载流子分布呈现正面

‘

低’背面

‘

高’的分布。

70.在所提结构的fwd元胞进入反向恢复时,即栅极电压小于零、发射极至集电极电压vec逐渐减为零并开始反向时。漂移区内载流子整体数量降低同时具有正面载流子浓度

‘

低’的分布特点,使得反向恢复电荷减小,同时有利于漂移区内的pn结耗尽区迅速展宽,将载流子扫出以承受耐压,从而减小反向恢复时间;漂移区内载流子背面

‘

高’的分布特点,使得电流在拖尾阶段时有足够的载流子实现续流,能避免出现反向恢复电流骤然减小的现象,抑制emi噪声的产生和降低反向恢复损耗。

71.在rc-igbt器件处于耐压状态时,即栅极电压小于零、发射极至集电极电压vec小于零。p型基区、浮空fp区或相邻的浮空fp区之间与n型漂移区形成的jfet结构,会将jfet沟道区夹断,进而屏蔽高电场对穿通型npn三极管的影响;同时穿通时耗尽区为pn结,其对高电场和高温更不敏感,泄漏电流不会显著增大。所提rc-igbt结构利用现有技术中的沟槽辅助栅结构,引入浮空fp区和穿通型npn三极管结构,与现有rc-igbt工艺兼容,同时不会影响rc-igbt的igbt元胞部分开关过程。

72.进一步的,当穿通型npn三极管位置调整到倒梯形沟槽辅助栅结构侧壁时,或者浮空fp区为u型形貌时;将有效增加发射区导电面积和穿通型npn三极管电子抽取能力,有利于减小导通压降和提升器件正向抗浪涌电流能力。随着槽栅密度的增加,穿通型npn三极管对正面电子抽取的面积增大,更有利于降低漂移区内正面载流子分布,进而进一步降低rc-igbt反向恢复损耗。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。