一种基于fpga的高速delay-fxlms滤波器设计方法

技术领域

1.本发明属于数字信号处理领域,对自适应滤波器进行算法和硬件结构进行优化,研究易于硬件实现的自适应滤波算法,提出了一种基于fpga的高速delay-fxlms滤波器设计方法。

背景技术:

2.目前,有源噪声控制(active noise control,anc)系统中使用最流行的自适应算法是滤波-x最小均方(filtered-x least mean square,fxlms)算法,fxlms算法因物理机理明晰、运算量小、实现简单成为有源噪声控制中的“基准”算法而被广泛应用。anc系统的核心是自适应算法和自适应滤波器,自适应滤波器在系统识别、逆建模、线性预测以及干扰对消领域具有广泛的应用。随着集成电路技术的发展,传统靠软件实现的算法通常不能满足所需的处理速度,fpga(field programmable gate array,现场可编程逻辑门阵列)因其功能强大设计灵活广泛应用于在语音信号处理、网络通信、音视频处理以及密码等领域。

3.现有主动噪声控制算法中,主要以matlab仿真阶段为主,且dfxlms算法本身存在自适应延迟m过大和系统输出滞后的问题,从而导致算法收敛性下降。本发明侧重于对自适应滤波器进行算法和硬件结构优化,研究易于硬件实现的自适应滤波算法,从算法的角度出发,采用延时分解算法来解决自适应延迟过大和系统输出滞后问题;从硬件设计的角度出发,在算法收敛性不变的前提下减小关键路径,优化电路模块减小寄存器数量;采用硬件共享的思想实现滤波器面积和速度的平衡,因此提出了一种基于fpga的高速delay-fxlms滤波器设计方法。

技术实现要素:

4.本发明旨在解决以上现有技术的问题。提出了一种基于fpga的高速delay-fxlms滤波器设计方法。本发明的技术方案如下:

5.一种基于fpga的高速delay-fxlms滤波器设计方法,其包括以下步骤:

6.首先进行df-dfxlms直接型延迟滤波-x最小均方算法滤波器设计,df-dfxlms滤波器用于音频主动降噪;然后进行tf-rdfxlms转置型重定时滤波-x最小均方算法滤波器设计,tf-rdfxlms滤波器用于高吞吐量实现音频主动降噪;最后进行hs-tf-rdfxlms硬件共享转置形式重定时滤波-x最小均方算法滤波器设计,hs-tf-rdfxlms滤波器用于低功耗和硬件复杂度实现音频主动降噪。

7.进一步的,所述df-dfxlms滤波器具体包括:

8.第一自适应滤波模块,用于实现用于实现n个权值系数与n个输入信号乘法运算,df-dfxlms滤波器迭代运算公式是y(n)=x(n)w

t

(n);y(n)、x(n)、w(n)分别表示为自适应滤波器输出、输入参考信号、滤波器系数向量;

9.第一误差计算模块,用于实现输出信号与噪声信号减法运算,df-dfxlms滤波器误差计算迭代运算公式是e(n-m)=d(n-m)-ys(n-m);e(n-m)、d(n-m)、ys(n-m)分别表示延迟误

差信号、延迟噪声信号、延迟输出信号;n、m分别表示变量、延迟量;

10.第一权值更新模块,由n个进位加法器组成,用来更新n个权值系数,df-dfxlms滤波器权值更新迭代运算公式是

11.w(n 1)=w(n)-2μe(n-m)x

′

(n-m)

12.μ、x

′

(n-m)分别步长因子、延迟次级路径信号;

13.第一次级路径模块,采用lms算法fir滤波器进行模型的自适应辨识,来修正lms算法的误差梯度估计值,df-dfxlms滤波器次级路径迭代运算公式是x'(n)=s(n)*x(n);

14.其中s(n)表示次级信号,*表示卷积运算,x'(n)表示滤波后的输入信号。

15.进一步的,所述tf-rdfxlms滤波器,为了减小自适应滤波器中寄存器数量,同时最小化重定时电路中的时钟周期,将寄存器最小化应用到电路设计中;

16.在重定时中实现节点v的输出边所需要的寄存器数目关系式为:

[0017][0018]

wr(e)表示重定时后的图gr中边e的数量,表示什么含义rv、v分别表示在重定时中实现节点v的输出边所需要的寄存器数目、节点;

[0019]

在重定时后的电路中,总寄存器的代价关系式为:

[0020]

cost=∑rv。

[0021]

进一步的,所述重定时电路,将一个电路g映射到一个重定时的电路gr,边的权重计算关系式为:

[0022]

wr(e)=w(e) r(v)-r(u)

[0023]

其中r(v)是图中每个节点v的值,w(e)是原始图g中边的e的权重,wr(e)是重定时后的图gr中边e的数量;

[0024]

对于重定时图的可行性来说,wr(e)≥0对于gr中的所有边e都是必须保持成立的;令e

1,2

代表从g1到g2的一条边,而e

2,1

代表从g2到g1的一条边;

[0025]

从g1到g2的每条边都增加k个延时为:

[0026]

wr(e

1,2

)≥0=>w(e

1,2

) k≥0

[0027]

类似地,从从g1到g2的每条边e

2,1

都减去k个延时为:

[0028]

wr(e

2,1

)≥0=>w(e

2,1

)-k≥0

[0029]

将上述过程结合起来并考虑割集的所有边可得:

[0030][0031]

其中k是重定时电路中延时量,取值范围是0≤k≤1。

[0032]

进一步的,所述的df-dfxlms自适应滤波器重定时分为三个过程,这三个过程具有一定的先后顺序:

[0033]

①

过程对fir滤波器模块进行重定时操作,由于在误差信号输入端和期望信号输出增加了m个延迟单元,其中的0.25m个延时单元映射到fir滤波器,另外的0.25m个延时单元映射到滤波器的输出端,经过一轮重定时操作,该自适应滤波器的fir电路的关键路径为一个乘法器的延时;

[0034]

②

和

③

过程要对权值更新模块和次级路径模块进行重定时操作,将滤波器输入信

号的0.25m个延时单元分别映射到权值更新部分和次级路径部分,使整个电路的关键路径为一个乘法器。经过重定时后dfxlms自适应滤波器延时单元从m减小到0.5m,关键路径从减小到t

mult

t

add

。t

mult

、t

add

分别表示一个乘法器运行所需时间、一个加法器运行所需时间;

[0035]

进一步的,所述的tf-rdfxlms pm结构主要由三个加法器、三个乘法器、六个寄存器、三个开关和一个门组成,采用脉动阵列设计结构,整个电路的结构对称,在pm结构中,滤波器权值是局部更新,可以通过添加更多pm模块来增加tf-rdfxlms滤波器的阶数,但不会改变滤波器关键路径的大小。

[0036]

进一步的,所述hs-tf-rdfxlms滤波器具体包括:

[0037]

第二自适应滤波模块,用于完成滤波计算,该模块采用fir结构,因为fir滤波器具有具有收敛速度快、稳态误差小等特点;

[0038]

第二误差计算模块,主要由一个转置型fir滤波器加上一个减法器构成,其中乘法部分负责计算n个权系数和n个相应的输入样本值的乘法运算;

[0039]

第二权值更新模块,主要硬件结构主要取决于自适应滤波算法的选择,由n个进位加法器组成,用来更新n个权值系数,其中收敛因子是2的负整数次幂,用相应的乘法运算移位来实现,可以大大地减少运算量和延时;

[0040]

第二次级路径模块,主要作用是修正lms算法的误差梯度估计值,一般采用基于lms算法的fir滤波器进行模型的自适应辨识。

[0041]

进一步的,所述的hs-tf-rdfxlms架构将抽头合并为:4tapx,pm(0)、pm(1)、pm(2)和pm(3)四个抽头合并为一个资源4tap0,将pm(4)、pm(5)、pm(6)和pm(7)四个抽头合并为一个资源4tap1;

[0042]

系统分为两组,其中第一组安排4tap0执行时钟周期0、2、4、6,第二组安排4tap1执行时钟周期1、3、5、7,采用硬件共享的方式实现自适应滤波器电路设计,在确保时钟速度的同时节约硬件资源,从而实现速度/面积权衡;

[0043]

e(n-2)=d(n-2)-ys(n-2)

[0044]

ꢀꢀꢀꢀꢀꢀ

=d(n-2)-s(n)*[w

t

(n-2)x(n-2)]

[0045]

ꢀꢀꢀꢀꢀꢀ

=d(n-2)-w

t

(n-2)x

′

(n-2)

[0046]

其中:d(n-2)为加入自适应延迟后主要噪声信号;s(n)表示次级路径估计信号;*表示卷积运算;y'(n-2)=s(n)*y(n-2)表示滤波后输出信号。

[0047]

第n时刻横向滤波器的权系数是w(n)=[w

l

(n),

…

,w2(n),w1(n)]

t

[0048]

第n时刻参考输入信号是x(n)=[x(n),

…

,x(n-l 2),x(n-l 1)]

t

[0049]

则误差传感器接收到的信号改写为:

[0050][0051]

根据最陡下降法原理递推滤波器系数,通过计算瞬时均方误差来替代计算均方误差是:

[0052]

梯度是

[0053]

所得瞬时均方误差来替代计算均方误差是:

[0054]

w(n 1)=w(n)-2μe(n-2)x

′

(n-2)

[0055]

hs-tf-rdfxlms算法步长界限是:

[0056]

其中:μ为收敛系数;λ

max

为滤波-x信号自相关矩阵的最大特征值。

[0057]

进一步的,根据最陡下降法原理递推滤波器系数,具体步骤包括:

[0058]

步骤1.从待求的最小化函数的最优值参数得一个初始猜测开始;

[0059]

步骤2.求解函数在该点相对于这些参数的梯度;

[0060]

步骤3.以步骤2中所得梯度的反方向移动一步进行参数更新,这对应于代价函数在当前点沿最陡下降方向上的一步;

[0061]

步骤4.重复步骤2和步骤3,直至参数有显著变化为止;

[0062]

所述延时分解算法的步骤具体为:

[0063]

步骤1.对fir滤波器模块进行延时分解,误差信号输出端和期望信号输出的m个延迟单元,将其中的0.25m个延迟单元映射到fir滤波器,另外的0.25m个延迟单元映射到滤波器的输出端;

[0064]

步骤2.对权值更新模块进行延时分解,将滤波器输入信号的0.25m个延迟单元映射到权值更新部分;

[0065]

步骤3.对次级路径模块进行延时分解,将滤波器输入信号的0.25m个延迟单元映射到次级路径部分;

[0066]

本发明的优点及有益效果如下:

[0067]

(1)权利要求5所述的df-dfxlms自适应滤波器设计,采用重定时技术对fir滤波器模块、权值更新模块、次级路径模块操作。由于在误差信号输入端和期望信号输出增加了m个延迟单元,将其中的0.25m个延时单元映射到fir滤波器,另外的0.25m个延时单元映射到滤波器的输出端,将滤波器输入信号的0.25m个延时单元分别映射到权值更新部分和次级路径部分,使整个电路的关键路径为一个乘法器。重定时后dfxlms自适应滤波器延时单元从m减小到0.5m,关键路径从减小到t

mult

t

add

;

[0068]

(2)权利要求6所述的tf-rdfxlms滤波器设计,数据处理模块(processing module,pm)结构主要由三个加法器、三个乘法器、六个寄存器、三个开关和一个门组成,采用脉动阵列设计结构,整个电路的结构对称,在pm结构中,滤波器权值是局部更新,可以通过添加更多pm模块来增加tf-rdfxlms滤波器的阶数,但不会改变滤波器关键路径的大小;

[0069]

(3)权利要求6所述的hs-tf-rdfxlms滤波器设计,将抽头合并为:4tapx,pm(0)、pm(1)、pm(2)和pm(3)四个抽头合并为一个资源4tap0,将pm(4)、pm(5)、pm(6)和pm(7)四个抽头合并为一个资源4tap1;系统分为两组,其中第一组安排4tap0执行时钟周期0、2、4、6,第二组安排4tap1执行时钟周期1、3、5、7,采用硬件共享的方式实现自适应滤波器电路设计,在确保时钟速度的同时节约硬件资源,从而实现速度/面积权衡;

附图说明

[0070]

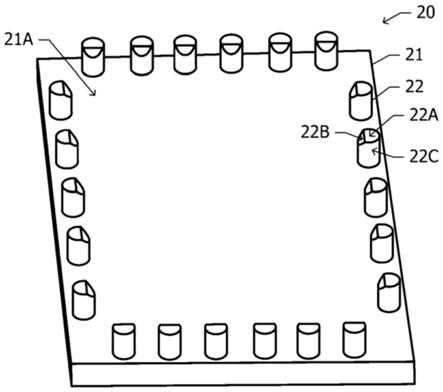

图1是本发明提供优选实施例的df-dfxlms滤波器重定时过程;

[0071]

图2本发明所提供的tf-rdfxlms滤波器设计;

[0072]

图3本发明所提供的hs-tf-rdfxlms滤波器设计;

[0073]

图4本发明所提供的设计的不同自适应滤波器的收敛性。

具体实施方式

[0074]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、详细地描述。所描述的实施例仅仅是本发明的一部分实施例。

[0075]

本发明解决上述技术问题的技术方案是:

[0076]

本发明公开了一种基于fpga的高速delay-fxlms滤波器设计方法。其主要包括三个部分(1)df-dfxlms滤波器设计(2)tf-rdfxlms滤波器设计(3)hs-tf-rdfxlms滤波器设计。

[0077]

如附图1所示,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,所述dfxlms滤波器具体包括:

[0078]

自适应滤波模块,用于实现用于实现n个权值系数与n个输入信号乘法运算,df-dfxlms滤波器迭代运算公式是y(n)=x(n)w

t

(n);

[0079]

误差计算模块,用于实现输出信号与噪声信号减法运算,df-dfxlms滤波器误差计算迭代运算公式是e(n-m)=d(n-m)-ys(n-m);

[0080]

权值更新模块,由n个进位加法器组成,用来更新n个权值系数,df-dfxlms滤波器权值更新迭代运算公式是

[0081]

w(n 1)=w(n)-2μe(n-m)x

′

(n-m)

[0082]

次级路径模块,采用lms算法fir滤波器进行模型的自适应辨识,来修正lms算法的误差梯度估计值,df-dfxlms滤波器次级路径迭代运算公式是x'(n)=s(n)*x(n);

[0083]

其中s(n)表示次级信号,*表示卷积运算,x'(n)表示滤波后的输入信号。

[0084]

如附图2所示,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,所述tf-rdfxlms滤波器,为了减小自适应滤波器中寄存器数量,同时最小化重定时中电路的时钟周期,将寄存器最小化应用到电路设计中。

[0085]

在重定时中实现节点v的输出边所需要的寄存器数目关系式为:

[0086][0087]

在重定时后的电路中,总寄存器的代价关系式为:

[0088]

cost=∑rv

[0089]

进一步的,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,其所述的重定时电路,将一个电路g映射到一个重定时的电路gr,边的权重计算关系式为:

[0090]

wr(e)=w(e) r(v)-r(u)

[0091]

其中r(v)是图中每个节点v的值,w(e)是原始图g中边的e的权重,wr(e)是重定时后的图gr中边e的数量。

[0092]

对于重定时图的可行性来说,wr(e)≥0对于gr中的所有边e都是必须保持成立的。令e

1,2

代表从g1到g2的一条边,而e

2,1

代表从g2到g1的一条边。

[0093]

从g1到g2的每条边都增加k个延时为:

[0094]

wr(e

1,2

)≥0=>w(e

1,2

) k≥0

[0095]

类似地,从从g1到g2的每条边e

2,1

都减去k个延时为:

[0096]

wr(e

2,1

)≥0=>w(e

2,1

)-k≥0

[0097]

将上述过程结合起来并考虑割集的所有边可得:

[0098][0099]

其中k是重定时电路中延时量,取值范围是0≤k≤1。

[0100]

进一步的,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,其所述的df-dfxlms自适应滤波器重定时分为三个过程,这三个过程具有一定的先后顺序:

[0101]

①

过程对fir滤波器模块进行重定时操作,由于在误差信号输入端和期望信号输出增加了m个延迟单元,其中的0.25m个延时单元映射到fir滤波器,另外的0.25m个延时单元映射到滤波器的输出端,经过一轮重定时操作,该自适应滤波器的fir电路的关键路径为一个乘法器的延时;

[0102]

②

和

③

过程要对权值更新模块和次级路径模块进行重定时操作,将滤波器输入信号的0.25m个延时单元分别映射到权值更新部分和次级路径部分,使整个电路的关键路径为一个乘法器。经过重定时后dfxlms自适应滤波器延时单元从m减小到0.5m,关键路径从减小到t

mult

t

add

。

[0103]

如附图3所示,本发明提出的一种一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,其所述的hs-tf-rdfxlms滤波器具体包括:

[0104]

自适应滤波模块,主要用于完成滤波计算,该模块采用fir结构,因为fir滤波器具有具有收敛速度快、稳态误差小等特点;

[0105]

误差计算模块,主要由一个转置型fir滤波器加上一个减法器构成,其中乘法部分负责计算n个权系数和n个相应的输入样本值的乘法运算;

[0106]

权值更新模块,主要硬件结构主要取决于自适应滤波算法的选择,由n个进位加法器组成,用来更新n个权值系数,其中收敛因子是2的负整数次幂,用相应的乘法运算移位来实现,可以大大地减少运算量和延时;

[0107]

次级路径模块,主要作用是修正lms算法的误差梯度估计值,一般采用基于lms算法的fir滤波器进行模型的自适应辨识。

[0108]

进一步的,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,其所述的hs-tf-rdfxlms架构将抽头合并为:4tapx,pm(0)、pm(1)、pm(2)和pm(3)四个抽头合并为一个资源4tap0,将pm(4)、pm(5)、pm(6)和pm(7)四个抽头合并为一个资源4tap1。

[0109]

系统分为两组,其中第一组安排4tap0执行时钟周期0、2、4、6,第二组安排4tap1执行时钟周期1、3、5、7,采用硬件共享的方式实现自适应滤波器电路设计,在确保时钟速度的同时节约硬件资源,从而实现速度/面积权衡。

[0110]

e(n-2)=d(n-2)-ys(n-2)

[0111]

ꢀꢀꢀꢀꢀ

=d(n-2)-s(n)*[w

t

(n-2)x(n-2)]

[0112]

ꢀꢀꢀꢀꢀ

=d(n-2)-w

t

(n-2)x

′

(n-2)

[0113]

其中:d(n-2)为加入自适应延迟后主要噪声信号;s(n)表示次级路径估计信号;*表示卷积运算;y'(n-2)=s(n)*y(n-2)表示滤波后输出信号。

[0114]

第n时刻横向滤波器的权系数是w(n)=[w

l

(n),

…

,w2(n),w1(n)]

t

[0115]

第n时刻参考输入信号是x(n)=[x(n),

…

,x(n-l 2),x(n-l 1)]

t

[0116]

则误差传感器接收到的信号改写为:

[0117][0118]

根据最陡下降法原理递推滤波器系数,通过计算瞬时均方误差来替代计算均方误差是:

[0119]

梯度是

[0120]

所得瞬时均方误差来替代计算均方误差是:

[0121]

w(n 1)=w(n)-2μe(n-2)x

′

(n-2)

[0122]

hs-tf-rdfxlms算法步长界限是:

[0123]

其中:μ为收敛系数;λ

max

为滤波-x信号自相关矩阵的最大特征值。

[0124]

进一步的,本发明提出的一种基于fpga的高速delay-fxlms滤波器设计方法,其特征在于,所述的tf-rdfxlms pm结构主要由三个加法器、三个乘法器、六个寄存器、三个开关和一个门组成,采用脉动阵列设计结构,整个电路的结构非常对称,此发明设计思想有利于后续的布线操作。

[0125]

在pm结构中,滤波器权值是局部更新,可以通过添加更多pm模块来增加tf-rdfxlms滤波器的阶数,但不会改变滤波器关键路径的大小。

[0126]

如附图4,表示设计的不同自适应滤波器的收敛性比较。

[0127]

上述实施例阐明的系统、装置、模块或单元,具体可以由计算机芯片或实体实现,或者由具有某种功能的产品来实现。一种典型的实现设备为计算机。具体的,计算机例如可以为个人计算机、膝上型计算机、蜂窝电话、相机电话、智能电话、个人数字助理、媒体播放器、导航设备、电子邮件设备、游戏控制台、平板计算机、可穿戴设备或者这些设备中的任何设备的组合。

[0128]

还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

[0129]

以上这些实施例应理解为仅用于说明本发明而不用于限制本发明的保护范围。在阅读了本发明的记载的内容之后,技术人员可以对本发明作各种改动或修改,这些等效变

化和修饰同样落入本发明权利要求所限定的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。