1.本发明涉及一种有机电致发光器件,属于光电显示器件技术领域,具体涉及一种采用设置于器件中相邻发光单元之间的特定连接层方案而形成串联结构的有机电致发光器件。

背景技术:

2.有机发光二极管(oled,organic light emission diodes)是一类有机电致发光器件,主要包括阴极、阳极以及位于两电极之间的发光单元,其中发光单元主要有有机半导体材料组成。作为一种电致注入型发光器件,在oled器件的电极施加电压,空穴和阳极注入到有机功能层中,电子从阴极注入到有机功能层中,电子和空穴在发光层复合并形成激子,并最终实现辐射发光。oled器件凭借低能耗、宽视角、可弯折等诸多优势在固态显示和照明技术领域展现出广阔的应用前景。

3.近年来,一种具有串联结构的oled器件受到了广泛的关注。串联oled器件的发光原理与传统的单层oled器件类似,其区别在于串联oled器件由多个发光单元通过连接层串联所构成,其中连接层的作用类似于电极,可以在外电场的驱动下可以成对地产生载流子,这些产生的载流子可以进一步分离并注入到相邻的发光单元中。由于这种串联的器件结构,每注入一个的电子或者空穴,每个发光单元均可以产生光子并实现辐射发光,因此对于含有n个发光单元的串联oled器件而言,其电流效率大约为单层oled器件的n倍。为了实现同样的亮度,串联oled器件所需电流密度大大降低,因而有助于改善oled器件的效率滚降和寿命问题。

4.目前,常见的串联oled器件中主要采用的连接层结构为n型掺杂层/p型掺杂层,n型掺杂层的lumo能级和p型掺杂层的homo能级之间的能级差较小,可以在较低的驱动电压下有效地产生载流子,其中n型掺杂层的掺杂客体主要由低功函数(wf《3.0ev)的碱金属或碱土金属组成,包括锂(li)、钠(na)、钾(k)、铷(rb)、铯(cs)、镁(mg),钙(ca)等。但这类碱金属或碱土金属类的n型掺杂剂在外电场作用容易向p型掺杂层一侧扩散,进而导致器件在工作中驱动电压上升,器件寿命显著下降,严重地影响了器件的效率和稳定性。

5.柯达公司的专利cn100544020a中提出的串联oled器件中设计了位于邻接的电致发光单元之间的中间连接器,该连接器包括n-掺杂的有机层,p-掺杂的有机层和界面层,其中界面层的作用主要是组织n型掺杂剂的有机层和电子接受层材料之间可能的相互扩散。在该专利中强调界面层应当是金属化合物或金属,具体而言该界面层可以选择高功函数的金属包括ti、zr、ti、nb、ta、cr、mo、w、re、fe、ru、os、co、rh、ir、ni、pd、pt、cu、ag、au、zn、al、in、sn或他们的合金,以及钛、锆、蛤、铌、钽、钼、钨、锰、铁、钌、铑、铱、镍、钯、铂、铜、硅、锗这些金属或其组合的化学计量氧化物或非化学计量氧化物、化学计量硫化物或非化学计量硫化物、化学计量碲化物或非化学计量碲化物、化学计量氮化物或非化学计量氮化物、化学计量碳化物或非化学计量碳化物。因此,上述的连接层均由无机材料组成,蒸镀的温度普遍较高,厚度需要精确控制以确保高透过率。

技术实现要素:

6.为此,本发明的目的在于提供一种新的串联oled器件连接层,解决现有技术中存在的问题。具体而言,传统的串联oled器件中连接层为n型掺杂层/p型掺杂层,在器件工作时金属类n型掺杂剂易于扩散进入p型掺杂层和相邻的发光层,从而导致器件驱动电压上升和发光效率的降低。

7.在串联oled器件的n型掺杂层和p型掺杂层之间引入间隔层结构,该间隔层由具有较好的电子传输性能的含氮杂环类电子传输材料构成,这些材料均为有机半导体材料,蒸镀温度较低,可见光范围内透过率较高。这类电子传输材料与碱金属、碱土金属以及部分过渡金属等金属类n型掺杂剂存在较强的相互作用,因而有助于抑制这类金属类n型掺杂剂向p型掺杂层的扩散,进而有效地改善器件工作中的驱动电压上升,提升器件的寿命。

8.具体说,本发明提供了一种串联有机电致发光器件,包括以下结构:阳极、阴极、设置在所述阳极和阴极之间的至少两个电致发光单元、设置在相邻的电致发光单元之间的连接层,所述每个电致发光单元至少包括一个电子传输层和一个有机发光层,其特征在于:所述连接层为多叠层结构,包括n型掺杂层、p型掺杂层和位于二者之间的间隔层;

9.所述p型掺杂层由p型掺杂主体材料和p型掺杂剂组成,所述p型掺杂主体采用具有空穴传输性能的有机材料,所述p型掺杂层中,所述p型掺杂主体采用具有空穴传输性能的有机材料,具体可选自下述化合物:

10.11.[0012][0013]

所述的p型掺杂层中采用的p型掺杂剂主要为具有高功函数的金属氧化物,包括moo3、wo3、v2o5、moo2、co3o4,以及具有强吸电子能力的有机半导体材料,包括cn6-cp、ddq、hatcn、c

60f36

、f4tcnq、f2hcnq、f6tcnnq、tectfcnbn中的一种或几种的混合物,p型掺杂剂的分子结构具体如下:

[0014][0015]

其特征在于,所述的p型掺杂层中,p型掺杂剂的掺杂比例为0.2wt%至30wt%,优选掺杂比例为0.5wt%至10wt%;

[0016]

所述n型掺杂层由n型掺杂主体材料和n型掺杂剂组成,所述n型掺杂主体采用具有电子传输性能的有机材料,所述n型掺杂剂采用碱金属、碱土金属或过渡金属;

[0017]

所述n型掺杂剂采用碱金属、碱土金属或过渡金属;优选的n型掺杂剂选自锂、钠、钾、铷、铯、镁、钙、金、银、铜、铁、镍、铂、钯、钌、镱中的一种或几种的混合物。最优选的n型掺杂剂选自锂、银、铯。

[0018]

所述的n型掺杂层中,n型掺杂主体采用具有电子传输性能的有机材料,具体可选

自下述化合物:

[0019]

[0020]

[0021]

[0022][0023]

所述间隔层采用具有电子传输性能的有机材料,该有机材料不同于所述n型掺杂主体材料。在本说明书中,所述的间隔层主要由电子传输材料组成,该电子传输材料具有较好的电子传输性能,并且分子结构中具有含氮杂环,可以与多种金属类n型掺杂剂存在较强的相互作用,这类电子传输材料具有如下式(1)所示的结构:

[0024]

r1-q-r2

ꢀꢀꢀꢀꢀꢀ

式(1)

[0025][0026]

式(1)中,桥连基团q选自取代或未取代的下述基团中的一种,所述取代基团q中的取代是指被选自氘、氚、氰基、卤素、c1~c10烷基、c3~c10环烷基、硅基、c6~c30芳胺基、c6~c30芳基、c2~c30杂芳基中的一种或者两种的组合所取代,其中为r1与桥连基团q键合的位置,为r2和桥连基团q键合的位置。

[0027]

[0028][0029]

所述r1和r2各自独立地选自取代或未取代的c3~c60杂芳基中的一种,所述杂芳基中含有至少一个氮原子,所述取代的杂芳基中的取代是指被选自氘、氚、氰基、卤素、c1~c10烷基、c3~c10环烷基、硅基、c6~c30芳胺基、c6~c30芳基、c2~c30杂芳基中的一种或者两种的组合所取代,该取代基独立地与相连接的杂芳环连接成环或不连接成环。

[0030]

进一步的,所述r1和r2各自独立地选自取代或未取代的下述基团中的一种:吡啶

基、嘧啶基、三嗪基、喹啉基、异喹啉基、喹喔啉基、喹唑啉基、苯并咪唑基、萘并咪唑基、邻菲罗啉基、苯并噻唑基、苯并噁唑基、吩嗪、二苯并吩嗪、噁二唑基、噻二唑基、三氮唑基、氧杂蒽醌基、蒽醌基,r1和r2中取代或未取代中的取代,是指被选自氘、氚、氰基、卤素、c1~c10烷基、c3~c10环烷基、硅基、c6~c30芳胺基、c6~c30芳基、c2~c30杂芳基中的一种或者两种的组合所取代,该取代基独立地与相连接的芳环或杂芳环连接成环或不连接成环。

[0031]

再进一步的,所述r1和r2各自独立地选自取代或未取代的下述基团中的一种:

[0032]

[0033]

[0034][0035]

继续优选的,本发明的有机电致发光器件中,用作间隔层的电子传输材料如式(1)所示,式(1)中的桥连基团q优选自下述基团中的一种:

[0036][0037]

[0038]

继续优选的,本发明的有机电致发光器件中,用作间隔层的电子传输材料如式(1)所示,式(1)中的r1和r2各自独立地优选自取代或未取代的下述基团中的一种:

[0039][0040]

进一步地,本发明所涉及的可用于制备串联oled器件连接层的间隔层材料的通式化合物中,可以优选出下述具体结构化合物m1-1至m1-76,m2-1至m2-76,m3-1至m3-76,m4-1至m4-76,m5-1至m5-76,m6-1至m6-76,m7-1至m7-76,m8-1至m8-76,m9-1至m9-76,m10-1至m10-76,这些化合物仅为代表性的:

[0041]

[0042]

[0043]

[0044][0045]

[0046]

[0047]

[0048][0049]

[0050]

[0051]

[0052]

[0053][0054]

[0055]

[0056]

[0057]

[0058][0059]

[0060]

[0061]

[0062][0063]

最优选的,本发明的有机电致发光器件中,所述间隔层所采用的具有电子传输性能的有机材料选自下述具体化合物中的至少一种:

[0064]

[0065]

[0066]

[0067]

[0068]

[0069]

[0070]

[0071]

[0072]

[0073][0074]

本发明的这类串联有机电致发光器件中,所述间隔层的总厚度为0.1nm至10nm;更优选间隔层的总厚度为0.3nm至5nm;更优选间隔层的总厚度为0.5nm至1nm。

[0075]

本发明的这类串联有机电致发光器件中,所述电致发光单元的数量为2至6;优选的,所述电致发光单元的数量为2至4。

[0076]

本发明的这类串联有机电致发光器件,所述发光单元中还包括空穴注入层、空穴传输层、电子阻挡层中的至少一层。

[0077]

在本说明书中,所述的“取代或未取代”的基团,可以取代有一个取代基,也可以取代有多个取代基,当取代基为多个时,可以选自不同的取代基,本发明中涉及到相同的表达方式时,均具有同样的意义,且取代基的选择范围均如上所示不再一一赘述。

[0078]

在本说明书中,“各自独立地”表示其主语具有多个时,彼此之间可以相同也可以不同。

[0079]

在本说明书中,若无特别说明,芳基和杂芳基均包括单环和稠环的情况。上述单环芳基是指分子中含有一个或至少两个苯基,当分子中含有至少两个苯基时,苯基之间相互独立,通过单键进行连接,示例性地如苯基、二联苯基、三联苯基等;稠环芳基是指分子中含有至少两个苯环,但苯环之间并不相互独立,而是共用环边彼此稠合起来,示例性地如萘基、蒽基等;单环杂芳基是指分子中含有至少一个杂芳基,当分子中含有一个杂芳基和其他

基团(如芳基、杂芳基、烷基等)时,杂芳基和其他基团之间相互独立,通过单键进行连接,示例性地如吡啶、呋喃、噻吩等;稠环杂芳基是指由至少一个苯基和至少一个杂芳基稠合而成,或,由至少两种杂芳环稠合而成,示例性地如喹啉、异喹啉、苯并呋喃,二苯并呋喃,苯并噻吩,二苯并噻吩等。

[0080]

本发明提出的这种串联oled器件,采用新型的连接层结构,即在n型掺杂层和p型掺杂层之间引入间隔层,这类间隔层由真空蒸镀的电子传输材料组成。该电子传输材料具有如式(1)所述的结构通式,其中q基团主要为π共轭基团,可以将两个受体基团键连起来,可以进一步扩大共轭体系,提升间隔层材料的传输性能,有利于实现较低的驱动电压;其中r1和r2均为电子受体,其中一个比较典型的特征在于其分子中具有含氮杂环,这类杂环的氮原子为sp2杂化,这类具有孤对电子的sp2杂化的氮原子与多种金属类n型掺杂剂之间存在较强的相互作用。因此,在n型掺杂层和p型掺杂层之间引入具有通式(1)结构的电子传输材料作为间隔层可以有效地抑制金属类n型掺杂剂向p型掺杂层的扩散和迁移,进而有效地改善串联有机电致发光器件工作时的电压上升,提升串联oled器件的寿命和稳定性。

[0081]

采用本发明所述的连接层结构的串联oled器件兼具驱动电压低、器件效率高、工作寿命长等诸多优势,能够满足当前显示和照明领域的需求。另外,本发明化合物的制备所需各个原材料易得,合成工艺、后处理及提纯过程简易可靠,制备工艺与现行的制备工艺兼容,适用于科学研究及工业生产。

附图说明

[0082]

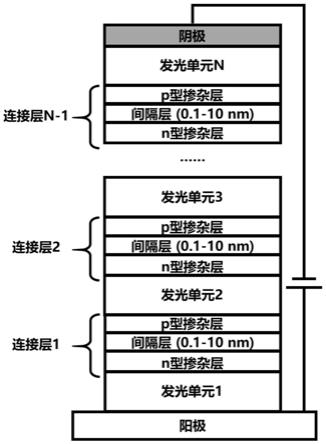

图1为本发明有机电致发光器件的实施例中制备的具有n个发光单元和n-1个连接层的串联有机电致发光器件的结构示意图;

[0083]

图(1)中,包括阳极、阴极、位于两个电极之间的n个发光单元以及位于每两个相邻发光单元之间的连接层,各个连接层中均为层叠结构,均具体包括n型掺杂层、p型掺杂层和位于两者之间的间隔层。

具体实施方式

[0084]

下面通过将本发明中所述的连接层在串联有机电致发光器件中的实际应用效果,并通过测试器件中表现和性能来展示和验证本发明的技术特色和优势。

[0085]

串联oled器件包括阳极、阴极,以及位于两个电极之间的有机材料层。该有机材料又可以分为多个区域。比如,该有机材料层可以包括空穴传输区、发光层、电子传输区。

[0086]

在具体实施例中,在第一电极下方或者第二电极上方可以使用基板。基板均为具有机械强度、热稳定性、防水性、透明度优异的玻璃或聚合物材料。此外,作为显示器用的基板上也可以带有薄膜晶体管(tft)。

[0087]

第一电极可以通过在基板上溅射或者沉积用作第一电极的材料的方式来形成。当第一电极作为阳极时,可以采用铟锡氧(ito)、铟锌氧(izo)、二氧化锡(sno2)、氧化锌(zno)等氧化物透明导电材料和它们的任意组合。第一电极作为阴极时,可以采用镁(mg)、银(ag)、铝(al)、铝-锂(al-li)、钙(ca)、镁-铟(mg-in)、镁-银(mg-ag)等金属或合金以及它们之间的任意组合。

[0088]

有机材料层可以通过真空热蒸镀、旋转涂敷、打印等方法形成于电极之上。用作有

机材料层的化合物可以为有机小分子、有机大分子和聚合物,以及它们的组合。

[0089]

空穴传输区位于阳极和发光层之间。空穴传输区可以为单层结构的空穴传输层(htl),包括只含有一种化合物的单层空穴传输层和含有多种化合物的单层空穴传输层。空穴传输区也可以为包括空穴注入层(hil)、空穴传输层(htl)、电子阻挡层(ebl)中的至少一层的多层结构。

[0090]

空穴传输区的材料可以选自、但不限于酞菁衍生物如cupc、导电聚合物或含导电掺杂剂的聚合物如聚苯撑乙烯、聚苯胺/十二烷基苯磺酸(pani/dbsa)、聚(3,4-乙撑二氧噻吩)/聚(4-苯乙烯磺酸盐)(pedot/pss)、聚苯胺/樟脑磺酸(pani/csa)、聚苯胺/聚(4-苯乙烯磺酸盐)(pani/pss)、芳香胺衍生物等。

[0091]

空穴注入层位于阳极和空穴传输层之间。空穴注入层可以是单一化合物材料,也可以是多种化合物的组合。

[0092]

发光层包括可以发射不同波长光谱的的发光染料(即掺杂剂,dopant),还可以同时包括主体材料(host)。根据不同的技术,发光层材料可以采用荧光电致发光材料、磷光电致发光材料、热活化延迟荧光发光材料等不同的材料。在一个串联oled器件中,可以采用单一的发光技术,也可以采用多种不同的发光技术的组合。这些按技术分类的不同发光材料可以发射同种颜色的光,也可以发射不同种颜色的光。

[0093]

oled有机材料层还包括电子传输区。电子传输区可以为单层结构的电子传输层(etl),即只含有一种化合物的单层电子传输层和含有多种化合物的单层电子传输层。电子传输区也可以为包括电子注入层(eil)、电子传输层(etl)、空穴阻挡层(hbl)中的至少一层的多层结构。

[0094]

在本发明所述的串联oled器件中,每个发光单元由空穴传输区、发光层、电子传输区组成。多个发光单元之间由连接层串联而成,其中发光单元可以是发射红、绿、蓝等单一颜色的单色发光单元,也可以是红、绿、蓝等不同颜色的单色发光单元,还可以是能同时发射红、绿、蓝等不同颜色的单一彩色发光层。

[0095]

本发明所述的串联oled器件中的连接层如图(1)所示,第一个发光单元制备在器件的阳极上,在第一发光单元和第二发光单元之间制备器件的连接层1,连接层中包括n型掺杂层、p型掺杂层和位于两者之间的间隔层,然后再在第二发光单元上制备连接层2、第三发光单元;依据器件结构设计需要,可相应制备n-1连接层,直至完成制备第n个发光单元,最后完成器件阴极的制备。

[0096]

其中n型掺杂层主要由掺杂主体和n型掺杂剂组成。其中掺杂主体主要为电子传输材料,n型掺杂剂主要由碱金属、碱土金属以及部分过渡金属组成,包括锂(li)、钠(na)、钾(k)、铷(rb)、铯(cs)、镁(mg),钙(ca)、金(au)、银(ag)、铜(cu)、铁(fe)、镍(ni)、铂(pt)、钯(pd)、钌(ru)、镱(yb)中的一种或几种的混合物。图(1)中,n型掺杂层中的金属类n型掺杂剂的掺杂比例为0.2wt%至30wt%,优选的掺杂比例为0.5wt%至10wt%。

[0097]

其中所述p型掺杂层由p型掺杂主体材料和p型掺杂剂组成,所述p型掺杂主体采用具有空穴传输性能的有机材料,所述p型掺杂剂采用具有高功函数的金属氧化物或者具有强吸电子能力的有机半导体材料;所述p型掺杂剂采用moo3、wo3、v2o5、moo2、co3o4、cn6-cp、ddq、hatcn、c

60f36

、f4tcnq、f4-r-tcnq、f3-r-tcnq、f2hcnq、f6tcnnq、tectfcnbn中的一种或几种的混合物。

[0098]

n型掺杂层和p型掺杂层之间的间隔层主要由电子传输材料组成,其总厚度为0.1nm至10nm,更优选为0.3nm至5nm。所述间隔层所采用的具有电子传输性能的有机材料具有如下式(1)所示的结构。

[0099]

r1-q-r2

ꢀꢀꢀꢀꢀꢀꢀ

(1)

[0100][0101]

本发明的实施例中有机电致发光器件制备过程如下:

[0102]

具体地,本实验中所采用的串联oled器件为双发光层器件,具有一个连接层。器件的制备过程如下:将涂布了ito透明导电层的玻璃板在商用清洗剂中超声处理,在去离子水中冲洗,在丙酮:乙醇混合溶剂中超声除油,在洁净环境下烘烤至完全除去水份,用紫外光和臭氧清洗,并用低能阳离子束轰击表面;

[0103]

把上述带有阳极的玻璃基片置于真空腔内,抽真空至1

×

10-5

~5

×

10-4

pa,在上述阳极层膜上真空蒸镀hatcn作为空穴注入层,蒸镀速率为0.05nm/s,蒸镀膜厚为5至10nm;

[0104]

在空穴注入层之上真空蒸镀npb作为器件的空穴传输层,蒸镀速率为0.1nm/s,蒸镀总膜厚为30至50nm;

[0105]

在空穴传输层之上真空蒸镀器件的发光层,本发明的发光层中包括主体材料be(bq)2和磷光染料ir(mphmq)2(tmd),采用多源共蒸的方法进行掺杂,通过高低晶振探头进行速率和掺杂浓度的调控。调节上述主体材料的蒸镀速率均为0.1nm/s,调节发光层中的染料蒸镀速率为主体蒸镀速率的1%至5%,进而实现预定的掺杂比例,发光层蒸镀总膜厚为20至50nm;

[0106]

在发光层之上真空蒸镀dppya作为电子传输层材料,其蒸镀速率为0.1nm/s,蒸镀总膜厚为20至60nm;

[0107]

在电子传输层(etl)上真空蒸镀厚度总厚度为20至60nm的连接层。其中n型掺杂层厚度为10nm,掺杂主体为bphen,n型掺杂剂为li,cs,ag等碱金属或者过渡金属,掺杂比例为10%。间隔层根据实验需要,厚度为0至10nm,其中p型掺杂层的厚度为20nm,掺杂主体为npb,p型掺杂剂为tectfcnbn,掺杂比例为3%。

[0108]

然后依次蒸30nm至50nm的npb作为空穴传输层,总膜厚为20至50nm的发光层,20至60nm的电子传输层,以及1nm的lif作为电子注入层,以及150nm的al作为阴极。然后制成双发光层的串联oled器件。

[0109]

下表1为本发明实施例制备的串联oled器件中所采用的有机化合物及结构式。

[0110]

表1:

[0111][0112]

器件实施例1

[0113]

将涂布了ito透明导电层的玻璃板在商用清洗剂中超声处理,在去离子水中冲洗,在丙酮:乙醇混合溶剂中超声除油,在洁净环境下烘烤至完全除去水份,用紫外光和臭氧清洗,并用低能阳离子束轰击表面;

[0114]

把上述带有阳极的玻璃基片置于真空腔内,抽真空至1

×

10-5

~5

×

10-4

pa,在上述阳极层膜上真空蒸镀hatcn作为空穴注入层,蒸镀速率为0.05nm/s,蒸镀膜厚为5nm;

[0115]

在空穴注入层之上真空蒸镀npb作为器件的空穴传输层,蒸镀速率为0.1nm/s,蒸镀总膜厚为35nm;

[0116]

在空穴传输层之上真空蒸镀器件的发光层,本发明的发光层中包括主体材料be(bq)2和磷光染料ir(mphmq)2(tmd),采用多源共蒸的方法进行掺杂,通过高低晶振探头进行速率和掺杂浓度的调控。调节上述主体材料的蒸镀速率均为0.1nm/s,调节发光层中的染料蒸镀速率为主体蒸镀速率的5%,进而实现预定的掺杂比例,发光层蒸镀总膜厚为24nm;

[0117]

在发光层之上真空蒸镀器件的电子传输层材料dppya,蒸镀速率为0.1nm/s,蒸镀总膜厚为40nm;

[0118]

在电子传输层(etl)上蒸镀n型掺杂层,在电子传输层(etl)上真空蒸镀厚度总厚度为20nm的连接层。其中n型掺杂层厚度为10nm,掺杂主体为bphen,n型掺杂剂为li,掺杂比例为10%。然后蒸镀10nm的p型掺杂层,掺杂主体为npb,p型掺杂剂为tectfcnbn,掺杂比例为3%。

[0119]

然后依次蒸镀50nm的npb作为空穴传输层,be(bq)2:ir(mphmq)2(tmd)的掺杂比例为5%、厚度为24nm的发光层,40nm的dppya作为电子传输层,以及1nm的lif作为电子注入层,以及150nm的al作为阴极。然后制成双发光层的串联oled器件。

[0120]

使其具有如下结构:

[0121]

ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0122]

器件实施例2

[0123]

与实施例1的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.1nm的l12间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0124]

器件实施例3:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.3nm的l12间隔层。

[0125]

器件实施例4:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0126]

器件实施例5:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l12间隔层。

[0127]

器件实施例6:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0128]

器件实施例7:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0129]

器件实施例8:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0130]

器件实施例9:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0131]

器件实施例10

[0132]

与实施例1的制备方法相同,区别在于,在所用的p型掺杂剂为moo3,p型掺杂层的厚度为10nm,p型掺杂剂的比例为10%。相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0133]

器件实施例11:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.1nm的l12间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.1nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0134]

器件实施例12:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层

之间引入0.3nm的l12间隔层。

[0135]

器件实施例13:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0136]

器件实施例14:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l12间隔层。

[0137]

器件实施例15:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0138]

器件实施例16:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0139]

器件实施例17:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0140]

器件实施例18:与实施例10的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0141]

上述的器件实施例1-18制备完成的采用l12作为间隔层的本发明的串联oled器件的性能汇总数据详见下表2。

[0142]

表2:

[0143][0144]

器件实施例19

[0145]

与实施例1的制备方法相同,区别在于,在所用的n型掺杂剂为cs,n型掺杂层的厚度为10nm,p型掺杂剂的比例为10%。相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:cs(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0146]

器件实施例20:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层

之间引入0.1nm的l12间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:cs(10%,10nm)/l12(0.1nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0147]

器件实施例21:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.3nm的l12间隔层。

[0148]

器件实施例22:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0149]

器件实施例23:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l12间隔层。

[0150]

器件实施例24:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0151]

器件实施例25:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0152]

器件实施例26:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0153]

器件实施例27:与实施例19的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0154]

器件实施例28

[0155]

与实施例19的制备方法相同,区别在于,在所用的p型掺杂剂为moo3,p型掺杂层的厚度为10nm,p型掺杂剂的比例为10%。相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:cs(10%,10nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0156]

器件实施例29:与实施例31的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.1nm的l4间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:cs(10%,10nm)/l12(0.1nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0157]

器件实施例30:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.3nm的l12间隔层。

[0158]

器件实施例31:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0159]

器件实施例32:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l12间隔层。

[0160]

器件实施例33:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0161]

器件实施例34:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0162]

器件实施例35:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0163]

器件实施例36:与实施例32的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0164]

上述的器件实施例19-36制备完成的采用l12作为间隔层的本发明的串联oled器件的性能汇总数据详见下表3。

[0165]

表3:

[0166][0167]

器件实施例37

[0168]

与实施例1的制备方法相同,区别在于,在所用的n型掺杂剂为ag,n型掺杂层的厚度为10nm,p型掺杂剂的比例为10%。相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:ag(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0169]

器件实施例38:与实施例41的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.1nm的l12间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:ag(10%,10nm)/l12(0.1nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0170]

器件实施例39:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.3nm的l12间隔层。

[0171]

器件实施例40:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0172]

器件实施例41:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层

之间引入1nm的l12间隔层。

[0173]

器件实施例42:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0174]

器件实施例43:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0175]

器件实施例44:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0176]

器件实施例45:与实施例42的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0177]

器件实施例46

[0178]

与实施例38的制备方法相同,区别在于,在所用的p型掺杂剂为moo3,p型掺杂层的厚度为10nm,p型掺杂剂的比例为10%。相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:ag(10%,10nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0179]

器件实施例47:与实施例51的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.1nm的l12间隔层,相应的串联oled器件结构如下:

[0180]

ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:cs(10%,10nm)/l12(0.1nm)/npb:moo3(10%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0181]

器件实施例48:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.3nm的l12间隔层。

[0182]

器件实施例49:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l12间隔层。

[0183]

器件实施例50:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l12间隔层。

[0184]

器件实施例51:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入3nm的l12间隔层。

[0185]

器件实施例52:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入5nm的l12间隔层。

[0186]

器件实施例53:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入7nm的l12间隔层。

[0187]

器件实施例54:与实施例52的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入10nm的l12间隔层。

[0188]

上述的器件实施例37-54制备完成的采用l12作为间隔层的本发明的串联oled器件的性能汇总数据详见下表4。

[0189]

表4:

[0190][0191][0192]

器件实施例55:与实施例1的制备方法相同,区别在于,该串联器件的发光单元为3个,连接层为2个。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0193]

器件实施例56:与实施例55的制备方法相同,区别在于,该串联器件的2个连接层均引入了0.5nm的l12作为间隔层。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.5nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.5nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0194]

器件实施例57:与实施例55的制备方法相同,区别在于,该串联器件的2个连接层均引入了1nm的l12作为间隔层。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0195]

器件实施例58:与实施例1的制备方法相同,区别在于,该串联器件的发光单元为4个,连接层为3个。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/

dppya(40nm)/bphen:li(10%,10nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0196]

器件实施例59:与实施例58的制备方法相同,区别在于,该串联器件的3个连接层均引入了0.5nm的l12作为间隔层。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.5nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.5nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.5nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0197]

器件实施例60:与实施例58的制备方法相同,区别在于,该串联器件的3个连接层均引入了1nm的l12作为间隔层。相应的串联oled器件结构为:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0198]

上述的器件实施例55-60制备完成的采用l12作为间隔层且发光单元数量不同的本发明的串联oled器件的性能汇总数据详见下表5。

[0199]

表5:

[0200][0201]

器件实施例61

[0202]

与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l1间隔层,相应的串联oled器件结构如下:ito/hatcn(5nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/bphen:li(10%,10nm)/l12(0.1nm)/npb:tectfcnbn(3%,10nm)/npb(35nm)/be(bq)2:ir(mphmq)2(tmd)(5%,24nm)/dppya(40nm)/lif(1nm)/al(150nm)

[0203]

器件实施例62:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l1间隔层。

[0204]

器件实施例63:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l2间隔层。

[0205]

器件实施例64:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层

之间引入1nm的l2间隔层。

[0206]

器件实施例65:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l3间隔层。

[0207]

器件实施例66:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l3间隔层。

[0208]

器件实施例67:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l4间隔层。

[0209]

器件实施例68:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l4间隔层。

[0210]

器件实施例69:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l5间隔层。

[0211]

器件实施例70:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l5间隔层。

[0212]

器件实施例71:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l6间隔层。

[0213]

器件实施例72:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l6间隔层。

[0214]

器件实施例73:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l7间隔层。

[0215]

器件实施例74:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l7间隔层。

[0216]

器件实施例75:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l8间隔层。

[0217]

器件实施例76:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l8间隔层。

[0218]

器件实施例77:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l11间隔层。

[0219]

器件实施例78:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l11间隔层。

[0220]

器件实施例79:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l13间隔层。

[0221]

器件实施例80:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l13间隔层。

[0222]

器件实施例81:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l14间隔层。

[0223]

器件实施例82:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l14间隔层。

[0224]

器件实施例83:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l19间隔层。

[0225]

器件实施例84:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l19间隔层。

[0226]

器件实施例85:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l20间隔层。

[0227]

器件实施例86:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l20间隔层。

[0228]

器件实施例87:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l21间隔层。

[0229]

器件实施例88:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l21间隔层。

[0230]

器件实施例89:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l22间隔层。

[0231]

器件实施例90:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l22间隔层。

[0232]

器件实施例91:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l25间隔层。

[0233]

器件实施例92:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l25间隔层。

[0234]

器件实施例93:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l26间隔层。

[0235]

器件实施例94:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l26间隔层。

[0236]

器件实施例95:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l27间隔层。

[0237]

器件实施例96:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l27间隔层。

[0238]

器件实施例97:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l28间隔层。

[0239]

器件实施例98:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l28间隔层。

[0240]

器件实施例99:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l29间隔层。

[0241]

器件实施例100:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l29间隔层。

[0242]

器件实施例101:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l31间隔层。

[0243]

器件实施例102:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l31间隔层。

[0244]

器件实施例103:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层

之间引入0.5nm的l32间隔层。

[0245]

器件实施例104:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l32间隔层。

[0246]

器件实施例105:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l33间隔层。

[0247]

器件实施例106:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l33间隔层。

[0248]

器件实施例107:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l35间隔层。

[0249]

器件实施例108:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l35间隔层。

[0250]

器件实施例109:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l37间隔层。

[0251]

器件实施例110:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l37间隔层。

[0252]

器件实施例111:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l43间隔层。

[0253]

器件实施例112:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l43间隔层。

[0254]

器件实施例113:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l49间隔层。

[0255]

器件实施例114:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l49间隔层。

[0256]

器件实施例115:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l57间隔层。

[0257]

器件实施例116:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l57间隔层。

[0258]

器件实施例117:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l75间隔层。

[0259]

器件实施例118:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l75间隔层。

[0260]

器件实施例119:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入0.5nm的l79间隔层。

[0261]

器件实施例120:与实施例2的制备方法相同,区别在于,在n型掺杂层和p型掺杂层之间引入1nm的l79间隔层。

[0262]

上述的器件实施例61-120制备完成的采用本发明中多个代表性化合物作为间隔层的本发明的串联oled器件的性能汇总数据详见下表6。

[0263]

表6:

[0264][0265]

[0266][0267]

通过实施例1至9、实施例37至45的对比可以发现,在串联有机电致发光器件结构中其他材料相同的情况下,通过在连接层中引入厚度为0.1nm至10nm的间隔层后器件工作24h后的电压上升值均有所降低,同时器件的稳定性有较大幅度提升,器件的寿命有相应的提高。推测应该是在加热蒸镀和在器件工作的过程中,金属类n型掺杂剂可能会向p型掺杂剂和发光层中发生迁移或者扩散,从而导致连接层的老化和发光层中的激子淬灭,从而导致器件的效率和寿命下降。在引入间隔层改善器件的寿命时一般最优厚度大约为0.1nm至10nm。

[0268]

通过对比实施例1至9、实施例19-27、实施例41至50可以发现n型掺杂剂的种类对于串联oled器件的寿命有显著的影响。单纯从寿命上看,其趋势为银》锂》铯,这主要是因为对于同一种掺杂主体而言,银和bphen之间存在较强的配位作用,作用力最强。而锂和铯和bphen之间主要为静电相互作用。由于铯的半径远远大于锂的半径,因此对于这两个形成 1价的离子而言锂和bphen之间的相互作用力比铯更强,因此这三种金属类n型掺杂剂和bphen之间的相互作用力强弱排序为银强于锂,且锂强于铯。因此基于银作为n型掺杂剂的串联oled器件寿命比基于铯的oled器件寿命更长。同时,由于引入的间隔层对于三种金属的迁移均有一定的迁移作用,本发明所述的间隔层对于采用不同n型掺杂剂的串联oled器件均为类似的寿命改善效果。

[0269]

通过对比实施例1至9和实施例10至18,实施例19至27和实施例28至36,实施例37至45和实施例46至54可以发现,无论是采用tectfcnbn这种有机半导体类的p型掺杂剂还是moo3这种无机半导体类的p型掺杂剂,本发明所述的间隔层均可以改善串联oled器件的稳定性,表现出类似的效果。这主要是因为金属类n型掺杂剂的迁移和扩散是导致串联器件老化时寿命衰减和电压上升的主要因素,因此引入间隔层有助于改善采用金属类n型掺杂剂和不同种类p型掺杂剂的串联oled器件性能。

[0270]

实施例1,4,5以及实施例61至120中采用了近30种不同的间隔层材料,我们发现采用l12作为间隔层的器件性能优于l14,具体而言就是器件的驱动电压变化较小,寿命较长。推测应该是l12的外围电子受体基团为邻菲啰啉,而l4的外围电子受体基团为2-苯基-邻菲啰啉,外围的苯基不仅会降低氮原子的静电势,而且会引入空间位阻,不利于其与金属的相互作用。因此l12阻挡金属类n型掺杂剂迁移或扩散的能力比l14更强,所以基于l12构筑的间隔层的串联oled器件寿命更优。此外,可以发现实施例61至82以及主要采用的含有双邻菲啰啉基团的间隔层材料,而实施例85至94主要为含有三嗪以及吡啶等基团的间隔层材料,可以发现在串联oled器件中的双邻菲啰啉类材料阻挡金属离子迁移的效果优于l19、l20等材料,这可能是优于邻菲啰啉基团的氮原子附近静电势更大,对于金属类n型掺杂剂的相互作用力更强,因而更利于抑制金属扩散和迁移。此外,实施例61至120中还比较了间隔层的厚度分别为0.5nm和1nm时各个串联器件的性能,对比后可以发现采用0.5nm的间隔

层的串联oled器件的器件驱动电压有所更低,这可能是由于其串联电阻更低。但间隔层厚度为1nm的串联oled器件的寿命和电压稳定性均优于间隔层厚度为0.5nm的串联oled器件,这说明采用更厚的间隔层有助于更好地抑制金属类n型掺杂剂的扩散,这也进一步反映出本发明所述的间隔层对于器件性能的影响。实施例95至120中所采用的间隔层材料的特征是一侧为苯基吡啶,另一侧为邻菲啰啉类基团,桥连基团为萘、取代及未取代的蒽等,这类大π共轭基团有利于形成较强的π-π堆积来提高电子迁移率,同时这类大π共轭的桥连基团有助于扩大分子的共轭,进而提升带负电的分子的稳定性,因此基于此类间隔层材料的串联oled器件也展现出较为优异的稳定性。基于以上结果,可以发现含氮杂环类电子传输材料所构筑的间隔层与多种金属类n型掺杂剂存在较强的相互作用,有助于抑制金属的迁移或扩散,因而有利于提升激子利用率以及oled器件的效率和寿命。

[0271]

在实施例55至60中主要验证了间隔层对于发光单元数量分别为3和4的串联oled的效果。可以发现对于含3个和4个发光单元的串联oled器件而言,引入1nm的l12作为间隔层同样可以抑制n型掺杂层中的金属迁移和扩散,提升有机电致发光器件的稳定性。

[0272]

综上,本发明所提出的在新型串联oled器件,即n型掺杂层/间隔层/p型掺杂层的的连接层设计策略有助于抑制串联oled器件中金属类n型掺杂剂的扩散和迁移,有助于提升连接层和的稳定性和减少发光层中的激子淬灭,因而可以应用于串联oled器件中,有助于器件在工作时实现较长的寿命和较低的电压上升。

[0273]

以上实验数据表明,本发明的所述的器件结构及与之匹配的电子传输材料性能优异,提升器件性能的效果明显,有望推广商业化应用。

[0274]

尽管结合实施例对本发明进行了说明,但本发明并不局限于上述实施例,应当理解,在本发明构思的引导下,本领域技术人员可进行各种修改和改进,所附权利要求概括了本发明的范围。显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本发明创造的保护范围之中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。