1.本技术涉及显示技术领域,尤其是涉及一种像素电路、显示面板及电子设备。

背景技术:

2.随着电子设备的发展,显示技术一直以来是相关技术中重要的研究领域之一。通常采用晶体管驱动像素单元发光,以进行显示。随着晶体管的工作时间增加,晶体管的阈值电压发生变化,从而影响到像素单元的发光,可能造成显示不正确等错误出现。

技术实现要素:

3.本技术公开了一种像素电路,能够解决晶体管阈值电压发生变化,从而影响像素单元发光的技术问题。

4.第一方面,本技术公开了一种像素电路,所述像素电路包括:驱动子电路、切换子电路、补偿子电路及像素单元,所述驱动子电路用于接收第一数据信号,所述切换子电路用于接收第一补偿信号,所述切换子电路用于切换所述驱动子电路与所述第一补偿信号连通,或者,所述驱动子电路与所述补偿子电路连通;当所述驱动子电路与所述第一补偿信号连通时,所述第一补偿信号对像素单元的一端电压进行补偿;当所述驱动子电路与所述补偿子电路连通时,所述补偿子电路产生的第二补偿信号对所述第一数据信号进行补偿以得到第二数据信号,所述驱动子电路根据所述第二数据信号驱动所述像素单元工作。

5.所述第一补偿信号对像素单元的一端电压进行补偿,或者,所述补偿子电路产生的第二补偿信号对所述第一数据信号进行补偿以得到第二数据信号,能够有效解决所述驱动子电路随着工作时间的增加使其中的电子元器件的参数发生变化,从而影响到驱动所述像素单元发光的技术问题。

6.第二方面,本技术还提供了一种显示面板,所述显示面板包括基板及如第一方面所述的像素电路,所述基板用于承载所述像素电路。

7.第三方面,本技术还提供了一种电子装置,所述电子装置包括本体及如第二方面所述的显示面板,所述本体用于承载所述显示面板。

附图说明

8.为了更清楚的说明本技术实施方式中的技术方案,下面将对实施方式中所需要使用的附图作简单的介绍,显而易见的,下面描述中的附图仅仅是本技术的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

9.图1为本技术第一实施方式提供的像素电路框架示意图。

10.图2为本技术一实施例提供的切换子电路示意图。

11.图3为本技术一实施例提供的补偿子电路框架示意图。

12.图4为本技术一实施例提供的控制子电路框架示意图。

13.图5为本技术一实施例提供的驱动子电路示意图。

14.图6为本技术一实施例提供的像素电路时序示意图。

15.图7为本技术另一实施例提供的像素电路时序示意图。

16.图8为本技术一实施例提供的显示面板俯视示意图。

17.图9为本技术一实施例提供的电子设备俯视示意图。

具体实施方式

18.下面将结合本技术实施方式中的附图,对本技术实施方式中的技术方案进行清楚、完整的描述,显然,所描述的实施方式仅是本技术一部分实施方式,而不是全部的实施方式。基于本技术中的实施方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本技术保护的范围。

19.本技术提供了一种像素电路1,请参阅图1,图1为本技术第一实施方式提供的像素电路框架示意图。所述像素电路1包括:驱动子电路11、切换子电路12、补偿子电路13及像素单元14,所述驱动子电路11用于接收第一数据信号vdata,所述切换子电路12用于接收第一补偿信号vint,所述切换子电路12用于切换所述驱动子电路11与所述第一补偿信号vint连通,或者,所述驱动子电路11与所述补偿子电路13连通;当所述驱动子电路11与所述第一补偿信号vint连通时,所述第一补偿信号vint对像素单元14的一端电压进行补偿;当所述驱动子电路11与所述补偿子电路13连通时,所述补偿子电路13产生的第二补偿信号对所述第一数据信号vdata进行补偿以得到第二数据信号,所述驱动子电路11根据所述第二数据信号驱动所述像素单元14工作。

20.需要说明的是,在传统的像素电路1中,所述驱动子电路11根据所述第一数据信号vdata驱动所述像素单元14发光。随着所述驱动子电路11工作时间的增加,所述驱动子电路11中的电子元器件的参数发生变化,所述驱动子电路11接收的所述第一数据信号vdata受到影响,导致所述驱动子电路11无法正确的驱动所述像素单元14发光。

21.具体的,在本实施例中,所述第一补偿信号vint为固定电压信号。所述切换子电路12可切换所述驱动子电路11与所述第一补偿信号vint连通,或者,所述驱动子电路11与所述补偿子电路13连通,使得所述第一补偿信号vint对像素单元14的一端电压进行补偿,或者所述补偿子电路13产生的第二补偿信号对所述第一数据信号vdata进行补偿以得到第二数据信号。进一步的减少了所述驱动子电路11中的电子元器件的参数发生变化所带来的影响。

22.可以理解的,在本实施例中,所述第一补偿信号vint对像素单元14的一端电压进行补偿,或者,所述补偿子电路13产生的第二补偿信号对所述第一数据信号vdata进行补偿以得到第二数据信号,能够有效解决所述驱动子电路11随着工作时间的增加使其中的电子元器件的参数发生变化,从而影响到驱动所述像素单元14发光的技术问题。

23.在一种可能的实施例中,请一并参阅图2,图2为本技术一实施例提供的切换子电路示意图。所述切换子电路12包括:第一开关晶体管t11及第二开关晶体管t12,所述第一开关晶体管t11及所述第二开关晶体管t12均包括栅极g、源极s及漏极d,所述第一开关晶体管t11的栅极g用于接收第一切换信号vscan_n-1_1,所述第一切换信号vscan_n-1_1用于控制所述第一开关晶体管t11的通断,所述第一开关晶体管t11的源极s用于接收第一补偿信号

vint,所述第一开关晶体管t11的漏极d电连接所述第二开关晶体管t12的漏极d及所述驱动子电路11;所述第二开关晶体管t12的栅极g用于接收第二切换信号vscan_n-1_2,所述第二切换信号vscan_n-1_2用于控制所述第二开关晶体管t12的通断,所述第二开关晶体管t12的源极s电连接所述补偿子电路13。

24.具体的,当所述第一切换信号vscan_n-1_1控制所述第一开关晶体管t11导通时,所述第二切换信号vscan_n-1_2控制所述第二开关晶体管t12关断,以使得所述驱动子电路11通过所述第一开关晶体管t11接收所述第一补偿信号vint。同理,当所述第二切换信号vscan_n-1_2控制所述第二开关晶体管t12导通时,所述第一切换信号vscan_n-1_1控制所述第一开关晶体管t11关断,以使得所述驱动子电路11通过所述第二开关晶体管t12电连接所述补偿子电路13。

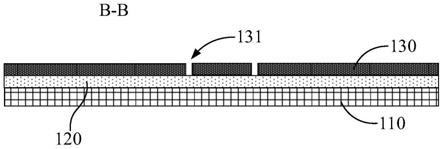

25.在一种可能的实施例中,请一并参阅图3,图3为本技术一实施例提供的补偿子电路框架示意图。所述补偿子电路13包括:转换子电路131、电压比较器132及控制子电路133,所述转换子电路131电连接所述切换子电路12,用于将接收到的电流信号转换为电压信号,并输入至所述电压比较器132,所述电压比较器132将接收到的所述电压信号与预设电压进行比较,并根据比较结果产生数字信号,并输入至所述控制子电路133,所述控制子电路133与所述驱动子电路11电连接,所述控制子电路133根据所述数字信号产生所述第二补偿信号。

26.具体的,所述控制子电路133通常被封装为具有计算能力的处理芯片。在本实施例中,所述补偿子电路13根据所述驱动子电路11传输的电流信号进行补偿。在其他可能的实施例中,所述补偿子电路13还可以根据所述驱动子电路11传输的电压信号进行补偿,也就是说,不需要所述转换子电路131进行转换,本技术对此不加以限制。

27.具体的,所述电压比较电路132将接收到的所述电压信号与预设电压进行比较,并根据比较结果产生数字信号,例如,所述电压比较电路132可以根据所述电压信号与所述预设电压的差值产生不同的数字信号。

28.在一种可能的实施例中,请一并参阅图4,图4为本技术一实施例提供的控制子电路框架示意图。所述控制子电路133包括数模转换模块133a,当所述数字信号为高电压时,所述控制子电路133输出的所述第二补偿信号为低电平;当所述数字信号为低电压时,所述控制子电路133输出所述第二补偿信号为高电平。

29.具体的,所谓高电压是指,所述数字信号的电压值大于一定的电压值;同理,所谓低电压是指,所述数字信号的电压值小于等于一定的电压值。所述数模转换模块133a可将所述数字信号转换为模拟信号,即高电平或低电平。所述控制子电路133根据输出的所述第二补偿信号对所述驱动子电路11进行补偿。

30.在一种可能的实施例中,请再次参阅图4,所述控制子电路133还包括:存储器133b及查询模块133c,所述存储器133b用于存储不同时刻所接收的所述数字信号,所述查询模块133c用于查询所述存储器133b存储的所述数字信号。

31.接下来将结合本技术所提供的一种像素电路1的电路实施例进行说明。

32.在一种可能的实施例中,请一并参阅图5,图5为本技术一实施例提供的驱动子电路示意图。所述驱动子电路11包括:第一晶体管t4、第二晶体管t2、第三晶体管t6、第四晶体管t5及第五晶体管t7,所述第一晶体管t4、所述第二晶体管t2、所述第三晶体管t6、所述第

四晶体管t5及所述第五晶体管t7均包括栅极g、源极s及漏极d,所述第一晶体管t4的栅极g用于接收使能信号vem,所述使能信号vem用于控制所述第一晶体管t4的通断,所述第一晶体管t4的漏极d用于接收第一电压信号vdd,所述第一晶体管t4的源极s电连接所述第二晶体管t2的漏极d;所述第二晶体管t2的栅极g电连接所述第三晶体管t6的漏极d,所述第二晶体管t2的源极s电连接所述第四晶体管t5的漏极d;所述第三晶体管t6的栅极g电连接所述第五晶体管t7的栅极g,并用于接收第一扫描信号vscan_n-1,所述第一扫描信号vscan_n-1用于控制所述第三晶体管t6及所述第五晶体管t7的通断,所述第三晶体管t6的源极s用于接收所述第一电压信号vdd;所述第四晶体管t5的栅极g用于接收所述使能信号vem,所述使能信号vem用于控制所述第四晶体管t5的通断,所述像素电极包括第一电极及第二电极,所述第一电极电连接所述第四晶体管t5的源极s,所述第二电极用于接收第二电压信号vss;所述第五晶体管t7的漏极d电连接所述第一电极,所述第五晶体管t7的源极s电连接所述第一开关晶体管t11的漏极d。

33.在一种可能的实施例中,请再次参阅图5,所述驱动子电路11还包括:第六晶体管t1、第七晶体管t3及存储电容c1,所述第六晶体管t1及所述第七晶体管t3均包括栅极g、源极s及漏极d,所述第六晶体管t1的栅极g电连接所述第七晶体管t3的栅极g,并用于接收第二扫描信号vscan_n,所述第二扫描信号vscan_n用于控制所述第六晶体管t1及所述第七晶体管t3的通断,所述第六晶体管t1的漏极d电连接所述控制子电路133的输出端,并用于接收所述第一数据信号vdata,所述第六晶体管t1的源极s电连接所述第二晶体管t2的源极s;所述第七晶体管t3的漏极d电连接所述第一晶体管t4的源极s,所述第七晶体管t3的源极s电连接所述第二晶体管t2的栅极g;所述存储电容c1的一端电连接所述第二晶体管t2的栅极g,另一端电连接所述第一电极。

34.在一种可能的实施例中,请一并参阅图6,图6为本技术一实施例提供的像素电路时序示意图。所述像素电路1具有:

35.感测阶段,所述驱动子电路11与所述补偿子电路13连通,所述补偿子电路13感测所述驱动子电路11输出的电流值;

36.复位阶段,所述驱动子电路11与所述第一补偿信号vint连通,所述第一补偿信号vint传输至所述像素单元14;

37.补偿阶段,所述补偿子电路13根据所述第二补偿信号对所述第一数据信号vdata进行补偿,以得到所述第二数据信号。

38.发光阶段,所述驱动子电路11根据所述第二数据信号驱动所述像素单元14发光。

39.具体的,在感测阶段中,所述第三晶体管t6导通,所述第一电压信号通过所述第三晶体管t6传输至所述第二晶体管t2的栅极g,控制所述第二晶体管t2导通,且所述第一晶体管t4、所述第四晶体管t5、所述第五晶体管t7及所述第二开关晶体管t12导通,使得所述驱动子电路11的电流传输至所述补偿子电路13;

40.所述第六晶体管t1及所述第七晶体管t3导通,所述第三晶体管t6及所述第五晶体管t7关断,所述第一数据信号vdata通过所述第六晶体管t1及所述第七晶体管t3对所述驱动子电路11进行预充电,所述补偿子电路13根据所述驱动子电路11的电流值计算出所述第二补偿信号;

41.所述第三晶体管t6、所述第五晶体管t7、所述第六晶体管t1及所述第七晶体管t3

关断,等待所述补偿子电路13根据所述第二补偿信号对所述第一数据信号vdata进行补偿,以得到所述第二数据信号。

42.具体的,在复位阶段中,所述第三晶体管t6、所述第五晶体管t7导通,所述第一晶体管t4、所述第四晶体管t5、所述第六晶体管t1及所述第七晶体管t3关断,所述第一开关晶体管t11导通,使得所述第一补偿信号vint传输至所述像素单元14的一端电极。

43.具体的,在补偿阶段中,所述第二晶体管t2、所述第六晶体管t1及所述第七晶体管t3导通,所述第一晶体管t4、所述第三晶体管t6、所述第四晶体管t5及所述第五晶体管t7关断,使得所述第二数据信号输入至所述驱动子电路11。

44.具体的,在发光阶段中,所述第一晶体管t4、所述第二晶体管t2及所述第四晶体管t5导通,使得所述像素单元14在所述第二数据信号的加载下发光。

45.在一种可能的实施例中,请一并参阅图7,图7为本技术另一实施例提供的像素电路时序示意图。在感测阶段中,所述第一晶体管t4、所述第三晶体管t6、所述第四晶体管t5及所述第五晶体管t7导通,所述第六晶体管t1及所述第七晶体管t3关断,使得所述驱动子电路11的电流传输至所述补偿子电路13;

46.所述第六晶体管t1及所述第七晶体管t3导通,所述第三晶体管t6及所述第五晶体管t7关断,所述第一数据信号vdata通过所述第六晶体管t1及所述第七晶体管t3对所述驱动子电路11进行预充电,所述补偿子电路13根据所述驱动子电路11的电流值计算出所述第二补偿信号。

47.需要说明的是,在本实施例中,复位阶段、补偿阶段及发光阶段的时序与上一实施例相同,故在此不再赘述。

48.在一种可能的实施例中,请一并参阅图8,图8为本技术一实施例提供的显示面板俯视示意图。所述显示面板2包括基板21及如上文所述的像素电路1,所述基板21用于承载所述像素电路1。通常情况下,所述像素电路1以阵列形式设置于所述基板21上。所述像素电路1请参阅上文描述,在此不再赘述。

49.在一种可能的实施例中,请一并参阅图9,图9为本技术一实施例提供的电子设备俯视示意图。所述电子装置包括本体31及如上文所述的显示面板2,所述本体31用于承载所述显示面板2。所述显示面板2请参阅上文描述,在此不再赘述。

50.本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的核心思想;同时,对于本领域的一般技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。