1.本发明属于涉及半导体技术领域,具体为滤波器芯片与无源器件集成的晶圆级封装技术。

背景技术:

2.随着电子产品小型化、便携化以及智能化的发展,对应芯片的小型化与集成化需求在逐渐增加,越来越多的系统级集成封装(sip,systemin packaging)需要集成无源器件(ipd,integrated passive device)的集成。

3.而现有的波器芯片和无源器件封装在同一基板上,芯片集成度较低,封装尺寸较大,无法实现芯片封装小型化。并且通常是通过滤波器晶圆分离成单个芯片后,倒装在集成无源器件的基板上进行封装,工艺采用类似fan out工艺,成本和工艺复杂度均较高。在滤波器晶圆和无源集成器件基板晶圆键合在一起的晶圆级封装工艺中,只能满足同一类型和同一尺寸的材质键合,如果滤波器晶圆和无源集成晶圆材质和尺寸差别较大,则工艺上难以实现。

4.另一方面,虽然晶圆级封装能够提高封装加工效率,但由于在封装时同时对晶圆上的所有芯片进行封装,不论是好的芯片或坏的芯片都将被封装,因此在晶圆制作的良率不够高时,就会带来多余的封装成本和测试时间浪费。同时,在切割成单芯片时,封装结构或者材料影响划片效率和划片成品率。

技术实现要素:

5.针对现有技术中存在不足,本发明提供了一种无源器件堆叠滤波器晶圆级封装方法,不仅能解决滤波器晶圆和无源集成器件封装的高度集成问题,实现无源集成器件和滤波器晶圆的不同尺寸和材质的晶圆级封装,进一步提高晶圆的空间利用率、封装效率和良品率。

6.本发明是通过以下技术手段实现上述技术目的的。

7.一种无源器件堆叠滤波器晶圆级封装方法,其特征在于,

8.提供一集成无源器件的第二晶圆,在所述第二晶圆上制作通孔,所述通孔的位置与滤波器的电极位置相对应;对第二晶圆背面进行减薄后,将第二晶圆切割分离成多个集成无源器件的芯片;

9.提供一承载滤波器的第一晶圆,在滤波器第一晶圆上制作围堰,所述围堰暴露出滤波器的电极和关键功能区;

10.将集成无源器件的芯片和第一晶圆上的滤波器位置一一对应得堆叠在滤波器第一晶圆上;集成无源器件的芯片和围堰一起组成了一个保护滤波器芯片关键功能区的空腔;且无源集成器件上的通孔位置对应围堰暴露滤波器的电极的位置;

11.在堆叠的集成无源器件的芯片和第一晶圆上制作钝化层,并暴露出滤波器电极的位置和无源集成器件电感和电容的引脚位置;

12.制作金属互联线将滤波器的电极和无源集成器件引脚引出到表面,再在金属互联位置和无源集成器件引脚上制作凸点;然后切割分离并封装。

13.进一步地,所述第一晶圆的材质为半导体材料、压电材料或非金属材料,第二晶圆的材质为半导体材料、非金属材料。

14.进一步地,所述半导体材料为硅、ge、gaas或sic,所述压电材料为litao3、linbo3或aln,所述非金属材料为玻璃或陶瓷。

15.进一步地,所述集成有无源器件的第二晶圆是通过物理气相沉积(简称pvd)、等离子体增强化学气相沉积(简称pecvd)、化学气相沉积(简称cvd)、化学机械研磨(简称cmp)、光刻和刻蚀工艺在第二晶圆上制作出无源器件,所述无源器件为电感、电阻和/或电容。

16.进一步地,所述通孔采用干法刻蚀、湿法刻蚀或激光打孔加工而成,通孔的直径>1um。

17.进一步地,第二晶圆减薄处理时,在第二晶圆正面贴上用于保护无源集成器件的功能区的研磨保护衬底,减薄处理后剩余晶圆厚度>10μm。

18.进一步地,将第二晶圆切割分离成单个芯片的过程中,首先将减薄后的第二晶圆贴在切割uv胶带上,然后拆掉研磨保护衬底,利用激光切割或机械切割工艺沿着切割位置将第二晶圆分离成单颗的集成无源器件的芯片。

19.进一步地,在将第二晶圆分离成单颗的集成无源器件的芯片后,提供单颗的集成无源器件的芯片的检验过程。

20.进一步地,围堰的制作是通过光刻工艺、3d打印、压印、电镀或化学镀方式制作而成,围堰厚度>1μm,材质为粘附性材料、金属或有机膜。

21.进一步地,钝化层的制作是利用光刻工艺、印胶工艺或pecvd工艺制作而成,钝化层厚度>1μm。

22.进一步地,金属互联线是利用pvd、电镀、刻蚀或化学镀工艺制作而成,金属互联线材质是ti、cu、al、sn、ag、ni、w、mo、au其中的一种金属或其合金;厚度>1μm。

23.进一步地,凸点是利用电镀、印刷或烧结金球工艺制作而成,凸点高度>1μm。

24.本发明所述的无源器件堆叠滤波器晶圆级封装方法,以无源集成器件晶圆分离成单颗芯片后,再堆叠到滤波器晶圆上的方式,实现了不同晶圆尺寸的匹配,可以将8inch或12inch的无源集成器件晶圆分离后堆叠到4inch或6inch的滤波器晶圆上,反之亦可。能够实现与不同尺寸或材质的无源集成器件晶圆的晶圆级封装加工方案。

25.本发明将无源集成器件晶圆分离后堆叠到滤波器晶圆上的封装方法,在将第二晶圆分离成单颗的集成无源器件的芯片后,通过单颗的集成无源器件的芯片的检验过程,提高了封装产品的良品率,避免因无源器件的芯片不合格导致良品率降低、封装工艺浪费及产品检验难度大的问题。还提高了集成无源器件晶圆基板的利用率。同时,由于堆叠到滤波器晶圆上的为单颗集成无源器件芯片,不仅能避免集成无源器件晶圆和滤波器晶圆进行晶圆级封装时的热胀系数(简称cte)不匹配问题,还提高了滤波器晶圆的分割效率及分割的良品率。

26.封装完成后,无源集成器件充当滤波器晶圆的密封保护层,即实现了滤波器晶圆的无源器件集成也满足了滤波器晶圆的封装保护。本发明所述的封装方法具有工艺简单、兼容性强、成本低、效率高,良品率高的优点。

附图说明

27.图1为本发明所述无源器件堆叠滤波器晶圆级封装方法的工艺流程图。

28.图2为制作完成的无源器件集成的截面图。

29.图3为制作完成的无源器件集成的俯视图。

30.图4为无源器件集成打孔后的截面图。

31.图5为无源器件集成打孔后的俯视图。

32.图6为第二晶圆的减薄过程。

33.图7为第二晶圆切割分离成单个芯片的过程。

34.图8为在第一晶圆上制作围堰后的结构图。

35.图9为将集成无源器件的芯片与第一晶圆堆叠后的结构图。

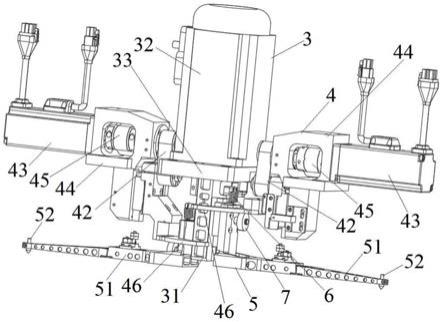

36.图10为集成无源器件的芯片堆叠完成后的结构图。

37.图11为制作金属互联线的过程。

38.图12为制作凸点之后形成的无源器件堆叠滤波器晶圆级封装结构。

39.图中:

40.100-第二晶圆,101-介电层,102-绝缘层,103-电感器件,104-电阻器件,105-电容器件,106-通孔,107-研磨保护衬底,108-切割uv胶带,110-第一晶圆,111-电极,112-关键功能区,113-围堰,114-钝化层,115-金属互联线,116-凸点。

具体实施方式

41.下面结合附图以及具体实施例对本发明作进一步的说明,但本发明的保护范围并不限于此。

42.本发明所述的无源器件堆叠滤波器晶圆级封装方法,其工艺流程如图1所示,包括以下步骤:

43.提供一集成无源器件的第二晶圆100,在所述第二晶圆100上制作通孔106,所述通孔106的位置与滤波器的电极位置相对应;对第二晶圆100背面进行减薄后,将第二晶圆100切割分离成多个集成无源器件的芯片。

44.提供一承载滤波器的第一晶圆110,在滤波器第一晶圆110上制作围堰113,所述围堰113暴露出滤波器的电极111和关键功能区112。

45.将集成无源器件的芯片和第一晶圆110上的滤波器位置一一对应得堆叠在第一晶圆110上;集成无源器件的芯片和围堰113一起组成了一个保护滤波器芯片关键功能区112的空腔;且无源集成器件上的通孔106位置对应围堰暴露滤波器的电极111的位置。

46.在堆叠的集成无源器件的芯片和第一晶圆110上制作钝化层114,并暴露出滤波器电极111的位置和无源集成器件电感103和电容105的引脚位置。

47.制作金属互联线115将滤波器的电极111和无源集成器件引脚引出到表面,再在金属互联位置和无源集成器件引脚上制作凸点116;然后切割分离并封装。

48.图2-图12示出了具体过程,图2、图3为制作的无源器件集成,利用pvd物理气相沉积、pecvd等离子体增强化学气相沉积、cvd化学气相沉积、cmp化学机械研磨、光刻和刻蚀等工艺在第二晶圆100上制作出电感器件103、电阻器件104和电容器件105等无源器件;第二晶圆100的材质为半导体材料,如si、ge、gaas、sic等,非金属材料,如玻璃、陶瓷等。

49.采用干法刻蚀、湿法刻蚀或激光打孔等工艺在第二晶圆100上与滤波器的电极111位置对应的位置加工通孔106,通孔直径>1μm,如图4、图5所示。

50.图6为第二晶圆100的减薄过程,在第二晶圆100正面贴上研磨保护衬底107保护无源集成器件的功能区,减薄无源集成器件晶圆的背面,剩余晶圆厚度>10μm。

51.图7为第二晶圆100切割分离成单个芯片的过程。将减薄后的晶圆贴在切割uv胶带108上,然后拆掉研磨保护衬底107。利用激光切割或机械切割工艺沿着切割位置109将第二晶圆100分离成一定尺寸的单颗集成无源集成器件的芯片。

52.第一晶圆110上围堰113制作:第二晶圆100完成加工分离后,再在承载有滤波器的第一晶圆110表面利用光刻工艺制作一层围堰113,围堰113暴露出滤波器的电极111和关键功能区112,例如声表滤波器的idt区域、fbar滤波器的薄膜空腔区域等,如图8所示。围堰113厚度>1μm,且围堰的材质为粘附性材料、金属、有机膜等。所述第一晶圆110的材质为半导体材料如硅、ge、gaas、sic等,压电材料litao3、linbo3、aln等或非金属材料玻璃、陶瓷等等。

53.图9为将集成无源器件的芯片与第一晶圆110堆叠后的结构图,利用贴片工艺将切割成单个芯片的无源集成器件一一堆叠在第一晶圆110上,无源集成器件芯片和第一晶圆110上滤波器芯片的位置一一对应。堆叠后集成无源器件的芯片和围堰113一起组成了一个保护滤波器关键功能区112的空腔;且集成无源器件的芯片上的通孔106位置对应围堰暴露电极111的位置。

54.图10为集成无源器件的芯片堆叠完成后的结构,第一晶圆110、集成无源器件的芯片上制作钝化层114。利用光刻工艺在第一晶圆110上堆叠的集成无源器件的芯片上覆盖一层钝化层114,并暴露出滤波器电极114的位置和无源集成器件电感103和电容105的引脚位置;钝化层厚度>1μm。

55.图11为制作金属互联线115,利用pvd、电镀、刻蚀和化学镀等工艺将滤波器电极111和无源器件引脚引出到表面,使滤波器电极和无源器件引脚做到同一平面。金属互联线115的材质是ti、cu、al、sn、ag、ni、w、mo、au等其中的一种金属或其合金,金属互联线115的厚度>1um。

56.图12为表面凸点116制作。利用电镀、印刷、烧结金球等工艺在金属互联位置和无源集成器件引脚上做上凸点116,为后续封装做准备;凸点高度>1um。至此,形成的无源器件堆叠滤波器晶圆级封装结构。最后将第一晶圆110切割分离,利用激光切割和激光切割等工艺将滤波器晶圆分离成单个芯片,完成整个封装工艺。

57.所述实施例为本发明的优选的实施方式,但本发明并不限于上述实施方式,在不背离本发明的实质内容的情况下,本领域技术人员能够做出的任何显而易见的改进、替换或变型均属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。