1.本发明涉及显示装置。

背景技术:

2.有机发光二极管(oled)元件是电流驱动的自发光元件,因此不需要背光。除此之外,oled元件具有实现低功耗、宽视角和高对比度的优势;期望能够为平板显示装置的发展做出贡献。

3.有源矩阵(am)oled显示装置包括用于选择像素的晶体管和用于向像素供应电流的驱动晶体管。oled显示装置中的晶体管是薄膜晶体管(tft);通常,使用低温多晶硅(ltps)tft。

4.tft的阈值电压和电荷迁移率具有变化。由于驱动晶体管决定了oled显示装置的发光强度,因此它们的电气特性变化可能会引起问题。因此,典型的oled显示装置包括用于补偿驱动晶体管的阈值电压的变化和偏移的校正电路。

5.oled显示装置可能会出现重影,这种现象称为图像残留。例如,在显示黑白棋盘状图案一定时间后显示中间灰度的全屏图像时,oled显示装置会显示一段时间的不同发光水平的棋盘状图案的重影。

6.这是由驱动晶体管的迟滞效应引起的。迟滞效应会在场效应晶体管中引起一种现象,使得在栅极源极电压从高电压变化到低电压的情况和栅极源极电压从低电压变化到高电压的情况下流过不同的漏电流。

7.也就是说,在发光水平从黑灰度变为中间灰度的像素和发光强度从白灰度变为中间灰度的像素之间流过不同的漏极电流。为此,oled显示装置发出不同强度的光。漏极电流的这种差异持续了几帧,因此,发光强度的差异被视觉识别为重影。

8.图像残留取决于由驱动tft的迟滞效应引起的的电流的瞬态响应特性和基于像素电路对驱动tft的阈值电压补偿特性。通过延长驱动tft的阈值电压补偿时间可以减少图像残留。为了延长阈值电压补偿时间,重要的是在不同的时段进行阈值电压补偿和向像素电路的数据写入。

9.然而,为了在不同的时段进行数据写入和阈值电压补偿,需要用于控制这些操作的不同的控制信号。同时,通常的oled显示装置通过发光控制信号来控制oled元件的发光的导通/断开。阈值电压补偿控制信号和发光控制信号可以具有与数据写入控制信号的脉冲宽度不同的脉冲宽度。

10.移位寄存器可以依次地产生和输出具有预定脉冲宽度的信号脉冲。在通常的显示装置中,包括用于输出像素控制信号的移位寄存器的电路设置在与显示区域相同的基板上但在显示区域的外侧。例如,为了使显示装置具有窄边框,要求用于输出控制信号的电路具有更小的尺寸。与用于输出用于数据写入的控制信号的移位寄存器的设计相比,在一帧时段内输出长时间使oled元件发光的发光控制信号的移位寄存器的设计通常是困难的。

技术实现要素:

11.因此,需要便于设计用于输出用于控制像素电路的控制信号的电路的技术。

12.根据本发明的一个方面的显示装置包括:包括多个像素电路行的显示区域;包括串联的多个移位寄存器单元的移位寄存器;和多个锁存电路,所述多个锁存电路被配置为根据从移位寄存器输入的信号向多个像素电路行输出信号脉冲。多个锁存电路中的每一个锁存电路被配置为向与该锁存电路相关联的像素电路行输出第一种信号的脉冲。多个移位寄存器单元被配置为依次输出第二种信号的脉冲。多个锁存电路中的每一个锁存电路被配置为接收来自第一移位寄存器单元的第二种信号的脉冲和来自在第一移位寄存器单元的后级的第二移位寄存器单元的第二种信号的脉冲。来自多个锁存电路中的每一个锁存电路的第一种信号的脉冲响应于来自第一移位寄存器单元的第二种信号的脉冲而从第一电位电平变化到第二电位电平并且响应于来自第二移位寄存器单元的第二种信号的脉冲从第二电位电平变化到第一电位电平。

13.根据本公开的另一方面的显示装置包括:显示区域;设置于显示区域的外侧的用于显示区域的驱动电路。显示区域包括:多个像素电路;以及与多个像素电路连接的多个第一控制线、多个第二控制线、多个信号线以及多个电源线。多个像素电路中的每一个像素电路包括:发光元件;多个第一导电型的开关晶体管;第二导电型的发光控制晶体管,该发光控制晶体管被配置为控制发光元件的发光的导通/断开;第二导电型的驱动晶体管,该驱动晶体管被配置为控制流向发光元件的电流量;以及与驱动晶体管连接的存储电容器。多个第一控制线被配置为将来自驱动电路的第一控制信号传输到多个第一导电型的开关晶体管。多个第二控制线被配置为将来自驱动电路的第二控制信号传输到第二导电型的发光控制晶体管。驱动电路包括多个晶体管、多个电容器以及多个连接线。驱动电路中包括的所有晶体管是第一导电型的晶体管。

14.本发明的一个方面使得能够容易地设计用于输出像素电路的控制信号的电路。

15.应当理解,前面的概述和以下详细描述都是示例性和解释性的,而不是对本发明的限制。

附图说明

16.图1示意性地示出了oled显示装置的薄膜晶体管(tft)基板和安装在tft基板上的控制电路的配置示例;

17.图2示出了实施方式中的像素电路的配置示例;

18.图3是用于控制图2所示的像素电路的信号的时序图的示例;

19.图4示意性地示出了连续四个像素电路行中的阈值补偿时段和数据写入时段之间的关系;

20.图5示出了锁存电路组中包含的锁存电路的配置示例;

21.图6提供了锁存电路的真值表;

22.图7是锁存电路的电路结构的一个示例;

23.图8示意性地示出了移位寄存器电路和锁存电路组的配置示例以及配线的布局示例;

24.图9示出了锁存电路组中包含的第n级锁存电路的输入输出信号;

25.图10a示意性地示出了用于生成发光控制信号em的移位寄存器电路和锁存电路组的配置示例以及配线的布局示例;

26.图10b是来自图10a的锁存电路的输出信号em的时序图;

27.图11示出了用于传输来自锁存电路的选择信号s1的信号线连接到电源电位voff的配置示例;

28.图12是图11所示的电路中的控制信号的时序图;

29.图13示出了向s1信号线供给电源电位voff的其他配置示例;

30.图14是图13的配置示例中的控制信号的时序图;

31.图15示出了像素电路的另一配置示例;

32.图16是用于一帧时段内控制图15所示的像素电路的信号的时序图;

33.图17示出了被设定为用于在图15和图16所示的配置示例的锁存电路组中的锁存电路的配置示例;

34.图18是锁存电路的输入信号和输出信号的时序图;

35.图19示意性地示出了通过移位寄存器电路和锁存电路组的组合来生成和输出控制信号s1、s2和em的电路配置示例;

36.图20是示意性地示出锁存电路的布局示例的俯视图;并且

37.图21示意性地示出了沿图20中的剖面线xxi-xxi的剖面结构。

具体实施方式

38.在下文中,将参考附图描述本发明的实施方式。附图中共同的元件由相同的附图标记表示并且附图中的每个元件在尺寸和/或形状上可能被夸大以清楚地理解描述。

39.在下文中公开了如有机发光二极管(oled)显示装置那样在发光型显示装置中产生和输出用于像素电路的控制信号的电路的配置,该发光型显示装置包括响应于驱动电流而发光的发光元件。本说明书的实施方式中的显示装置通过移位寄存器电路和多个锁存电路的组合产生并输出用于控制像素电路的控制信号。通过移位寄存器电路和多个锁存电路的组合,可以容易地设计输出具有期望的脉冲宽度的信号脉冲的电路。

40.例如,可以通过花费较长时间进行驱动tft的阈值电压补偿来减少图像残留。通过在与数据写入时段不同的时段内进行阈值电压补偿,可以获得较长的阈值电压补偿时段。移位寄存器电路和多个锁存电路的组合可以容易地产生关于数据写入时段的控制信号和关于阈值电压补偿时段的控制信号。

41.移位寄存器电路包括多个串联的移位寄存器单元。例如,每个移位寄存器单元向相关联的像素电路行输出关于数据写入时段的控制信号。每个锁存电路从两个不同的移位寄存器单元接收该控制信号,并向相关联的像素电路行输出关于阈值电压补偿时段的控制信号。这种配置不需要用于关于阈值电压补偿时段的控制信号的移位寄存器电路,因此可以实现更小的电路面积。

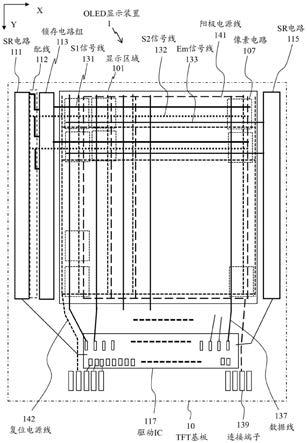

42.在另一个例子中,移位寄存器电路和多个锁存电路的组合可以产生和输出用于控制发光元件的发光的导通/断开的发光控制信号。每个锁存电路接收来自两个不同移位寄存器单元的信号,并向相关联的像素电路行输出发光控制信号。该配置使得能够容易地设计用于生成发光控制信号的驱动器电路。

43.除了发光控制信号之外,移位寄存器电路和多个锁存电路的组合可以产生和输出数据写入信号。每个移位寄存器单元向相关联的像素电路行输出关于数据写入时段的控制信号。每个锁存电路从两个不同移位寄存器单元接收数据写入控制信号,并向相关联的像素电路行输出发光控制信号。

44.显示装置的配置

45.以下,更具体地描述本说明书的实施方式。图1示意性地示出了oled显示装置的薄膜晶体管(tft)基板和安装在tft基板上的控制电路的配置示例。在图1中,相同类型的部件中的仅一个部件用附图标记表示。oled显示装置1包括在其上制造有机发光元件(oled元件)和像素电路的tft基板10以及用于封装oled元件的未示出的薄膜封装(tfe)。

46.薄膜封装是结构封装单元的一个例子。结构封装单元的另一示例可以包括用于封装oled元件的封装基板和用于将tft基板与封装基板粘合的粘合部(玻璃料密封剂)。例如,tft基板与封装基板之间的空间填充有干燥的氮气。

47.tft基板10包括绝缘基板;在绝缘基板上制作用于显示图像的显示区域101。第一移位寄存器(sr)电路111、锁存电路组113、第二移位寄存器电路115和驱动ic 117设置在显示区域101的外侧。在图1中,第一移位寄存器电路111设置在显示区域101的左侧,第二移位寄存器电路115设置在显示区域101的右侧;这些移位寄存器电路彼此相对。连接第一移位寄存器电路111和锁存电路组113的配线112设置在它们之间的空间中。

48.驱动ic 117经由未示出的柔性印刷电路(fpc)连接到外部设备。fpc的连接端子与tft基板10上的连接端子139相互连接。

49.第一移位寄存器电路111驱动tft基板10上的s2信号线132。s2信号线132设置为从第一移位寄存器电路111沿x轴延伸,并沿y轴上下布置。在图1中,s2信号线132由虚线表示。第一移位寄存器电路111向s2信号线132依次输出控制信号s2的脉冲。锁存电路组113驱动tft基板10上的s1信号线131。s1信号线131设置为从锁存电路组113沿x轴延伸并沿y轴上下布置。锁存电路组113向s1信号线131依次输出控制信号s1的脉冲。稍后将描述控制信号s1和s2。

50.第二移位寄存器电路115驱动发光信号线(em信号线)133以控制像素的发光时段。em信号线133设置为从第二移位寄存器电路115沿x轴延伸并且沿y轴上下布置。第二移位寄存器电路115向em信号线133依次输出em信号(发光控制信号)的脉冲。稍后将描述em信号。

51.例如,驱动ic 117安装有各向异性导电膜(acf)。驱动ic 117向第一移位寄存器电路111和第二移位寄存器电路115供应电源信号和时序信号(控制信号)。驱动ic 117向数据线137输出规定像素亮度的数据信号。在图1的配置示例中,数据线137设置为沿y轴延伸并沿x轴并排布置。驱动ic 117向每条数据线137供应规定所选择的oled元件的亮度水平的数据信号。

52.显示区域101包括用于控制多个像素的oled元件的发光的多个像素电路107。在图1的配置示例中,像素电路设置成矩阵。像素电路的布局不限于特定的布局。例如,在多色oled显示装置中,每个oled元件发射红色、蓝色和绿色中的一种颜色的光。多个像素电路构成像素电路阵列。

53.由多个像素电路组成的每个像素电路行与s1信号线131、s2信号线132和em信号线133连接。s1信号线131、s2信号线132和em信号线133分别传输控制信号s1、控制信号s2和控

制信号em至相关联的像素电路行。每个数据线137与一个像素电路列连接。每个像素电路列与每个像素电路行中的一个像素电路连接。数据线137将规定发光水平的数据信号传输到所选择的像素电路行中的像素电路。

54.阳极电源线141和复位电源线142设置在tft基板10上。阳极电源线141传输要供应给每个oled元件的阳极的电源电位。在图1中,阳极电源线141由长虚线表示,其图案包括沿x轴延伸的配线和沿y轴延伸并沿x轴并排布置的多条配线。沿y轴延伸的配线与沿x轴延伸的配线连接。

55.复位电源线142传输用于复位每个像素电路中的特定节点的电位的电源电位。在图1中,复位电源线142由虚线表示,其图案包括沿x轴延伸的配线和沿y轴延伸并沿x轴并排设置的多条配线。沿y轴延伸的配线与沿x轴延伸的配线连接。这些电源电位可以从外部电源电路或驱动ic 117中的电源电路供应。图1不包括将参考图2描述的电源线的一部分。

56.如后面将描述的,每个像素电路包括驱动tft(驱动晶体管)和用于保持用于确定驱动tft的驱动电流的信号电压的存储电容器。通过数据线137传输的数据信号被调整并存储(写入)到存储电容器。存储电容器的电压决定驱动tft的栅极电压(vgs)。调整后的数据信号以模拟方式改变驱动tft的电导,以向oled元件供应与发光灰度对应的正向偏置电流。

57.像素电路的配置

58.图2示出了实施方式中的像素电路107的配置示例。像素电路107被包括在第n级像素电路行(n是整数)中。像素电路107包括各自具有栅极、源极和漏极的六个晶体管(tft)m11至m16。本示例中的所有晶体管m11至m16都是p型tft。

59.晶体管m11是用于控制流向oled元件e1的电流量的驱动晶体管。驱动晶体管m11根据存储在存储电容器c10中的电压控制从供应电源电位pvdd的阳极电源向oled元件e1供应的电流量。存储电容器c10在一帧时段内保持写入电压。oled元件e1的阴极与用于传输来自阴极电源的电源电位pvee的电源线204连接。

60.图2的配置示例中的存储电容器c10由串联的电容器c11和c12组成。存储电容器c10的一端被供应阳极电源电位pvdd,另一端与开关晶体管m13和m14的源极/漏极连接。存储电容器c10的又一端与驱动晶体管m11的栅极连接。更具体地,电容器c12的一端与阳极电源线141连接;电容器c11的一端与开关晶体管m13和m14的源极/漏极连接;电容器c11和c12之间的中间节点与驱动晶体管m11的栅极连接。

61.存储电容器c10的电压为驱动晶体管m11的栅极与阳极电源线141之间的电压。驱动晶体管m11的源极与阳极电源线141连接;源极电位是阳极电源电位pvdd。因此,存储电容器c10存储驱动晶体管m11的栅极和源极之间的电压。在图2的配置示例中,电容器c12保持驱动晶体管m11的栅极-源极电压。

62.晶体管m15是用于控制oled元件e1的发光的导通/断开的开关晶体管。晶体管m15的源极与驱动晶体管m11的漏极连接。晶体管m15使向与漏极连接的oled元件e1的电流供应导通/断开。晶体管m15的栅极与em信号线(发光控制线)133连接,晶体管m15由从移位寄存器电路115输入到其栅极的发光控制信号em控制。

63.晶体管m16用于向oled元件e1的阳极供应复位电位vrst。晶体管m16的源极/漏极的一端与用于传输复位电位vrst的电源线142连接,另一端与oled元件e1的阳极连接。

64.晶体管m16的栅极与s1信号线131连接,晶体管m16由控制信号s1控制。当晶体管

m16被从锁存电路组113输入到其栅极的控制信号s1导通时,晶体管m16将由电源线142传输的复位电位vrst供应给oled元件e1的阳极。晶体管m16还具有在向oled元件e1的阳极供应复位电位vrst的同时,在复位时段旁路从电源pvdd经由m11和m15流入的电流以防止泄漏发光的功能。

65.晶体管m12是用于将用于校正(补偿)驱动晶体管m11的阈值电压的电压写入到存储电容器c10以及用于复位驱动晶体管m11的栅极电位的开关晶体管。晶体管m12的源极和漏极连接驱动晶体管m11的栅极和漏极。因此,当晶体管m12导通时,驱动晶体管m11处于二极管连接的状态。

66.晶体管m14为开关晶体管,用于将用于补偿驱动晶体管m11的阈值电压的电压写入存储电容器c10。晶体管m14控制是否向存储电容器c10供应基准电位vref。晶体管m14的源极/漏极的一端与用于传输基准电位vref的电源线202连接,另一端与电容器c11的一端连接。晶体管m14的栅极与s1信号线131连接,晶体管m14由从锁存电路组113输入到其栅极的控制信号s1控制。

67.晶体管m12、m16和m14由控制信号s1控制。因此,这些晶体管m12、m16和m14同时导通/断开。在这些晶体管导通的期间,当发光控制晶体管m15导通时,驱动晶体管m11的栅极电位被复位,随后发光控制晶体管m15断开。当晶体管m12和m14导通时,晶体管m11是处于二极管连接的晶体管。电源电位pvdd与基准电位vref之间的阈值补偿电压被写入存储电容器c10。

68.晶体管m13是用于选择要被供应数据信号的像素电路并将数据信号(数据信号电压)写入存储电容器c10的开关晶体管。晶体管m13的源极/漏极的一端与用于传输数据信号vdata的数据线137连接,另一端与存储电容器c10连接,更具体地,晶体管m13的源极/漏极的另一端与电容器c11的一端连接。

69.晶体管m13的栅极与用于传输用于选择写入数据信号的像素电路行的控制信号s2的s2信号线132连接。晶体管m13由从移位寄存器电路111供应的控制信号s2控制。当晶体管m13导通时,晶体管m13将从驱动ic 117经由数据线137供应的数据信号vdata供应给存储电容器c10。

70.图3是用于控制图2中的像素电路107的信号的时序图的示例。图3为将驱动晶体管m11的阈值补偿电压和数据信号vdata写入第n级像素电路行的像素电路中的时序图。具体地,图3示出了用于选择第n级像素电路行以写入数据信号vdata的选择信号s1_n和s2_n、用于第n级像素电路行的发光控制信号em_n以及用于选择第(n-6)级像素电路行的选择信号s2_n-6在一帧中的时间变化。图3示出了这些信号的信号电位电平的变化。选择信号是一种控制信号,可以称为扫描信号。

71.图3的时序图中的1h时段是向像素电路写入数据信号vdata的时段和选择信号s2为低的时段。阈值补偿时段长于1h并且在图3的示例中为5小时。

72.在时刻t1,选择信号s2_n-6从高变为低。如稍后将描述的,响应于选择信号s2_n-6的变化,选择信号s1_n从高变为低。晶体管m12、m14和m16响应于选择信号s1_n的变化而导通。由于发光控制信号em_n在时刻t1为低,所以晶体管m15导通。

73.由于晶体管m12和m14至m16导通,因此复位电位vrst被供应给oled元件e1的阳极,此外还供应给驱动晶体管m11的栅极。在时刻t2,发光控制信号em_n从低变为高。从时刻t1

到时刻t2的时段是复位驱动晶体管m11的栅极电压的时段。选择信号s2_n-6也在时刻t2从低变为高。从时刻t1到时刻t2的时段是向第(n-6)级像素电路行写入数据信号的时段。从时刻t1到时刻t2的时段的长度为1h。

74.从时刻t2到时刻t3,保持信号s1_n、s2_n、em_n和s2_n-6的电位电平。晶体管m12、m14和m16导通,包括晶体管m15的其他晶体管断开。在从时刻t2到时刻t3的时段中,阈值补偿电压被写入到存储电容器c10。从时刻t2到时刻t3的时段为阈值补偿时段,长度为5h。

75.在时刻t3,选择信号s2_n由高变低。如稍后将描述的,响应于选择信号s2_n的改变,选择信号s1_n从低变为高。晶体管m12、m14和m16响应于选择信号s1_n的变化而断开。选择信号s1_n在时刻t3之后维持为高。

76.此外,晶体管m13响应于选择信号s2_n的变化从断开变为导通。结果,数据信号vdata开始写入存储电容器c10。在时刻t4,选择信号s2_n从高变为低。作为响应,晶体管m13由导通变为断开以结束向第n级像素电路行的数据写入。从时刻t3至时刻t4的时段为向第n级像素电路行写入数据的时段,其长度为1h。选择信号s2_n在时刻t4之后保持为高。

77.在时刻t4,发光控制信号em_n从高变为低。作为响应,晶体管m15从断开变为导通。结果,驱动电流被供应给oled元件e1并且oled元件e1开始发光。

78.图4示意性地示出了四个连续的像素电路行中的阈值补偿时段和数据写入时段之间的关系。在每个像素电路行中,数据写入时段在阈值补偿时段之后。数据写入时段和阈值补偿时段的长度对于各像素电路行是共同的。数据写入时段的长度为1h,阈值补偿时段的长度为(q-1)*h,其中q为大于1的整数。为了更合适的阈值补偿,将q的值确定为大于2的整数。在参照图3描述的示例中,q的值为6。

79.如稍后将描述的,阈值补偿时段根据前一行的选择信号s2_n-q可以具有不同的长度以引起选择信号s1_n的改变。如上所述,选择信号s1_n为低的时段的长度为qh并且阈值补偿时段的长度为(q-1)*h。在设计显示装置时,选择q的值以获得适当的阈值补偿时段。

80.如图4所示,数据信号被依次写入各像素电路行。每个像素电路行的数据写入时段在前一行的数据写入时段结束后立即开始。不同像素电路行的数据写入时段从不重叠。每个像素电路行的阈值补偿时段与前一像素电路行的阈值补偿时段和数据写入时段重叠。阈值补偿时段可以与紧接其前的和一些之前的像素电路行的数据写入时段重叠。

81.移位寄存器电路与锁存电路组的组合

82.图5示出了在锁存电路组113中包括的锁存电路300的配置示例。图5中的锁存电路向第n级像素电路行输出选择信号s1_n。锁存电路300包括用于接收信号的set端子301和rst端子302以及用于输出信号的q端子303。

83.第(n-6)级像素电路行的选择信号s2_n-6从移位寄存器电路111输入到set端子301。第n级像素电路行的选择信号s2_n输入到rst端子302。锁存电路300从q端子303向第n级像素电路行的s1信号线131输出s1_n信号。

84.图6提供了锁存电路300的真值表。在图6的真值表中,l表示逻辑低电平,h表示逻辑高电平。在参考图3至图5描述的配置中,信号s1和s2的高电位电平对应于逻辑低电平,信号s1和s2的低电位电平对应于逻辑高电平。

85.当set输入为l并且rst输入为l时,q输出为l。当set输入为h并且rst输入为l时,q输出为h,即使之后set输入变化,q输出也保持为h。当set输入为l并且rst输入为h时,q输出

为l。不允许set输入和rst输入均为h的状态。

86.从参照图3和图5的描述可以理解,移位寄存器电路111向像素电路行依次输出选择信号s2的脉冲。脉冲宽度为1h。每个锁存电路300向相关联的像素电路行输出s1信号。

87.如上所述,当第n行的锁存电路300在set端子301处接收到提前预定行数的行的选择信号s2_n-q的低电位电平(逻辑电平h)的脉冲时,它将从q端子303输出的选择信号s1_n改变为低电位电平。尽管选择信号s2_n-q随后变为高电位电平(逻辑电平l),但rst端子302的输入s2_n处于高电位电平,因此从q端子303输出的选择信号s1_n保持在低电位电平。

88.随后,锁存电路300在rst端子302处接收第n级像素电路行的选择信号s2_n的低电位电平(逻辑电平h)的脉冲。作为响应,锁存电路300将从q端子303输出的选择信号s1_n改变为高电位电平(逻辑电平l)。从锁存电路300输出的s1_n信号的脉冲宽度是qh。

89.图7示出了锁存电路300的电路配置的示例。在图7的配置示例中,锁存电路300包括四个晶体管和一个电容元件。四个晶体管m21至m24是p型晶体管。晶体管m21处于二极管连接状态并且在漏极处接收来自set端子301的输入。晶体管m22被连接在晶体管m21和用于供应电源电位pvee的电源之间,并且在栅极处接收来自rst端子302的输入。

90.晶体管m23被连接在用于供应电源电位pvdd的电源与q端子303之间,并且其栅极与晶体管m21和m22之间的中间节点连接。晶体管m24被连接在晶体管m23和用于供应电源电位pvee的电源之间,并在栅极处接收来自rst端子的输入。电容元件cb被连接在晶体管m23的栅极和q端子303之间。晶体管m23与m24之间的中间节点与q端子303连接。

91.图8示意性地示出了移位寄存器电路111和锁存电路组113的配置示例以及配线112的布局的示例。移位寄存器电路111包括串联的多个移位寄存器单元。在图8中,移位寄存器单元中的仅一个用附图标记400表示。

92.图8包括第(n-6)级至第(n 3)级移位寄存器单元400。这些移位寄存器单元400与第(n-6)级至第(n 3)级像素电路行相关联。数据位根据两个时钟信号ck和ckb从移位寄存器单元400被传输到下一个移位寄存器单元400。保持数据位的移位寄存器单元400输出信号脉冲。

93.锁存电路组113包括多个锁存电路300。在图8中,锁存电路中的仅一个用附图标记300表示。图8包括第(n-6)级至第(n 3)级锁存电路300。这些锁存电路300与第(n-6)级至第(n 3)级像素电路行相关联。

94.移位寄存器电路111包括各自与像素电路行相关联的移位寄存器单元400。与像素电路行关联的移位寄存器单元400向关联的像素电路行和两个锁存电路300输出信号脉冲。移位寄存器单元400的数量大于像素电路行的数量。一些移位寄存器单元400(未示出)不与像素电路行连接并且仅向锁存电路300输出信号。

95.锁存电路300的两个输入与两个不同的移位寄存器单元400的输出连接。具体来说,前级的移位寄存器单元400的输出被输入到set端子,标记为s,来自后级的移位寄存器单元400的输出被输入到rst端,标记为r。在图8的配置示例中,第(n-6)级移位寄存器单元400的输出被输入到第n级锁存电路300的set端子,并且第n级移位寄存器单元400的输出被输入到第n级锁存器电路300的rst端。

96.第n级移位寄存器单元400将用于第n级像素电路行的选择信号s2输出至第n级像素电路行、第n级锁存电路300的rst端子、以及第(n 6)级锁存电路300的set端子。第n级移

位寄存器单元400同时向它们输出信号脉冲。

97.第n级锁存电路300从q端子(标记为q)向第n级像素电路行输出选择信号s1。如上所述,第n级锁存电路300响应于来自第(n-6)级移位寄存器单元400的信号脉冲而开始选择信号s1的脉冲,并响应于来自第n级移位寄存器单元400的信号脉冲而结束该脉冲。来自锁存电路300的脉冲为第一种信号的脉冲,来自移位寄存器单元400的脉冲为第二种信号的脉冲。如上所述,选择信号s1_n是利用两个移位寄存器单元和一个锁存电路产生的。

98.上述关于第n级移位寄存器单元400和第n级锁存电路300的描述适用于与各个像素电路行相关联的其他级的移位寄存器单元400和锁存电路300。虽然上述例子以来自两个相隔六级的移位寄存器单元400的输出来控制锁存电路300,用于控制锁存电路300的移位寄存器单元400的级的关系根据选择信号s1的脉冲宽度来确定。

99.更一般地,第n级锁存电路的输出由来自第k级移位寄存器单元的信号脉冲设定,并由来自第(k p)级移位寄存器单元的信号脉冲复位,其中k为整数,p为大于1的整数。在上述示例中,k为(n-6),并且p为6。

100.第(n q)级锁存电路的输出由来自第(k q)级移位寄存器单元的信号脉冲设定,并由来自第(k q p)级移位寄存器单元的信号脉冲复位,其中q是大于0的整数。来自锁存电路300的脉冲具有p*h的脉冲宽度。来自第(n q)级锁存电路的脉冲相对于来自第n级锁存电路的脉冲延迟q*h的时间。如上所述,阈值补偿时段的长度为(p-1)*h。

101.接着,说明利用移位寄存器电路和锁存电路组的组合来生成发光控制信号em的结构。图9示出了在锁存电路组中包括的第n级锁存电路350的输入和输出信号。锁存电路350的真值表与参照图6描述的相同。

102.选择信号s2_n-5从第(n-5)级移位寄存器单元输入到锁存电路350的rst端子352。选择信号s2_n 1从第(n 1)级移位寄存器单元输入到锁存电路350的set端子351。锁存电路350从q端子353向第n级像素电路行输出发光控制信号em_n。在阈值补偿时段的长度为(p-1)*h的情况下,锁存电路350在rst端352处从第(n-(p-1))级移位寄存器接收选择信号s2。

103.图10a示意性地示出了用于生成发光控制信号em的移位寄存器电路和锁存电路组的配置示例以及配线的布局示例。该配置使得能够更容易地设计用于生成发光控制信号em的电路。

104.移位寄存器电路451包括串联的多个移位寄存器单元452。移位寄存器单元中的仅一个用附图标记452表示。每个移位寄存器单元452具有与移位寄存器单元400相同的配置。移位寄存器电路451不直接向像素电路输出信号,而是仅向锁存电路组461输出信号。

105.锁存电路组461包括多个锁存电路350,每个锁存电路与像素电路行相关联。锁存电路中的一个用附图标记350表示。锁存电路组461具有与参考图8描述的锁存电路组相同的配置。图10的配置与图8的配置相比,不同之处在于移位寄存器电路451和锁存电路组461之间的连接线471。

106.图10a包括第(n-6)级至第(n 3)级移位寄存器单元452和锁存电路350。锁存电路350与第(n-6)级至第(n 3)级像素电路行相关联。移位寄存器单元452的数量大于像素电路行的数量。

107.锁存电路350的两个输入与两个不同的移位寄存器单元452的输出连接。具体来说,前级的移位寄存器单元452的输出被输入到rst端子,来自后级的移位寄存器单元452的

输出被输入到set端子。在图10a的配置示例中,第(n-5)级移位寄存器单元452的输出被输入到第n级锁存电路350的rst端子,第(n 1)级移位寄存器单元452的输出被输入到第n级锁存电路350的set端子。

108.第n级移位寄存器单元452向第(n-1)级锁存电路350的set端子和第(n 5)级锁存电路350的rst端子输出控制信号。第n级移位寄存器单元452同时向它们输出信号脉冲。

109.第n级锁存电路350从q端子向第n级像素电路行输出发光控制信号em。第n级锁存电路350响应于来自第(n-5)级移位寄存器单元452的信号脉冲而开始发光控制信号em的脉冲,并响应于来自第(n 1)级移位寄存器单元452的信号脉冲而结束脉冲。

110.发光控制信号em的脉冲的极性(电位电平)与选择信号s1的脉冲的极性相反。信号的时序图在图10b中提供。来自锁存电路350的脉冲是第一种信号的脉冲,来自移位寄存器单元452的脉冲是第二种信号的脉冲。

111.关于第n级移位寄存器单元452和第n级锁存电路350的上述描述适用于与各个像素电路行相关联的其他级的锁存电路350和移位寄存器单元452。虽然上述例子利用来自两个相隔六级的移位寄存器单元452的输出来控制锁存电路350,但是可以根据发光控制信号em的脉冲宽度来确定用于控制锁存电路350的多个移位寄存器单元452的级的关系。

112.更一般地,第n级锁存电路的输出由来自第k级移位寄存器单元的信号脉冲复位,并由来自第(k p)级移位寄存器单元的信号脉冲设定。在上述示例中,k为(n-5)并且p为6。

113.第(n q)级锁存电路的输出由来自第(k q)级移位寄存器单元的信号脉冲复位,并且由第(k q p)级移位寄存器单元的信号脉冲设定。来自锁存电路的脉冲具有p*h的脉冲宽度。来自第(n q)级锁存电路的脉冲相对于来自第n级锁存电路的脉冲延迟q*h的时间。如上所述,断开向oled元件e1供应电流的时段的长度为p*h。

114.参考图10a描述的配置示例使用移位寄存器电路和锁存电路组的组合,仅生成和输出发光控制信号em而不生成选择信号s2。除了发光控制信号em之外,另一个配置示例可以产生和输出选择信号s2。在这种情况下,oled显示装置包括移位寄存器电路,移位寄存器电路用于产生选择信号s1并将其输出,而不将其发送到锁存电路组。

115.用于产生选择信号s2和发光控制信号em的电路是通过在图10a的配置示例中追加从移位寄存器单元452的输出到相关联的像素电路行的控制信号线而获得的。与像素电路行连接的移位寄存器单元452向相关联的像素电路行以及参考图10a描述的两个锁存电路输出信号脉冲。本发明的驱动方法不限于上述两个实施方式,而是通过改变向锁存电路输入的set信号和rst信号的时序以及set信号和rst信号之间的间隔来产生具有期望宽度的脉冲的通用方法。

116.图11示出了用于传输来自锁存电路300的选择信号s1的信号线131被连接到电源电位voff的配置示例。这种配置可防止s1信号线在发光时段变为浮动状态。

117.由于与s1信号线连接的晶体管m23和m24在发光时段断开,所以s1信号线变为电浮置状态。s1信号线的电位由整个信号线的电容保持,但由于经由显示区域中与s1信号线交叉的数据线的电容耦合的电容的馈通噪声而改变。当这种潜在的变化很大时,图像质量可能会下降。因此,在发光时段中固定s1信号线的电位是更合适的。

118.图11的配置示例包括用于导通/断开在s1信号线131和电源电位voff的电源线之间的连接的复位开关(开关晶体管)501。图11的配置示例中的复位开关501是p型tft。每个

s1信号线131设置有复位开关501。在参考图2至图10描述的配置示例中,电源电位voff是与选择信号s1的脉冲电位相反的电位,并且处于高电位电平。

119.复位开关501通过从移位寄存器电路115输出的发光控制信号em来导通/断开。发光控制信号em是用于控制是否向oled元件e1供应驱动电流的信号。具体地,用于导通/断开电源电位voff向第n级像素电路行的s1信号线131的供应的复位开关501通过相同的第n级像素电路行的发光控制信号em_n而导通/断开。

120.图12是图11所示的电路中的控制信号的时序图。下面主要说明与图3的时序图的不同之处。发光控制信号em_n在比时间t1提前1h的时间t0从低变为高。当发光控制信号em_n为低时,复位开关501导通并且第n个s1信号线131固定在电源电位voff。

121.复位开关501响应于发光控制信号em_n向高的变化而断开。s1信号线131变为浮动状态。在时刻t1,锁存电路300开始向选择信号s1_n输出低电平信号。发光控制信号em_n为高并且晶体管m15断开。复位电位vrst被供应给oled元件e1的阳极,但不供应给驱动晶体管m11的栅极。

122.在比时刻t4晚1h的时刻t5,发光控制信号em_n从高变为低。复位开关501响应于发光控制信号em_n向低的变化而导通。第n个s1信号线131固定到电源电位voff。

123.图13图示了用于向s1信号线供应电源电位voff的另一配置示例。图13的配置示例通过移位寄存器电路503和锁存电路组的组合产生和输出用于控制复位开关501的信号vreset。虽然图13以示例的方式示出了第n级锁存电路505,锁存电路组包括与所有的s1信号线一一对应的锁存电路505。锁存电路505的输出被输入到与同一s1信号线相关联的复位开关501的栅极。来自移位寄存器单元的脉冲的时段为1h。

124.在图13的配置示例中的第n级锁存电路505在rst端子接收第(n-6)级移位寄存器单元的输出,并在set端子接收第n级移位寄存器单元的输出。第n级锁存电路505从q端子向第n级复位开关501的栅极输出控制信号vreset。

125.图14是图13的配置示例中的控制信号的时序图。下面主要描述与图13的时序图的不同之处。如图14所示,第n级复位开关501的控制信号vreset与第n级像素电路行的选择信号s1互补地变化。换句话说,一个信号是高或低,另一个信号是低或高。这种配置使s1信号线的电位稳定。

126.在时刻t1,锁存电路505的输出响应于到rst端子的控制信号r_n-6的脉冲而从逻辑h变为逻辑l。换言之,锁存电路505的输出vreset从低电位电平变为高电位电平,使得复位开关501断开。

127.在随后的时刻t3,锁存电路505的输出响应于到set端子的控制信号r_n的脉冲而从逻辑l变为逻辑h。换言之,锁存电路505的输出vreset从高电位电平变为低电位电平,使得复位开关501导通,以向s1信号线供给电源电位voff。

128.如参考图11至图14描述的,用于将脉冲从锁存电路传输到像素电路行的每条配线在脉冲结束之后连接到处于高电位电平的电源线。这种配置使配线的电位稳定。供应给配线的电位电平是脉冲的基准电位电平,并且根据s1信号的波形可以是低电平。

129.参考图13和图14描述的配置示例包括第二移位寄存器电路503和多个第二锁存电路505。每个锁存电路505向与其相关的复位开关501输出信号脉冲。

130.移位寄存器电路503依次输出信号脉冲。每个锁存电路505接收来自移位寄存器电

路503中的移位寄存器单元的信号脉冲和来自第一移位寄存器单元后级的另一个移位寄存器单元的信号脉冲。来自锁存电路505的信号脉冲响应于来自前级移位寄存器单元的信号脉冲而开始,并且响应于来自后级移位寄存器单元的信号脉冲而结束。

131.每个锁存电路505以与s1信号脉冲同步的信号脉冲控制相关的复位开关501,以在s1信号脉冲结束之后将用于将s1信号脉冲传输至像素电路行的配线连接至处于高电平电位的电源线。

132.像素电路的其他配置

133.图15示出了像素电路的另一配置示例。像素电路550包括p型tft和n型tft。p型tft可以是低温多晶硅tft,n型tft可以是氧化物半导体tft。像素电路550包括七个晶体管(tft)m51至m57。在这个例子中,晶体管m51、m53和m56是p型tft,晶体管m52、m54、m55和m57是n型tft。

134.晶体管m53是用于控制流向oled元件e1的电流量的驱动晶体管。驱动晶体管m53根据存储电容器cst中存储的电压来控制从阳极电源提供给oled元件e1的电流量。oled元件e1的阴极连接到阴极电源。存储电容器cst存储驱动晶体管m53的栅极-源极电压。

135.晶体管m51和m56是控制oled元件e1是否发光的发光控制晶体管。晶体管m51从其源极端子与阳极电源连接,并且接通/断开向与其漏极端子连接的驱动晶体管m53的电流供应。晶体管m56从其源极端子与驱动晶体管m53的漏极端子连接,并且接通/断开向与其漏极端子连接的oled元件e1的电流供应。晶体管m51和m56由发光控制信号em控制。

136.晶体管m57用于向oled元件e1的阳极供应复位电位。当晶体管m57通过输入到其栅极的选择信号s2而导通时,晶体管m57从复位电源向oled元件e1的阳极供应复位电位vrst。复位电源的另一端与gnd连接。

137.晶体管m55控制是否向驱动晶体管m53的栅极供应复位电位。当晶体管m55通过输入到其栅极的选择信号s1而导通时,晶体管m55从与其源极/漏极连接的复位电源向驱动晶体管m53的栅极供应复位电位vrst。复位电源的另一端与gnd连接。oled元件e1的阳极的复位电位与驱动晶体管m53的栅极的复位电位可以不同。

138.晶体管m52是用于选择要被供应数据信号的像素电路550的选择晶体管。晶体管m52的栅极电压由选择信号s2控制。选择晶体管m52当其导通时将从驱动ic 117通过数据线供应的数据信号vdata供应给驱动晶体管m53的栅极(存储电容器cst)。

139.在本示例中,选择晶体管m52被连接在数据线和驱动晶体管m53的源极之间。进一步地,晶体管m54被连接在驱动晶体管m53的漏极和栅极之间。

140.晶体管m54用于校正驱动晶体管m53的阈值电压。当晶体管m54导通时,驱动晶体管m53变为二极管连接的状态。来自数据线的数据信号vdata通过导通的选择晶体管m52、驱动晶体管m53和晶体管m54的沟道(源极和漏极)被供应给存储电容器cst。

141.存储电容器cst用于保持驱动晶体管m53的栅极-源极电压;其一端与驱动晶体管m53的栅极连接,另一端与在晶体管m51的源极与阳极电源之间的节点连接。存储电容器cst保持根据驱动晶体管m53的阈值电压vth调整的数据信号(电压)。

142.图16是在一帧时段中控制图15所示的像素电路550的信号的时序图。图16是选择第n级像素电路行并将数据信号vdata写入像素电路550的时序图。

143.图16示出了发光控制信号em_n、选择信号s1_n和选择信号s2_n在一帧内的变化。

144.在时刻t11,发光控制信号em从低变为高。晶体管m51和m56断开。在时刻t11,选择信号s1_n和s2_n为低。根据这些控制信号,晶体管m52、m54、m55和m57断开。这些晶体管的状态被保持直至时间t11之后的时间t12。

145.在时刻t12,选择信号s1_n从低变为高。在时刻t12,发光控制信号em_n为高并且选择信号s2_n为低。晶体管m55响应于选择信号s1_n的变化而导通。晶体管m51、m52、m54、m56和m57断开。

146.响应于晶体管m55导通,驱动晶体管m53的栅极电位变化到复位电位vrst。从时刻t12到时刻t13,复位电位vrst被供应给驱动晶体管m53的栅极。驱动晶体管m53可以通过在其栅极被供应复位电位来减少滞后效应。

147.在时刻t13,选择信号s1_n从高变为低,选择信号s2_n从低变为高。发光控制信号em_n为高。晶体管m55响应于选择信号s1_n的变化而断开。晶体管m52、m54和m57响应于选择信号s2_n的变化而导通。晶体管m51和m56断开。

148.响应于晶体管m57导通,复位电源的复位电位vrst被供应给oled元件e1的阳极。由于晶体管m54导通,因此驱动晶体管m53被进行二极管连接。由于晶体管m52导通,因此来自数据线的数据信号vdata通过晶体管m52、m53和m54被写入存储电容器cst。

149.要写入存储电容器cst的电压是在将对驱动晶体管m53的阈值电压vth的校正并入数据信号vdata之后的电压。在时刻t13至时刻t14的时段,进行数据信号vdata向像素电路550的写入以及对驱动晶体管m53的阈值补偿。

150.在时刻t14,选择信号s2_n从高变为低。在时刻t14,发光控制信号em_n为高并且选择信号s1_n为低。晶体管m52、m54和m57响应于选择信号s2_n的变化而断开。晶体管m51、m52和m54至m57断开。控制信号和晶体管的这些状态从时刻t14到时刻t15保持。

151.在时刻t15,发光控制信号em_n从高变为低,晶体管m51和m56从断开变为导通。选择信号s1_n和s2_n为低;晶体管m52、m54、m55和m57仍然断开。

152.驱动晶体管m53基于存储电容器cst中存储的调整后的数据信号来控制供应给oled元件e1的驱动电流。这意味着oled元件e1发光。在图16的时序图中,从时刻t11到时刻t12、从时刻t12到时刻t13、从时刻t13到时刻t14中的每一个时段具有1h的长度。在图15和图16所示的配置示例中,阈值补偿和数据写入是在同一时段内进行,并且它们不分开执行。

153.在下文中,说明通过在图15和图16所示的配置示例中设定的移位寄存器电路和锁存电路的组合来生成和输出控制信号s1、s2和em的方法。图17图示了在锁存电路组中使用的锁存电路380的配置示例。虽然图17示出了第n级锁存电路380,但是其他级的锁存电路具有相同的配置。

154.锁存电路380包括四个晶体管和一个电容元件。四个晶体管m61至m64是n型晶体管。晶体管m61处于二极管连接状态;它在其漏极接收来自set端子381的输入。晶体管m62被连接在晶体管m61和用于供应电源电位pvee的电源之间,并且在其栅极接收来自rst端子382的输入。

155.晶体管m63被连接在用于供应电源电位pvdd的电源和q端子383之间,并且其栅极与在晶体管m61和m62之间的中间节点连接。晶体管m64被连接在晶体管m63和供应电源电位pvee的电源之间,并在其栅极接收rst输入。电容元件cd被连接在晶体管m63的栅极和q端子383之间。q端子383与在晶体管m63和m64之间的中间节点连接。

156.图18是锁存电路380的输入信号和输出信号的时序图。在锁存电路380中,当信号的逻辑电平为h时,电位电平为高。锁存电路380的真值表与图6中的真值表相同。

157.当set信号和rst信号都处于低电位电平时,q输出处于低电位电平。当set输入变为高电位电平时,q输出变为高电位电平。即使set输入随后变为低电位电平,q输出也保持高电位电平。此后,响应于rst输入变为高电位电平,q输出变为低电位电平。随后,rst输入变为低电位电平,q输出保持低电位电平。

158.图19示意性地图示了利用移位寄存器电路和锁存电路组的组合来生成和输出控制信号s1、s2和em的电路配置的示例。图19示出了移位寄存器电路507和锁存电路组中的一个锁存电路380。移位寄存器电路507与移位寄存器电路111一样,包括串联的多个移位寄存器单元。移位寄存器电路507可以具有期望的电路结构。在一个实施方式中,移位寄存器电路507中包含的晶体管均为n型tft。

159.多个移位寄存器单元依次输出信号脉冲。信号脉冲处于高电位电平。第n级移位寄存器单元的输出s_n被输入到第n级像素电路行的s2信号线、第(n 1)级像素电路行的s1信号线、第(n-2)级锁存电路380的rst端子和第(n 2)级锁存电路380的set端子。s1信号线和s2信号线为第一控制线。

160.移位寄存器单元向两个像素电路行输出选择信号s1和s2,进而向两个锁存电路380输出rst信号和set信号。由上述可知,移位寄存器单元的输出脉冲为一个相关联的像素电路行的s2信号脉冲和另一个相关联的像素电路行的s1信号脉冲(第三信号脉冲)。

161.例如,第n级像素电路行的选择信号s1_n为第(n-1)级移位寄存器单元的输出信号s_n-1。第n级像素电路行的选择信号s2_n为第n级移位寄存器单元的输出信号s_n。

162.如上所述,第n级锁存电路380在set端子接收来自第(n-2)级移位寄存器单元的输出信号s_n-2并且在rst端子接收来自第(n 2)级移位寄存器单元的输出信号s_n 2。第n级锁存电路380从q端子输出用于第n级像素电路行的发光控制信号em_n。q端子的输出由信号脉冲控制到达set端子和rst端子。用于传输发光控制信号的em信号线为第二控制线。

163.从以上可以理解,该配置示例从第n级像素电路行之前的两行和之后的两行的像素电路行的移位寄存器信号生成第n级像素电路行的发光控制信号em_n。发光控制信号em的脉冲的时段为4h。该配置示例中的发光控制信号em被供应给p型晶体管m51和m56的栅极,因此,发光控制信号em具有与选择信号s1和s2相同极性的脉冲。

164.具有相同极性的脉冲意味着信号处于高电平的时段明显短于信号处于低电平的时段。通过采用n型tft而不是采用p型tft,可以用较少数量的tft构成用于产生这种信号的电路以实现较小的电路面积。在一个实施方式中,锁存电路和移位寄存器电路中包含的晶体管均为n型tft。

165.如上所述,参考图15描述的像素电路550包括用于发光控制晶体管m56和m51和驱动晶体管m53的p型(第二导电型)tft和用于开关晶体管m52、m54、m55和m57的n型(第一导电型)tft。如参考图19所描述的,来自移位寄存器电路507的控制线(第一控制线)传输选择信号s,来自锁存电路380的控制线(第二控制线)传输发光控制信号em。在移位寄存器电路507和锁存电路308中包括的所有晶体管都是n型(第一导电型)tft。

166.如上所述,该配置示例利用包括n型tft的移位寄存器电路和锁存电路组生成和输出选择信号s1和s2以及脉冲宽度长于1h的发光控制信号em。如果像素电路550中的晶体管

的导电类型改变为相反的导电型,并且移位寄存器电路和锁存电路包括p型tft,则移位寄存器电路和锁存电路可以由一种导电类型的晶体管构成。

167.锁存电路的装置结构

168.以下,描述锁存电路的装置结构的示例。图20是示意性地示出锁存电路300的布局示例的平面图。如参照图7所述,锁存电路300包括晶体管m21至m24和电容元件cb。在图20中,相同材料的层由相同的图案表示。具体地,锁存电路300包括半导体层sc、第一金属层mt1和第二金属层mt2。

169.图21示意性地示出了沿图20中的剖面线xxi-xxi的剖面结构。图21示出了晶体管m22的剖面结构。底涂膜uc设置在绝缘基板sub上。底涂膜uc可以是氮化硅膜。

170.半导体层sc设置在底涂膜uc上。半导体层sc可以是多晶硅。在tft为n型的情况下,可以使用氧化物半导体。半导体层sc被栅极绝缘膜gi覆盖。栅极绝缘膜gi可以是氧化硅膜、氮化硅膜或这些膜的叠层。

171.在第一金属层mt1中包括的栅极电极gt和第一配线ml1设置在栅极绝缘膜gi上。例如,mo、w、nb或al可以用于第一金属层mt1。

172.第一金属层mt1和从第一金属层mt1暴露的栅极绝缘膜gi被层间绝缘膜ild覆盖。层间绝缘膜ild可以是氮化硅膜或氧化硅膜。在第二金属层mt2中包括的第二配线ml2设置在层间绝缘膜ild上。

173.第二配线ml2的一部分经由穿过层间绝缘膜ild和栅极绝缘膜gi开口的接触孔与半导体层sc接触。第二配线ml2的另一部分经由穿过层间绝缘膜ild和栅极绝缘膜gi开口的接触孔与半导体层sc接触,并且进一步经由穿过层间绝缘膜ild开口的接触孔与第一配线ml1接触。整个锁存电路300被保护绝缘膜pv覆盖。保护绝缘膜pv可以是无机膜,例如氮化硅膜或氧化硅膜。

174.如上所述,已经描述了本发明的实施方式;然而,本发明不限于前述实施方式。本领域技术人员可以在本发明的范围内容易地修改、添加或转换前述实施方式中的各个元件。一个实施方式的配置的一部分可以用另一实施方式的配置替换,或者一个实施方式的配置可以合并到另一实施方式的配置中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。