具选择性屏蔽式凹陷场效电板的高密度功率元件

1.相关案件的交叉参考

2.2019年8月12日所申请的美国申请案第62/885,708号、以及2020年6月12日所申请的美国申请案第63/038,571号中主张优先权,其两者在此并入供参考。

技术领域

3.本发明申请案是关于在半导体块体(semiconductor mass)的表面附近具有多数载子源极区的功率半导体元件,尤其是关于功率金氧半导体场效电晶体(mosfet)。

背景技术:

4.注意,以下所讨论的各要点可能反映从所揭示各发明获得的后见之明,并不必然认为背景技术。

5.在许多电子应用中,功率mosfet广泛使用为切换元件。为了尽量减少其传导功率损耗,所需功率mosfet具有低具体导通电阻(rsp或r*a),其定义为mosfet的导通电阻乘以主动(active)晶粒面积的乘积。降低rsp的最常见方式是缩小元件的单位单体间距(cell pitch,cp),以提高每单位面积的单体的封装密度或数量。然而,随着单体密度提高,元件的等相关联本质电容(intrinsic capacitance)(诸如闸极-源极电容(cgs)、闸极-汲极电容(cgd)、总输入电容(ciss)、和总输出电容(coss))也提高。因此,对于较高单体密度元件,元件的切换功率损耗将提高。

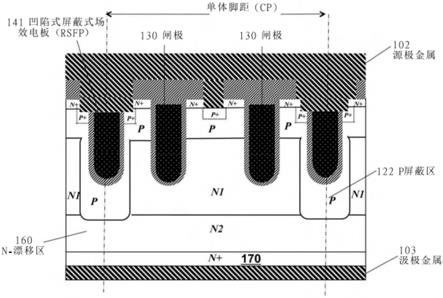

6.具例诸如图1(a)所示的凹陷场效电板(recessed field plate,rfp),或具例诸如图1(b)和图1(c)所示的凹陷式屏蔽式场效电板(recessed shielded field plate,rsfp)141的功率mosfet结构,提供较低rsp和cgd,也即较低总闸极电荷(qg)和「米勒(miller)」电荷(qgd)。(除了n-增强区以外,rsfp具有p屏蔽补偿区122。)例如,参见并入供参考的美国专利案第8076719号和第8659076号。具p屏蔽结构的rfp在反向偏压下的p主体区中提供空乏型(depletion)降低,并藉由降低在闸极沟槽的底部的电场而改良元件可靠度。如图1(a)所示的厚底部氧化物124或如图1(c)所示的分裂闸极结构126的使用,将降低qg和qgd。

7.具有rfp沟槽140和p屏蔽区122的mosfet结构提供数个优势。总导通电阻ron是决定为通道的导通电阻(rch)加上漂移区的电阻rdrift的总和。等沟槽式闸极电极130建立用于电流传导(引起rch)的主动路径,而n-漂移层和n 基材促成rdrift。rsp的进一步降低是受到提高单体/通道密度或降低cp的能力的限制。降低cp(也即各p屏蔽区的间的间隔)导致由等p屏蔽区(接面场效电晶体(jfet)闸极)和n-增强(jfet通道)所形成的寄生jfet的夹断电压效应(pinching)。jfet通道夹断电压效应导致rdrift提高,并降低载流能力(jfet饱和电流)idsat。因此,重要的是要认识到,在目前rfp mosfet结构中,存在对单体密度提高的限制。

技术实现要素:

8.除了其他创新之外,本发明申请案教示一种凹陷场效电板沟槽(或屏蔽式凹陷场

效电板沟槽或其类似物)围绕多个相邻闸极电极的垂直元件结构。因此,具体导通状态电导为提高,因为场效电板面积与通道面积的比率为降低。各种改型在单个rfp或rsfp沟槽布局(layout)的内部使用两、三、或多个可分辨闸极电极。

附图说明

9.所揭示各发明将参考显示各重要范例具体实施例并并入本说明书供参考的多个附图来说明,其中:

10.图1(a)显示先前所提出具凹陷场效电板(rfp)的元件结构的范例。

11.图1(b)和图1(c)显示先前所提出具凹陷屏蔽式场效电板(rsfp)的元件结构的范例。

12.图2显示n通道mosfet基本单体结构的范例。

13.图3显示类似于图2所示,但具附加第三闸极沟槽电极的另一具体实施例。

14.图4显示类似于图3所示,但具采用厚底部氧化物填充的等闸极沟槽的另一具体实施例。

15.图5(a)显示类似于图4所示,但具有分裂闸极的另一具体实施例。

16.图5(b)显示类似于图5(a)所示,但具等rfp沟槽中的各分裂电极的另一具体实施例。

17.图6(a)显示具由嵌入式rsfp电极所围绕的两闸极电极的俯视示意布局。图6(b)、图6(c)、和图6(d)显示沿着图6(a)的x-y坐标线的各种剖面。

18.图7(a)显示替代性具体实施例,其中等屏蔽区由多个植入产生。

19.图7(b)显示另一替代性具体实施例。

20.图8(a)显示范例具体实施例的掺杂轮廓。图8(b)概略显示在图8(a)的结构中,在65v所施加电压下的崩溃附近的电场(电位等值线)。

21.图9(a)和图9(b)共同显示图9(b)中的创新结构的范例与图9(a)中的先前结构之间的比较。

22.图10(a)显示搭配所揭示各发明使用的范例布局的俯视图。

23.图10(b)显示搭配所揭示各发明使用的另一范例布局的俯视图。

24.图10(c)显示各创新结构的各范例。左侧的场效电板结构是rsfp,而右侧的场效电板结构是rfp。

25.图11显示使用以上所说明的数种创新构想的绝缘闸极双载子电晶体(igbt)。

26.附图标记

27.102:源极金属

28.102’:射极金属

29.103:汲极金属

30.103’:集极金属

31.120:沟槽式闸极电极条状;条状

32.121:p井区

33.122:p屏蔽补偿区;p屏蔽区

34.124:厚底部氧化物

35.126:分裂闸极结构;分裂闸极

36.130:沟槽式闸极电极;主体接触;闸极

37.140:凹陷场效电板(rfp)沟槽;凹陷场效电板;rfp

38.141:凹陷式屏蔽式场效电板(rsfp);rsfp沟槽;rsfp

39.160:n-漂移区

40.162:n-增强区

41.170:n

具体实施方式

42.本发明申请案的众多创新教示将可特别参考目前各较佳具体实施例(藉由范例而非限制)说明。本发明申请案说明数种发明,且以下陈述通常不应视为限制诸请求项。

43.在本技术案中,揭示使用选择性屏蔽式凹陷场效电板结构的新型屏蔽式rfp mosfet元件。这些新型mosfet结构藉由使用每单位面积较高通道密度而达成较低rsp,从而允许高饱和电流idsat,同时仍然维护rfp结构的性能与可靠度优势。

44.在本发明的一具体实施例中,n通道mosfet基本单体结构是显示在图2中。该新型结构单体具有两闸极电极和一rfp电极。对于相同主动面积、设计规则、和处理能力,闸极沟槽与rfp沟槽的比率为大致加倍。所以,图2中的该新型结构的每单位面积通道密度为较高。再者,n-漂移区是由不同掺杂层组成,例如一上层n1和一下层n2。依所需最佳化(对于额定工作电压)而定,n1可具有低于、高于、或相同于n2的电阻率。n1和/或n2区的任一者可藉由植入n型掺杂物,或藉由利用生长在高浓度掺杂n 基材上面的磊晶层而形成。或者,n1和n2层可由逐渐变化掺杂轮廓所替代。掺杂梯度可为例如线性或其他分布。rfp和闸极沟槽可为实质相等深度。闸极和rfp沟槽壁是采用绝缘材料(诸如二氧化硅(sio2))衬里。闸极和rfp电极是由导电材料(诸如掺杂多晶硅)形成。rfp电极是一独立偏压,或(更佳为)连接到源极电极。重要的是要注意,p屏蔽区的间的n-增强掺杂隔开是设计成减少rdrift并提高jfet饱和电流。

45.rfp沟槽140、rsfp沟槽141、和沟槽式闸极电极130的各部位称为「可分辨」,若其在剖面中为隔开,如在此所例示,即使其为电连接在一起。此外注意到,称为「可分辨」的各要素不必然以任何其他方式彼此不同。

46.图3显示另一具体实施例,其通常在某种程度上类似于图2所示,但具一附加第三闸极沟槽电极。因此,图3的新型结构的每单位面积通道密度是高于图2。此概念是可进一步扩展到在每个单体中具有闸极沟槽的数量较高于rfp沟槽的mosfet。因此,较高密度rfp结构可藉由选择性使用rfp沟槽的较少数量及/或位置而实现。此等结构具有最佳化汲极饱和电流idsat的优势,其中边界条件为:idsat的最小值(以满足应用电流能力要求),以及idsat的最大值(以满足对于短路条件下的限流的要求)。在此等结构中,rfp沟槽和对应p屏蔽区、漂移层厚度、与掺杂是设计成在闸极沟槽保持足够低的电场,并降低关闭(off)状态下的p主体区的空乏。

47.图4显示另一具体实施例,其通常在某种程度上类似于图3所示,但具采用厚底部氧化物填充的闸极沟槽,以尽量减少闸极电极和汲极漂移区的重迭以降低cgd。

48.图5(a)显示另一具体实施例,其通常在某种程度上类似于图4所示,但具有分裂闸

极以降低cgd。分裂闸极较佳为连接到源极端子(未显示)。

49.图5(b)显示另一具体实施例,其通常在某种程度上类似于图5(a)所示,但具rfp沟槽中的各分裂电极。

50.在其他具体实施例中,图6(a)所示的等元件结构、具由rsfp电极所围绕的两闸极电极的俯视示意布局,以及图6(b)、图6(c)、和图6(d)通常在某种程度上类似于图2、图4、和图5(a)所示,但具嵌入并具有顶部介电材料的rfp电极。再者,不同或自对准金属接触设计可用于提高单体密度。嵌入式rfp或rsfp电极为独立偏压,或(更佳为)连接到源极电极或闸极电极。

51.图7(a)显示替代性具体实施例,其中屏蔽区由多个植入产生。在此范例中,所生成的屏蔽向下延伸到汲极区的更低度掺杂部分。

52.图7(b)显示另一替代性具体实施例。在此,屏蔽区亦具有由多个植入产生的轮廓。然而,在此范例中,汲极区并未包括图7(a)所示的更高度掺杂部位。

53.图8(a)显示范例具体实施例的掺杂轮廓。在此范例中,有由凹陷场效电板电极的两部位所围绕的两平行闸极电极条状(以剖面显示)。(以剖面显示的两部位可为分开条状,或可为围绕闸极电极的单个大矩形(或其他闭合路径)的各部分。)在此范例中,磊晶层厚度为6.5μm,且掺杂为2.3e16 cm-3,且p屏蔽总剂量为3.1e13 cm-2。

54.图8(b)概略显示在图8(a)的结构中,崩溃(在此范例中的65v所施加电压下)附近的电场(电位等值线)。

55.图9(a)和图9(b)联合显示图9(b)中的创新结构的范例与图9(a)中的先前结构(其具有由沟槽式凹陷场效电板所围绕的仅一闸极条状)之间的比较。所示的图式是电流流线图示;注意到,图9(a)中的结果显示比图9(b)中更高的电流密度。此显示图9(b)的结构降低jfet夹断电压效应。

56.图10(a)显示搭配所揭示发明使用的范例布局的鸟瞰图。两沟槽式闸极电极条状120是仅由主体接触130的条状所侧向隔开(在布局中)。等两条状120是由凹陷场效电板140所联合围绕。坐标线x-y指出正交于其中采取图10(c)的剖面图的表面的平面。

57.图10(c)显示多个创新结构的比较。左侧的场效电板结构是rsfp,而右侧的场效电板结构是rfp。

58.图10(b)显示搭配所揭示发明使用的另一范例布局的鸟瞰图。

59.图11显示使用以上所说明的数种创新构想的绝缘闸极双载子电晶体(igbt)。然而,漂移区轮廓变更,以在通道下方的p-n接面实施某种程度的少数载子产生,习惯上采用igbt元件。注意到,在此范例中,漂移区的轮廓是由在底部添加n型缓冲掺杂层所修饰。

60.使用本发明中所说明的方法制造的各元件的等具体电气特性取决于若干因素(包括层的厚度、其掺杂程度、所使用的材料、布局的几何形状等)。熟习该项技艺者将明白,模拟、实验、或其组合可用于判定如所欲操作所需要的设计参数。

61.尽管此本发明示出的图式为定性正确,但实作上所使用的几何形状可能不同,且不应以任何方式视为限制。熟习该项技艺者了解到,实际布局将依实施的具体情况而变化,且本文所例示的任何叙述不应以任何方式视为限制。

62.此外,新型结构可使用不同半导体材料(诸如硅、碳化硅等)实现。

63.优势

64.在各种具体实施例中,所揭示创新提供至少下列多个优势之一或多者。然而,这些优势并非所有皆由所揭示的创新的每一者产生,且此等优势的列举并未限制各种所请求的发明。

65.·

改善的功率转换系统效率;

66.·

具较高崩溃电压的功率半导体元件;

67.·

具较低具体导通电阻的功率半导体元件;及/或

68.·

对于特定电压和电流额定值具较低成本的功率半导体元件。

69.根据一些但不必然是全部具体实施例,其提供:一种半导体主动元件结构,其包含:多个闸极沟槽,其在一半导体基材中,每个闸极沟槽含有一闸极电极,其与基材的各相邻部位绝缘,并电容耦合到基材的相邻第一导电类型通道部位;一成对凹陷场效电板沟槽,其围绕等多个闸极沟槽;多个第二导电类型源极区,其定位接近等闸极沟槽,以发射可经过各自沟槽的表面附近的多数载子;一第二导电类型汲极区,其位于等闸极沟槽下面。

70.根据一些但不必然是全部具体实施例,其提供:一种半导体主动元件结构,其包含:多个闸极沟槽,其在一半导体基材中,每个闸极沟槽含有一闸极电极,其与基材的各相邻部位绝缘,并电容耦合到基材的一相邻第一导电类型通道部位;一成对凹陷场效电板沟槽,其围绕前述闸极沟槽的两者,使得闸极沟槽的一些是相邻于凹陷场效电板沟槽的一者、以及闸极沟槽的另一者;多个第二导电类型源极扩散区,其定位接近闸极沟槽,以发射可经过各自沟槽的表面附近的多数载子;一第二导电类型汲极区,其位于闸极沟槽下面。

71.根据一些但不必然是全部具体实施例,其提供:一种用于制造半导体元件的方法,其按任何顺序包含下列动作:a)制造复数隔开闸极电极;以及b)制造围绕复数隔开闸极电极,但未插入在至少一些相邻成对闸极电极之间的一凹陷场效电板结构。

72.根据一些但不必然是全部具体实施例,其提供:一种用于制造半导体元件的方法,其按任何顺序包含下列动作:a)在一第一导电类型主体区(其位于一第二导电类型漂移区上方)内制造多个可分辨沟槽式闸极电极;b)制造侧向围绕多个闸极电极,但未插入在至少一些相邻成对闸极电极之间的一凹陷场效电板结构;c)形成通常在凹陷场效电板结构(而非主体区内的闸极电极)下方的一屏蔽区;以及d)在漂移区内形成提高漂移区的导通状态导电性的一附加第二导电类型掺杂组件。

73.根据一些但不必然是全部具体实施例,其提供:一种半导体主动元件,其包含:一沟槽式闸极电极,其采用一第一布局图案;一沟槽式场效电板电极,其采用一第二布局图案;其中沟槽式场效电板电极的布局图案侧向封围沟槽式闸极电极的整个布局图案;且其中沟槽式闸极电极的各部位彼此侧向联接,而沟槽式场效电板电极的任何部位则未联接。

74.根据一些但不然是全部具体实施例,其提供:一种半导体主动元件,其包含:一沟槽式闸极电极,其采用一第一布局图案;一沟槽式场效电板电极,其采用一第二布局图案;其中沟槽式场效电板电极的布局图案侧向封围沟槽式闸极电极的整个布局图案;其中沟槽式闸极电极的各部位彼此侧向联接,而沟槽式场效电板电极的任何部位则未联接;以及一第二导电类型源极区,其定位接近沟槽式闸极电极,以发射可经过沟槽式闸极电极的表面附近,并从其进入一第二导电类型漂移区的多数载子。

75.根据一些但不必然是全部的具体实施例,提供:一种凹陷场效电板沟槽围绕多个相邻闸极电极的垂直电晶体结构。因此,具体导通状态电导为提高,因为凹陷场效电板面积

与通道面积的比率降低。各种改型使用单个rfp或rsfp沟槽布局的内部的两、三、或多个隔开闸极电极。

76.修饰例和变化例

77.熟习该项技艺者将明白,本发明申请案中所说明的创新概念在极大应用范围内可修饰和变化,且因此专利性标的事项的范畴并未受到任何特定具体示例性教示。所欲是接受落于文后申请专利范围的精神与广泛范畴内的所有此等替代例、修饰例、和变化例。

78.例如,还考虑到,在各种替代例中,可布局四或多个闸极条状,平行于单个凹陷场效电板或凹陷屏蔽式场效电板沟槽的周边或在其内部。

79.此外,还预期到,若有需要,所揭示发明可应用于半导体覆绝缘体(semiconductor-on-insulator,soi)实施。

80.此外,还考虑到,如maxpower semiconductor inc.的其他专利和公开申请案中所示的其他补偿区形状修饰例可亦用于修饰前述教示。例如,但不限于,任何下列内容及其组合可结合熟习功率半导体元件技艺者的知识使用,以教示或建议适当修饰例:美国专利案7910439、7911021、7923804、7960783、7989293、8076719、8304329、8310001、8310006、8310007、8319278、8330186、8330213、8330214、8354711、8378416、8390060、8546893、8564057、8581341、8680607、8704295、9024379、9048118、10062788、和10529810,其整个在此并入供参考。

81.此外,亦可设想可使用p型源极,采用反向的施加电压。

82.此外,熟习功率半导体元件的领域技术者已习知,厚度/掺杂变更可施加以实施不同的工作电压。

83.结构的所有以上变体可采用条状或单元式布局(诸如正方形、矩形、六角形、或圆形布局)实现。

84.此外,应理解,以上多个具体实施例的众多组合为亦可实现。

85.此外,可理解,各种半导体材料可使用,诸如硅(si)、碳化硅(sic)、或sige、或其他二元或三元iv族化合物半导体。或者但不是较佳,所揭露发明可调适搭配其他半导体材料(诸如iii-v化合物半导体、iii-n半导体、或其他)一起使用。

86.本发明申请案中的说明内容不应理解为意味着任何特定要素、步骤、或功能必须包括在所主张范畴内的基本要素:专利标的事项的范畴仅由文后发明申请范围所定义。此外,除非用词「构件」前导元件名称,否则这些请求项并未意要援用美国专利法第35篇第112条第6项。

87.如所申请的诸请求项旨在尽可能全面性,且没有标的事项旨在让与、献给、或放弃。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。