一种低压台面tvs半导体芯片及其制造方法

技术领域

1.本发明涉及芯片制造领域,具体是一种低压台面tvs半导体芯片及其制造方法。

背景技术:

2.瞬态抑制二极管tvs产品,广泛应用于家用电器、计算机系统、网络通信等方面。而近年来,对低压tvs器件的漏电流大小和浪涌性能要求的越来越高,从而触发更多新型结构低压tvs半导体芯片的产生。传统低压台面tvs半导体芯片的制作方法以p型硅基底材料,芯片结构自上而下为npn的三层结构,该结构由于击穿发生于槽内,并且高温扩散会将多余的杂质扩入硅片内,导致产品漏电流不受控,浪涌性能降低。因此,需要发明一种新的技术方案来解决上述问题。

3.以传统低压台面tvs半导体芯片为例,通过扩散的形式在p型硅片正背面形成大面积的n 结,通过挖槽实现隔离,击穿主要发生在槽内。同时高温扩散会将多余的杂质扩入硅片内和槽内清洗问题,会导致低压tvs漏电不受控,降低芯片的可靠性。为了进一步提高芯片的漏电性能。

4.在已经公开的文件cn201610874344-一种低电容功率tvs器件及其制造方法中,包括n型半导体基体、n 型扩散层、p 型扩散层、离子注入区、钝化层、金属层。将功率tvs二极管和低电容的二极管串联集成在单一芯片上,没有吸杂区无法吸收高温扩散,将多余的杂质扩入硅片内,并且芯片漏电的几率也会变高,器件ipp通流能力变差。

技术实现要素:

5.为了解决上述问题,本发明公开了一种低压台面tvs半导体芯片及其制造方法,避免槽内击穿,有效提高减少芯片漏电的几率和提高器件ipp通流能力。

6.本发明的技术方案为:一种低压台面tvs半导体芯片,包括p型硅片,p型硅片的正面和背面设有上下对称的环状玻璃钝化沟槽,沟槽内设有玻璃钝化层,p型硅片的表面生长有氧化层,氧化层间隙刻蚀有电极,p型硅片的正面和背面设有n 击穿区,正面和背面设有n 吸杂区,n 吸杂区和n 击穿区与p型硅片之间pn结形成了下凹上凸的结构。

7.进一步地,n 吸杂区位于玻璃钝化层和氧化层之间下方的位置为朝向两侧的向下和向上的凹陷,电极中部下方的位置为为朝向电极的上凸和下凸的结构。

8.进一步地,p型硅片包括半导体材料soi、砷化镓、氮化镓、磷化铟、碳化硅或锗硅,p型硅片的厚度为150~300μm、电阻率为0.004~0.05ω

·

cm。

9.进一步地,n 吸杂区的结深在10~40μm, n 击穿区的结深在5~20μm。

10.一种制造低压台面tvs半导体芯片的方法,包括下列步骤:步骤1:选择p型硅片;步骤2:在p型硅片表面生长氧化层,进行正面、背面n 吸杂区的光刻,光刻后进行正面、背面n 吸杂区磷预扩散和再扩散分布,窗口区域的局部扩散,磷掺杂在p型硅片衬底之间的横向、纵向扩散,形成下凹的pn结结构;

步骤3:去除氧化层后,在p型硅片进行n 击穿区正面、背面磷预扩散,在通pocl3的扩散内进行预沉积,击穿区为整面磷掺杂,为纵向扩散,同时由于p型材料本身的补偿作用,吸杂区和击穿区与p型材料三者之间形成了上凸的pn结构结构,使击穿发生在击穿区而不是槽内;步骤4:进行沟槽光刻,然后台腐,在p型硅片和正面、背面n 吸杂区交接处形成环状钝化沟槽;步骤5:金属淀积、光刻、刻蚀,氧化层间隙形成t1/t2电极;步骤6:合金。

11.进一步地,步骤1中的p型硅片片厚150~300μm,电阻率为0.004~0.05ω

·

cm。

12.进一步地,步骤2中的预扩散条件为:温度1000℃~1180℃,时间50min~100min,在通pocl3的扩散内进行预沉积;再扩散条件为:氮气气氛下,温度1180℃~1250℃,时间5h~30h,形成正正面、背面n 吸杂区2,结深10~40μm。

13.进一步地,步骤3中预扩散条件为:温度800℃~1100℃、时间50min~100min,再扩散条件为:氮气气氛下、温度1100℃~1250℃、时间2h~15h,结深5~20μm,击穿区为整面磷掺杂,为纵向扩散。

14.进一步地,步骤7中合金的条件为炉温400~530℃、时间10min~30 min、真空度10-3

pa。

15.n 吸杂区,磷的吸杂原理是硅中掺杂的磷原子易与杂质原子因库仑力形成离子配对,起到俘获杂质的作用。同时磷的浓度越高,产生的失配位网格密度越大,离子配对几率越大,对杂质离子的俘获能力越强,吸杂能力更显著。同时n 吸杂区结深深,击穿电压高;n 击穿区结深浅,击穿电压低,所以n 吸杂区和n 击穿区与p型硅片之间pn结形成了下凹上凸的结构,会提前在击穿区发生击穿,避免了槽内击穿。

16.本发明的有益之处:1、本发明通过在器件体内引入n 吸杂区,重磷掺杂的俘获作用,成功吸收了高温扩散扩入的杂质。

17.2、本发明n 吸杂区和n 击穿区与p型硅片之间pn结形成了下凹上凸的结构,使得击穿提前发生在浅结处的击穿区,避免了槽内击穿。

18.3、本发明将传统低压台面tvs的槽内击穿转移到体内击穿,因此改善了低压台面tvs芯片的漏电流,从而提高了器件ipp通流能力。

附图说明

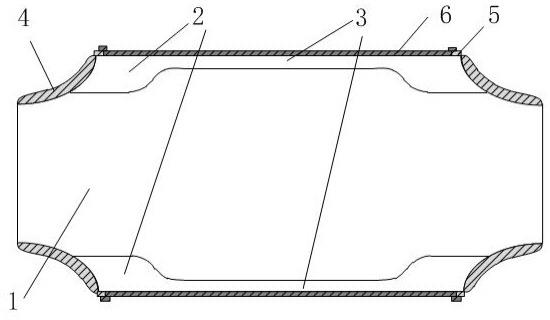

19.图1为本发明的结构示意图;其中:1、p型硅片,2、n 吸杂区,3、n 击穿区,4、玻璃钝化层,5、氧化层,6、电极。

具体实施方式

20.为了加深对本发明的理解,下面结合附图详细描述本发明的具体实施方式,该实施例仅用于解释本发明,并不构成对本发明的保护范围的限定。

21.如图1所示,实施例1一种低压台面tvs半导体芯片,包括p型硅片1,p型硅片1的正面和背面设有上下对

称的环状玻璃钝化沟槽,沟槽内设有玻璃钝化层4,p型硅片1的表面生长有氧化层5,氧化层5间隙刻蚀有电极,p型硅片1的正面和背面设有n 击穿区3,正面和背面设有n 吸杂区2,n 吸杂区2和n 击穿区3与p型硅片1之间pn结形成了下凹上凸的结构。

22.n 吸杂区2位于玻璃钝化层4和氧化层5之间下方的位置为朝向两侧的向下和向上的凹陷,电极6中部下方的位置为为朝向电极6的上凸和下凸的结构。

23.p型硅片为半导体材料soi,p型硅片1的厚度为150μm、电阻率为0.004ω

·

cm。

24.n 吸杂区2的结深在10μm, n 击穿区2的结深在5μm。

25.一种制造低压台面tvs半导体芯片的方法,包括下列步骤:步骤1:选择硅片片厚150μm,电阻率为0.004ω

·

cm的p型硅片1;步骤2:在p型硅片1表面生长氧化层5,进行正面、背面n 吸杂区2的光刻,光刻后进行正面、背面n 吸杂区2磷预扩散和再扩散分布,预扩散条件为:温度1000℃,时间50min,在通pocl3的扩散内进行预沉积;再扩散条件为:氮气气氛下,温度1180℃,时间5h,形成正正面、背面n 吸杂区2,结深10μm,窗口区域的局部扩散,磷掺杂在p型硅片衬底之间的横向、纵向扩散,形成下凹的pn结结构;步骤3:去除氧化层5后,在p型硅片1进行n 击穿区3正面、背面磷预扩散,在通pocl3的扩散内进行预沉积,进行再扩散分布,温度800℃、时间50min,再扩散条件为:氮气气氛下、温度1100℃、时间2h,形成正面、背面n 击穿区,结深5μm,击穿区为整面磷掺杂,为纵向扩散;步骤4:进行沟槽光刻,然后台腐,在p型硅片1和正面、背面n 吸杂区2交接处形成环状钝化沟槽;步骤5:金属淀积、光刻、刻蚀,氧化层间隙形成t1/t2电极6;步骤6:合金,合金的条件为炉温400℃、时间10min、真空度10-3

pa。

26.实施例2一种低压台面tvs半导体芯片,包括p型硅片1,p型硅片1的正面和背面设有上下对称的环状玻璃钝化沟槽,沟槽内设有玻璃钝化层4,p型硅片1的表面生长有氧化层5,氧化层5间隙刻蚀有电极,p型硅片1的正面和背面设有n 击穿区3,正面和背面设有n 吸杂区2,n 吸杂区2和n 击穿区3与p型硅片1之间pn结形成了下凹上凸的结构。

27.n 吸杂区2位于玻璃钝化层4和氧化层5之间下方的位置为朝向两侧的向下和向上的凹陷,电极6中部下方的位置为为朝向电极6的上凸和下凸的结构。

28.p型硅片为砷化镓,p型硅片1的厚度为300μm、电阻率为0.05ω

·

cm。

29.n 吸杂区2的结深在40μm, n 击穿区2的结深在20μm。

30.一种制造低压台面tvs半导体芯片的方法,包括下列步骤:步骤1:选择硅片片厚150μm,电阻率为0.04ω

·

cm的p型硅片1;步骤2:在p型硅片1表面生长氧化层5,进行正面、背面n 吸杂区2的光刻,光刻后进行正面、背面n 吸杂区2磷预扩散和再扩散分布,预扩散条件为:温度1180℃,时间100min,在通pocl3的扩散内进行预沉积;再扩散条件为:氮气气氛下,温度1250℃,时间30h,形成正正面、背面n 吸杂区2,结深10μm,窗口区域的局部扩散,磷掺杂在p型硅片衬底之间的横向、纵向扩散,形成下凹的pn结结构;步骤3:去除氧化层5后,在p型硅片1进行n 击穿区3正面、背面磷预扩散,在通

pocl3的扩散内进行预沉积,进行再扩散分布,温度1100℃、时间100min,再扩散条件为:氮气气氛下、温度1250℃、时间15h,形成正面、背面n 击穿区,结深5μm,击穿区为整面磷掺杂,为纵向扩散;步骤4:进行沟槽光刻,然后台腐,在p型硅片1和正面、背面n 吸杂区2交接处形成环状钝化沟槽;步骤5:金属淀积、光刻、刻蚀,氧化层间隙形成t1/t2电极6;步骤6:合金,合金的条件为炉温530℃、时间30 min、真空度10-3

pa。

31.实施例3一种低压台面tvs半导体芯片,包括p型硅片1,p型硅片1的正面和背面设有上下对称的环状玻璃钝化沟槽,沟槽内设有玻璃钝化层4,p型硅片1的表面生长有氧化层5,氧化层5间隙刻蚀有电极,p型硅片1的正面和背面设有n 击穿区3,正面和背面设有n 吸杂区2,n 吸杂区2和n 击穿区3与p型硅片1之间pn结形成了下凹上凸的结构。

32.n 吸杂区2位于玻璃钝化层4和氧化层5之间下方的位置为朝向两侧的向下和向上的凹陷,电极6中部下方的位置为为朝向电极6的上凸和下凸的结构。

33.p型硅片为磷化铟,p型硅片1的厚度为300μm、电阻率为0.05ω

·

cm。

34.n 吸杂区2的结深在40μm, n 击穿区2的结深在20μm。

35.一种制造低压台面tvs半导体芯片的方法,包括下列步骤:步骤1:选择硅片片厚300μm,电阻率为0.05ω

·

cm的p型硅片1;步骤2:在p型硅片1表面生长氧化层5,进行正面、背面n 吸杂区2的光刻,光刻后进行正面、背面n 吸杂区2磷预扩散和再扩散分布,预扩散条件为:温度1180℃,时间100min,在通pocl3的扩散内进行预沉积;再扩散条件为:氮气气氛下,温度1250℃,时间15h,形成正正面、背面n 吸杂区2,结深40μm,窗口区域的局部扩散,磷掺杂在p型硅片衬底之间的横向、纵向扩散,形成下凹的pn结结构;步骤3:去除氧化层5后,在p型硅片1进行n 击穿区3正面、背面磷预扩散,在通pocl3的扩散内进行预沉积,进行再扩散分布,温度1100℃、时间100min,再扩散条件为:氮气气氛下、温度1250℃、时间13h,形成正面、背面n 击穿区,结深20μm,击穿区为整面磷掺杂,为纵向扩散;步骤4:进行沟槽光刻,然后台腐,在p型硅片1和正面、背面n 吸杂区2交接处形成环状钝化沟槽;步骤5:金属淀积、光刻、刻蚀,氧化层间隙形成t1/t2电极6;步骤6:合金,合金的条件为炉温500℃、时间20 min、真空度10-3

pa。

36.实施例4一种低压台面tvs半导体芯片,包括p型硅片1,p型硅片1的正面和背面设有上下对称的环状玻璃钝化沟槽,沟槽内设有玻璃钝化层4,p型硅片1的表面生长有氧化层5,氧化层5间隙刻蚀有电极,p型硅片1的正面和背面设有n 击穿区3,正面和背面设有n 吸杂区2,n 吸杂区2和n 击穿区3与p型硅片1之间pn结形成了下凹上凸的结构。

37.n 吸杂区2位于玻璃钝化层4和氧化层5之间下方的位置为朝向两侧的向下和向上的凹陷,电极6中部下方的位置为为朝向电极6的上凸和下凸的结构。

38.p型硅片为磷化铟,p型硅片1的厚度为200μm、电阻率为0.004ω

·

cm。

39.n 吸杂区2的结深在30μm, n 击穿区2的结深在15μm。

40.一种制造低压台面tvs半导体芯片的方法,包括下列步骤:步骤1:选择硅片片厚200μm,电阻率为0.004ω

·

cm的p型硅片1;步骤2:在p型硅片1表面生长氧化层5,进行正面、背面n 吸杂区2的光刻,光刻后进行正面、背面n 吸杂区2磷预扩散和再扩散分布,预扩散条件为:温度1100℃,时间60min,在通pocl3的扩散内进行预沉积;再扩散条件为:氮气气氛下,温度1200℃,时间10h,形成正正面、背面n 吸杂区2,结深30μm,窗口区域的局部扩散,磷掺杂在p型硅片衬底之间的横向、纵向扩散,形成下凹的pn结结构;步骤3:去除氧化层5后,在p型硅片1进行n 击穿区3正面、背面磷预扩散,在通pocl3的扩散内进行预沉积,进行再扩散分布,温度1000℃、时间60min,再扩散条件为:氮气气氛下、温度1200℃、时间10h,形成正面、背面n 击穿区,结深15μm,击穿区为整面磷掺杂,为纵向扩散;步骤4:进行沟槽光刻,然后台腐,在p型硅片1和正面、背面n 吸杂区2交接处形成环状钝化沟槽;步骤5:金属淀积、光刻、刻蚀,氧化层间隙形成t1/t2电极6;步骤6:合金,合金的条件为炉温500℃、时间20 min、真空度10-3

pa。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。