避免反激式转换器中的虚假nsn检测

1.优先权

2.本技术是2019年12月5日提交的美国专利申请no.16/704,975的国际申请,其要求2019年9月19日提交的美国临时申请no.62/902,537的优先权和权益,这两个申请的全部内容通过引用的方式并入本文。

技术领域

3.本公开涉及反激式ac-dc转换器。

背景技术:

4.ac-dc转换器将来自交流(ac)源的功率转换成指定电压电平的直流(dc)。通常,ac-dc转换器将功率从耦合到变压器的初级侧的ac输入传输到耦合到变压器的次级侧的dc输出。一些ac-dc转换器在非连续传导模式(dcm)下操作。在dcm模式中,转换器在初级(例如,ac)侧的导通周期期间将功率存储在其变压器中,同时次级(例如,dc)侧关闭;转换器在次级侧的接下来的导通周期期间传输所存储的功率,同时初级侧关闭。

5.在dcm模式中操作的转换器的主要问题是虚假负感测(nsn)检测。当次级侧控制器错误地将转换器的初级侧上的谐振振铃解释为接通次级ps-fet以将功率传输到次级侧的信号时,就会发生虚假nsn检测。然而,如果在初级侧仍然导通的情况下打开了次级侧,则交叉传导可能导致非常高的次级侧电流,该非常高的次级侧电流导致次级侧晶体管和二极管的击穿。常规上,消隐时间(例如,在某个时间间隔内消隐nsn检测)可以用作该问题的解决方案。然而,消隐时间可能无法完全解决问题,并且由于在这种消隐时间期间功率将通过整流器二极管而不是次级ps-fet传输而导致次级侧的不必要且不及时的打开,由此造成功率损失,从而降低了转换器的效率。

附图说明

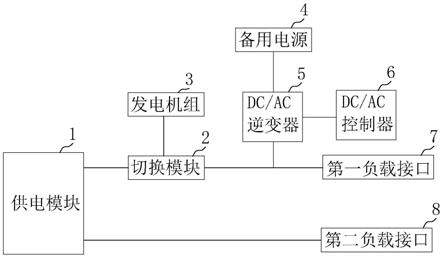

6.图1示出了根据示例性实施例的初级控制的ac-dc转换器系统。

7.图2示出了用于初级控制的ac-dc转换器系统的信号流图。

8.图3示出了根据一些实施例的ac-dc转换器系统中的变压器的电容模型的示意图。

9.图4示出了根据一些实施例的ac-dc转换器系统中的次级侧的波形图。

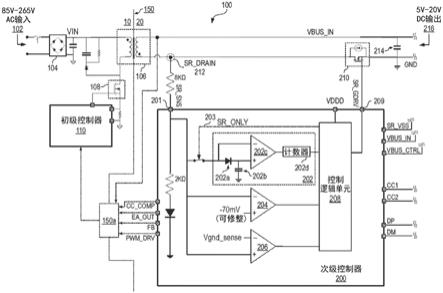

10.图5示出了根据一些实施例的示例性初级控制的ac-dc转换器系统。

11.图6示出了根据一些实施例的用于避免初级控制的ac-dc转换器系统中的虚假nsn检测的示例性方法。

12.图7示出了根据一些实施例的用于检测ac-dc转换器系统中的高频、电感泄漏振铃的模拟结果图。

13.图8示出了根据一些实施例的用于ac-dc转换器系统的示例性集成电路(ic)控制器。

具体实施方式

14.以下描述阐述了许多具体细节,例如具体系统、部件、方法等的示例,以便提供对本文描述的用于避免反激式转换器中的虚假负感测(nsn)检测的技术的各种实施例的良好理解。然而,对于本领域技术人员来说显而易见的是,可以在没有这些具体细节的情况下实践至少一些实施例。在其他实例中,没有详细描述众所周知的部件、元件或方法或者以简单的框图格式呈现众所周知的部件、元件或方法,以避免不必要地模糊本文描述的主题。因此,下文阐述的具体细节仅仅是示例性的。特定的实施方式可能与这些示例性细节不同,并且仍被认为在本发明的精神和范围内。

15.在描述中对“实施例”、“一个实施例”、“示例性实施例”、“一些实施例”和“各种实施例”的提及是指结合实施例描述的特定特征、结构、步骤、操作或特性被包括在本发明的至少一个实施例中。此外,在说明书的各个地方出现的短语“实施例”、“一个实施例”、“示例性实施例”、“一些实施例”和“各种实施例”不一定都指代相同的(一个或多个)实施例。

16.该描述包括对形成具体实施方式的一部分的附图的参考。附图示出了根据示例性实施例的图示。这些实施例在本文中也可以被称为“示例”,其被足够详细地描述以使本领域技术人员能够实践本文描述的所要求保护的主题的实施例。可以组合实施例,可以利用其他实施例,或者可以进行结构、逻辑和电气上的改变,而不脱离所要求保护的主题的范围和精神。应当理解,本文描述的实施例并非旨在限制主题的范围,而是使本领域技术人员能够实践、做出和/或使用该主题。

17.图1示出了根据一些实施例的初级控制的ac-dc转换器100。ac-dc转换器100是在ac输入102和dc输出216之间提供电流隔离的反激式转换器。ac-dc转换器100包括设置在变压器106的ac输入侧上的初级侧10和设置在变压器106的dc输出侧上的次级侧20。具有隔离元件150a的隔离屏障150将初级侧10与次级侧20电隔离。在初级控制模式下,变压器的初级侧控制转换器的操作,因为从初级侧到次级侧的唯一通信通道是变压器提供到次级侧的电压电平。初级侧和次级侧的导通周期通常相隔一个时间间隔,在该时间间隔期间,存储在变压器中的功率通过整流器二极管传输,这会导致更高的功率损失,从而降低效率。

18.参考图1,ac-dc转换器100的初级侧10包括ac输入102、桥式整流器104、变压器106、初级功率开关(ps)-场效应晶体管(fet)108和初级控制器110。次级侧20包括次级控制器200、同步整流器(sr)电路210、漏极节点(sr_drain)212、输出电容器214和通用串行总线(usb)type-c连接器220。在初级侧10上,ac输入102被配置为接收来自电源(例如壁式插座(图1中未示出))的交流电流。桥式整流器104耦合在ac输入102和变压器106之间以对在ac输入102处接收的输入电压进行整流。变压器106被耦合以将来自桥式整流器104的ac电流通过其初级线圈和初级ps-fet108传导到地。初级控制器110耦合到ps-fet108的栅极以控制变压器106的导通周期和关闭周期。在次级侧20上,sr电路210耦合在变压器106的次级线圈和输出电容器214之间。sr电路210包括与二极管并联耦合的次级ps-fet,使得当次级ps-fet被接通时,感应电流流向漏极节点212。sr电路210被配置为对输出电容器214充电(在连续的导通和关闭周期中),以使输出电容器可以向dc输出216提供稳定电压。dc输出216耦合到功率连接器220。次级控制器200耦合到sr电路210的漏极节点212以感测漏极节点上的电压(及其变化)。次级控制器200也耦合到sr电路210中的次级ps-fet的栅极,以基于在漏极节点212上感测到的电压峰值、负电压和零电压交叉点来接通和关断sr电路(例如,在相应

的导通和关闭周期中)。

19.确定ac-dc转换器(例如,转换器100)的效率的关键要素是控制sr电路(例如,sr电路210)的操作周期的次级ps-fet开关(例如,ps-fet 210)的操作。在初级控制模式中,次级侧控制器(例如,控制器200)完全取决于sr电路的漏极节点(例如,sr_drain 212)的电压电平,因为没有从初级侧(10)到次级侧(20)的其他通信通道。在典型的操作场景中,sr_drain节点上的电压降到-0.2v以下,以指示次级控制器接通次级ps-fet。当sr_drain节点上的电压回到0v时,次级侧控制器检测到该零电压交叉点并关断次级ps-fet。

20.虚假nsn检测对于在初级控制的ac-dc转换器的环境中操作的次级侧控制器来说是主要问题。当转换器在非连续传导模式(dcm)下操作时,会在谐振振铃期间发生这种虚假nsn检测。在这种谐振振铃期间,sr电路的sr_drain节点上的电压可能降到-200mv以下。这将被次级侧控制器错误地解释为有效nsn检测事件,从而导致次级侧控制器接通sr电路的次级ps-fet。这反过来又会由于sr电路的不必要的接通而导致效率损失,从而将输出负载电容器放电到地。此外,如果初级侧控制器同时接通初级ps-fet,则会导致交叉传导,其中初级侧和次级侧两者同时接通。然而,这种交叉传导可能导致非常高的次级侧电流,该非常高的次级侧电流可能导致sr电路的二极管和晶体管部件的击穿。常规上,消隐时间可以用作这个问题的解决方案(例如,在某个时间间隔内消隐nsn检测)。然而,使用这种消隐时间会降低转换器的效率,因为在该时间期间,次级ps-fet不会接通,而sr电路的二极管将承载峰值电流,从而导致功率损失。

21.图2是示出虚假nsn检测问题的示例性信号图(例如,对于在dcm模式下操作的初级控制的ac-dc转换器)。当初级侧导通时(初级导通周期),初级ps-fet导通,次级ps-fet关闭,并且初级电流105流过变压器的初级线圈。当次级侧导通时(次级导通周期),初级ps-fet关闭,次级ps-fet导通,并且次级电流211流向sr电路的漏极节点。如图2所示,初级导通周期和次级导通周期以常规方式分隔开消隐时间间隔107。

22.当初级侧接通时,在sr_drain信号213上实现泄漏振铃事件109a。当sr_drain信号213上的电压下降到大约-0.7v时,可以基于在消隐时间间隔107结束时的输出nsn信号(nsn_out)205而检测到真实nsn事件205a。在消隐时间间隔107之后,初级侧关断并且次级侧接通。真实nsn事件205a的检测用于将控制信号sr_drv 209驱动为高,这接通了次级ps-fet。结果,sr-drain信号上的电压上升并最终跨过0v。当这种情况发生时,可以基于控制信号zcd_out 207检测到过零检测(zcd)事件207a,并且控制信号sr_drv 209被驱动为低以关断次级ps-fet。然而,在zcd事件207a之后,sr_drain信号209上的电压继续上升并在其上实现谐振振铃213a。这导致基于nsn_out信号205在sr_drain信号213上检测到虚假nsn检测事件205b。该(虚假)nsn事件205b的检测用于将控制信号sr_drv 209驱动为高,这不必要地(即,错误地)接通了次级ps-fet。

23.为了防止次级ps-fet的这种错误接通,本文描述的技术提供用于检测初级侧的现实的、真实的接通事件并避免虚假nsn检测。例如,本文描述的技术提供用于检测次级侧sr漏极节点上的高频振铃,这仅在初级侧ps-fet真实接通时才发生。如下文关于图3和图4所描述的,这种振铃的频率远高于由虚假nsn事件引起的谐振振铃的频率。因此,根据本文描述的技术配置的ac-dc转换器可以区分现实和虚假nsn检测事件。

24.图3示出了ac-dc转换器中的变压器的电容模型的示意图。在图3中,变压器301被

示为耦合到寄生元件303,寄生元件303在次级侧上的sr电路的sr_drain节点上引起寄生振铃。例如,变压器301的绕组间电容以及连接到ac-dc转换器的不同元件的电容可以被共同建模为寄生电容clump。由于不完美耦合而从初级侧到次级侧的泄漏能量被示为泄漏电感lleak。每当初级ps-fet开关被接通时,泄漏电感lleak以及寄生电容clump在sr_drain节点上创建振荡行为(例如,电感振铃)。电感振铃的频率fleak被表示为以下等式(1):

[0025][0026]

同样,每当变压器中的能量变为零时,次级侧中的sr_drain节点上就会出现谐振振铃。该谐振振铃的频率fdcm被表示为以下等式(2):

[0027][0028]

其中lp是变压器初级线圈的电感。

[0029]

通常,泄漏电感lleak与初级电感lp相比非常小(例如,小于2%)。因此,基于等式(1)和(2),可以观察到与谐振振铃的频率fdcm相比,电感振铃的泄漏频率fleak非常高。本文所述的技术使用泄漏频率fleak和谐振振铃频率fdcm之间的巨大差异来检测现实的初级侧接通事件并区分现实和虚假nsn检测事件。这在图4中示出,图4示出ac-dc转换器的次级侧上的sr电路的漏极节点(sr_drain)的电压信号的波形图。如图4所示,电感泄漏振铃401的频率远高于谐振振铃403的频率。

[0030]

根据本文描述的技术,在ac-dc转换器的次级侧上在每一个周期中测量sr电路的sr_drain节点上的振铃的频率。当测量的频率比预期的谐振频率高得多(例如,至少高出阈值量)时,生成信号以启用sr_drain节点上的nsn检测。这有效地将现实nsn事件与虚假nsn事件区分开,从而消除了次级ps-fet的虚假接通。

[0031]

图5示出了根据本文描述的技术配置的用于避免虚假nsn检测事件的转换器100(例如,诸如图1的ac-dc转换器100)。在图5中,ac-dc转换器100是在ac输入102和dc输出216之间提供电流隔离的反激式转换器。转换器100是在dcm模式下操作的初级控制的ac-dc转换器。转换器100的各种部件可以设置在包封在合适外壳中的一个或多个基板(例如,作为印刷电路板、pcb)上并且彼此耦合。例如,在一些实施例中,ac-dc转换器100可以是设置在电子设备内的电源转换器。在其他实施例中,ac-dc转换器可以是用于便携式电子设备的独立电源。

[0032]

参考图5,转换器100包括初级侧10、隔离屏障150和次级侧20。初级侧10控制转换器100的操作,因为从初级侧10到次级侧20的唯一通信通道是变压器106提供到次级侧的电压电平。

[0033]

在其他部件中,转换器100的初级侧10包括ac输入102、桥式整流器104、变压器106、初级ps-fet 108和初级控制器110。ac输入102被配置用于耦合到电源(例如,诸如壁式插座),该电源提供在85v至265v范围内的ac电压。桥式整流器104被耦合以接收来自ac输入102的输入电压并向变压器106的初级线圈提供整流输出电压(vin)。变压器106的初级线圈被耦合以将来自桥式整流器104的电流通过初级ps-fet 108而传导到地。ps-fet 108是功率开关,其可以被实施为一个或多个金属氧化物半导体场效应晶体管(mosfet)或其他合适的高电压/功率半导体器件。初级控制器110耦合到ps-fet 108的栅极以控制变压器106的

导通和关闭周期。在一些实施例中,初级控制器110可以被实施为制造在半导体管芯上的单芯片集成电路(ic)控制器。在其他实施例中,主控制器110可以是被制造为片上系统(soc)的单芯片ic。在又一些实施例中,主控制器110可以是包封在单个半导体封装中的多芯片模块。

[0034]

包括隔离元件150a的隔离屏障150设置在初级侧10和次级侧20之间以将初级侧与次级侧电隔离。隔离元件150a是耦合到初级控制器110的一个或多个输入引脚、耦合到次级侧20上的vbus_in线、并且耦合到次级控制器200的一个或多个输出引脚的电子电路。隔离元件150a被配置为提供到初级控制器110的(多个)非电流反馈信号,以便控制由变压器106在vbus线上输出的电压电平。

[0035]

例如,在一些实施例中,隔离元件150a可以是光隔离器电路。光隔离器电路包括发光元件(例如发光二极管(led))以及光敏元件(例如光电晶体管)。led具有通过分压器耦合到次级侧20上的vbus_in线的阳极和直接耦合到次级控制器200的误差放大器输出(ea_out)引脚的阴极。led的阴极还通过一个或多个电阻器-电容器网络而耦合到反馈(fb)引脚并耦合到次级控制器200的恒流补偿(cc_comp)引脚。光隔离器电路的光电晶体管耦合到初级控制器110的输入引脚并且被配置为(例如,在合适的外壳内)接收从led发射的光信号。在操作中,次级控制器200使用来自其ea_out引脚的输出信号来驱动led以提供关于vbus_in线上的电压的光反馈信号。通过光隔离器元件150a中的光电晶体管,将光反馈信号提供给初级控制器110。初级控制器110使用接收到的反馈信号来控制初级侧10的导通周期的长度,从而控制由变压器106的次级线圈输出到次级侧20上的vbus_in线的电压的电平。

[0036]

在另一个示例中,在一些实施例中,隔离元件150a可以是脉冲变压器电路。脉冲变压器电路包括耦合在次级控制器200的脉冲宽度调制驱动(pwm_drv)引脚和初级控制器110的输入引脚之间的脉冲变压器。次级控制器200的pwm_drv引脚上的信号输出反映了次级侧20上的vbus_in线上的电压。在操作中,pwm_drv引脚上的信号输出被提供给脉冲变压器的初级线圈,该初级线圈感应出相应的信号(至脉冲变压器的次级线圈),该信号被作为反馈信号提供给初级控制器110。初级控制器110使用接收到的反馈信号的脉冲宽度来操作初级ps-fet 108并控制初级侧10的导通周期的长度,从而控制通过变压器106的次级线圈输出到次级侧20上的vbus_in线的电压的电平。

[0037]

在其他部件中,转换器100的次级侧20包括次级控制器200、同步整流器(sr)电路210、漏极节点(sr_drain)212和输出电容器214。sr电路210耦合在变压器106的次级线圈和输出电容器214之间。sr电路210包括与二极管并联耦合的次级ps-fet,使得当次级ps-fet接通时,感应电流流向漏极节点212。sr电路210中的次级ps-fet是功率开关,其可以被实施为一个或多个mosfet或其他合适的高电压/功率半导体器件。sr电路210的漏极节点212耦合到次级控制器200的输入引脚(例如,端子)201,并且sr电路中的次级ps-fet的栅极耦合到次级控制器的输出引脚209。

[0038]

次级控制器200被配置为感测漏极节点212处的电压(及其变化)。次级控制器200还被配置为通过在其输出引脚209上提供控制信号(sr_gdrv)来控制sr电路210的次级ps-fet的栅极。在一些实施例中,次级控制器200可以被实施为在半导体管芯上制造的单芯片ic控制器。在其他实施例中,次级控制器200可以是被制造为片上系统(soc)的单芯片ic。在又一些实施例中,次级控制器200可以是包封在单个半导体封装中的多芯片模块。

[0039]

在次级控制器200的控制下,sr电路210操作用于在连续的导通和关闭周期中对输出电容器214充电。输出电容器214被配置为用作向dc输出216提供dc电压的滤波器。例如,在初级侧10的导通周期和次级侧20的关闭周期期间(例如,当ps-fet 108闭合并且sr电路210中的次级ps-fet开路时),在变压器106中建立磁场,同时初级侧10上的电流线性增加。在初级侧10的关闭周期和次级侧20的导通周期期间(例如,当ps-fet 108开路并且sr电路210中的次级ps-fet闭合时),在变压器106中建立的磁场开始崩塌,并且随着功率传输到输出电容器214,在变压器的次级线圈中感应出电流。在次级侧导通周期期间,次级侧20中的电流稳定但逐渐减小,直到达到流过漏极节点212的电流基本上为零的点。以这种方式,输出电容器214在连续周期中被充电以向dc输出216提供稳定的dc电压。

[0040]

dc输出216被耦合以向电子设备或其他负载供应dc电压。例如,在一些实施例中,在dc输出216上提供的标称dc电压可以在3.3v(或5v)到20v的范围内。此外,在一些实施例中,dc输出216可以作为电子设备的内部电源被耦合。在其他实施例中,dc输出216可以耦合到功率连接器(图5中未示出)以用于向便携式电子设备提供功率。在一个这样的实施例中(例如,如图1所示),功率连接器可以是根据usb type-c规范配置的usb type-c连接器(220)。usb type-c规范定义了type-c插座、type-c插头和type-c电缆,其可以通过在usb-pd规范的各种修订/版本中定义的协议来支持usb通信以及功率输送(pd)。根据usb type-c规范,type-c连接器端口(例如,type-c插座或type-c插头)提供vbus电源线、dp(d )和dm(d-)数据线、以及gnd接地回流线等。此外,type-c连接器端口还提供两条配置通道线路(cc1和cc2),以用于发现、配置和管理通过type-c电缆的连接。如图1的实施例所示,usb type-c连接器220提供vbus线(vbus_in)、gnd线、cc1和cc2线、以及dp和dm数据线。vbus_in线耦合到次级控制器200的相应输入引脚以提供功率信号(vbus_in),而gnd线耦合到次级控制器的相应引脚以提供来自sr电路210的源极节点的控制信号(sr_vss)。vbus_in线包括功率开关,其被实施为由从次级控制器200的输出引脚提供的控制信号(vbus_ctrl)控制的开/关半导体器件。usb type-c连接器220的cc1、cc2、dp和dm线耦合到次级控制器200的相应引脚。

[0041]

返回参考图5,ac-dc转换器100中的次级控制器200根据本文描述的技术被配置用于避免虚假nsn检测。次级控制器200包括控制逻辑单元208,其被耦合以通过功率引脚(vddd)从外部源接收功率。如本文所用,“逻辑单元”是指具有一个或多个电路的硬件块,所述电路包括被配置为处理模拟和/或数字信号并响应于(多个)控制信号而执行一个或多个操作的各种电子部件。这种电子部件的示例包括但不限于晶体管、二极管、电阻器、电容器、电感器、逻辑门及其各种电路。控制逻辑单元208被耦合以通过引脚209向sr电路210提供控制信号(sr_gdrv)。控制信号sr_gdrv被施加到sr电路210中的ps-fet的栅极以接通和关断sr电路。控制逻辑单元208还可以包括用于接收高频时钟信号的电路,该高频时钟信号用作参考以确定来自sr_drain节点212的信号的频率何时高于预定频率阈值。

[0042]

次级控制器200还包括频率检测器202、负电压检测器204和零电压检测器206,它们通过引脚201耦合到sr_drain节点212。具有8k外部电阻器和2k内部电阻器的分压器在输入引脚201处被耦合以生成分压输入信号(sr_sns),其被提供给频率检测器202、负电压检测器204和零电压检测器206。频率检测器202、负电压检测器204和零电压检测器206的输出端子耦合到控制逻辑单元208。

[0043]

频率检测器202(也称为“峰值检测器”)是包括二极管202a、参考电容器202b、高速比较器202c和数字计数器202d的电路。频率检测器202还可以包括被耦合以从控制逻辑单元208接收启用信号的控制端子(图5中未示出)。参考电容器202b被耦合在二极管202a和比较器202c的非反相端子之间。比较器202c的反相端子被耦合以接收来自sr_drain节点212的sr_sns输入信号。二极管202a也被耦合以接收sr_sns输入信号。计数器202d可以是寄存器或其他适合于存储数字计数的元件。频率检测器202被配置为检测sr_drain节点212上的任何振荡信号的峰值点,并且两个连续峰值之间的差可以用于确定振荡的频率。例如,比较器202c向计数器202d输出高信号,并且控制逻辑单元208使用存储在计数器202d中的计数来确定来自sr_drain节点212的sr_sns输入信号的频率。

[0044]

在一些实施例中,次级控制器200可以包括既可以在初级控制模式下操作又可以在次级控制模式下操作的硬件部件。在次级控制模式下,ac-dc转换器100还包括向初级控制器110提供非电流反馈路径的电子部件(例如,具有发光二极管和光敏光电晶体管的光隔离器电路,或具有脉冲宽度调制(pwm)斜坡发生器和脉冲变压器的pwm电路),使得次级控制器200可以将控制信号传递到初级控制器并控制初级控制器的操作。在这样的实施例中,为了实现次级控制器200的初级控制或次级控制操作模式,控制逻辑单元208被配置为向耦合到二极管202a的开关提供启用信号(sr_only)203。在初级控制模式下,控制逻辑单元208持续将sr_only启用信号203施加到开关,因此sr_sns输入信号被持续提供给频率检测器202。

[0045]

负感测检测器204是包括比较器204的电路。比较器204的反相端子被耦合以接收来自sr_drain节点212的sr_sns输入信号。比较器204的非反相端子耦合到可微调电压参考源(例如,在-70mv或以下)。负感测检测器204还可以包括被耦合以接收来自控制逻辑单元208的启用信号的控制端子(图5中未示出)。负感测检测器204的输出被耦合以向控制逻辑单元208提供输出信号。例如,负感测检测器204被配置为在sr_sns输入信号的负电压降到某个电压阈值(例如,-200mv)以下时提供高输出信号。

[0046]

零电压检测器206是包括比较器206的电路。比较器206的非反相端子被耦合以接收来自sr_drain节点212的sr_sns输入信号。比较器206的反相端子被耦合到零电压参考源,vgnd_sense(例如,在0v)。零电压检测器206还可以包括被耦合以接收来自控制逻辑单元208的启用信号的控制端子(图5中未示出)。零电压检测器206的输出被耦合以向控制逻辑单元208提供输出信号。例如,零电压检测器206被配置为在sr_sns输入信号的电压从先前的负电压值达到0v时提供高输出信号。

[0047]

在根据本文描述的技术的操作中,频率检测器202和控制逻辑单元208在转换器100的次级侧20上的每个周期中测量sr电路210的sr_drain节点212上的振铃的频率。当测量的频率高于频率阈值(例如,预期谐振频率的十倍,或10*fdcm),控制逻辑单元208启用负感测检测器204。例如,控制逻辑单元208可以将启用信号施加到负感测检测器204或(例如,如果负感测检测器被配置用于连续操作)可以简单地接通负感测检测器的输出。以这种方式,负感测检测器204仅在sr_drain节点212上检测到高频(例如,电感泄漏)振铃之后才被接通,从而指示主控制器110的真实接通事件。当启用时,负感测检测器204操作用于感测来自sr_drain节点212的sr_sns输入信号的负电压。当sr_sns输入信号的负电压降到某个电压阈值(例如,-200mv)以下时,负感测检测器204向控制逻辑单元208输出高信号。作为响应,控制逻辑单元208接通sr电路210的次级ps-fet以将功率传输到转换器100的次级侧20。

此后(例如,在接通sr电路之后),控制逻辑单元208禁用负感测检测器204(和/或来自其的输出信号)。当sr_drain节点212上的电压从其先前的负电压电平回到0v时,零电压检测器206检测到过零事件并向控制逻辑单元208输出高信号。作为响应,控制逻辑单元208通过将适当的控制信号sr_gdrv施加到输出引脚209来关断sr电路210中的ps-fet开关。然而,由于负感测检测器204在过零事件之前和期间被禁用,因此避免了负感测检测器检测到可能的(虚假)nsn事件。

[0048]

图6示出了根据示例性实施例的用于避免初级控制的ac-dc转换器中的虚假nsn检测的方法600。图6中的方法600的操作被描述为由频率检测器、nsn检测器和控制逻辑单元(例如,分别例如是频率检测器202、负感测检测器204和图5的控制逻辑单元208)执行。然而,应当注意,各种实施方式和实施例可以使用各种并且可能不同的硬件部件来执行方法600的操作。因此,下文中对方法600的描述被认为是说明性的而不是限制性的。

[0049]

根据本文描述的技术,方法600基于来自在dcm模式下操作的初级控制的ac-dc转换器的次级侧上的sr电路的漏极节点的输入信号来执行。

[0050]

在操作602中,ac-dc转换器的次级控制器中的控制逻辑单元将频率计数器重置为0。在操作604中,控制逻辑单元启用频率检测器并将频率检测器的输出路由到频率计数器。在一些实施例中,次级控制器可以包括可以在初级控制模式和次级控制模式下操作的硬件部件。在这样的实施例中,初级控制模式在操作602和604之前在次级控制器内被启用。例如,控制逻辑单元可以连续地向频率检测器施加启用信号以确保次级控制器接收来自sr电路的漏极节点的输入信号。

[0051]

在操作606中,控制逻辑单元禁用其nsn检测器。例如,控制逻辑单元可以将禁用信号施加到nsn检测器。如果nsn检测器被配置为连续操作,则控制逻辑单元可以关断其接收来自nsn检测器的输出信号的电路。

[0052]

在操作608中,频率检测器确定从sr电路的漏极节点接收的输入信号的频率,并且控制逻辑单元连续监测频率检测器的输出。例如,控制逻辑单元可以被配置为连续地接收来自频率检测器中的峰值检测比较器的输出信号。当峰值检测比较器的输出为低信号时,控制逻辑单元继续进行操作606以禁用nsn检测器。然而,当峰值检测比较器的输出是高信号时,在操作610中,控制逻辑单元对来自频率计数器的输出进行采样(例如,以1mhz采样频率)。

[0053]

在操作612中,控制逻辑单元将采样频率与频率阈值进行比较。根据本文所述的技术,频率阈值基于来自sr电路的漏极节点的输入信号的预期谐振频率。在一些实施例中,频率阈值可以等于预期谐振频率的十倍(例如,10*fdcm),但应注意,取决于转换器的具体类型和其中的电路,各种实施例可以使用不同的频率阈值。

[0054]

如果在操作612中控制逻辑单元确定采样频率不大于频率阈值,则控制逻辑单元在操作614中将频率计数器重置为0,并且然后继续操作606以禁用nsn检测器。

[0055]

如果在操作612中控制逻辑单元确定采样频率大于频率阈值,则控制逻辑单元确定检测到ac-dc转换器的初级侧的真实接通事件。然后控制逻辑单元继续进行操作616以启用nsn检测器。例如,响应于确定采样频率大于频率阈值,控制逻辑单元可以将启用信号施加到nsn检测器以将其接通。如果nsn检测器被配置为连续操作,则在操作616中,响应于确定采样频率大于频率阈值,控制逻辑单元可以接通其接收来自nsn检测器的输出信号的电

路。

[0056]

在操作618中,控制逻辑单元监测来自nsn检测器的输出信号。如果来自nsn检测器的输出信号为低,则控制逻辑单元返回到操作616以确保nsn检测器仍然被启用。

[0057]

如果在操作618中控制逻辑单元检测到来自nsn检测器的输出信号为高,则控制逻辑单元确定来自sr电路的漏极节点的输入信号的电压已经下降到某个电压阈值以下(例如,-200mv)。这向控制逻辑单元指示需要接通sr电路。因此,在操作620中,nsn检测器输出信号被提供给控制逻辑单元的内部硬件电路(例如,合成rtl),其将启用信号施加到sr电路的ps-fet的栅极以将其接通。此外,响应于检测到来自nsn检测器的输出信号处于高电平,控制逻辑单元继续进行操作614以将频率计数器重置为0,并且然后进行操作606以禁用nsn检测器。

[0058]

通过这种方式,nsn检测器仅在检测到ac-dc转换器的初级侧的真实接通事件后才被启用,而在其余时间保持被禁用。以这种方式操作nsn检测器确保了避免检测到虚假nsn事件。

[0059]

图7示出了用于检测高频振铃的模拟结果图。该图的顶部部分示出了当ac-dc转换器的初级侧接通时,sr_drain输入信号上的电感泄漏振铃。该图的底部部分示出了根据本文描述的技术的来自频率检测器的峰值检测比较器的输出信号。如该图的底部部分所示,来自峰值检测器的输出信号可以用于检测sr_drain信号上的以17.2mhz振荡的电感泄漏振铃。

[0060]

本文描述的技术提供用于检测ac-dc转换器的初级侧上的真实接通事件,从而提高效率并避免转换器的次级侧上的sr电路中的ps-fet的虚假接通。这是通过检测sr电路的漏极节点上的每当初级侧上的ps-fet被接通时就会发生的高频电感泄漏振铃来实现的。这种电感泄漏振铃的频率远高于由虚假nsn事件引起的谐振振铃。此外,通过检测初级侧上的真实接通事件,本文描述的技术不需要提供用于关断nsn检测的消隐时间。此处描述的技术还提供了改进的操作可靠性,由于在虚假nsn事件期间次级ps-fet将不会接通,因此将不会存在任何交叉传导。此外,基于实际初级导通检测信号,转换器的次级侧可以启用前馈方案,以感测提供给转换器的初级侧上的变压器的vin电压。反过来,这种电压信息可以用于更改内部参数,以进一步优化转换器效率。

[0061]

图8示出了根据用于避免本文描述的虚假nsn检测的技术配置的示例性半导体器件。在图8所示的实施例中,装置800是制造在半导体管芯上的单芯片ic控制器。在另一示例中,ic控制器800可以是被制造为片上系统(soc)的单芯片ic。在其他实施例中,ic控制器800可以是包封在单个半导体封装中的多芯片模块。在各种操作语境中,ic控制器800可以用作图1和图5的ac-dc转换器系统100中的次级控制器200。

[0062]

参考图8,ic控制器800包括cpu子系统802、外围互连814、系统资源816、输入/输出(i/o)子系统818、usb-pd子系统820、以及被配置用于接收和发送信号的各种端子(例如,引脚)。

[0063]

cpu子系统802包括耦合到系统互连812的一个或多个cpu(中央处理单元)804、闪存806、sram(静态随机存取存储器)808和rom(只读存储器)810。cpu 804是可以在ic或soc设备中操作的合适的处理器。闪存806是被配置用于存储数据、程序和/或其他固件指令的非易失性存储器(例如,nand闪存、nor闪存等)。闪存806紧密耦合在cpu子系统802内以改进

访问时间。sram 808是易失性存储器,其被配置为用于存储由cpu 804访问的数据和固件指令。rom 810是只读存储器(或其他合适的存储介质),其被配置为用于存储启动例程、配置参数和其他固件参数和设置。系统互连812是系统总线(例如,单级或多级高级高性能总线,或ahb),其被配置为将cpu子系统802的各种部件彼此耦合的接口,以及cpu子系统的各种部件与外围互连814之间的数据和控制接口。

[0064]

外围互连814是外围总线(例如,单级或多级ahb),其提供在cpu子系统102与其外围设备和其他资源(例如系统资源816、i/o子系统818和usb-pd子系统820)之间的主要数据和控制接口。外围互连814可以包括各种控制器电路(例如,直接存储器访问,或dma控制器),其可以被编程为在外围块之间传输数据而不会给cpu子系统802增加负担。在各种实施例中,cpu子系统的每个部件和外围互连可能因cpu、系统总线和/或外围总线的每种选择或类型而不同。

[0065]

系统资源816包括各种电子电子电路,其支持ic控制器800在其各种状态和模式下的操作。例如,系统资源816可以包括具有每个控制器状态/模式所需的模拟和/或数字电路(例如,睡眠控制电路、唤醒中断控制器(wic)、上电复位(por)、电压和/或电流参考(ref)电路等)的功率子系统。在一些实施例中,功率子系统还可以包括如下电路,该电路允许ic控制器800从具有若干不同电压和/或电流电平的外部源汲取功率和/或向该外部源提供功率,并支持在几种功率状态817(例如,活动状态、睡眠状态和时钟关断的深度睡眠状态)中的控制器操作。此外,在一些实施例中,cpu子系统802可以针对具有广泛时钟门控的低功率操作进行优化,并且可以包括允许cpu在各种功率状态817下操作的各种内部控制器电路。例如,cpu可以包括唤醒中断控制器,其被配置为将cpu从睡眠状态唤醒,从而允许在ic芯片处于睡眠状态时关闭功率。系统资源816还可以包括具有用于时钟生成和时钟管理的模拟和/或数字电路(例如,时钟控制电路、看门狗定时器(wdt)电路、内部低速振荡器(ilo)电路以及内部主振荡器(imo)电路等)的时钟子系统。系统资源816还可以包括提供复位控制并支持外部复位(xres)的模拟和/或数字电路块。

[0066]

i/o子系统818包括几种不同类型的i/o块和子系统。例如,i/o子系统818包括gpio(通用输入输出)块818a、tcpwm(定时器/计数器/脉冲宽度调制)块818b和scb(串行通信块)818c。gpio 818a包括模拟和/或数字电路,其被配置为实施各种功能,例如上拉、下拉、输入阈值选择、输入和输出缓冲器启用/禁用、连接到各种i/o引脚的多路复用信号等。tcpwm 818b包括模拟和/或数字电路,其被配置为实施定时器、计数器、脉冲宽度调制器、解码器以及被配置为对输入/输出信号进行操作的各种其他模拟/混合信号元件。scb 818c包括模拟和/或数字电路,其被配置为实施各种串行通信接口,例如i2c、spi(串行外围接口)、uart(通用异步接收器/发射器)、can(控制器局域网)接口、cxpi(时钟扩展外围接口)等。

[0067]

usb-pd子系统820提供到诸如usb type-c端口的功率连接器的接口。如本文所用,“usb-pd子系统”是指一个或多个逻辑块和其他模拟/数字硬件电路,它们可以由固件控制并且被配置为并且可操作用于执行功能并满足在usb-pd规范的至少一个版本中规定的要求。usb-pd规范定义了标准协议,其被设计为通过经由usb type-c端口通过单个usb type-c电缆提供更灵活的功率输送以及数据通信,来实现启用usb的设备的最大功能。usb-pd规范还描述了用于管理通过usb type-c电缆的功率输送所必需的架构、协议、电源行为、参数和电缆布线(例如,对于总共高达100w的功率,在高达20v下的高达5a的电流)。usb-pd规范

还定义了用于可以在一对启用usb的设备之间协商的功率输送合同(pd合同)的要求。pd合同可以指定两个设备可以适应的功率水平和功率传输方向,并且可以被动态地重新协商(例如,无需拔出设备)。

[0068]

在其他电路中,usb-pd子系统820可以包括:一个或多个用于将各种模拟信号转换为数字信号的模数转换器(adc);误差放大器(error amp),其用于控制每个pd合同的施加到vbus线的电源电压;电流感测放大器(csa)和过电压保护(ovp)电路,其用于在具有可配置阈值和响应时间的vbus线上提供过电流和过电压保护;用于支持type-c通信通道(cc)线上的通信的通信通道phy(cc bb phy)逻辑单元;连接到dp和dm线的电荷检测器逻辑块(chrg det),其用于检测符合各种标准和专有电池充电规范的常规电池充电器;至少两个管芯上放电(vbus disch)电路,其可以将vbus线电压放电至可编程电压电平范围中的任何范围;一个或多个栅极驱动器(gate drv),其用于控制接通和关断通过vbus线的功率供应的功率开关;高电压调节器(hv reg),其用于将电源电压转换成为ic控制器800供电所需的精确电压(例如3-5v);以及短路保护块(scp),其用于在耦合于接地回流路径上的外部电阻器两端进行附加的短路检测。

[0069]

根据本文描述的用于避免虚假nsn检测的技术,usb-pd子系统820包括sr感测逻辑块(sr sense)和sr驱动器逻辑块(sr drv)。根据本文所述的技术,sr感测逻辑块包括:频率检测器,其用于确定来自ac-dc转换器的sr电路的漏极节点的输入信号的频率;负感测检测器,其用于在sr电路的漏极节点上的负电压降到某个电压阈值以下时提供高输出信号;以及zcd检测器,其用于在sr电路的漏极节点上的电压从先前的负电压值达到0v时提供高输出信号。sr驱动器逻辑块包括控制逻辑单元,该控制逻辑单元被配置为根据本文描述的技术基于来自频率检测器、负感测检测器和zcd检测器的信号来驱动sr电路的ps-fet的栅极。

[0070]

本文描述的用于避免反激式ac-dc转换器中的虚假nsn检测的技术的各种实施例可以包括各种操作。这些操作可以由硬件部件、数字硬件和/或固件、和/或其组合来执行和/或控制。如本文所用,术语“耦合到”可以表示直接连接或通过一个或多个中间部件的间接连接。通过各种管芯上总线提供的任何信号可以与其他信号进行时间复用,并且通过一个或多个公共的管芯上总线来提供通过各种管芯上总线提供的任何信号。此外,电路部件或块之间的互连可以被示为总线或单个信号线。每条总线可以替代地是一条或多条单个信号线,并且单个信号线中的每个可以替代地是总线。

[0071]

某些实施例可以被实施为计算机程序产品,该计算机程序产品可以包括存储在非暂时性计算机可读介质(例如易失性存储器和/或非易失性存储器)上的指令。这些指令可以用于编程和/或配置包括处理器(例如,cpu)或其等同物(例如,处理核心、处理引擎、微控制器等)的一个或多个设备,以使得在由处理器或其等同物执行时,所述指令使(多个)所述设备执行本文所述的用于usb-c电源架构的所描述的操作。计算机可读介质还可以包括用于以机器(例如,诸如设备或计算机)可读的形式(例如,软件、处理应用等)存储或传输信息的一种或多种机制。非暂时性计算机可读存储介质可以包括但不限于电磁存储介质(例如软盘、硬盘等)、光存储介质(如cd-rom)、磁光存储介质、只读存储器(rom)、随机存取存储器(ram)、可擦除可编程存储器(例如eprom和eeprom)、闪存或另一种现在已知或稍后开发的适合于存储信息的非暂时性类型的介质。

[0072]

尽管本文的电路和块的操作以特定顺序示出并描述,但是在一些实施例中,每个

电路/块的操作的顺序可以改变,从而可以以相反的顺序执行某些操作或使得某些操作可以至少部分地与其他操作同时和/或并行地执行。在其他实施例中,可以以间歇和/或交替的方式执行不同操作的指令或子操作。

[0073]

在前面的说明书中,已经参考本发明的具体示例性实施例描述了本发明。然而,显然可以对其进行各种修改和改变而不脱离如所附权利要求中阐述的本发明的更广泛的精神和范围。因此,说明书和附图应被视为说明性意义而非限制性意义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。