1.本技术涉及通信技术领域,特别涉及一种译码方法及装置。

背景技术:

2.随着网络容量需求的不断增加,单个光模块的流量由主流的100g向着200g、400g甚至800g及以上快速演进。在网络设备散热能力的限制下,流量增加对每比特的平均传输功耗提出了极高的要求。

3.目前,为了获取更远的传输距离,光传输芯片中普遍采用高性能的软判决前向纠错(forward error correction,fec)技术,其功耗往往占整个芯片功耗的40%左右,而其中95%以上来自于fec译码器。因此,如何降低译码功耗是fec研究中的关键问题。

技术实现要素:

4.本技术提供了一种译码方法及装置,以降低译码功耗。

5.第一方面,本技术提供一种译码装置,该译码装置可以设置于通信设备的接收机中,例如,通信设备可以为终端设备、接入网设备、核心网设备等。该译码装置可以包括:依次设置的n个译码引擎、分别与n个译码引擎连接的输入总线以及分别与n个译码引擎连接的输出总线;其中,n个译码引擎中第j个译码引擎和第j 1个译码引擎电连接,第n个译码引擎与第1个译码引擎电连接。那么,输入总线,被配置为从信道接收第一码字。第j 1个译码引擎,被配置为从输入总线获取第一码字从第j个译码引擎和/或第j 1个译码引擎获取与第一码字关联的历史数据,并根据第一码字关联的历史数据对第一码字进行n次迭代译码。输出总线,被配置为在第一码字完成n次译码后,输出第n次译码结果。n≥2,j《n-1,n和j为正整数。

6.在本技术中,上述n个译码引擎呈环形结构,第1个译码引擎与第n个译码引擎首尾连接。这n个译码引擎在物理上可以单独设置,也可以集成在一起。

7.在本技术中,在上述呈环状结构的译码引擎中,由于每个译码引擎都包括存储模块,使得每个译码引擎无需共用一个memory,如此可以避免巨大mux和海量连线带来的asic设计拥塞;进一步地,由于译码引擎中的译码模块可以获取前一个译码引擎的存储模块中的关联历史数据,可以完全省去译码过程中的无效数据搬移,进而节省译码过程中的内存读写功耗。

8.在一些可能的实现方式中,第j个译码引擎包括:第一译码模块、第一存储模块、第一输入接口和第一输出接口;第j 1个译码引擎包括:第二译码模块、第二存储模块、第二输入接口和第二输出接口;第一译码模块与第一存储模块电连接,第二译码模块分别与第一存储模块和第二存储模块电连接。第二输入接口,被配置为从输入总线获取第一码字,并写入第二存储模块。第二译码模块,被配置为:周期地从第二存储模块获取第二码字;从第一存储模块和/或第二存储模块获取第二码字关联的历史数据;根据第二码字关联的历史数据对第二码字进行第i 1次译码;将第i 1次译码后的译码结果写入第二存储模块。第二输

出接口,被配置为获取第一码字的第n次译码结果,并向输出总线输出第n次译码结果。第二码字为第一码字或者第一码字的第i次译码结果,1≤i≤n,i为正整数

9.在本技术中,第一译码模块可以包括一个或者多个第一处理器,第一存储模块可以为一个或者多个第一存储器,第一输入接口可以为输入电路、输入模块、输入装置等,第一输出接口可以为输出电路、输出模块、输出装置等。第二译码模块可以包括一个或者多个第二处理器,第二存储模块可以为一个或者多个第二存储器,第二输入接口可以为输入电路、输入模块、输入装置等,第二输出接口可以为输出电路、输出模块、输出装置等。

10.在另一些可能的实施方式中,第二码字可以包括m帧数据。第二译码模块,被配置为:周期地从第二存储模块获取m帧数据中的第k帧数据;从第一存储模块和/或第二存储模块获取第k帧数据关联的历史数据;根据第k帧数据关联的历史数据对第k帧数据进行第i 1次译码;使用第i 1次译码结果更新第k帧数据。k≤m,m和k为正整数。

11.在另一些可能的实施方式中,第二输入接口,被配置为以n

×

m帧为周期循环地从输入总线获取第一码字。第二输出接口,被配置为以n

×

m帧为周期向输出总线输出第n次译码结果。

12.在另一些可能的实施方式中,每一帧数据为包含多个ofec帧的复帧。在实际应用中,一个复帧可以包括3个ofec帧。

13.在另一些可能的实施方式中,输出总线通过第一输出接口与第一存储模块连接,输出总线通过第二输出接口与第二存储模块连接。

14.在另一些可能的实施方式中,输出总线通过第一输出接口与第一译码模块连接,输出总线通过第二输出接口与第二译码模块连接。

15.第二方面,本技术提供一种译码方法,该方法可以应用于第一方面及其任一种可能的实施方式所述的译码装置。该译码方法可以包括:输入总线从信道接收第一码字;第j 1个译码引擎从输入总线获取第一码字;第j 1个译码引擎从第j个译码引擎和/或第j 1个译码引擎获取第一码字关联的历史数据;第j 1个译码引擎根据第一码字关联的历史数据,对第一码字进行n次迭代译码;输出总线在第一码字完成n次迭代译码后,输出第n次译码结果;其中,n≥2,j《n-1,n和j为正整数。

16.在一些可能的实施方式中,第j 1个译码引擎从输入总线获取第一码字,可以包括:第二输入接口从输入总线获取第一码字,并写入第二存储模块;第二译码模块周期地从第二存储模块获取第二码字,第二码字为第一码字或第一码字的第i次译码结果,1≤i≤n,i为正整数。第j 1个译码引擎从第j个译码引擎获取第一码字关联的历史数据,包括:第二译码模块从第一存储模块和/或第二存储模块获取第二码字关联的历史数据。第j 1个译码引擎根据第一码字关联的历史数据,对第二码字进行n次迭代译码,包括:第二译码模块根据第二码字关联的历史数据,对第二码字进行第i 1次译码,并将第i 1次译码结果写入第二存储模块;第二输出接口在第一码字完成n次译码后,获取第n次译码结果,并向输出总线输出第n次译码结果。

17.在另一些可能的实施方式中,第二码字包括m帧数据。第二译码模块周期地从第二存储模块获取第二码字,包括:第二译码模块周期地从第二存储模块获取m帧数据中的第k帧数据,其中,k≤m,m和k为正整数。第二译码模块从第一存储模块和/或第二存储模块获取第二码字关联的历史数据,包括:第二译码模块从第一存储模块和/或第二存储模块获取第

k帧数据关联的历史数据。第二译码模块将第i 1次译码结果写入第二存储模块,包括:第二译码模块使用第i 1次译码结果更新第k帧数据,直至第二译码模块完成m帧数据的第i 1次译码。

18.在另一些可能的实施方式中,第二输入接口从输入总线获取第一码字,包括:第二输入接口以n

×

m帧为周期循环地从输入总线获取第一码字。第二输出接口向输出总线输出第n次译码结果,包括:第二输出接口以n

×

m帧为周期向输出总线输出第n次译码结果。

19.在另一些可能的实施方式中,每一帧数据为包含多个ofec帧的复帧。可选的,每个复帧可以包括3个ofec帧。

20.在另一些可能的实施方式中,第二输出接口获取第n次译码结果,包括:第二输出接口从第二存储模块获取第n次译码结果;或,第二输出接口从第二译码模块获取第n次译码结果。

21.第三方面,本技术提供一种译码装置,可以包括:处理器和存储器,处理器与存储器耦合;处理器,用于支持译码装置实现如上述第二方面或者第二方面的任一种可能的实施方式中所述译码模块的译码方法。

22.第四方面,本技术提供一种计算机可读存储介质,计算机可读存储介质存储有指令。当指令在计算机上运行时,用于执行如上述第二方面或者第二方面的任一种可能的实施方式所述译码模块的译码方法。

23.第五方面,本技术提供一种计算机程序产品,当计算机程序产品在计算机上被执行时,使得计算机实现如上述第二方面或者第二方面的任一种可能的实施方式所述译码模块的译码方法。

24.应当理解的是,本技术的第二至五方面与本技术的第一方面的技术方案一致,各方面及对应的可行实施方式所取得的有益效果相似,不再赘述。

附图说明

25.为了更清楚地说明本技术实施例中的技术方案,下面将对本技术实施例或背景技术中所需要使用的附图进行说明。

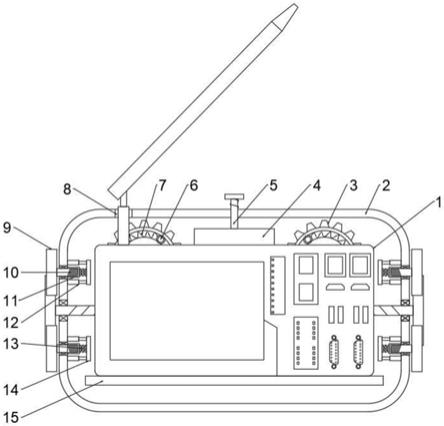

26.图1为本技术实施例中的译码装置的一种实现方式示意图;

27.图2为本技术实施例中的译码装置的另一种实现方式示意图;

28.图3为本技术实施例中的译码装置的又一种结构示意图;

29.图4为本技术实施例中的相邻两个译码引擎的示意图;

30.图5为本技术实施例中的输出接口和存储模块的一种示意图;

31.图6为本技术实施例中的输出接口和存储模块的另一种示意图;

32.图7为本技术实施例中的ofec码字的结构示意图;

33.图8为本技术实施例中的0至4时段的一次译码过程的示意图;

34.图9为本技术实施例中的译码方法的流程示意图。

具体实施方式

35.下面结合本技术实施例中的附图对本技术实施例进行描述。以下描述中,参考形成本技术一部分并以说明之方式示出本技术实施例的具体方面或可使用本技术实施例的

具体方面的附图。

36.需要说明的是,本技术中所述的“和/或”用于描述关联对象的关联关系。可以理解的,“和/或”可以表示关联对象之间存在三种关系。例如,a和/或b,可以表示单独存在a、同时存在a和b以及单独存在b这三种情况。

37.随着网络容量需求的不断增加,单个光模块的流量由主流的100g向着200g、400g甚至800g及以上快速演进。在网络设备散热能力的限制下,流量增加对每比特的平均传输功耗提出了极高的要求。然而为了获取更远的传输距离,光传输芯片中普遍采用高性能的软判决前向纠错(forward error correction,fec)技术,其功耗往往占整个芯片功耗的40%左右,而其中95%以上来自于fec译码器。因此的如何在保证性能增益的同时降低fec译码功耗是当前fec研究中的关键问题。

38.当前主流的fec译码器多采用迭代译码方式,可以通过配置不同的迭代级数来调整译码性能、延时等指标。同时,不同的迭代级数也影响fec译码器的实现复杂度和译码功耗。

39.在具体的芯片实现设计中,由于fec译码器的总体资源较大,经常将1个或者多个译码模块封装为一个译码引擎(可以称为processing engine或者decoder engine)单独进行实现设计。在fec译码过程中,需要在各个译码引擎之间实时地传递译码信息。如何高效的在各个译码引擎之间传递译码信息是低功耗译码设计中的一个关键点。

40.目前,上述迭代译码方式可以且不限于以下几种。

41.第一种,在多级迭代译码架构中,不同迭代译码级数读写相同的逻辑存储器(下面记作memory),memory中的数据不会随着迭代译码而移动。

42.在实际实现中,为了满足读写时序要求,图1为本技术实施例中的译码装置的一种实现方式示意图,参见图1中的(a)所示,在逻辑结构中,多级译码模块公用一个memory;参见图1中的(b)所示,在实现结构中,一个memory会被拆分成多块具体的物理memory,通过数据复用器(multiplexer,mux)与各级译码模块连接。但是,巨大的mux横跨多级译码模块,其中包含的成千上万根连线会为芯片的后端设计带来巨大的拥塞风险与功耗代价。

43.第二种,图2为本技术实施例中的译码装置的另一种实现方式示意图,参见图2所示,为了避免上述拥塞风险,每级译码模块可以单独配置对应的逻辑memory,在迭代译码过程中,译码数据随着译码级数的增加在不同逻辑memory中随着搬移。

44.举例来说,对于译码装置的译码周期中的一个时段,如第一时段,数据块1存储在memory 1中,由译码模块1(decoding module 1)进行第一次译码;数据块2存储在memory 2中,由译码模块2进行第二次译码,以此类推,数据块n存储在memory n中,由译码模块n进行第n次译码。

45.在第一时段的下一个时段,如第二时段,数据块n经历n次迭代译码后输出,同时新的数据块0写入memory 1,其他的数据块整体向后搬移一个memory,即数据块1搬移至memory 2、数据块2搬移至memory 3、

……

、数据块n-1搬移至memory n。那么,数据块0由译码模块1进行第一次译码,数据块1由译码模块2进行第二次译码,数据块2由译码模块3进行第三次译码,以此类推,数据块n-1由译码模块n进行第n次译码。

46.经此循环往复,每个数据块从输入到输出都会分别在n个译码模块中经历n次迭代译码,从而实现整个迭代译码过程。

47.在上述迭代译码过程中,数据块在memory之间是整体搬移的。但是,对于不同迭代级数来说,有些数值是不需要改变的(可以理解为不需要搬移的)。例如从信道输入的原始对数似然比(likelihood ratio,llr)和已经在译码过程中被译码正确的比特的后验概率值(a posteriori probability,app)。那么,在迭代译码过程中,在不同的memory之间搬移这些并不需要改变的数据会带来功耗的浪费。

48.那么,为了解决上述功耗浪费的问题,本技术实施例提供一种译码装置,该译码装置可以设置于通信设备的接收机中。例如,通信设备可以为终端设备、接入网设备、核心网设备等。这里,终端设备可以是一种向用户提供语音或者数据连通性的设备,例如也可以称为用户设备(user equipment,ue)、移动台(mobile station)、用户单元(subscriber unit)、站台(station)或者终端设备(terminal equipment,te)等。通信设备可以为蜂窝电话(cellular phone)、个人数字助理(personal digital assistant,pda)、无线调制解调器(modem)、手持v2p(handheld vehicle to perdestrian)设备、膝上型电脑(laptop computer)、无绳电话(cordless phone)、无线本地环路(wireless local loop,wll)台或者平板电脑(pad)等。随着无线通信技术的发展,可以接入无线通信系统、可以与无线通信系统的网络侧进行通信,或者通过无线通信系统与其它设备进行通信的设备都可以是本技术实施例中的终端设备,例如智能交通中的终端、汽车或路侧单元(road side unit,rsu)、智能家居中的家用设备、智能电网中的电力抄表仪器、电压监测仪器、环境监测仪器、智能安全网络中的视频监控仪器、收款机等等。终端设备可以是静态固定的,也可以是移动的。

49.图3为本技术实施例中的译码装置的结构示意图,参见图3所示,本技术提供的译码装置300可以包括:依次设置的n个译码引擎301(例如包括译码引擎301_0、译码引擎301_1、

……

、译码引擎301_j、译码引擎301_j 1、

……

、译码引擎301_n-1)、分别与n个译码引擎301连接的输入总线302和分别与n个译码引擎301连接的输出总线303。这里,n≥2,j《n-1,n和j为正整数。

50.n个译码引擎301中的第j个译码引擎(即译码引擎301_j)和第j 1个译码引擎301_j 1(即译码引擎301_j 1)电连接,n个译码引擎(即译码引擎301_n-1)与第1个译码引擎(即译码引擎301_1)电连接。

51.可以理解的,译码引擎301_j为译码引擎301_j 1的前一个译码引擎,上述n个译码引擎呈环形结构,第1个译码引擎与第n个译码引擎首尾连接。

52.在本技术实施例中,上述输入总线302,被配置为从信道接收第一码字(也可以理解为待译码码字或者新的码字)。

53.译码引擎303_j 1,被配置为:从输入总线获取第一码字;从译码引擎301_j和/或自身获取第一码字关联的历史数据;根据第一码字关联的历史数据,对第一码字进行n次迭代译码。

54.输出总线303,被配置在第一码字完成n次迭代译码后,输出第n次译码结果。

55.这里,本技术实施例中的码字可以包括m帧数据,m为正整数,如m=1、3、5等。那么,对于一次译码过程来说,译码引擎301_j 1在不同的时间段内对第一码字中不同的数据帧进行译码。首个进行译码的数据帧所关联的历史数据存储于译码引擎301_j中,最后进行译码的数据帧所关联的历史数据存储于译码引擎301_j 1中,而其他数据帧所关联的历史数据一部分存储于译码引擎301_j中,另一部分存储于译码引擎301_j 1中。

56.可选的,译码引擎301可以在开始新的译码周期时一次性从输入总线获取m帧数据,即全部的第一码字;或者,译码引擎301可以在一个译码周期中分部分获取m帧数据,即译码引擎301可以在译码周期中的一个时段获得一帧数据,在另一个时段获得另一帧数据,在其他时段获得剩下的数据帧;或者,译码引擎301在一个时段获得s帧数据,在另一个时段d帧,s d=m。当然,译码引擎301还可以采用其他方式从输入总线获取第一码字,本技术实施例不做具体限定。

57.需要说明的是,上述n个译码引擎在物理上可以单独设置,也可以集成在一起。

58.在本技术实施例中,上述n个译码引擎中的每个译码引擎可以包括:译码模块、存储模块、输入接口和输出接口。

59.这里,输入接口从输入总线获取第一码字,并写入存储模块。译码模块周期地(如按照译码周期)从存储模块获取第二码字(如第一码字或者第一码字的第i次译码结果),并从前一个译码引擎中的存储模块和/或自身的存储模块获取第一码字关联的历史数据。然后,译码模块根据第二码字关联的历史数据,对第二码字进行第i 1次译码,并将第i 1次译码结果写入存储模块;如此循环往复,直至译码模块完成对第一码字的n次迭代译码。输出接口获取第一码字的第n次译码结果,并向输出总线输出第n次译码结果。这里,1≤i≤n,i为正整数。

60.在一些可能的实施方式中,当译码模块对第一码字进行第一次译码时,第二码字就是第一码字本身,当译码模块对第一码字进行第i 1次译码时,第二码字就是第一码字的第i次译码结果。

61.在一些可能的实施方式中,第一码字与历史数据的关联关系是由编码方式决定的。根据编码方式,译码模块可以从前一个译码引擎的存储模块中读取第一码字关联的历史数据;或者,译码引擎可以从前一个译码引擎的存储模块读取第一码字关联的历史数据的一部分,以及从自身的存储模块各读取第一码字关联的历史数据的另一部分,由此获得第一码字关联的历史数据;再者,译码引擎还可以从自身的存储模块读取第一码字关联的历史数据。示例性的,历史数据可以包括从信道获取的原始llr、前一个译码引擎在译码后产生的外信息等。

62.需要说明的是,这里所说的两个译码引擎电连接是指前一个译码引擎中的存储模块与后一个译码引擎中的译码模块之间电连接。

63.在实际应用中,译码模块可以通过一个或者多个处理器的方式来实现。存储模块可以通过一个或者多个存储器的方式来实现。输入接口可以为输入电路、输入模块、输入装置等。输出接口可以为输出电路、输出模块、输出装置等。

64.示例性的,上述处理器可以通过专用集成电路(application specific integrated circuit,asic)实现,或可编程逻辑器件(programmable logic device,pld)实现。上述pld可以是复杂程序逻辑器件(complex programmable logical device,cpld),现场可编程门阵列(fpga),通用阵列逻辑(generic array logic,gal)或其任意组合。

65.上述存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,rom)、可编程只读存储器(programmable rom,prom)、可擦除可编程只读存储器(erasable prom,eprom)、电可擦除可编程只读存储器(electrically eprom,eeprom)或闪存。易失性存储器可以是

随机存取存储器(random access memory,ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(static ram,sram)、动态随机存取存储器(dram)、同步动态随机存取存储器(synchronous dram,sdram)、双倍数据速率同步动态随机存取存储器(double data date sdram,ddr sdram)、增强型同步动态随机存取存储器(enhanced sdram,esdram)、同步连接动态随机存取存储器(synchlink dram,sldram)和直接内存总线随机存取存储器(direct rambus ram,dr ram)。

66.当然,译码模块和存储模块还可以采用其他形式实现,本技术实施例不做具体限定。

67.图4为本技术实施例中的相邻两个译码引擎的示意图(可以理解的,图4示出的存储模块与输出接口的连接关系为一种实现方式的示例),结合图3和图4所示,上述译码引擎301_j可以包括:第一译码模块411、第一存储模块412、第一输入接口413和第一输出接口414;译码引擎301_j 1包括:第二译码模块421、第二存储模块422、第二输入接口423和第二输出接口424;第一译码模块411与第一存储模块412电连接,第二译码模块421分别与第一存储模块412和第二存储模块422电连接。

68.参见上述对译码引擎的描述,第一译码模块可以包括一个或者多个第一处理器,第一存储模块可以为一个或者多个第一存储器,第一输入接口可以为输入电路、输入模块、输入装置等,第一输出接口可以为输出电路、输出模块、输出装置等;第二译码模块可以包括一个或者多个第二处理器,第二存储模块可以为一个或者多个第二存储器,第二输入接口可以为输入电路、输入模块、输入装置等,第二输出接口可以为输出电路、输出模块、输出装置等。

69.在一些可能的实施方式中,第二输入接口,被配置为从输入总线获取第一码字(记为数据块a),并写入第二存储模块。

70.进一步地,第二译码模块,被配置为:周期地从第二存储模块获取第二码字(记为数据块b,例如数据块b可以为数据块a的第i次译码结果);从第一存储模块和/或第二存储模块获取数据块b关联的历史数据(可以理解的,数据块b关联的历史数据也与数据块a关联);根据数据块b关联的历史数据,对数据块b进行第i 1次译码,并将第i 1次译码结果写入第二存储模块。

71.进一步地,第二输出接口,被配置为获取第一码字的第n次译码结果,并向输出总线输出第n次译码结果。

72.具体来说,在第一时段,第二译码模块获取数据块b(即第一码字的第i次译码结果)以及从第一存储模块和/或第二存储模块读取数据块b关联的历史数据。然后,第二译码模块将数据块b关联的历史数据以及数据块b一同进行第i 1次译码,以得到第i 1次译码结果。接下来,第二译码模块将第i 1次译码结果写入第二存储模块,以更新数据块b。

73.在第二时段,第二译码模块再次获取更新后的数据块b以及从第一存储模块和/或第二存储模块中数据块b关联的历史数据;然后,第二译码模块将数据块b关联的历史数据以及获取的数据块b一同进行第i 2次译码,以得到第i 2次译码结果;接下来,第二译码模块将第i 2次译码结果写入第二存储模块,以更新数据块b。如此类推,直至第二译码模块对数据块a完成n次译码。

74.在一些可能的实施方式中,在第一时段,译码引擎301_j 1在进行第i 1次译码的

同时,译码引擎301_j可以进行第i 2次译码,译码引擎301_j 2可以在进行第i次译码,以此类推;同样的,在第二时段,若译码引擎301_j完成n(即n=i 2)次译码,则译码引擎301_j 1在进行第i 2次译码的同时,译码引擎301_j 2可以在进行第i 1次译码,以此类推。

75.在一些可能的实施方式中,上述实施例中的第一码字或者第二码字可以包括m帧数据。相应地,第二译码模块还可以被配置为:周期地从第二存储模块获取m帧数据中的第k(k≤m,k为正整数)帧数据;从第一存储模块获取第k帧数据关联的历史数据;根据第k帧数据关联的历史数据,对第k帧数据进行第i 1次译码;使用第i 1次译码结果更新第k帧数据。

76.这里,第二译码模块在进行第i 1次译码的过程中,按照译码周期,从第二存储模块中获取m帧数据中的第k帧数据(也就是上述数据块b),并从第一存储模块和/或第二存储模块获取第k帧数据关联的历史数据,然后,第二译码模块将第k帧数据和第k帧数据关联的历史数据一同进行译码,以获得第k帧数据的第i 1次译码结果,接着,第二译码模块将第i 1次译码结果写入第二存储模块,以更新第k帧数据,使得第二译码模块在进行第i 2次译码的过程可以使用更新后的第k帧数据进行第i 2次译码。

77.在本技术实施例中,上述译码引擎301_j 1中,第二输入接口可以被配置为以n

×

m帧为周期(即译码周期)循环地从输入总线获取第一码字,并将第一码字写入第二存储模块。然后,第二译码模块一个时段从第二存储模块读取一帧数据,m个时段读取m帧数据,以此为一次循环。

78.进一步地,第二输出接口可以被配置为以n

×

m帧为周期向输出总线输出第n次译码结果。可以理解的,在m个时段内,m帧数据在完成一次译码后,会被重新写入第二存储模块,以供进行下一次译码,直至m帧数据完成n次译码,第n次译码结果会被第二输出接口输出至输出总线。

79.示例性地,上述码字可以为fec码字、开放式前向纠错(open fec,ofec)码字等。

80.进一步地,为了提高译码效率,每一帧数据可以为包含多个ofec帧的复帧,在一个时段中可以并行译码。

81.在一些可能的实施方式中,上述图3和图4中的译码引擎中的输出接口和存储模块可以且不限于采用以下两种连接关系。

82.第一种,图5为本技术实施例中的输出接口和存储模块的一种示意图,结合图3和图5所示(输入接口未示出),在上述译码引擎301中,输出接口501可以设置在输出总线303和存储模块502之间,存储模块502与译码模块503电连接。译码模块在对数据块b完成第n次译码后,将第n次译码结果写入存储模块;然后,输出接口从存储模块获取第n次译码结果,并向输出总线输出。那么,结合图4所示,对于译码引擎301_j来说,输出总线可以通过第一输出接口414与第一存储模块412连接;对于译码引擎301_j 1来说,输出总线还可以通过第二输出接口424与第二存储模块422连接。

83.第二种,图6为本技术实施例中的输出接口和存储模块的另一种示意图,结合图3和图6所示(输入接口未示出),在上述译码引擎301中,输出接口601还可以设置在输出总线303和译码模块602之间,存储模块603与译码模块602电连接。译码模块602在对数据块b完成第n次译码后,将第n次译码结果输出给输出接口601,并由输出接口601向输出总线303输出,也就是说,译码模块602可以将第n次译码结果直接输出;进一步地,译码模块602还可以将第n次译码结果写入存储模块603,以供下一次译码使用。那么,结合图4所示,对于译码引

擎301_j来说,输出总线可以通过第一输出接口414与第一译码模块411连接;对于译码引擎301_j 1来说,输出总线还可以通过第二输出接口424与第二译码模块421连接。

84.下面以ofec码字为例对上述译码装置的工作过程进行说明。

85.ofec码字是由无限多行和x列(x=128)组成的无限矩阵中的集合。具有以下特性:每个位是两个“组成代码字”的一部分,其中每个组成代码字是长度为2x的二进制矢量x,满足奇偶校验约束xh=0,其中h是(2x,2x-k)二进制矩阵,其中2n》k》n。这里k=239,每个组成代码字有(2n

–

k)=17个奇偶校验位。作为奇偶校验位的分数是17/128,代码的速率是111/128=0.867,开销是17/111=15.3%。

86.特别是在ofec中,h是扩展bch(256,239)码的奇偶校验矩阵。该bch代码的汉明(hocquenghem)距离最小为6。

87.为了实现高速并行编码和解码,图7为本技术实施例中的ofec码字的结构示意图(图7中以不同的线型标识不同的组成代码字),参见图7所示,ofec码字的结构可以如下所示:

88.1、上述无限矩阵被划分为b

×

b位的方块(b=16),按行和列排列,如图7所示。每行有n/b个块(n/b=8),每个方块由方块行号r和方块列号c来标识,其中c=0、1、

…

、n/b-1分别出现在图的左侧和顶部数字。

89.2、方块内的每个位都由其行号r,其中r=0、1、...、b

–

1,和列号c,其中c=0、1、...、b

–

1。(其中位0的标识在方块的左上角)。总之,无限矩阵中的每个位都由四元组{r,c,r,c}来标识。

90.3、保护块的行数必须为2g的偶数(例如,图7中g=2或2g=4行)。

91.参见图7所示,一行比特由(r,r)标识,在该方块内有一个方块行号r和一个比特行号r,其中r=0、1、

…

、b

–

1。组成代码字可以通过包含该码字另一半的所有位的行号来标识。组成代码字(r,r)的第k位(k=0、1、

…

、2n

–

1)可以通过如下四元组来标识:

92.(1)如果k《n,则{(r^1)-2g-2n/b 2[k/b],[k/b],(k%b)^r,r};

[0093]

(2)如果k≥n,则{r,[(k-n)/b],r,(k%b)^r}。

[0094]

其中,(a%b)表示a取模b的值,(a^b)表示a和b按位“异或”的值。

[0095]

需要说明的是,在图7中相同线型的线段(垂直或水平)的并集构成了组成代码字的位。这些线段的顺序不是其在码字中的顺序。

[0096]

例如,参见图7所示,对于组成代码字(20,0),线段a指示其在半无限矩阵中的位置。位0到15在块(1,0)的第0列中,位16到31在块(3,1)的第0列中,

…

,以及位112至127在块(15,7)的第0列,位128至255位于块(20,0)至块(20,7)中的第0行。这里,位0到127被称为组成代码字的“前部(front)”,位128到255被称为组成代码字的“后部(back)”。

[0097]

请注意,ofec编码器中的每一位属于一个组成代码字的“前部”,而又属于另一个组成代码字的“后部”。同样,如果组成代码字的“后部”在方块的奇数行中,则其“前部”在方块的偶数行中,反之亦然。

[0098]

进一步地,位于某一个组成代码字的“前部”之下和“后部”之上的方块被称为保护块。

[0099]

继续参见图7所示,标识组成代码字(20,15)的线段b(即组成代码字(20,15)的“后部”)与标识组成代码字(20,0)的线段a(即组成代码字(20,0)的“前部”)位于相同的块中,

然而,因为上述“r”是15而不是0,所以公式(1)和(2)中的表达式“^r”有效,并且在每个块中以相反的顺序获取位。例如,组成代码字(20,15)的“前部”中的位0到15在块(1,0)中的第15列。

[0100]

基于上述ofec码字,假设上述译码装置包括4个译码引擎(n=4),即译码引擎0、译码引擎1、译码引擎2以及译码引擎3;译码周期设置为20个时段。

[0101]

其中,译码引擎0、译码引擎1、译码引擎2以及译码引擎3依次电连接,译码引擎3与译码引擎0电连接。需要说明的是,这里所说的两个译码引擎电连接是指前一个译码引擎中的存储模块与后一个译码引擎中的译码模块之间电连接。

[0102]

图8为本技术实施例中的0至4时段的译码过程的示意图,参见图8所示,以不同的填充图案标识不同的码字,其中,两个填充图案标识不同的码字可以组成一个ofec帧,3个ofec帧组成一个复帧。在一个时段(time slot)中,译码引擎可以对一个数据帧或者一个复帧进行译码。

[0103]

假设,译码引擎0在一个时段内对一个复帧进行译码。可选的,译码引擎0可以一次性从输入总线读取复帧0至4,并写入译码引擎0的存储模块,然后开始译码。

[0104]

在0时段中,译码引擎0中的译码模块从自身的存储模块读取复帧0(即6个不同填充图案标识的码字),以及从译码引擎3中读取复帧0关联的历史数据(即译码引擎3中与复帧0相同填充图案标识的数据块,也可以理解为复帧0中每一个ofec码字的“前部”),然后,译码引擎0中的译码模块对复帧0及其关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎0中的存储模块。

[0105]

在1时段中,译码引擎0中的译码模块从自身的存储模块读取复帧1,以及从译码引擎3中的存储模块和译码引擎0自身的存储模块读取复帧1关联的历史数据(即译码引擎3和译码引擎0中与复帧1相同填充图案标识的数据块,也可以理解为复帧1中每一个ofec码字的“前部”),然后,译码引擎0中的译码模块对复帧1及其关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎0中的存储模块。

[0106]

示例性的,在对复帧1进行译码时,译码引擎0可以将从译码引擎3中获取的与复帧1关联的数据块(即译码引擎3中与复帧1相同填充图案标识的数据块)以及从译码引擎0中获取的复帧0的第1次译码结果的“前部”和/或从信道获取的原始llr作为复帧1关联的历史数据。

[0107]

与上述1时段类似,在2到3时段中,译码引擎0依次从输入总线中读取复帧2和复帧3,每个时段读取对应的一个复帧,并写入译码引擎0中的存储模块。在每个时段内,译码引擎0中的译码模块从存储模块读取一个复帧(即当前复帧)以及从译码引擎3中的存储模块和自身的存储模块读取当前复帧关联的历史数据(即当前复帧中每一个ofec码字的“前部”)。然后,译码引擎0中的译码模块对当前复帧和当前复帧关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎0中的存储模块。

[0108]

在4时段中,译码引擎0中的译码模块从自身的存储模块读取复帧4,以及从自身的存储模块读取复帧4关联的历史数据(如复帧0至3的第一次译码结果的“前部”),然后,译码引擎0中的译码模块对复帧4及其关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎0中的存储模块。

[0109]

在对复帧0至4完成译码之后,由于复帧0至4只经历了一次迭代译码,因此不需要

输出。

[0110]

与上述过程类似,在5到9时段中,译码引擎1从输入总线中读取复帧5至9,每个时段读取对应的复帧,并写入译码引擎1中的存储模块。在每个时段内,译码引擎1中的译码模块从存储模块读取一个复帧(即当前复帧)以及从译码引擎0和/或译码引擎1中的存储模块获得当前复帧关联的历史数据。然后,译码引擎1中的译码模块对当前复帧和当前复帧关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎1中的存储模块。在对复帧5至9完成译码之后,由于复帧5至9只经历了一次迭代译码,因此不需要输出。而与此同时,译码引擎0则对复帧0至4进行第二次迭代译码。

[0111]

在10到14时段中,译码引擎2从输入总线中读取复帧10至14,每个时段读取对应的复帧,并写入译码引擎2中的存储模块。在每个时段内,译码引擎2中的译码模块从存储模块读取一个复帧(即当前复帧)以及从译码引擎1和/或译码引擎2中的存储模块获得当前复帧关联的历史数据。然后,译码引擎2中的译码模块对当前复帧和当前复帧关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎2中的存储模块。在对复帧10至14完成译码之后,由于复帧10至14只经历了一次迭代译码,因此不需要输出。而与此同时,译码引擎0则对复帧0至4进行第三次迭代译码,译码引擎1则对复帧5至9进行第二次迭代译码。

[0112]

在15到19时段中,译码引擎3从输入总线中读取复帧15至19,每个时段读取对应的复帧,并写入译码引擎3中的存储模块。在每个时段内,译码引擎3中的译码模块从存储模块读取一个复帧(即当前复帧)以及从译码引擎2和/或译码引擎3中的存储模块获得当前复帧关联的历史数据。然后,译码引擎3中的译码模块对当前复帧和当前复帧关联的历史数据一同译码,获得第1次译码结果,并将第1次译码结果写入译码引擎3中的存储模块。在对复帧15至19完成译码之后,由于复帧15至19只经历了一次迭代译码,因此不需要输出。而与此同时,译码引擎0则对复帧0至4进行第四次迭代译码,译码引擎1则对复帧5至9进行第三次迭代译码,译码引擎2则对复帧10至14进行第二次迭代译码。在译码引擎0中的复帧0至4在经历四次迭代译码之后,向从输出总线输出第4次的译码结果,腾出对应的存储空间,因此在下一个译码周期中又可以向译码引擎0中的存储模块写入新到达的数据。

[0113]

经此循环往复,每个复帧在输入和输出之间均会经历四次完整的迭代译码,从而完成整个译码流程。

[0114]

由上述可知,在上述呈环状结构的迭代译码引擎中,由于每个译码引擎都包括存储模块,使得每个译码引擎无需共用一个memory,如此可以避免巨大mux和海量连线带来的asic设计拥塞;进一步地,由于译码引擎中的译码模块可以获取前一个译码引擎的存储模块中的关联历史数据,可以完全省去译码过程中的无效数据搬移,进而节省译码过程中的内存读写功耗。

[0115]

基于同一发明构思,本技术实施例还提供一种译码的方法,该方法可以应用于上述实施例中的译码装置。那么,结合上述译码装置的结构,对本技术实施例所述的译码方法进行说明。

[0116]

图9为本技术实施例中的译码方法的流程示意图,参见图9所示,该方法可以包括:

[0117]

s901、输入总线从信道接收第一码字。

[0118]

s902、第j 1个译码引擎从输入总线获取第一码字。

[0119]

s903、第j 1个译码引擎从第j个译码引擎和/或第j 1个译码引擎获取第一码字关联的历史数据。

[0120]

s904、第j 1个译码引擎根据第一码字关联的历史数据,对第一码字进行n次迭代译码。

[0121]

s905、输出总线在第一码字完成n次迭代译码后,输出第n次译码结果。

[0122]

其中,n≥2,j《n-1,n和j为正整数。

[0123]

在一些可能的实施方式中,第j个译码引擎包括:第一译码模块、第一存储模块、第一输入接口和第一输出接口;第j 1个译码引擎包括:第二译码模块、第二存储模块、第二输入接口和第二输出接口;第一译码模块与第一存储模块电连接,第二译码模块分别与第一存储模块和第二存储模块电连接;

[0124]

相应的,s902可以包括:第二输入接口从输入总线获取第一码字,并写入第二存储模块;第二译码模块周期地从第二存储模块获取第二码字,第二码字为第一码字或第一码字的第i次译码结果,0≤i≤n,i为正整数;

[0125]

s903可以包括:第二译码模块从第一存储模块和/或第二存储模块获取第二码字关联的历史数据;

[0126]

s904可以包括:第二译码模块根据第二码字关联的历史数据,对第二码字进行第i 1次译码,并将第i 1次译码结果写入第二存储模块;第二输出接口在第一码字完成n次译码后,获取第n次译码结果,并向输出总线输出第n次译码结果。

[0127]

在一些可能的实施方式中,第一码字可以包括m帧数据,m为正整数。可以理解的,第二码字也可以包括m帧数据。

[0128]

相应的,第二译码模块周期地从第二存储模块获取第二码字的步骤可以包括:第二译码模块周期地从第二存储模块获取m帧数据中的第k帧数据,其中,k≤m,k为正整数;

[0129]

第二译码模块从第一存储模块获取历史数据的步骤可以包括:第二译码模块从第一存储模块和/或第二存储模块获取第k帧数据关联的历史数据;

[0130]

第二译码模块将第i 1次译码结果写入第二存储模块的步骤可以包括:第二译码模块使用第i 1次译码结果更新第k帧数据。

[0131]

在一些可能的实施方式中,s902中第二输入接口从输入总线获取第一码字的步骤可以包括:第二输入接口以n

×

m帧为周期循环地从输入总线获取第一码字;

[0132]

s904中第二输出接口向输出总线输出第n次译码结果可以包括:第二输出接口以n

×

m帧为周期向输出总线输出第n次译码结果。

[0133]

在一些可能的实施方式中,每一帧数据为包含多个ofec帧的复帧,例如,一个复帧可以包括3个ofec帧。

[0134]

在一些可能的实施方式中,s904中第二输出接口获取第n次译码结果可以包括:第二输出接口从第二存储模块获取第n次译码结果;或,第二输出接口从第二译码模块获取第n次译码结果。

[0135]

由上述可知,通过采用上述呈环状结构的迭代译码引擎执行图9所述的译码方法,可以在不无效搬移数据的情况下完全等效的实现图1和图2所述的迭代译码功能。

[0136]

在上述实施例中,对各个实施例的描述各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

[0137]

以上所述,仅为本技术示例性的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。