一种微纳米结构定点缺陷掺杂的方法及nv色心传感器

技术领域

1.本发明涉及微纳加工技术与量子信息技术领域,具体涉及一种基于自对准工艺的微纳米结构定点缺陷掺杂的方法及应用。

背景技术:

2.固态量子系统因其可集成化、器件化,在量子信息领域被广泛的应用和研究。其中固体中的点缺陷因受到固体材料的保护,通常拥有良好的自旋性质和光学性质,因此成为目前固态量子计算、量子精密测量等方向研究和应用的热点,例如金刚石中的氮-空位色心(nv)、硅-空位色心(siv)、镍-氮色心(ne8)、碳化硅中的点缺陷等。其中金刚石中的nv色心凭借室温下优越的自旋相干时间、光学初始化读出手段、成熟微波控制方法,成为量子信息领域主要研究的固态体系之一。尤其是在微观磁测量领域,nv色心作为单自旋量子传感器展示出了纳米空间分辨率、单自旋探测灵敏度、宽松工作条件、无破坏性和无需磁屏蔽等突出优势

3.以nv色心为代表的光学缺陷通常发光较弱,受晶体材料本身高折射率的限制(比如金刚石(n=2.4)、碳化硅(n=2.6)等)点缺陷发出的荧光绝大部分在界面发生全反射效应,需要制备微纳米结构来提高光学荧光收集效率。例如制备固体浸没透镜[applied physics letters,2010,97(24):241901、journal of applied physics,2015,118(14):144501]、纳米柱波导[nano letters,2015,15(1):165-169]、超薄金刚石“牛眼”[nano letters,2015,15(3):1493-1497]以及抛物面[nano letters,2018,18(5):2787-2793]等微纳米光学结构。

[0004]

而光学荧光收集效率的提升效果与微纳米光学结构中缺陷的空间位置密切相关,通常要求缺陷在结构中心空间定位精度达到50nm才会有较强的效果。传统方法通过无掩膜离子注入进行掺杂,难以控制缺陷在结构中的空间位置,通常只有不到10%的光学结构达到预期增强效果。

[0005]

由工艺缺陷引起的空间位置不确定性是制约光学结构效果以及成品率的关键。为提升微纳光学结构的良率,需要将微纳结构和缺陷掺杂对准,实现微纳结构定点缺陷掺杂。

[0006]

目前已有的技术方案主要有:

[0007]

1.电子束光刻套刻,利用电子束成像实现对准[nano lett.2010,10,3168-3172]

[0008]

2.afm针尖制备小孔掩模结合,利用afm成像实现对准[applied physics a,2008,91(4):567-571、专利:us7126139b2]。

[0009]

3.聚焦离子束注入,利用离子束成像实现对准[nature communications,2017,8(1):1-7、physica status solidi(a),2013,210(10):2055-2059]

[0010]

这些方法,均存在复杂的对准过程,且对准过程会有对准误差的存在,设备工艺要求较高且成本昂贵。

技术实现要素:

[0011]

(一)要解决的技术问题

[0012]

针对上述问题,本发明提供了一种基于自对准工艺的微纳米结构定点缺陷掺杂的方法及应用,用于至少部分解决传统无掩膜缺陷掺杂工艺难以控制缺陷在微纳米结构中的空间位置的等技术问题。

[0013]

(二)技术方案

[0014]

本发明一方面提供了一种基于自对准工艺的微纳米结构定点缺陷掺杂的方法,包括:s1,在晶体衬底表面依次形成牺牲层、光刻胶层;s2,根据微纳米图形在光刻胶层光刻出掩模孔;s3,通过掩模孔对牺牲层各向同性刻蚀,将微纳米图形放大至牺牲层;s4,对掩模孔下方裸露的晶体表面进行离子注入掺杂;s5,去除光刻胶层,沉积掩模材料;s6,去除牺牲层,牺牲层中微纳米放大图形转移为掩模材料图形;s7,对裸露晶体表面进行刻蚀,去除表面掩模材料并退火形成特定缺陷。

[0015]

进一步地,s1中牺牲层、光刻胶层形成双层薄膜结构,形成方式包括涂覆和气相沉积。

[0016]

进一步地,s1中牺牲层材料包括pmgi(聚二甲基戊二酰亚胺)、sio2、s1n。

[0017]

进一步地,s2中掩模孔为微纳米图形等比例缩小的图形,掩模孔位于下层结构图形中心正上方位置。

[0018]

进一步地,s4中离子注入的离子种类与掺杂缺陷种类相关,离子穿透深度不能超过光刻胶层的厚度。

[0019]

进一步地,s5中沉积掩模材料采用镀膜工艺,包括蒸发镀膜、溅射镀膜。

[0020]

进一步地,s6中去除牺牲层采用溶脱剥离的方式。

[0021]

进一步地,s7中对裸露晶体表面刻蚀采用干法刻蚀工艺,包括等离子体刻蚀、反应离子刻蚀、感应耦合等离子体刻蚀。

[0022]

进一步地,s7中去除表面掩模材料采用干法刻蚀或湿法刻蚀工艺。

[0023]

本发明另一方面提供了一种nv色心传感器,nv色心传感器中的nv色心通过如前述的方法制备。

[0024]

(三)有益效果

[0025]

本发明实施例提供的一种基于自对准工艺的微纳米结构定点缺陷掺杂的方法及应用,实现了微纳米结构中的定点掺杂,有效的提升缺陷在微纳结构中位置的精确性;去除空间位置不确定性对光学结构效果以及成品率的影响;并可获得利用该方法所制备的高品质nv色心传感器。

附图说明

[0026]

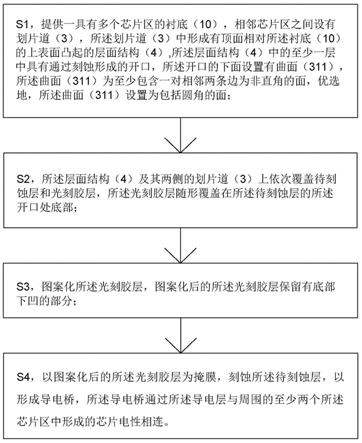

图1示意性示出了根据本发明实施例基于自对准工艺的微纳米结构定点缺陷掺杂的方法的流程图;

[0027]

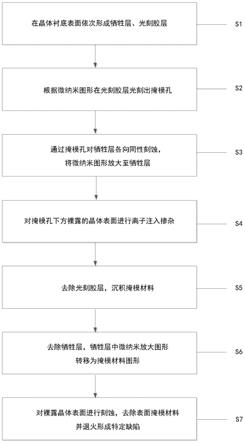

图2示意性示出了根据本发明实施例基于自对准工艺的微纳米结构定点缺陷掺杂示意图;

[0028]

附图标记

[0029]

1-pmma;

[0030]

2-pmgi;

[0031]

3-金刚石样品;

[0032]

4-晶格缺陷;

[0033]

5-金属掩模;

[0034]

6-nv色心。

具体实施方式

[0035]

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

[0036]

本发明的第一实施例提供一种基于自对准工艺的微纳米结构定点缺陷掺杂的方法,请参见图1,包括:s1,在晶体衬底表面依次形成牺牲层、光刻胶层;s2,根据微纳米图形在光刻胶层光刻出掩模孔;s3,通过掩模孔对牺牲层各向同性刻蚀,将微纳米图形放大至牺牲层;s4,对掩模孔下方裸露的晶体表面进行离子注入掺杂;s5,去除光刻胶层,沉积掩模材料;s6,去除牺牲层,牺牲层中微纳米放大图形转移为掩模材料图形;s7,对裸露晶体表面进行刻蚀,去除表面掩模材料并退火形成特定缺陷。

[0037]

提供晶体衬底,在表面形成双层薄膜结构,下层结构为牺牲层能够被各向同性腐蚀,顶层结构为光刻胶;通过光刻工艺根据微纳米结构形状在顶层胶结构上制备出掩模孔;利用刻蚀液通过掩模孔,对下层结构进行各向同性刻蚀。将掩模孔图形放大至下层结构,实现下层结构的图形化;将顶层结构作为掩模,通过离子注入对掩模孔下方裸露的晶体表面进行掺杂;去除顶层光刻胶,利用镀膜工艺沉积掩模材料;通过溶脱剥离的方式去除下层结构材料,实现下层结构的图形转移为掩模材料图形;将掩模材料图形作为抗刻蚀的掩模,利用干法刻蚀工艺对裸露晶体表面进行刻蚀形成微纳米结构。后去除表面剩余掩模材料并退火形成特定缺陷。

[0038]

在上述实施例的基础上,s1中牺牲层、光刻胶层形成双层薄膜结构,形成方式包括涂覆和气相沉积。

[0039]

光刻胶层用于通过s2光刻制备掩模孔用于离子注入,牺牲层用于s3各向同性刻蚀形成图形,并通过s5镀膜和s6去除以形成刻蚀掩模。

[0040]

涂覆工艺通过旋涂或喷涂形成膜层结构,常用于光刻胶、pmgi、旋涂sio2层等材料;气相沉积通过物理气相沉积或化学气相沉积形成膜层结构,常用于sio2、sin材料。光刻胶材料包括紫外光刻胶、电子光刻胶。

[0041]

在上述实施例的基础上,s1中牺牲层材料包括pmgi、sio2、sin。

[0042]

牺牲层优选pmgi,其特点在于s3过程可以通过四甲基氢氧化铵(tmah)溶液进行各向同性刻蚀,过程对上层光刻胶结构影响较小。并且在s5过程去除光刻胶层使用丙酮时,不会溶解于丙酮。s6过程中用使用试剂n-甲基吡咯烷酮(nmp)进行去除得到掩模材料图形。

[0043]

牺牲层还可以选sio2、sin牺牲层,他们的特点在于s3过程可以通过boe(缓冲氧化物刻蚀液)或氢氟酸溶液进行各向同性刻蚀,过程对上层光刻胶结构影响较小。并且在s5过程去除光刻胶层使用丙酮时,不会溶解于丙酮。s6过程中用使用试剂boe(缓冲氧化物刻蚀液)或氢氟酸溶液得到掩模材料图形。

[0044]

在上述实施例的基础上,s2中掩模孔为微纳米图形等比例缩小的图形,掩模孔位

于下层结构图形中心正上方位置。

[0045]

掩模孔不仅作为s3过程牺牲层各项同性刻蚀掩模,还作为s4过程离子注入的掩模孔。通过光刻工艺根据微纳米结构形状在顶层胶结构上制备出掩模孔,光刻工艺可以是电子束光刻工艺、紫外光刻工艺。

[0046]

在上述实施例的基础上,s4中离子注入的离子种类与掺杂缺陷种类相关,离子穿透深度不能超过光刻胶层的厚度。

[0047]

根据掺杂缺陷种类的不同,注入的离子种类不同,例如掺杂nv色心注入含氮离子;掺杂siv色心注入含硅离子。

[0048]

离子穿透深度不能超过光刻胶层的厚度是因为超过光刻胶层厚度过后,光刻将无法阻挡离子注入晶体,因此无法控制注入离子位置。

[0049]

在上述实施例的基础上,s5中沉积掩模材料采用镀膜工艺,包括蒸发镀膜、溅射镀膜。

[0050]

掩模材料可以是金属、金属氧化物、非金属、非金属氧化物,蒸发镀膜工艺包括热蒸发镀膜和电子束蒸发镀膜,其具有能量低剥离后掩模边缘良好的优点;溅射镀膜工艺具有膜层致密度高粒径小的优点。

[0051]

在上述实施例的基础上,s6中去除牺牲层采用溶脱剥离的方式。

[0052]

溶脱剥离过程选用试剂根据下层结构材料种类决定,例如使用试剂n-甲基吡咯烷酮(nmp)进行下层结构pmgi的溶脱剥离、使用含有氢氟酸试剂进行下层结构sio2、sin的溶脱剥离。

[0053]

在上述实施例的基础上,s7中对裸露晶体表面刻蚀采用干法刻蚀工艺,包括等离子体刻蚀、反应离子刻蚀、感应耦合等离子体刻蚀。

[0054]

干法刻蚀工艺,包括离子束刻蚀、反应等离子体刻蚀、感应耦合等离子体刻蚀等,并且通过调节刻蚀功率、气体比例、刻蚀气压、刻蚀温度、刻蚀时间等条件,实现刻蚀深度,刻蚀侧壁倾斜角度的控制,形成特定的微纳米结构。

[0055]

在上述实施例的基础上,s7中去除表面掩模材料采用干法刻蚀或湿法刻蚀工艺。

[0056]

去除掩模材料采用干法刻蚀或湿法刻蚀工艺均可,干法刻蚀工艺需要使用等离子体刻蚀设备,具有操作简单工艺稳定精度高的优点,湿法刻蚀工艺具有低成本的优点。

[0057]

本发明的第二实施例提供一种nv色心传感器,nv色心传感器中的nv色心通过前述的方法制备。

[0058]

请参见图2,本发明提供一种实现微纳米结构中定点掺杂的方法,方法可以用于金刚石、碳化硅、h-bn微纳米结构中的点缺陷定点掺杂。以下以金刚石纳米柱波导端面正中心氮空位色心的定点掺杂为实施例,给出具体的实施方案:

[0059]

在金刚石衬底3表面形成双层薄膜结构,使用旋涂工艺形成pmgi牺牲层2、电子束光刻胶pmma光刻胶层1,即s1;

[0060]

对电子束光刻胶pmma进行电子束光刻制备出掩模孔,掩模孔为圆形状,直径小于纳米柱波导直径,即s2;

[0061]

刻蚀液不能损坏双层薄膜结构顶层,本步骤使用四甲基氢氧化铵(tmah)溶液进行各向同性刻蚀;实现下层结构的图形化为最终微纳米结构的形状,衬底平面内掩模孔位于下层结构图形中心正上方位置,本实施例中下层结构图形为圆形,掩模孔在正中心位置,即

s3;

[0062]

掺杂的缺陷平面内位置由离子注入方向进行控制,本实施例中,离子注入方向垂直衬底表面,晶格缺陷4位置将位于下层图形正中心;离子注入离子种类为含氮基团离子,即s4;

[0063]

使用丙酮对顶层光刻胶pmma进行溶解,同时不会破坏下层结构pmgi牺牲层2;掩模材料5使用金属ti,优选蒸发镀膜工艺,即s5;

[0064]

使用试剂n-甲基吡咯烷酮(nmp)进行下层结构pmgi牺牲层2的溶脱剥离,即s6;

[0065]

通过感应耦合等离子体刻蚀,形成高荧光收集效率的金刚石纳米柱波导结构;使用boe溶液湿法刻蚀去除ti金属5;使用600-1200℃真空环境进行退火形成nv色心6,其位于纳米柱波导端面正中心即s7。

[0066]

以上实施例完成微纳米结构的自对准定点掺杂。最终通过实施例可获得一种nv色心传感器,其特点在于nv色心均处于金刚石纳米柱波导结构端面正中心位置,均能达到预期的最优荧光收集效率,具有较高的良率。nv色心传感器的工作原理是,将外界的磁、电、温度等信息转化为nv色心荧光强度的信息进行读出。本实施例获得的nv色心传感器具有更高的荧光信号收集效率,因此具有更好的探测灵敏度。

[0067]

需要说明的是本专利所获得的传感器可以与扫描显微成像技术相结合,形成扫描试nv色心传感器。例如替代专利cn202010100070.x中纳米柱波导结构制作方法,提升传感器的良率。

[0068]

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。